# PHYSICALLY UNCLONABLE FUNCTION USING SCHMITT TRIGGERS

### **DISSERTATION - II**

Submitted In partial fulfilment of the Requirement for the Award of the Degree of

## MASTER OF TECHNOLOGY IN Electronics and Communication Engineering

By

### **RITU GUPTA**

Under the Esteemed Guidance of

MR. ABHISHEK KUMAR

PHAGWARA (DISTT. KAPURTHALA), PUNJAB

Department of Electronics and communication Engineering Lovely Professional University Phagwara-144411, Punjab (India) MAY 2017

### DECLARATION

I hereby declare that the dissertation-I report entitled "PHYSICALLY UNCLONABLE FUNCTION USING SCHMITT TRIGGERS" is an authentic record of my own work carried out as the requirements for the award of degree of Master of Technology in ELECTRONICS AND COMMUNICATION at Lovely Professional University, Phagwara under the guidance of Abhishek Kumar, Assistant Professor, Department of Electronics and Communication Engineering.

Date: 29/04/2017

**RITU GUPTA Reg. No. 11504950**

# **CERTIFICATE**

This is to certify that the pre-dissertation titled "**PHYSICALLY UNCLONABLE FUNCTION USING SCHMITT TRIGGERS** " that is being submitted by "**RITU GUPTA**" in partial fulfillment of the requirements for the award of **MASTER OF TECHNOLOGY** (**ELECTRONICS & COMMUNICATION**), is a record of bonafide work done under my guidance. The content of this report, in full or in parts, have neither taken from any other source nor have been submitted to any other Institute or university for award of any degree or diploma and the same is certified.

#### **ABHISHEK KUMAR**

#### Assistant professor

Lovely professional university Phagwara, Punjab.

Date: 29/04/2017

# ACKNOWLEDGEMENT

Time flies and I believe in that as it was just first day when I started working on this subject and didn't knew well from where and how to start and now it's been more than an year that I started working and is writing this report as a gist of my learning. It has been a marvelous experience.

I feel gratitude by getting an opportunity to pursue my masters in this university and to work and share my experience on this area of research of Analog VLSI. It has been a wonderful time while working under the guidance of Head of the Department **Ms. Cherry Bhargav** and mainly my mentor and my guide **Mr. Abhishek Kumar**. I also thank my friends who supported and encouraged me on my work.

> Ritu Gupta May 2017

### ABSTRACT

Physically unclonable functions or PUFs are innovative physical security primitives which produce unclonable and inherent instance-specific measurements of physical objects; PUFs are in many ways the inanimate equivalent of biometrics for human beings. Since they are able to securely generate and store secrets, PUFs allow to bootstrap the physical implementation of an information security system. Physically Unclonable Functions (PUF) are security primitives to combat Integrated Circuit (IC) cloning and counterfeiting. The response of the PUF is expected to be stable under environmental fluctuations (e.g., temperature and voltage fluctuation). Our analysis indicate that conventional arbiter PUF experiences significant variations due to environmental fluctuation degrading quality. In this paper we propose a novel Schmitt-Trigger (ST) based PUF that exploits the susceptibility of ST to process variations to realize high-quality robust arbiter type PUF. We have used 5 different types of ST level by level in order to change overall delay of the circuit. We have used an Inverter-based conventional arbiter PUF structure. The response is determined based on relative delay between paths. The path selection is done by challenges. The overall circuit is 8X8 level ST which includes multiplexers and flip flops aswell. To show encryption i.e, to generate a set of keys we have used a 3-bit circuit having eight outputs.

# TABLE OF CONTENTS

| TITLE                                   | PAGE NO. |

|-----------------------------------------|----------|

| Declaration                             | 1        |

| Certificate                             | 2        |

| Acknowledgement                         | 3        |

| Abstract                                | 4        |

| Table of Contents                       | 5        |

| CHAPTER-1                               | 6        |

| INTRODUCTION                            |          |

| CHAPTER-2                               | 8        |

| LITERATURE REVIEW                       |          |

| CHAPTER-3                               | 10       |

| <b>RATIONALE AND SCOPE OF THE STUDY</b> |          |

| CHAPTER-4                               | 11       |

| <b>OBJECTIVES OF THE STUDY</b>          |          |

| CHAPTER-5                               | 12       |

| MATERIALS AND RESEARCH METHODOLOGY      |          |

| CHAPTER-6                               | 17       |

| RESULT AND DISCUSSION                   |          |

| CHAPTER-7                               | 31       |

#### **CONCLUSION AND FUTURE SCOPE**

### REFERENCES

## **CHAPTER-1**

### INTRODUCTION

Anything can be possible in this world as this world is not ideal so, it would be exceptionally gullible to imagine that everybody is inherently dependable. Many gatherings have outside thought processes to carry on in a dependable way, e.g. the businesspeople, banks and business won't get numerous clients when they can't be trusted, and the other auto proprietors will essentially drive deliberately for their own security. Some can't be trusted at all like crooks and fear mongers, however this can likewise incorporate disappointed workers, jealous partners or meddling neighbors, or even typically genuine individuals who are enticed to mishandle a circumstance when it presents itself. Frameworks that actuate, ensure or even implement dependability of a group, individual or a system in our non-ideal world are called security systems and such systems which enable trust within us and that feeling which makes us feel and realize that we are safe is called security.

If we talk about information security there are few goals that can be achieved and that are data confidentiality, entity authentication, data authentication and data integration. **Cryptology** is another aspect which manages the development of conventions and calculations to accomplish data security objectives, normally on a numerical premise. An essential outline rule for some cryptographic developments is to lessen the security objective they endeavor to accomplish to the mystery of a solitary parameter in the development, called the key. The level of security is communicated in terms of the degree of effort required to break the key without even knowing about it.

**PUFs (Physically Unclonable Functions)** are items which are unclonable and give just a single reaction when a test is displayed. These are alter confirmation and can't be controlled without physically crushing them. In this way, they are other options to brilliant cards and biometric gadgets which are being utilized to secure home systems or little systems in an association. A PUF is best portrayed as "an outflow of an inalienable and unclonable occasion particular element of a physical protest", and all things considered has a solid likeness to biometric components of people, similar to fingerprints. To be particular, PUFs demonstrate qualities which can't be gotten from cryptographic decreases, however require a physical premise to set up them, the most imperative being physical unclonability. This implies through physical thinking it is demonstrated that delivering a physical clone of a PUF is to a great degree hard or inconceivable.

**1.1 PUF Constructions, Properties and Applications:-** The physical inspiration for asserting unclonability of an intrinsic example particular element is found in the specialized restrictions of the

generation of physical items. Indeed, even with outrageous control over an assembling procedure, no two physically precisely indistinguishable items can be made because of the impact of arbitrary and wild impacts. Normally, these impacts are little and just produce results at (sub-) minute scales, however leave there arbitrary checks in any case. A high-exactness estimation of these imprints fills in as an innate and case particular element. In addition, making a moment question which delivers a comparable estimation is infeasible from a physical point of view, and frequently even in fact outlandish. Producing such an estimation with an exactness sufficiently high to recognize these example particular components is the essential objective in the investigation of PUF developments. The essential system which is commonly utilized, is to plan a development, either outside or interior to the protest, which opens up these tiny contrasts to for all intents and purposes detectable levels.

A wide assortment of PUF developments in view of this standard are conceivable and have been proposed, considering objects from a wide range of materials and advancements, each with their own particular complexities and helpful properties. To apply PUFs to achieve physical security destinations, a non specific and target depiction of these PUF properties is required. In addition, it is critical to recognize genuinely PUF-particular properties from other helpful qualities which are characteristic to a particular developments however can't be summed up to all PUFs.

In light of their unclonability and other helpful properties, PUFs can satisfy various physical security targets when connected in the correct way. Other than exploiting the physical security properties of PUFs, such PUF-based applications additionally need to manage the functional constraints of the development. This is proficient by conveying a PUF in a plan together with different primitives that improve its qualities. Conveying a PUF in a bigger framework normally prompts exchange offs, and consequently streamlining issues, between the sought security level and the execution limitations of the application. In light of an investigation of such a plan, some PUF developments will offer preferred exchange offs over different ones.

| Year Topic Author Research Result |      |    |      |        |          |        |

|-----------------------------------|------|----|------|--------|----------|--------|

|                                   | Year | Te | opic | Author | Research | Result |

# CHAPTER-2 REVIEW OF LITERATURE

| After<br>2012(Exact<br>year<br>unknown- A<br>shorter<br>version of<br>this paper has<br>been<br>published at<br>CHES 2012) | PUFs: Myth, Fact<br>or Busted?<br>A Security<br>Evaluation of<br>Physically<br>Unclonable<br>Functions (PUFs)<br>Cast in Silicon<br>Extended Version? | Stefan Katzenbeisser1,<br>Ünal Kocabas1,<br>Vladimir Rožic3,<br>Ahmad-Reza Sadeghi2,<br>Ingrid<br>Verbauwhede3, and<br>Christian Wachsmann1 | Robustness & Unpredictability<br>of PUFs (SRAM, Ring<br>Oscillator, Arbiter, Flip-flop,<br>Latch)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SRAM and ring oscillator PUFs seem to finish all<br>desired properties of a PUF. In any case, the<br>arbitrator PUFs have a low entropy and the entropy<br>of the flip-tumble and snare PUFs is defenseless to<br>temperature assortments. Thusly, the sensibility of<br>these PUFs for security-essential applications, for<br>instance, check or key time must be purposely<br>considered.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Unknown Key-recovery<br>Attacks on Various<br>RO PUF<br>Constructions via<br>Helper Data<br>Manipulation                   |                                                                                                                                                       | Jeroen Delvaux and<br>Ingrid Verbauwhede                                                                                                    | PUF reaction bits are not<br>specifically usable as a mystery<br>key on account of two issues:<br>they are not flawlessly<br>reproducible and non-<br>consistently circulated. Along<br>these lines,listing the root<br>causes and providing examples<br>for RO PUFs in particular.<br>Helper data constructions are<br>required to resolve the former<br>issues. Hereby, public helper<br>bits are generated during a one-<br>time post-manufacturing<br>enrollment phase. They are<br>stored in (ochip) NVM and<br>assist with every key<br>reconstruction. However: the<br>secrecy of the response bits<br>should be preserved. | Like any other PUF, RO PUFs do require helper<br>data constructions so as to produce reproducible<br>and consistently appropriated keys. Be that as in<br>may, developments to be powerless against<br>control of their open partner information. By<br>observing system failure rates, an attacker car<br>retrieve the key, or at least obtain some information<br>about it. Actually, many more helper data<br>constructions have been proposed in literature, not<br>necessarily limited to the RO PUF.                                                                                                                                                                                                                                                                                                                               |  |

| 2009                                                                                                                       | SRAM<br>Characteristics as<br>Physical<br>Unclonable<br>Functions                                                                                     | Robyn Colopy &<br>Jatin Chopra                                                                                                              | Loss of revenue to the vendor<br>because attackers may steal and<br>clone the designs without<br>paying the original designer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Keeping in mind the end goal to peruse the substance, for this specific chip, we initially needed to introduce the substance. This introduction procedure sketched out by Xilinx set the greater part of the bits of the BRAM equivalent to zero. This would pulverize the first substance and thrashing our motivations of portraying a chip that can be utilized to verify a specific board in view of a key. However for future contemplations, with a FPGA chip whose capacities permit the perusing of the BRAM without annihilating the first substance, an execution of this comparable venture should be possible to describe the BRAM.                                                                                                                                                                                          |  |

| 2010                                                                                                                       | A Large Scale<br>Characterization of<br>RO-PUF                                                                                                        | Abhranil Maiti, Jeff<br>Casarona, Luke<br>McHale, Patrick<br>Schaumont                                                                      | Estimation of an<br>altogether vast<br>arrangement of<br>chips to portray<br>the impact of on-<br>chip minor<br>departure from<br>RO-PUF. Analysis<br>of the dataset<br>keeping in mind<br>the end goal to<br>demonstrate the<br>impact of circuit-<br>level minor<br>departure from<br>RO-PUF. A delay<br>model of the RO                                                                                                                                                                                                                                                                                                         | Possible to describe the break.<br>Portrayal of a ring-oscillator PUF over a<br>fundamentally substantial populace of<br>FPGAs. The outcomes demonstrates that<br>PUF yield marks are decently consistently<br>dispersed with high rate of uniqueness as<br>far as between pass on Hamming<br>separation. The high proportion of static<br>variety to the dynamic variety complies with<br>high unwavering quality of the PUF yield as<br>far as intra-chip Hamming separation. In<br>future, we plan to proceed with this work as<br>far as growing the size of the investigation.<br>Promote examination of the dataset<br>alongside testing elements, for example,<br>maturing impact of the chip is a piece of our<br>future work, and in addition refreshing our<br>open database as we try advance in our<br>estimation endeavors. |  |

| 2012            | Low Power Schmitt<br>Trigger                                                                                  | Swati Kundra*,<br>Priyanka Soni             | Reducing delay and making the schmitt trigger faster and low power consuming.                                                                                                                                                                                                                                                                                                                                      | Reduced number of PMOS and using capacitors for the balance instead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Schmitt-Trigger-<br>based Arbiter-PUFs<br>and Selective<br>Challenge-Pruning<br>for Robustness and<br>Quality | Swaroop Ghosh                               | perform nitty gritty<br>investigation to evaluate the<br>quality contrasted with<br>mediator PUF.<br>(b) Proposing low-overhead<br>ST-PUF plans to lessen the<br>region/control overhead while<br>upgrading the quality.<br>(c) Proposing specific test<br>pruning to upgrade the<br>heartiness by screening the<br>shaky test reaction sets.                                                                      | that undertakings the shortcoming of ST to process<br>assortments to recognize fabulous solid judge PUF,<br>performed unobtrusive components examination of<br>the ST-PUF under voltage and temperature<br>instabilities and number of stages. The ST-PUF can<br>give 44% better soundness at any rate, it is<br>connected with immense domain, power and<br>throughput overhead. We extended this thought to<br>arrange a couple low-overhead ST-based PUFs that<br>give similar quality. We similarly proposed a<br>specific test pruning method that can improve the<br>PUF security out and out with minor defilement in<br>number of available test response sets. |

| Unknown<br>2015 | Reliable and<br>Efficient PUF-<br>Based Key<br>Generation<br>Using Pattern<br>Matching<br>A Family of         | Zdenek (Sid) Paral, and<br>Srinivas Devadas | the uniqueness<br>and<br>the reliability of the RO-<br>PUF are influenced by<br>the variation of the<br>oscillation-loop delay.<br>As opposed to utilizing a<br>settled (and potentially) open<br>test, while keeping the reaction<br>bits mystery, we invert the<br>worldview and keep mystery<br>the specific challenges that<br>produce uncovered reaction<br>bits. The mystery key can be<br>picked aimlessly. | Just a PUF, registers, bit-correlation, and edge<br>calculation rationale are required. The era of keys<br>can be made speedier and the security level raised<br>by expanding the quantity of PUFs. All together for<br>the presented reactions to not be a security peril we<br>needed to utilize a 4-XOR judge PUF. Future work<br>will concentrate on the advancement of new defer<br>PUF structures that are difficult to demonstrate and<br>have less characteristic commotion than a 4-XOR<br>judge PUF.<br>Proposed a novel Schmitt Trigger (ST) based PUF                                                                                                       |

|                 |                                                                                                               |                                             | loop is described,<br>and show how                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# CHAPTER-3 RATIONALE AND THE SCOPE OF THE STUDY

Anything we plan or do has a set of reasons, logics and motive of its own. Physically unclonable functions (PUF) is the budding technology in this era of electronics. In PUF we basically utilize the flaw of a circuit to hide and transmit confidential information and also to create passwords by generating a set of keys from that analog output which is a result of these flaws in the basic circuit.

Physically Unclonable Function (PUF) can be implemented using any circuit such as Multiplexers, Adders, Subtractors, Multipliers, Encoder, Decoder or any electrical circuit. Here, we are using Schmitt Triggers to implement PUF. Keeping in mind the previous analysis and experiments done by other researchers we have observed that the set of keys generated by PUF circuits are best suited for security purposes.

The main motive of this research is to ensure that a sufficient amount of delay can be generated and utilized to generate a set of keys for encryption purpose. So, here we have used a 64-bit circuit to check delay and then have used a part (3-bit i.e. a circuit with eight outputs) of the same circuit to check the that it is capable to generate a certain set of keys for encryption .

# CHAPTER-4 OBJECTIVES OF THE STUDY

Keeping in mind the end goal to give these physical security targets, we can't depend on scientific diminishments any longer. Rather, we have to create physical procedures and primitives which, in light of physical thinking, can be trusted to withstand certain physical ambushes and can in this way give certain physical security objectives. We call such primitives physical establishments of trust. Veritable self-assertive number generators gather sporadic numbers from truly physical wellsprings of discretion and can consequently be trusted to convey extremely unpredictable keys for cryptographic purposes. Arrangement styles for automated silicon circuits have been delivered which restrict and ideally discard certain physical side channels. Physically unclonable limits or PUFs convey whimsical and event specific values and can be used to give physically secure key time and limit. They are the principal subject of this recommendation.

# CHAPTER-5 MATERIALS AND RESEARCH METHODOLOGY

**5.1 DEFINITION-** Keeping in mind the end goal to give these physical security targets, we can't depend on scientific diminishments any longer. Rather, we have to create physical procedures and primitives which, in light of physical thinking, can be trusted to withstand certain physical assaults and can subsequently give certain physical security goals. We call such primitives physical foundations of trust. Genuine arbitrary number generators collect irregular numbers from really physical wellsprings of arbitrariness and can hence be trusted to deliver very irregular keys for cryptographic purposes. Configuration styles for computerized silicon circuits have been produced which limit and preferably dispose of certain physical side channels. Physically unclonable capacities or PUFs deliver erratic and occasion particular values and can be utilized to give physically secure key era and capacity. They are the fundamental subject of this proposition.

**5.2 INTRODUCTION-** Integrated Circuit (IC) cloning or duplicating includes replicating the plans and manufacturing them with the goal to imitate the bona fide chip, access secure substance as well as release mystery data. Physically Unclonable Function (PUF) is the prime fixing to avoid cloning. It replaces the hard-coded enter in the IC with particularly composed circuits that work on the rule of test reaction. The reaction to a specific test depends on the physical properties of the chip (e.g., handle). The unclonability of the PUF makes the reaction difficult to anticipate by the foes. A few sorts of PUFs have been proposed however because of its straightforwardness, referee PUF is a generally acknowledged plan. The ordinary judge PUF that produces 1-bit reaction for each arrangement of difficulties. It contains a mediator and two indistinguishably outlined postpone ways. For confirmation, a flag is dashed in two ways (the correct way is controlled by the test). The reaction is produced by looking at the postponements of the two ways in race. The postpone contrast is changed over to 0 or 1 reaction. Mediator PUF depends on the way that the way deferrals will vary because of process varieties. In this manner, the PUF reaction will be arbitrary in nature. This plan likewise utilizes postpone distinction to limit ecological change (i.e. temperature and voltage variety) incited mistakes.

**5.3 BASIC PURPOSE-** The basic purpose of PUFs is to provide ultimate security without getting cloned and hence protecting from all sort of theft attacks by providing an unique identity which only a particular individual will have and no resemblance with any other user will occur.

**5.4 RELIABILITY-** When it comes to reliability there is no match to PUFs. They are highly reliable when it comes to performance. And as this PUF uses five different types of Schmitt triggers, it gives a highly reliable output as per requirement.

**5.5 COST EFFECTIVENESS OF PUFs-** As it is possible to authenticate individual ICs using PUF without using costly cryptography primitives it results in reduction of overall cost of the security systems. Physical unclonable functions (PUFs) can be utilized as a financially savvy intends to store cryptographic key material in an unclonable way. A solid PUF will supplant the protected memory and crypto equipment on an inserted gadget and is utilized to safely distinguish the gadget to a server. Since the PUF does not require secure nonvolatile memory, hostile to alter hardware, or extra supporting crypto speeding up equipment, a PUF-based arrangement requires less range, power, and cover layers than a conventional way to deal with secure confirmation.

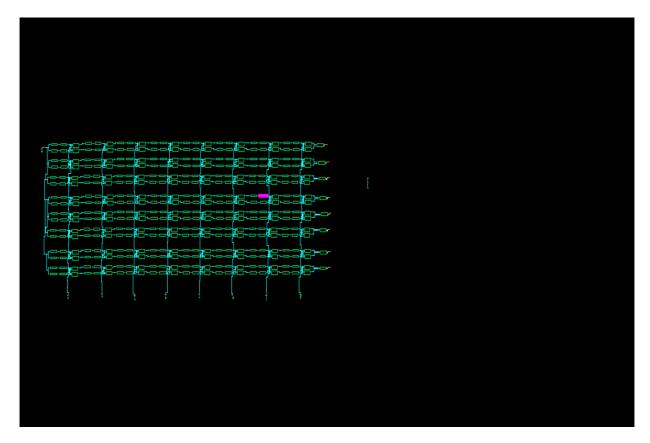

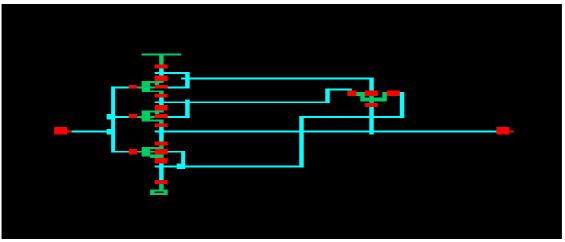

### 5.6 BASIC BLOCK OF 8X8 PUF-

Fig 1. Basic block diagram of 8X8 PUF using five different types of Schmitt Trigger(ST) circuits.

As the diagram shows that it has ten different delay paths and each path consists of a single type of or two type of at max Schmitt Triggers connected in series along with 2X1 Multiplexers and S-R Flip-Flop at the output. Each Multiplexer has a different select lines and each pair of delay lines have a single S-R Flip-Flop at the output. The five different types of Schmitt Triggers are as follows:

**5.6.1 GENERAL SCHMITT TRIGGER-** It's a comparator which switches the yield negative when the info goes upward through a positive reference voltage. It then uses positive criticism of a negative voltage to forestall changing back to the next state until the information goes through a lower limit voltage, therefore balancing out the exchanging against quick activating by clamor as it passes the trigger point. That is, it gives criticism which is not turned around in stage, but rather for this situation the flag that is being sustained back is a negative flag and keeps the yield driver to the negative supply voltage until the info dips under the lower outline limit.

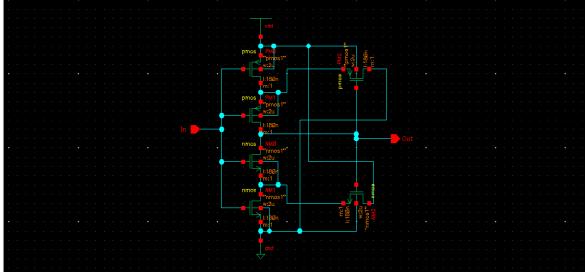

Fig2. General Schmitt Trigger

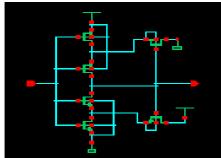

**5.6.2** N-TYPE SCHMITT TRIGGER- As the name indicates N-Type Schmitt Trigger includes NMOS as a dominating component as the functioning of the circuit, as shown in Fig3 mainly depends on the flow of electrons. Its bit faster as compared to the general Schmitt Trigger as the mobility of electron is more. This type of Schmitt trigger basically acts as a low power Schmitt Trigger. This circuit was referred by Swati Kundra and Priyanka Soni.

Fig3. N-Type Schmitt Trigger.

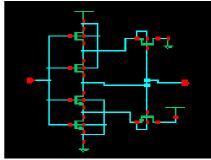

**5.6.3 P-TYPE SCHMITT TRIGGER-** This circuit is proposed by me keeping in mind the concept of N-Type Schmitt Trigger. As the name indicates P-Type Schmitt Trigger includes PMOS as a dominating component as the functioning of the circuit, as shown in Fig4 mainly

depends on the flow of holes. Its bit slower as compared to the general Schmitt Trigger as the mobility of holes is less. So, as a result it gives a larger delay comparatively.

Fig4. P-Type Schmitt Trigger

**5.6.4 UP and Down SCHMITT TRIGGER-** These are basically he normal Schmitt Triggers. the only difference is that both the Schmitt Triggers have different W/L parameters than the general Schmitt Triggers and also from each other. The

circuit diagrams are as shown below:

Fig5(a) UP Schmitt Trigger

Fig5(b) Down Schmitt Trigger

As we see that both the diagrams are basically same. There is the difference of width parameters only.

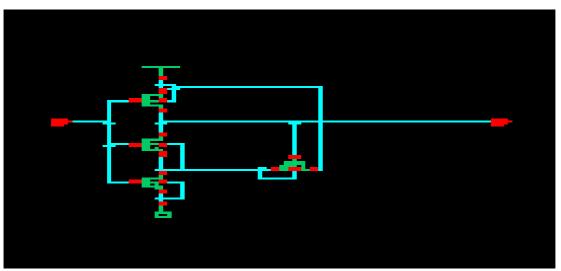

**5.6.5 MULTIPLEXER** - We are using here a 2:1 one multiplexer which has two inputs and is taking its inputs from the two different delay path and generating output which is fed to the next stage. We have used transmission gates for designing mux in order to reduce the number of transistors. The circuit Diagram is shown below:

Fig6. 2:1 Multiplexer using transmission gates.

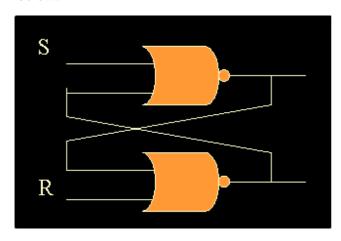

**5.6.6 S-R Flip Flop/Latch-** Here we are using a simple S-R Latch at the output made by using Nand gates. Circuit diagram and truth table is shown below.

| S | R | Action       |

|---|---|--------------|

| 0 | 0 | Not allowed  |

| 0 | 1 | Q = 1        |

| 1 | 0 | <b>Q</b> = 0 |

| 1 | 1 | No change    |

# CHAPTER-6 RESULT AND DISCUSSION

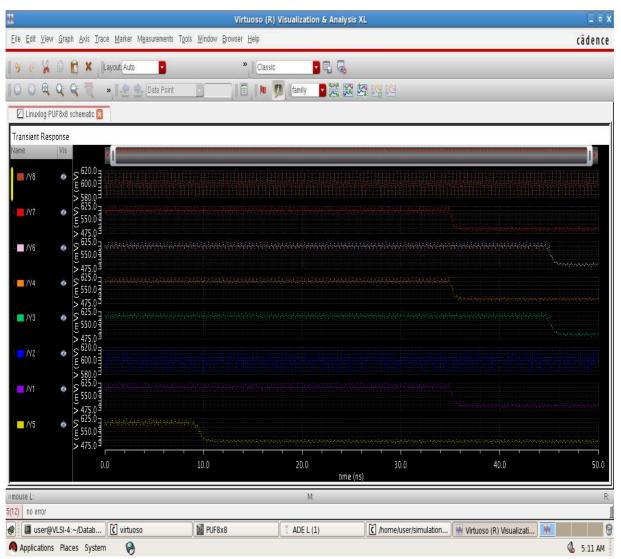

Considering **Fig.1** the delay output waveform received for over all circuit of **8X8** will be as follows:

Fig. 7 Output waveform for delay of 8X8 circuit.

The calculated value will be  $125 \times 10^{-12}$  seconds which is quiet a delay as compared to when simple basic Schmitt triggers are used.

| •                                                                                                                                                                                                   | Virtuoso (R) Visualization & Analysis XL ca                                                     | Iculator 📃 🗆 🗙                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| <u>File Tools View Option</u>                                                                                                                                                                       | ons <u>C</u> onstants <u>H</u> elp                                                              | cādence                                                            |

| In Context Results [                                                                                                                                                                                | DB: /home/user/simulation/PUFL6X8/spectre/schematic/psf                                         |                                                                    |

|                                                                                                                                                                                                     | c ⊖ vs ⊖ op ⊖ var ⊖ vn   ⊖ sp ⊖ vswr ⊖ hp ⊖ zm<br>⊖ is ⊖ opt ⊖ mp ⊖ vn2   ⊙ zp ⊖ yp ⊖ gd ⊖ data |                                                                    |

| Soff 🔾 Family 🔾 War                                                                                                                                                                                 | ve 🗹 Clip   🏹 🚛 Append 🔽 Rectangular 🔽 🎲   🗐                                                    |                                                                    |

| Key         Ø X         125           7         8         9         /           4         5         6         *           1         2         3         -           0         ±         +         4 | 0E-12<br>D 🚯 🎇 📴 🏚 📾 🎉 🎬 🎬 🚈 separator 🥱 🦿                                                      |                                                                    |

| Function Panel                                                                                                                                                                                      |                                                                                                 | ē x                                                                |

| All                                                                                                                                                                                                 | <b>2</b> Q                                                                                      |                                                                    |

| delay                                                                                                                                                                                               |                                                                                                 |                                                                    |

| Signal1                                                                                                                                                                                             | (v(*/Out" ?result "tran-tran")                                                                  |                                                                    |

| Signal2                                                                                                                                                                                             | v("/Vin" ?result "fran")                                                                        |                                                                    |

| Threshold Value 1                                                                                                                                                                                   | 0.5 Threshold Value                                                                             | 2 0.5                                                              |

| Edge Number 1                                                                                                                                                                                       | 1 Edge Number                                                                                   | 2 1                                                                |

| Edge Type 1                                                                                                                                                                                         | either 🔽 Edge Type                                                                              | 2 either 🔽 🗾                                                       |

| Periodicity 1                                                                                                                                                                                       | 1 Periodicity                                                                                   | 2 1                                                                |

| Number of occurrences                                                                                                                                                                               | single Plot/print v                                                                             | s. trigger                                                         |

| Start 1                                                                                                                                                                                             | 0.0                                                                                             |                                                                    |

| Start 2                                                                                                                                                                                             | nil Start 2 relative                                                                            | o (trigger 🔽 🔽                                                     |

| Ston                                                                                                                                                                                                | nil                                                                                             |                                                                    |

|                                                                                                                                                                                                     |                                                                                                 | <u>QK</u> <u>Apply</u> <u>D</u> efaults <u>C</u> lose <u>H</u> elp |

| Function Panel E                                                                                                                                                                                    | xpression Editor                                                                                |                                                                    |

| Successful evaluation                                                                                                                                                                               |                                                                                                 |                                                                    |

| 37                                                                                                                                                                                                  |                                                                                                 |                                                                    |

| 😵 🔲 [user@VLSI-4:.                                                                                                                                                                                  | 🕻 [virtuoso] 📓 PUFL6X8 📲 ADE L (3) 📁 [VAIDYA] 🥻                                                 | home/user/si) 👾 Virtuoso (R) Vi) 🙀 Virtuoso (R) Vi) 😌 🔣            |

| Applications Place                                                                                                                                                                                  | s System 🥱                                                                                      | 🚯 3:53 PM                                                          |

Fig.8 Calculated value of delay.

The power output waveform will look like as follows:

Fig.9 Power output of 8X8 circuit.

| ₩.                                                                                                                                                        | Virtuoso (R) Visualization & Analysis XL calculator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _ = >           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| <u>File</u> <u>T</u> o                                                                                                                                    | ools <u>V</u> iew <u>O</u> ptions <u>C</u> onstants <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | cādence         |

| 🛉 In                                                                                                                                                      | Context Results DB: //home/user/simulation/PUF&x8/spectre/schematic/psf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |

|                                                                                                                                                           | ∨vf   ⊖ vdc   ⊖ vs   ⊖ op ⊖ var   ⊖ vn   ⊖ sp ⊖ vswr ⊖ hp ⊖ zm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |

| ⊖ it                                                                                                                                                      | o if o idc o is o opt o mp o vn2 o zp o yp o dd o data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |

| off (                                                                                                                                                     | 🔾 Family 🔾 Wave  Clip   🌇 🚛 Append 💦 📴 Rectangular 💽 🎯   \Xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |

| 4 5                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |

| Function                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>e</b> >      |

| 4II                                                                                                                                                       | <b>2</b> Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |

| 1/x<br>10**x<br>PN<br>Rn<br>a2d<br>abs_jitter<br>acos<br>acosh<br>asinh<br>atan<br>atan<br>atan<br>atanh<br>average<br>b1f<br>bandwidt<br>clip<br>compare | d2a     freq_uinter     harmonicFreq     Ishift     phaseRadUmvrapped     root     tangent       dB10     frequency     histogram2D     mag     pir     rshift     tanh       dB20     ga     ifreq     nc_freq     pinNoise     s11     thd       dBm     gac_freq     in     nc_gain     pn     s12     totalNoise       dBn     gac_freq     integ     nf     pow     s12     totalNoise       defav     gainBwProd     imag     nfm     prms     s22     value       dth     gainBwProd     imag     nfmin     prms     s22     value       dthb     gatAscilWave int     overshoot     psdtingTime vh |                 |

|                                                                                                                                                           | ion Panel C Expression Editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | uoso (R) Visual |

| 🛥 Abbii                                                                                                                                                   | ications Places System 🛛 😔                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 🚯 12:35 PM      |

And the calculated value for power is as shown in Fig.10:

Fig.10 Calculated power output for 8X8 circuit

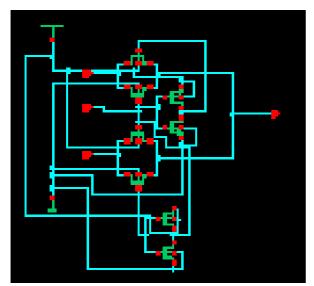

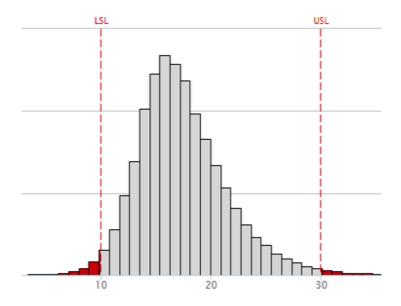

We can use **Monte Carlo** method to check that whether the output can be converted to required set of keys or not. So, here we are considering a 3-bit circuit which can generate eight outputs and is using Monte Carlo method to check as a reference that the main circuit will also be capable to generate required set of keys.

Little irregular varieties happen amid the assembling of circuit gadgets, bringing about behavioral contrasts between indistinguishably outlined gadgets. These varieties, or gadget confounds, are frequently rejected as an immaterial or troublesome part of simple circuit plan. This is not astonishing in light of the fact that it is hard to logically anticipate the conduct of any non-unimportant circuit because of the aggregation of the confuse mistakes from individual gadgets. Monte Carlo recreation can be utilized to examine how the individual gadget befuddles of a circuit may aggregate and influence the circuit all in all. This is accomplished by investigating a substantial arrangement of circuit instantiations, whose circuit gadgets have each been independently randomized in understanding to the jumble model of the specific gadget sort. As circuit architects experience difficulty appropriately surveying the impacts of gadget confound, the primary objective of this paper is to show an adaptable instrument that can reenact and break down information, as well as enable others to further research into gadget jumble. The following figure shows the circuit on which we are going to apply Monte carlo method to generate a set of outputs or keys:

| 2                                                | ADE XL Editing: Linuxlog 2X2 schematic                       | _ = ×                     |

|--------------------------------------------------|--------------------------------------------------------------|---------------------------|

| Launch <u>File</u> Edit <u>V</u> iew <u>C</u> re | eate Check Options Migrate Window Parasitics/LDE ADE XL Help | cādence                   |

| 1 🕒 🗁 🔹 🕪 🖸                                      | 🖾 🗶 🕕 » 🔍 🔍 🔍 » 🎝 1. 1. » Basic 📑 🖬 🗔 🕼 💭 💭 Sim Time         |                           |

| No Parasitics/LDE                                | 🔽 🐁 🖾 » Monte Carlo Sampling 🔄 🗞 🧇 🧿 🔕 🕼 Reference:          |                           |

| Navigator ? 🗗 🗙                                  | A adexi 2X2                                                  | ×                         |

| Pefault     G     Search     Name                |                                                              |                           |

| EX2<br>⊕                                         |                                                              |                           |

|                                                  |                                                              |                           |

|                                                  |                                                              |                           |

|                                                  |                                                              |                           |

|                                                  |                                                              |                           |

|                                                  |                                                              |                           |

|                                                  |                                                              | · · · · · · · · · · · · · |

|                                                  |                                                              |                           |

| mouse L: schSingleSelectPt()                     | M: schHiMousePopUp()                                         | R: schHiMousePopUp()      |

| 1(4) >                                           | •                                                            | Cmd: Sel: 0               |

|                                                  | 3:53 PM 🧠 Applications Places System                         |                           |

Fig.11 3-bit circuit to generate eight set of outputs

Monte-Carlo simulation is used to analyze how the proper selection of arbiter element and gate sizing can affect the delay. Let us understand it better with the help of an example illustrated by the group of Minitab engineers.

As somebody who has gathered and investigated genuine information as a profession, utilizing reproduced information for a Monte Carlo recreation sounds somewhat odd. How might you enhance a genuine item with reproduced information?

Companion by Minitab is an outcome stage that joins a desktop application for executing quality tasks with a web dashboard that makes writing about your whole quality activity truly easy. Among the first-in-class instruments in the desktop application is a Monte Carlo reproduction apparatus that makes this strategy amazingly available. **What Is Monte Carlo Simulation?**

The Monte Carlo strategy utilizes rehashed arbitrary testing to produce mimicked information to use with a numerical model. This model frequently originates from a factual investigation, for example, an outlined examination or a relapse investigation. Assume you concentrate a procedure and utilize insights to model it like this: Regression Equation

```

Material

Formula1 Insulation = 33.80 + 0.04630 InjPress - 0.3152 InjTemp - 1.064 CoolTemp

+ 0.01385 InjTemp*CoolTemp

```

With this sort of direct model, you can enter the procedure input values into the condition and anticipate the procedure yield. Nonetheless, in this present reality, the info values won't be a solitary esteem on account of fluctuation. Lamentably, this information inconstancy causes changeability and deformities in the yield. To outline a superior procedure, you could gather a pile of information with a specific end goal to decide how input inconstancy identifies with yield fluctuation under an assortment of conditions. In any case, on the off chance that you comprehend the run of the mill conveyance of the info qualities and you have a condition that models the procedure, you can without much of a stretch create an unlimited measure of

recreated information values and enter them into the procedure condition to deliver a reenacted circulation of the procedure yields.

You can likewise effectively change these information dispersions to reply "consider the possibility that" sorts of inquiries. That is the thing that Monte Carlo reenactment is about. In the illustration we are going to work through, we'll change both the mean and standard deviation of the recreated information to enhance the nature of an item. Today, reenacted information is routinely utilized as a part of circumstances where assets are restricted or assembling genuine information would be excessively costly or illogical.

### How Can Monte Carlo Simulation Help You?

Monte Carlo analysis can be used in order to:

- Simulate item comes about while representing the fluctuation in the data sources

- Optimize handle settings

- Identify basic to-quality elements

- Find an answer for decrease surrenders.

En route, Companion deciphers recreation comes about and gives well ordered direction to help you locate the most ideal answer for lessening absconds. I'll demonstrate to you proper methodologies to achieve the greater part of this correct at this point!

### Step-by-Step Example of Monte Carlo Simulation

A materials design for a building items maker is building up another protection item. The designer played out a test and utilized measurements to dissect handle calculates that could affect the protecting adequacy of the item. (The information for this DOE is only one of the numerous informational collection illustrations that can be found in Minitab's Data Set Library.) For this Monte Carlo recreation case, we'll utilize the relapse condition appeared above, which depicts the measurably noteworthy variables required all the while.Let's open Companion by Minitab's desktop app. Open or start a new a project, then right-click on the project Roadmap<sup>TM</sup> to insert the Monte Carlo Simulation tool.

### **Step 1: Define the Process Inputs and Outputs**

The main thing we have to do is to characterize the sources of info and the dissemination of their qualities. The procedure information sources are recorded in the relapse yield and the designer knows about the run of the mill mean and standard deviation of every variable. For the yield, we basically duplicate and glue the relapse condition that portrays the procedure from Minitab measurable programming right into Companion's Monte Carlo tool! When the Monte Carlo tool opens, we are presented with these entry fields:

| X Name        | Distribution | Parameters |        | Prev | view Action |

|---------------|--------------|------------|--------|------|-------------|

|               | Normal       | Mean       | St Dev |      | 0           |

| Add Another > | x            |            |        |      |             |

It's a simple matter to enter the data about the sources of info and yields for the procedure as appeared.

| X Name            | Distribution   |           | Parameters       |                            |                              | Preview                  | Actions        |

|-------------------|----------------|-----------|------------------|----------------------------|------------------------------|--------------------------|----------------|

|                   |                |           | Mean             | St Dev                     |                              |                          |                |

| InjPress          | Normal         | -         | 112              | 40                         |                              |                          | ۵              |

|                   |                |           | Mean             | St Dev                     |                              | 112                      |                |

| InjTemp           | Normal         | -         | 92.5             | 12                         |                              |                          | ۵              |

|                   |                |           | Mean             | St Dev                     |                              | 92.5                     |                |

| CoolTemp          | Normal         | -         | 35               | 11                         |                              |                          | 8              |

| Y Name            | Equation       |           |                  |                            | Spec Limits                  |                          | Action         |

| Y Name            | Equation       |           |                  |                            |                              |                          | Actions        |

| Insulation        | = 33.80+0.0463 | 0InjPress | -0.3152InjTemp-1 | 064CoolTemp+0.01385InjTemp |                              | USL<br>30                | ٥              |

|                   |                |           |                  |                            |                              |                          |                |

| Add Another Model | Y              |           |                  | Before you run the simu    | ılation, use the diagram bel | ow to verify that the mo | del is correc  |

|                   | Y              |           |                  | Before you run the simu    | ulation, use the diagram bel | ow to verify that the mo | odel is correc |

Verify your model with the above diagram and then click **Simulate** in the application ribbon.

|       | 300                 | 1.     |                 |                   | SI   | MULATION  |     |             |  |

|-------|---------------------|--------|-----------------|-------------------|------|-----------|-----|-------------|--|

| ΩĽ.   | 1                   | OME    | INCOME.         | VIEW              | SI   | MULATION  |     |             |  |

| X Add | Yo<br>Add<br>Output |        | Create<br>Group | 50,(<br>Iteration |      | Simulate  |     |             |  |

| Defin | e Model             | Funct  | tion Groups     | Run S             | imu  |           |     |             |  |

| >     | Proje               | ect To | day 🗌           | Monte C           | arte | Simulatio | e × |             |  |

|       | Def                 | ine    | Mode            | ł                 |      |           |     |             |  |

|       | X Nar               | te .   |                 | Distribu          | 600  | 1         |     | Parameters. |  |

|       |                     |        |                 |                   |      |           |     | Mean        |  |

### Initial Simulation Results

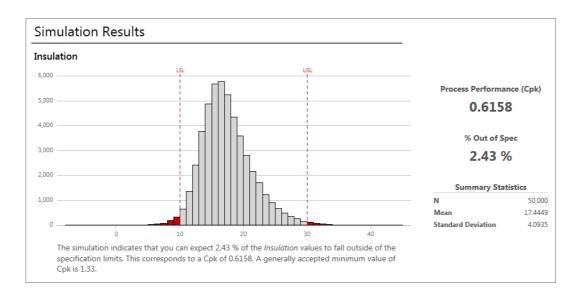

After you click Simulate, Companion rapidly runs 50,000 recreations as a matter of course, however you can determine a higher or lower number of reenactments.

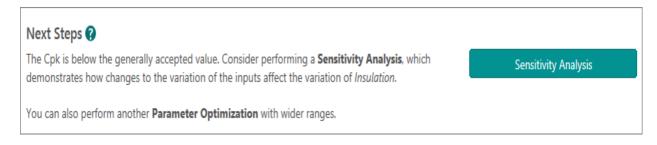

Companion translates the outcomes for you utilizing yield that is commonplace for ability examination—a capacity histogram, rate of deformities, and the Ppk measurement. Sidekick accurately calls attention to that our Ppk is beneath the for the most part acknowledged least estimation of Ppk.

### Step-by-Step Guidance for the Monte Carlo Simulation

But Companion doesn't simply run the recreation and afterward let you figure what to do next. Rather, Companion has established that our procedure is not palatable and presents you with a brilliant grouping of ventures to enhance the procedure capacity. How is it brilliant? Sidekick realizes that it is by and large less demanding to control the mean than the inconstancy. In this way, the following stride that Companion presents is Parameter Optimization, which finds the mean settings that limit the quantity of imperfections while as yet representing input fluctuation.

### Step 2: Define the Objective and Search Range for Parameter Optimization

At this stage, we need Companion to locate an ideal blend of mean information settings to limit deserts. After you click Parameter Optimization, you'll have to indicate your objective and utilize your procedure information to characterize a sensible scan extend for the information factors.

| Output (V)<br>Insulation                | Goal         | nize                    | Object  | t of Spec | -   |      |                |

|-----------------------------------------|--------------|-------------------------|---------|-----------|-----|------|----------------|

| efine Search I<br>ecify a range of para | Range 🕜      | : input. If an input is |         |           |     |      |                |

| input (X)                               | Distribution | Parameter               | Current | Noise     | Low | High | Representation |

| injPress                                | Normal       | Mean                    | 112     |           | 50  | 175  | 112            |

| njTemp                                  | Normal       | Mean                    | 92.5    |           | 50  | 150  | 92.5           |

| CoolTemp                                | Normal       | Mean                    | 35      |           | 15  | 60   | 35             |

|                                         |              |                         |         |           |     |      |                |

|                                         |              |                         |         |           |     |      |                |

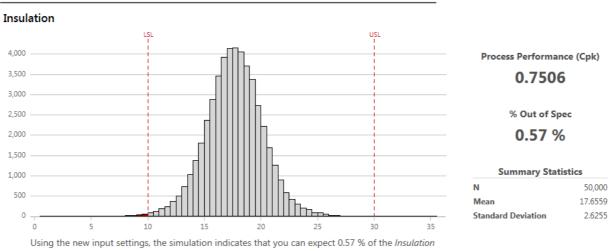

And, here are the simulation results!

Parameter Optimization Results

using the new input settings, the simulation indicates that you can expect 0.57 % of the *Insulation* values to fall outside of the specification limits. This corresponds to a Cpk of 0.7506. A generally accepted minimum value of Cpk is 1.33.

Initially, we can tell that the rate of imperfections is path down. We can likewise observe the ideal information settings in the table. Be that as it may, our Ppk measurement is still underneath the by and large acknowledged least esteem. Luckily, Companion has a prescribed next stride to additionally enhance the capacity of our procedure.

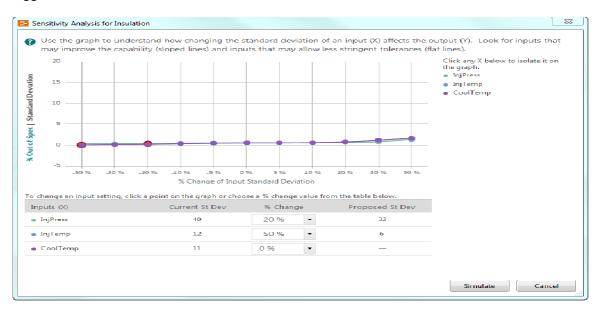

### Step 3: Control the Variability to Perform a Sensitivity Analysis

Up until now, we've enhanced the procedure by streamlining the mean information settings. That decreased imperfections incredibly, however regardless we have more to do in the Monte Carlo reenactment. Presently, we have to diminish the fluctuation in the process contributions to request to additionally lessen abandons.

Decreasing changeability is commonly more troublesome. Thusly, you would prefer not to waste assets controlling the standard deviation for sources of info that won't diminish the number deformities. Luckily, Companion incorporates an inventive diagram that helps you distinguish the sources of info where controlling the changeability will create the biggest decreases in deformities.

In this diagram, search for contributions with slanted lines since lessening these standard deviations can diminish the changeability in the yield. Alternately, you can ease resistances for contributions with a level line since they don't influence the changeability in the yield. In chart, the inclines are genuinely equivalent. Thusly, we'll take a stab at lessening the standard deviations of a few sources of info. You'll have to utilize prepare learning so as to distinguish practical diminishments. To change a setting, you can either tap the focuses on the lines, or utilize the draw down menu in the table.

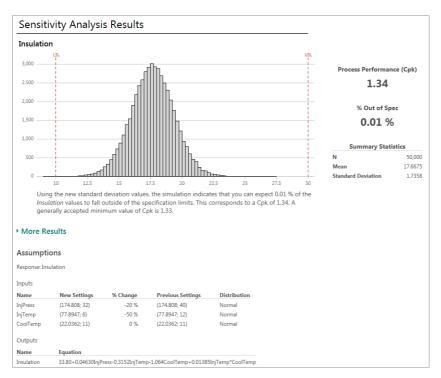

#### **Final Monte Carlo Simulation Results**

Victory! Here we see diminished number of imperfections in our procedure and our Ppk measurement is 1.34, which is over the benchmark esteem. The presumptions table demonstrates to us the new settings and standard deviations for the procedure inputs that we ought to attempt. In the event that we ran Parameter Optimization once more, it would focus the procedure and I'm certain we'd have even less imperfections.

To improve our process, Companion guided us on a smart sequence of steps during our Monte Carlo simulation:

- 1. Simulate the original process

- 2. Optimize the mean settings

- 3. Strategically reduce the variability

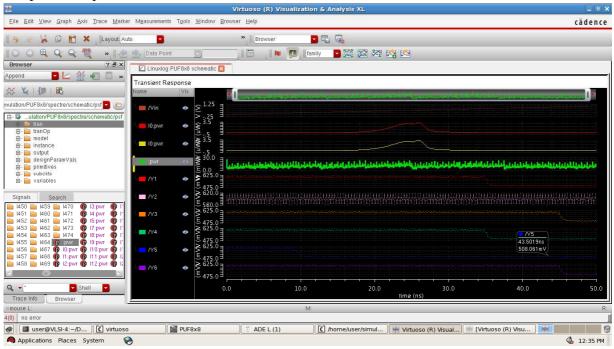

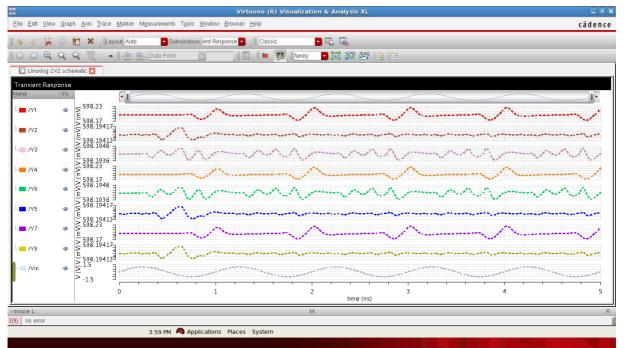

Now, with the reference to above explanation we can have the output for Fig.11 as follows:

Fig.12 Output waveform for 3-bit circuit

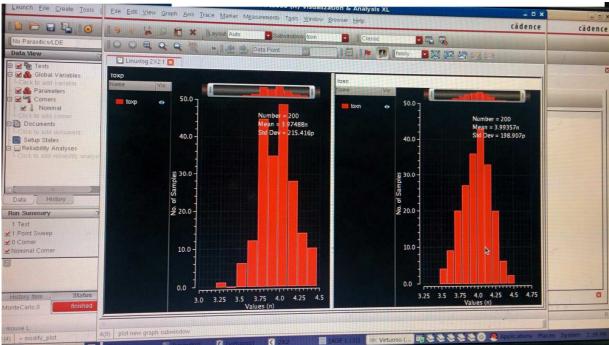

Fig.16.1 Monte Carlo output for 3-bit circuit

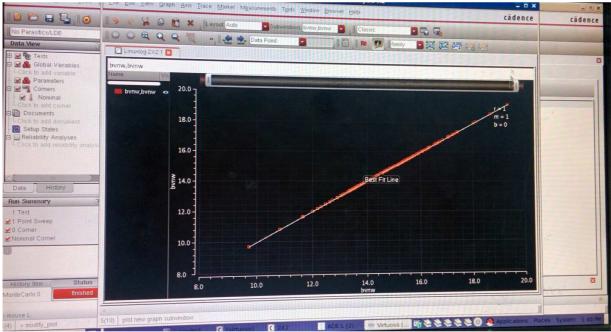

Fig16.2 Monte Carlo line output for 3-bit circuit

Hence, we can see that encryption of the delay output of a circuit using Schmitt Trigger is possible.

# CHAPTER-7 CONCLUSION AND FUTURE SCOPE

As PUF technology is not much old so there are encourage advancements conceivable, both in attempting to accomplish essential security goals in view of PUFs, and additionally endeavoring to coordinate PUFs and PUF-based primitives safely and effectively into bigger security frameworks. This report concludes that by altering small things like channel width or finger width, architecture of the Schmitt Trigger circuit can result to a sufficient amount of delay which will be enough for the processing of PUF. Also, it is possible to utilize that output for encryption in future.

## REFERENCES

[1] Suh, G. Edward, and Srinivas Devadas. "Physical unclonable functions for device authentication and secret key generation." In Proceedings of the 44th annual Design Automation Conference, pp. 9-14. ACM, 2007.

[2] J. Rabaey, et. al., Digital integrated circuits. Prentice hall, 2002.

[3] Lim, D.; Lee, J.W.; Gassend, B.; Suh, G.E.; van Dijk, M.; Devadas, S., "Extracting secret keys from integrated circuits," Very Large Scale Integration (VLSI) Systems, IEEE Transactions on , vol.13, no.10, pp.1200,1205, Oct. 2005.

[4] Gassend, Blaise, Dwaine Clarke, Marten Van Dijk, and Srinivas Devadas. "Silicon physical random functions." In Proceedings of the 9th ACM conference on Computer and Communications security, pp.14 8-160. ACM, 2002.

[5] Swati Kundra\*, Priyanka Soni "Low power Schmitt Trigger" Innovative Systems Design and Engineering www.iiste.org ISSN 2222-1727 (Paper) ISSN 2222-2871 (Online) Vol 3, No 2, 2012

[6] O. Schmitt (Jan 1938), "A thermionic trigger," J. Scientific Instruments, pp. 24-26.

[7] S. Seo, Y. Jeong, and J. Kenney (2007), "A modified CMOS frequency doubler considering delay time matching condition", *Proc. Int 'I Symp. Info. Tech. Converg.*, pp. 392-395.

[8] C. Wu and C. Chiang (Aug 2004), "A low-photo current CMOS retinal focal-plane sensor with a pseudo-BJT smoothing network and an adaptive current Schmitt trigger for scanner applications," *IEEE Sensors J.* **4**(4), 510-518.

[9] Kulkarni, K. Kim, and K. Roy (Oct 2007), "A 160 mV robust Schmitt trigger based sub-threshold SRAM," *IEEE J. Solid-State Circuits* **42**(10), 2303-2313.

[10] D. Park, 1. Rhee, and Y. Joo (2009), "Wide dynamic range and high SNR self reset CMOS image sensor using a Schmitt trigger", *Proc. IEEE Sensor Conf.*, pp. 294-296.