## PHYSICAL UNCLOANABLE FUNCTION (PUF)

### **DISSERTATION II**

Submitted By

## KONSAM JEMSON MEITEI

Department of ECE

In partial fulfilment of the Requirement For the

Award of the degree of

## MASTER OF TECHNOLOGY IN VLSI DOMAIN

Under the Esteemed Guidance of

#### MR. JYOTIRMOY PATHAK

School of Electronics & Communication Engineering Lovely Professional University, Punjab MAY 2017

|                                                                                            | <b>CERTIFICATE</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>FUNCTION(PUF)</b> fulfilment of the re <b>(VLSI)</b> , is a record full or in parts, ha | ify that the dissertation titled "PHYSIVAL UNCLOANABLE" in particular that is being submitted by "KONSAM JEMSON MEITEI" in particular particular that is being submitted by "KONSAM JEMSON MEITEI" in particular particular that is being submitted by "KONSAM JEMSON MEITEI" in particular pa |

|                                                                                            | Mr. JYOTIRMOY PATHAK<br>ASSISTANT PROFESSOR<br>(LOVELY PROFESSIONAL UNIVERSITY)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                            | Objective of the Thesis is satisfactory /unsatisfactory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

**Examiner I**

**Examiner II**

|                              | <u>ACKNOWLEDGEMENT</u>                                                                                                                                                        |               |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| opportunity                  | ke to thank <b>LOVELY PROFESSIONAL UNIVERSITY</b> to use their resource and work in such a challenging environm duals whom contributed their valuable time towards my thesis. |               |

| PATHAK"                      | express my sincere and heart full gratitude to my guide "MR Assistant professor, who guides me to take up this thesis in stentific approach.                                  |               |

| I would also<br>and supporte | o like to extend my gratitude to my friends and family who all<br>ed me in this thesis work.                                                                                  | lways encoura |

|                              |                                                                                                                                                                               |               |

|                              |                                                                                                                                                                               |               |

|                              | KONSAM JE<br>Reg. No. 1                                                                                                                                                       |               |

|                              |                                                                                                                                                                               |               |

|                              |                                                                                                                                                                               |               |

|                              |                                                                                                                                                                               |               |

|                              |                                                                                                                                                                               |               |

## **DECLARATION**

I, **KONSAM JEMSON MEITEI**, student of **MASTER OF TECHNOLOGY (VLSI)** under Department of ELECTRONICS ENGINEERING of Lovely Professional University, Punjab, hereby declare that all the information furnished in this dissertation-II report is based on my own intensive research and is genuine.

This dissertation-II, to the best of my knowledge, does not contain any part of my work which has been submitted for the award of my degree without proper citation.

Date:

KONSAM JEMSON MEITEI Reg. No. 11508694

# LIST OF CONTENTS

| CHAPTER NO | CHAPTER NAME P                                 | AGE NO |

|------------|------------------------------------------------|--------|

| 1          | INTRODUCTION                                   | 1      |

|            | 1. Historical overview                         | 1      |

|            | 2. Attacks on IC circuit                       | 1      |

|            | 3. Hardware security or PUF                    | 5      |

|            | 4. Types of silicon PUF                        | 6      |

|            | 4.1. Strong PUF                                | 6      |

|            | 4.2. Weak PUF                                  | 8      |

|            | 5. PUF application in hardware security        | 11     |

|            | 5.1. Authentication and Identification         | 11     |

|            | 5.2. Key generation                            | 11     |

|            | 6. PUF qualities and Metrics                   | 12     |

| 2          | LITERATURE REVIEW                              | 15     |

| 3          | RESEARCH METHODOLOGY                           | 22     |

|            | 1. Implementation of arbiter physical          |        |

|            | unclonable function                            | 22     |

|            | 2. Sub components                              | 25     |

|            | 2.1. MUX                                       | 25     |

|            | 2.2. Arbiter circuit                           | 28     |

|            | 3. Simulation of arbiter puf                   | 30     |

|            | 3.1 power and reliability measurement of basic |        |

|            | mux and standard feed forward                  | 30     |

|            | 3.2 The proposed modified feed forward mux pr  | uf 33  |

| 4 | PERFORMANCE COMPARISION OF THE VARIOUS MUX- BASED PUF | 39 |

|---|-------------------------------------------------------|----|

| 5 | CONCLUSIONS AND FUTURE SCOPE                          | 40 |

|   | REFERENCE                                             | 41 |

|   | APPENDIX:                                             |    |

|   | AUTOBIOGRAPHY                                         | 42 |

# LIST OF FIGURES

| FIG. | FIGURE CAPTION                                                  | PAGE |

|------|-----------------------------------------------------------------|------|

| NO.  |                                                                 | NO   |

| 1    | General representation of PUF                                   | 5    |

| 2    | The schematic of arbiter PUF                                    | 7    |

| 3    | Simple ring oscillator PUF architecture                         | 8    |

| 4    | Simple structure of SRAM cell                                   | 9    |

| 5    | The logical structure of latch PUF cell                         | 10   |

| 6    | General representation of a PUF                                 | 23   |

| 7    | General block diagram of an arbiter PUF                         | 24   |

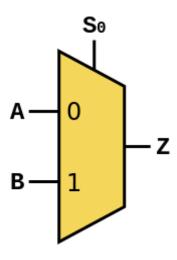

| 8    | 2:1 MUX circuit diagram representation                          | 26   |

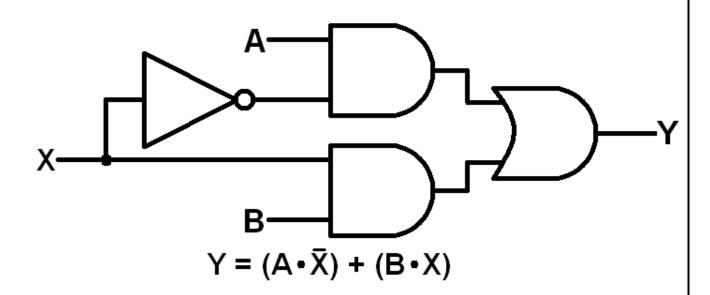

| 9    | 2:1 MUX logic diagram using logic gates                         | 26   |

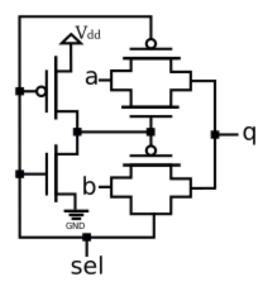

| 10   | 2:1 MUX using pass transistor                                   | 27   |

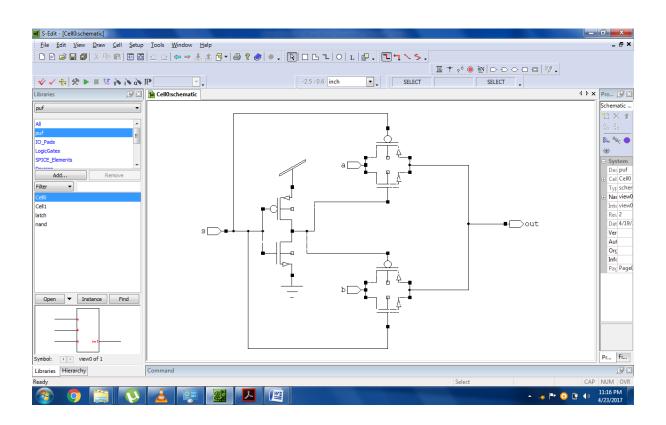

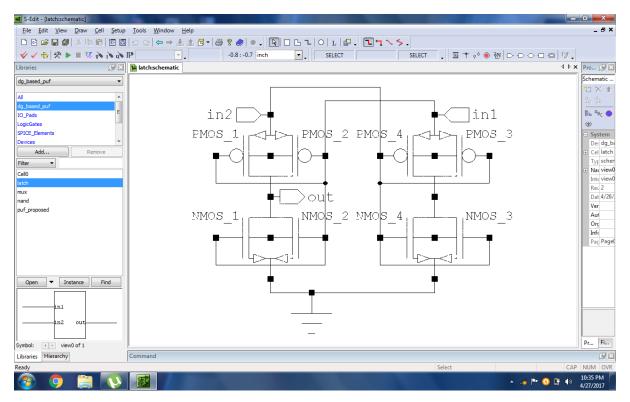

| 11   | Schematic representation of 2:1 MUX using pass transistor logic | 27   |

| 12   | A simple SR latch                                               | 28   |

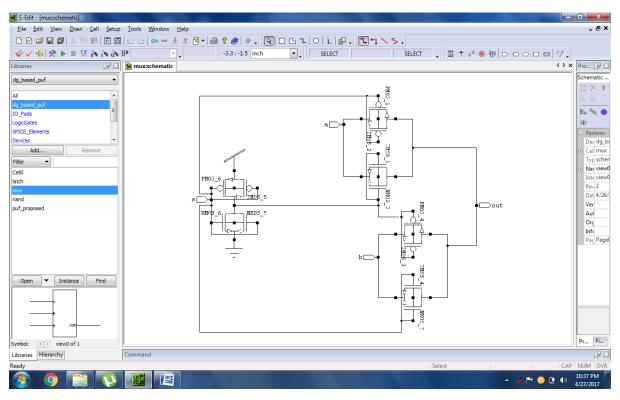

| 13   | Metastable state arbiter                                        | 29   |

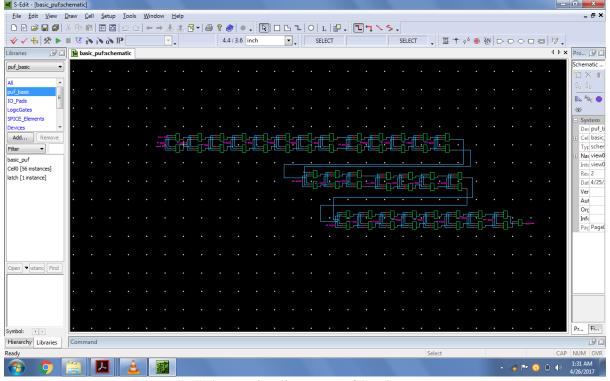

| 14   | Schematic diagram of basi mux puf                               | 30   |

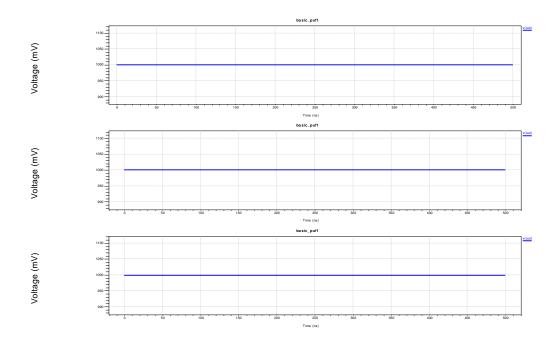

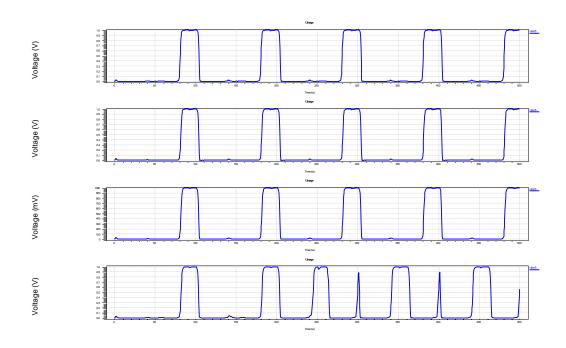

| 15   | Analog simulation output performed at 0°C, 27°CAND 100°C        | 31   |

| 16   | Schematic diagram of 14 stage feed forward mux PUF              | 32   |

| 17   | Analog simulation output performed at 0°C, 10°C, 25°C and 35°C  | 33   |

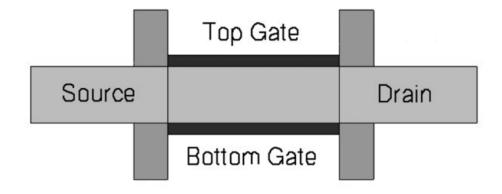

| 18   | Device structure of double gate MOSFET                          | 33   |

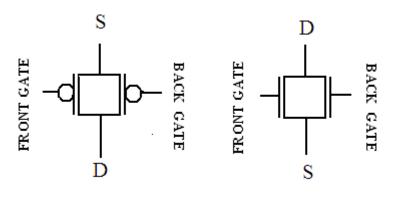

| 19   | Circuit symbols of DG-PMOS and DG-NMOS                          | 34   |

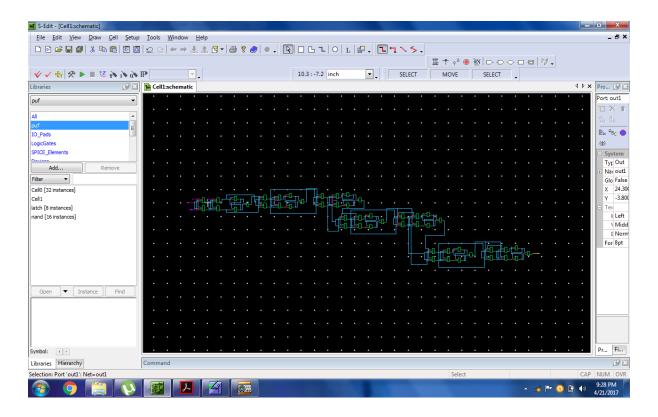

| 20   | Schematic of arbiter circuit using DG MOSFET                    | 35   |

| 21   | Schematic representation of 2:1 mux using DG MOSFET             | 35   |

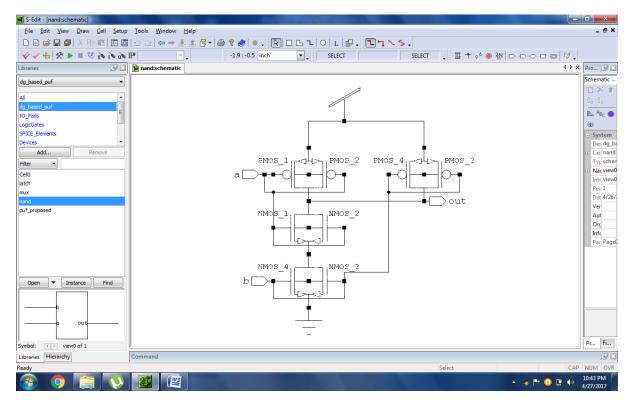

| 22   | Schematic representation of NAND gate using DG MOSFET           | 36   |

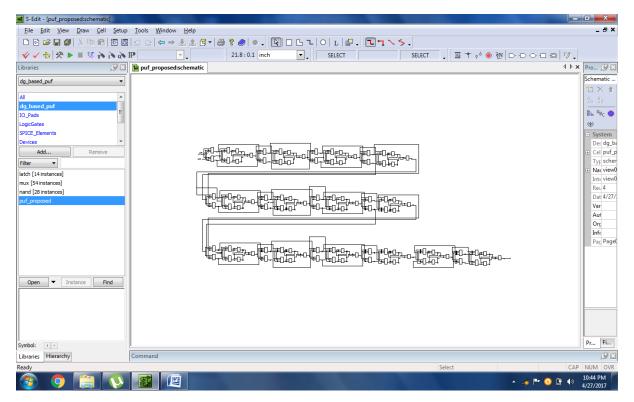

| 23   | Schematic diagram of 14 stage feed forward PUF using DG         | 37   |

|      | MOSFET                                                          |      |

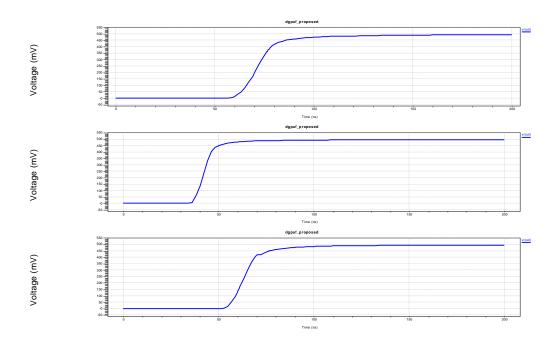

| 24   | Analog simulation output performed at -5°C, 0°C, 25°C           | 37   |

# LISTS OF TABLES

| TABLE  | TABLE CAPTION                      | PAGE   |

|--------|------------------------------------|--------|

| NUMBER |                                    | NUMBER |

| 1      | SIMPLE LINEAR MUX PUF              | 39     |

| 2      | COMPARISION OF SIMPLE FEED-FORWARD | 39     |

|        | MUX PUF AND FEED-FORWARD MUX PUF   |        |

|        | USING DG MTCMOS                    |        |

|        |                                    |        |

#### **ABSTRACT**

Physical Unclonable Function (PUF) is a physical entity that provides secret key or fingerprints in silicon circuits by exploiting the uncontrollable randomness during its manufacturing randomness. Its provides a hardware unique signature or identification. Its properties of uniqueness comes from its unpredictable way of mapping challenges to responses, even if it was manufactured with the same process. Previous work has mainly focused on novel structures for non-FPGA reconfigurable silicon PUFs which does not need any special fabrication method and which can overcome the limitations of FPGA-based simulations. Their performance were quantified by the inter-chip variations, intra-chip variations and reconfigurability tests to meet practical application needs. This paper presents a novel approach of designing a low power non-FPGA feed-forward PUF using double gate MOSFET and also to analysed its parameters like reliability and power.

#### **TOPIC APPROVAL PERFORMA**

School of Electronics and Electrical Engineering

**Program:** P175::M.Tech. (Electronics and Communication Engineering) [Full Time]

COURSE CODE: ECE521 REGULAR/BACKLOG: Regular GROUP NUMBER: EEERGD0216

**Supervisor Name**: Jyotirmoy Pathak **UID**: 16082 **Designation**: Assistant Professor

Qualification: Research Experience:

| SR.NO. | NAME OF STUDENT      | REGISTRATION NO | ватсн | SECTION | CONTACT NUMBER |

|--------|----------------------|-----------------|-------|---------|----------------|

| 1      | Konsam Jemson Meitei | 11508694        | 2015  | E1514   | 9915122907     |

SPECIALIZATION AREA: VLSI Design Supervisor Signature:

**PROPOSED TOPIC**: Design of a Physically Unclonable Function for generation of random sequence for hardware security.

| Qualitative Assessment of Proposed Topic by PAC |                                                                                                                                                                                           |                    |  |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|

| Sr.No.                                          | Parameter                                                                                                                                                                                 | Rating (out of 10) |  |

| 1                                               | Project Novelty: Potential of the project to create new knowledge                                                                                                                         | 7.67               |  |

| 2                                               | Project Feasibility: Project can be timely carried out in-house with low-cost and available resources in the University by the students.                                                  | 8.00               |  |

| 3                                               | Project Academic Inputs: Project topic is relevant and makes extensive use of academic inputs in UG program and serves as a culminating effort for core study area of the degree program. | 8.00               |  |

| 4                                               | Project Supervision: Project supervisor's is technically competent to guide students, resolve any issues, and impart necessary skills.                                                    | 8.00               |  |

| 5                                               | Social Applicability: Project work intends to solve a practical problem.                                                                                                                  | 8.00               |  |

| 6                                               | Future Scope: Project has potential to become basis of future research work, publication or patent.                                                                                       | 8.00               |  |

| PAC Committee Members                   |            |                        |  |  |

|-----------------------------------------|------------|------------------------|--|--|

| PAC Member 1 Name: Anshul Mahajan       | UID: 11495 | Recommended (Y/N): Yes |  |  |

| PAC Member 2 Name: Dushyant Kumar Singh | UID: 13367 | Recommended (Y/N): NA  |  |  |

| PAC Member 3 Name: Cherry Bhargava      | UID: 12047 | Recommended (Y/N): Yes |  |  |

| PAC Member 4 Name: Anshul Mahajan       | UID: 11495 | Recommended (Y/N): Yes |  |  |

| DAA Nominee Name: Manie Kansal          | UID: 15692 | Recommended (Y/N): NA  |  |  |

Final Topic Approved by PAC: Design of a Physically Unclonable Function for generation of random sequence for hardware security.

Overall Remarks: Approved

PAC CHAIRPERSON Name: 11211::Prof. Bhupinder Verma Approval Date: 08 Oct 2016

## **CHAPTER 1**

### INTRODUCTION

#### 1.1 HISTORICAL OVERVIEW

Reference of exploiting the hardware properties of systems for verification purposes dates back to the early 1980's. An authentication scheme for memory cards was provided by Naccache and Fremanteau in 1992. By the early 2000's the terem physical one way function(POWF) and physical unclonable function were composed. To be more specific in 2001 and 2002 respectively. PUF gained its attention in the smartcard market from 2010 till 2013 as a unique way of providing "silicon unique identity".

#### 1.2 ATTACKS ON IC CIRCUIT

The advancement of semiconductor device has altered the world and empowered numerous incredible applications. For instance, the cell phones and tablets have now turned out to be so predominantly utilized as a part of online instalment, web program, gaming, individual information aide and individual human services than the standard elements of its antecedent component telephones and PCs. The every inescapable impact of electronic gadgets can be felt in each part of our present life. The propeller behind this ever quicker reestablishment of electronic devices is the interminable increment in gadget coordination thickness is the increase in device integration density (the quantity of gadgets per unit range in a coordinated circuit (IC)) anticipated by the Moore's Law in the "silicon era".

The significantly increase in the intellectual and authoritative complexity of IC configuration is driving the semiconductor enterprises towards a vertical specialization where different phases of IC configuration are broken down, outsourced to outside firms also, moved crosswise over national limits that have the implied information and skill. For the most part, the design of an IC is encouraged by the following outside administration and resource providers:

• Electronic design automation(EDA) organizations give the intense and complicated programming instruments that guide the design and confirmation of present day ICs.

- Semiconductor foundries furnish the IC design with the electronic gadget models and the administrations to create and fabricate the chips with their own resource so that the creators can profit by the lower per capital cost of chip assembling and center their innovative work exertion on the item works required by the end markets.

- Cell library engineers and Intellectual property (IP) center sellers give the IP blocks, for example, the standard and particular cell libraries, CPU centers, memory and controllers that have been completely tried and streamlined to convey the coveted execution. These IP block help to decrease the outline time, enhance the quality and yield, and meet the brief timeframe to-market window for the advancement of the unpredictable framework on-chip.

- The dynamic interest of the different outside specialists in the outline and assembling stream of an IC has made the whole IC store network exceptionally defenseless to chip corruption and subversion. Thus modern ICs have been under various threats in the design and fabrication procedure. Some of the mainstream examples of such threats in the different stages of IC design procedures are given below:

- Malignant logics (hardware Trojan) insertion: The original design can be altered in the deaign stage or amid the manufacture stage, if the enemy picks up the entrance to it. The equipment Trojans may conceivably release the delicate information, lessen the IC dependability or make a framework come up short at a basic time. The Trojans for the most part don't change the first function of the circuit and furthermore very little in size, which can barely be recognized by the parametric tests performed by the real users

- IP theft: The hacker can break down the plan or take the IP. The stolen IP can be unlawfully utilized or replicated to mass create or fake the plan. After effects of the investigation on the stolen IP can likewise be utilized by plotting aggressors to help in future programming or equipment construction.

- Reverse engineering: High-class ehackers can spend days getting to the chip surface straightforwardly and watch the IC layout layer by layer with the help assistance of the current equipments. These intrusive attack can help the hackers comprehend the inner components and structures of the outline. With this data, the hackers can undoubtedly fake the plan, and embed pernicious equipment Trojan to sidestep identification or take the sensitive information stored in the IC.

- Fault injection: The equipment Trojans or the secondary DOOR implanted in an IC can be activated by presenting it to abnormal working conditions (concentrated light pulse, radiation, and so forth.).

- Side-channel attack: This attack depends on data picked up from the physical usage of a crypto-framework, as opposed to by brutal constrain or through misusing hypothetical shortcomings in the cryptographic calculations. The side-channels of a gadget can be the delay, control utilization or the electronic attractive radiation.

The fast developing complexity of ICs and the dependence on outsourcing of schedule and the less important value included in the IC value chain have made guaranteeing the IC trustworthiness more troublesome than any other time in recent memory. In the mean time, present day and rising innovations, for example, filtering optical microscopy, light incited voltage shift and machine learning, are likewise making it simpler to attack an IC after its organization.

As opposed to the approaching CMOS gadget scaling anticipated many years ago, technology scaling ends up being a key empowering agent of hardware cryptography. Security primitives have been incorporated with lightweight applications that would have been unbelievable only 10 years back. In 2005, the Defence Advanced Research Projects Agency (DARPA) starts the Trust in ICs program. From that point on, persistent developments have been brought into this incipient field. With Internet of Things (IoT) conceived to wind up plainly an extreme driver for the following development period of semiconductor industry, Radio frequency identification (RFID) and a few other lightweight electronic labelling advancements will benefit themselves most in this universal figuring upheaval of progress network of gadgets, frameworks and administrations. unfortunately, the impression and control spending plan have seriously constrained the quality of cryptographic calculation implementable on a RFID

or other intelligent labels, and the mystery information put away in these lightweight gadgets can be effortlessly perused or figured out and duplicated.

Critics are worried that the image of IoT will make digital attack an inexorably annihilating physical (instead of virtual) attack. Another reason that makes hardware security an appealing examination zone is that it is the last line of protection. Software security has been tormented by security issues for a long time, and hardware has for quite some time been touted as a place of boon for security insurance. All in all, hardware oriented security has the accompanying two special focal points over the software based security:

- Minimal operation level: The operation of the hardware is situated in the least level.

Hardware security primitives can be quicker, exceptionally application-particular

what's more, more productive than the software instruments. Moreover, programming

security measures can do little against some capable equipment assaults, for instance,

micro probing.

- Modifiability: The capacity to effectively change or refresh the product is a ambiguous tool. On one hand, this can help the developers settle and fix known software bugs rapidly. Then again, a similar adaptability can likewise be misused by the aggressors to introduce infections or Trojans in the working framework. Interestingly, the inserted secure equipment circuits in a chip can't be effectively altered after the IC deployment.

Nevertheless, without adequate protection, any hardware can be as vulnerable as the software. Any successful attacks to a hardware integrated system can cause greater disruptions, leading to heavier economic losses and may even endanger human lives. Given the tight coupling between information and communication technologies and physical systems today, the new security concerns of disastrous hardware attacks are requiring a rethinking and re-examination of the commonly used objectives and methods.

#### 1.3 HARDWARE SECURITY OR PUF

PUFs is a hardware peripheral that is represented in a hardware system and is anything but difficult to assess however difficult to anticipate. More than that, an exclusive PUF hardware or gadget have to be anything but difficult to build however in every way that really matters hard to duplicate, even given the right gathering process that made it. The name PUF may be small beguiling as few of them are might still be duplicated, and almost all of them are clamorous and in this way don't fulfill the necessities of a function.

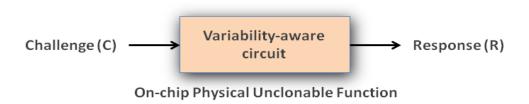

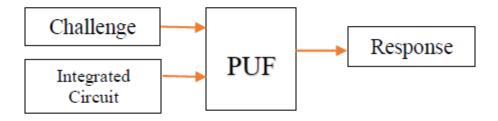

Now a days, PUFs are realised in IC and are regularly used as a piece of components with high security necessities. It is a input to output framework in which the mapping between a input and the output is subjected to the variation in properties of a physical material. For example, an on-chip PUF is a chip-special test reaction framework misusing the manufacturing procedure assortment inside IC. The association among an input and its output is directed by confounding, quantifiable assortment in method of reasoning and adjoining in an IC. A PUF is essentially a fluctuation mindful circuit which can perceive the mismatch in circuit parts made by collecting process variety.

It is assumed that the disorder cannot be cloned or reproduced exactly, not even by the original manufacturer of the PUF with exact known feature. This concludes that each and every PUF have a different identification like fingerprint as of human being. The PUF is embedded in physical device in an inseparable way for secure identification of the device to be identified. Due to the fractious random component, PUFs are not hard to measure but hard to copy, conclude or recreate practically. Moreover, they are impossible to mount an invasive attack which will copy the classified data without interrupting physical unpredictability. Because of such advantages, in cryptographic application, PUFs can be applied for generation of efficient and reliable secret key; and enables low cost authentication of ICs (Integrated Circuits).

Fig1: General representation of PUF

#### 1.4 Types of Silicon PUF

In the course of the most recent few years, numerous number of PUFs have been effectively proposed for the security applications because of the promising properties of physical unclonability, alter proof and little equipment overhead. This survey centers on the most well known silicon based PUFs, as they are easy to be coordinated with the standard CMOS process. generally, there are two essential applications of PUFs: authentication and secure key generation. In view of the two applications, the PUFs are extensively sorted as "strong PUFs" and "weak PUFs". Strong PUFs can be focused for authentication, while weak PUFs are more reasonable for the secret key generation.

Prior to the examination of the classifications and operations of the PUFs, the terminologies for PUF are presented. The input and output of PUFS circuits are ordinarily called as the challenge and response. A given challenge and its respectiveresponse are termed as challenge response pair(CRP). Actually, the crucial contrast between the WEAK and solid PUFs lies in the connection between their challenge and response.

#### 1.4.1 Strong PUF

Strong PUFs are cluttered physical systems with a complex challenge-response behaviour characterized by a substantial challenge-response space. It is virtually impossible to clone a strong with the same CRPs as that of the original PUF. And furthermore, measuring or determining all the specific CRPs for a strong PUFs is impossible for an attacker within a limited time. The main examples for the strong PUFs are: the arbiter delay PUF and the ring oscillator (RO) PUF.

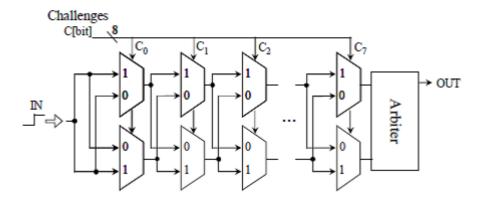

#### • Arbiter PUF

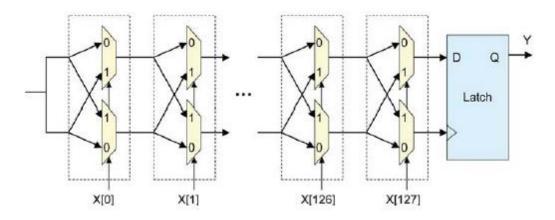

In the arbiter PUF, a symmetric circuit is taken a race condition is establish by giving different challenges. Fig. below shows the implementation of the basic arbiter PUF. It consists of a string of switches, of which each switch is controlled by one bit of the challenge. When an input is given, at the beginning the rising edge is split into the two multiplexors. Different path are being selected by the different input challenges. Because of the variation in the manufacturing process in the gate delay of each stage one edge will arrive at the latch faster than the other even though the two channel or the selected two lines are laid out in the same fashion. The arbiter circuit or here latch will processed whichever edge arrives firt of

the two string thereby producing the response. So it can be concluded that the response is determined by the challenge bits

It can be noticed due to the metastability of the arbiter makes the PUFs prone to environmental noises. Furthermore, the digital delay in the basic arbiter PUF has to be considered. In other words, the delay of each array of switch blocks is the sum of the delay in each stages. This can makes the arbiter PUF susceptible to the model-building attacks. By observing a number of CRPs, one might be able to build a mathematical model that predicts the response of future challenge that might be of high precision. There are a couple of adjusted architecture proposed which might overcome model-building, by presenting nonlinearity in the delays and by limiting the I/Os to the PUF.

**Figure 2 :** The schematic of arbiter PUF

#### • (RO-PUF)- Ring Oscillator PUF

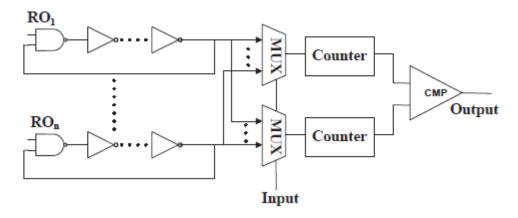

The simple RO PUFs architecture comprises of 2N-1 multiplexors, dual counters, single comparator and N similar ring oscillators, as shown in figure. An odd number of inverters in a feedback loop comprises each ROs. The delay in the inverter array in each RO differs Due to the inter- and intra-chip process variations and environmental variability, which might make a deviation of the oscillation frequencies between any two ROs. The data select lines of the two multiplexors is fed with a 2log2N-bit challenge to elect a pair of ROs. The output frequencies of the elected ROs are then used to clock two similar counters. A comparator is then connected with the two counter outputs. The output bit of the PUF which is the counter output, is either 0 or 1 depending on which oscillator has reached the same pre-loaded count value earlier. So, the difference between the oscillation frequencies of any RO pair, the output r bit of the PUF is more reliable. RO PUFs have more physically strong to layout differences.

Figure 3: Simple ring oscillator puf architecture

#### 1.4.2 Weak PUF

Rather than the solid PUFs, the weak PUFs may have less CRPs. Weak PUFs can normally viewed as a unique type of memory, yet they are more strong to the intrusive attack than the non-volatile memory like EEPROM. The most mentioned weak PUFs are the memory-based PUFs: SRAM PUF, latch PUF and butterfly PUF.

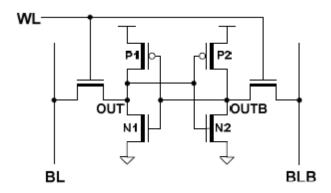

#### SRAM PUF

SRAM is a notable weak PUF structure that endeavors the positive feedback loop in a SRAM cell. As shown in the figure below it has two stable states: either "1" or '0'. The positive feedback in the cell compels it into one of these two states. When it enters either state, it averts the cell from traveling out of this state accidentally. In reference to the format, the double cross-coupled inverters are well proportioned as shown in the figure. It ought to be in the meta-stable state amid the charging stage. Be that as it may, in the genuine implementation, the circuit in the cross-coupled inverters are confounded due to the assembling process varieties. One of the feedback is somewhat more stronger than the other. The positive feedback of the cross-coupled inverters will be opened up by the mismatches

and will in the long run produce either a logic 1 or a logic 0. Expecting irregular hardware variations, each SRAM cell may likewise create either logic 1 or logic 0 randomly with an equivalent probability of 50%. This makes the binary response string read out from the SRAM string one of a kind, arbitrary and non-traceable. Be that as it may, arbitrary noise, e.g., thermal noise and shot noise, can likewise trigger the positive feedback loop when it is in the meta-stable state, which makes the response of a SRAM PUF unstable. It is noticed that the last state relies on upon the contrast between two feedback loops. The estimation is taken differentially so that the impacts of common mode noise, for example, temperature, power supply vacillations, and common mode process variation will be reduced.

Figure 4: simple structure of SRAM cell

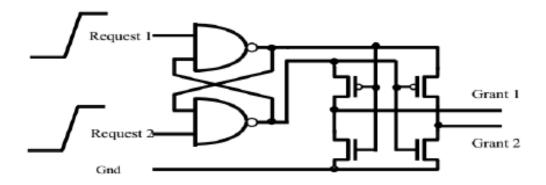

#### • Latch PUF

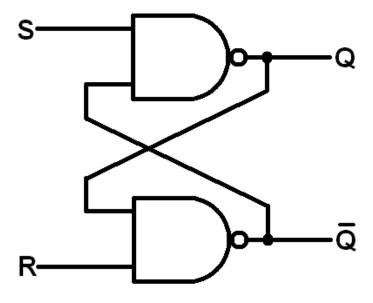

Not every ICs have an SRAM array and it is difficult to just reset the SRAM subsequent after powering up for a few design. thus, the utilization of the SRAM PUFs is limited. Latch PUF was proposed to swamped the shortcomes of SRAM PUF. The logical structure of a latch PUF cell is shown in the figure below. Rather than cross-coupling two inverters in a SRAM cell, two NOR gates are cross-coupled. Like the SRAM PUF, by declaring a reset signal, this latch becomes uncertain and after that joins to a steady state again relying upon the internal difference between the electronic segments.

Figure 5: the logical structure of the latch puf cell

#### 1.5 PUF APPLICATIONS IN HARDWARE SECURITY

Silicon PUFs are for the mostly intended for two applications in hardware security: device authentication and identification, and key generation for encryption units.

#### 1.5.1 AUTHENTICATION AND IDENTIFICATION

PUF can be utilized to authenticate or confirm each ICs without utilizing costly cryptographic modules. This kind of validation is extremely helpful for resource obliged RFIDs where cryptographic operations are too costly as far as silicon range and power utilization. The validation or authentication with PUF utilizes a challenge-response protocol. After producing a gadget, the client of the PUF needs to keep the CRPs of its PUF in an enlistment stage. These CRPs are stored in a secure database. At the point when the ID or the validation is questioned, the challenges chosen from the enlistment stage are connected with the exact PUF. Since each PUF gives a novel reaction and its output must be calculated if one among them has the physical gadget, the confirmation is viewed as effective when the response matches (or sufficiently close to) the recorded one. To maintain a strategic distance from replay (spying) assaults, the used challenge ought not be used again. Consequently, it is greatly helpful to have a (strong) PUF that can support countless CRPs. This validation and authentication procedure can likewise be utilized by IC merchants to prevent forging attacks.

### 1.5.2 Key Generation

The security of a cryptographic framework depends not on the mystery of its calculation but rather in the mystery of its encryption and decryption keys. Generally, the keys are put away in non-volatile memory of a device which are powerless to obtrusive attack. Be that as it may, if a PUF's reaction to a special challenge (or some subsidiary of its response) is utilized as an encryption key, then the key is physically inserted in the device structure instead of put away in memory. Any intrusive or semi-obtrusive attack will definitely demolish the physical structure. So, the first information or the original data will never again be the same after the attack. It is also noticed that the response of a given PUF can't be utilized specifically as a key in cryptographic calculations, since its response are probably going to be distinctive in every assessment notwithstanding for the same challenge, and the raw response may not be

really arbitrary. These constraints can be overcome by joining extra post-processing modules, for example, the error correction coder (ECC) or the fuzzy extractor. There are two stages in the error correction process: initialization and re-generation. In the initialization step, an error disorder is registered when the test is connected. This disorder is utilized later amid regenerated to rectify any errors that may have occured in the PUF response. The revised PUF response is then taken through a hash function to produce the unique key.

The alluring security applications for PUFs have likewise attracted the consideration industry by Verayo and Intrinsic ID. Verayo gives the PUF item as an IP to be authorized for RFID, ASIC and FPGA applications. Intrinsic ID offers secure key stockpiling solutions for protecting semiconductor items from cloning and reverse engineering

### 1.6 PUF Qualities and Metrics

There are three most important properties to consider while examining the quality of a PUF design, which are uniqueness, reliability and unpredictability. They are briefly explained as in the following paragraph:

#### • **RELAIBILITY:**

Reliability defines how balance are the CRPs of the given PUF against different operating conditions. The dynamic operating conditions can be taken as the variations in temperature, supply voltage and ambient noise. The intra chip deviation is the unit of reliability of PUFs that is controlled by correlating the analog impression of the PUF as for similar test under various environmental conditions or temperature situation. Here, we consider  $P_{intra}$  as the probability that a response of 1's at some point of time may flip when applied with a randomly selected challenge for a multiple number of times. Thus,  $P_{intra}$  may be utilized to serve as the intra chip dissimilarity for the whole response. Difference between the intravariation response forms the hamming distance which is used for variation in MUX-based PUFs. The  $P_{intra}$  or the hamming distance (HD) average is defined as:

$$E(HD_{intra}) = Pintra = E(\frac{1}{m}\sum_{i=1}^{m} \frac{HD(R,R')}{L} \times 100\%)$$

Where, m= the number of HD comparisons

,R and R'= two measurements of the PUF output under different environmental state

Now with this in hand reliability of a PUF system can be defined as:

Reliability =

$$1-P_{intra}$$

### • Uniqueness:

The inter chip abnormality is the measure of rareness that is assessed by looking at the hamming distance between two analog impression which are created from the same input and arrange information from various chips. We can characterize P<sub>inter</sub> as the output created by a similar test for diverse PUF are distinctive. Since rareness is the unit for P<sub>inter</sub> execution, almost all chip blends ought to be studied. Uniqueness can be measured by the medocre interchip Hamming Distance of the output produced by different PUFs.

Thus, the average Pinter of Z STAGES PUFs can be measured as:

E(Pinter) = Pinter = E(

$$\frac{2}{Z(Z-1)}\sum_{I=1}^{K-1}\sum_{J=i+1}^{Z}\frac{E(R(i),R(j))}{L} \times 100\%$$

)

#### • RANDOMNESS:

A PUFs may be utilized to stock clasified and coded keys, PUF response ought to be unusual/irregular with various known CRPs so as to guarantee that the classified information stays safe. A few measures of unconventionality have been used in the writing. As high accuracy more than 90% can be accomplished through machining learning attacks on direct PUFs, for example, Arbiter PUFs, one specially appointed measure of eccentrics is by deciding how appropriate machine learning assaults may be utilized as display CRPs of PUF. A MUX PUF is relied upon in a perfect world to deliver neutral 0's and 1's. Irregularity in

the response represents the capacity of the PUF to yield 0's and 1's output with same probability. One estimation of of irregularity may be inclined as::

Randomness =

$$1 - |2 \times (R = 1) - 1|$$

When P(R = 1) is all the nearer to 0.5 it shows better randomness.

#### **CHAPTER 2**

#### LITERATURE REVIEW

The chapter is focused on review of literature of different fast adder designs. To conclude this topic many journals, articles, conference papers have been studied. Some of them are described as below.

# • S. V. SANDEEPAVVARU, CHEN ZHOU, SAROJSATAPATHY, YINGJIE LAO, C. H. KIM, K. K. PARHI (2016):

Evaluating delay differences of each phase in a standard MUX-based physical unclonable capacity (PUF). Test information gathered from PUFs created utilizing 32 nm processes are utilized to prepare a linear model. The delay differences of the phase are directly corresponding to the model parameters. These parameters are prepared by utilizing an east mean square (LMS) adaptive algorithm. The correctness of the response utilizing the proposed model is around 97.5% and 99.5% for two dissimilar PUFs. Second, the PUF is likewise displayed by a perceptron. The perceptron has just about 100% classification correctness. These demonstrate shows that the perceptron model parameters are scaled versions of the model derived by the LMS algorithm. So, the delays differences can be evaluated from the perceptron demonstrate where the scaling component is registered by looking at the models of the LMS calculation and the perceptron. Because of the defer contrasts is test autonomous, these parameters can be put away on the server. So that, this will empower the server to issue random challenges whose responses require not be put away. Accordingly this examination demonstrates affirms that the delay differences of all phases of the PUFs on a similar chip have a place with the same Gaussian probability density function.

#### • YINGJIE LAO, K. K. PARHI:

PUFs are original device primitives that hold the unique data in silicon circuits by abusing uncontrollable arbitrariness because of assembling procedure varieties. In this case, it has as of now been demonstrated that a rearrangeable architecture of PUF won't just empower

PUFs to meet useful application needs, additionally can enhance the reliability quality and insurance of PUF-based verification or distinguishing system. Here, we proposed a few original structures of non-FPGA reconfigurable silicon PUFs, which needn't bother with any exceptional fabrication means and can conquer the confinements and disadvantages of FPGA-based methods. Their achievement are evaluated by the Pinter variation, Pinter variation and reconstructable tests. The delay-based silicon PUFs is constantly considered a stable input-output behavior and the PUF create equal or flaw tolerated output. These examination show that these PUF construction are powerless against a few attack techniques together with emulation, rerun, and reverse engineering. Also, updatable cryptographic keys are exceptionally fascinating in a few applications. Accordingly, a dynamic PUF which can modify the CRP each time the information is modified to keep the secret data spilled out is desired.

### • T.Addabbo, A.Fort, M.Mugnaini, S.Rocchi, V.Vignoli (2012):

Silicon PUFs are innovative circuit primitives whose computerized yield altogether depend on upon the produce irregular physical assortments introduced in the midst of the fabricate strategy of coordinated circuits. The measurable portrayal of a basic PUF module depends on ring oscillators to actualize challenge-reaction FPGA validation. The test bits assume a part in changing the time flow required in the chip reaction estimation. The exploratory outcomes likewise demonstrate that by considering legitimate qualities for the test bits the repeatability mistake rate is littler than 5% at given chip temperature and supply voltage, getting a PUF module working with 4 challenge bits while showing a high affectability to the fabricate irregular physical varieties. The outcomes are practically identical to that one's exhibited for different arrangements, with a constrained utilization of equipment assets. For the most part, the arrangements misuse the wild wire deferral and voltage exchange attributes of straightforward computerized circuit primitives.

#### • MUSLIM MUSTAPA, MOHAMMED NIAMAT (2014):

Physical Unclonable Function (PUF) is a function that can't be demonstrated in light of the fact that it uses the random procedure variations from a silicon chip to produce a special piece stream of '1's and '0's (reaction bits) which can be utilized for verification/ authentication and cryptography applications. Furthermore, PUF is profoundly depend upon process varieties, the response bits created are represented by the efficient/ systematic procedure variation rather than the stochastic procedure variation, which will diminish the randomness in the response bits. The novel Random Patch Mixer (RPM) method is to reject the systematic variation effect on the response bits produced. RPM method is connected on information or information acquired from 29 Spartan 3E FPGA chips. These exhibit that the RPM technique has successfully ousted the orderly variety impact on the reaction bits created from the ROPUF on FPGA. These also exhibited that the reactions created by applying the RPM Technique passed the National Institute of Standards and Technology NIST measurable test for irregularity. ROPUF presents the time of '1's and '0's bit stream in view of the technique minor departure from a silicon chip. The method variety is a sporadic technique that occurs amid silicon chip creation brought on by the mistake in the manufacture methodology. The incorrectness brought on a little defer that is not useful operation of the circuit on a silicon chip. The ROPUF intensifies this little postponement through the recurrence era from a Ring Oscillator (RO). The qualifications in the frequencies delivered by the ROs will be used to arbitrary paired piece stream, which then can be affirmation/confirmation or the cryptography encryption and interpreting key. The irregular double piece stream is known as a reaction. Each reaction is made by a given test from the customer or client. Test is a double piece stream that will choose the RO combine examination. Each test will convey a novel or one of a kind reaction. As ROPUF uses the technique assortments to make the secured reaction bits, there is so far a shortcoming exist since the think assortment governed the general system assortments. So it is basic to dismiss the consider assortment effect and augmentation the genuine irregularity on the reaction era in ROPUF.

#### • TENGXU, DONGFANG LI, AND MIODRAGPOTKONJAK:

PUFs are difficult to anticipate and difficult to imitate. Though, the utilization analytical models are to alterably describe the delay based PUFs, and utilize it as a starting stage to copy a delay-based PUF. The fundamental thought is that as for any input CA of a delay-based PUF A, there is a strong risk of finding a paired input CB. At the point when apply CB to another delay-based PUF B, it can deliver same output from applying CA on PUF A. These model outcomes demonstrate over 99% accuracy for the PUF response expectation utilizing characterization and 96% accuracy utilizing copying. Additionally tested the feasibility on the Xilinx Spartan-6 Field Programmable Gate Array (FPGA).

#### YINGJIE LAO, K. K. PARHI:

PUFs has the ability hold classified keys in ICs by abusing the uncontrollable unpredictability because of assembling procedure variations. These PUFs can be utilized for verification or authentication of devicws and for key generation in security applications. This analysis presents a thorough statistical examination of different sorts of multiplexer-based (MUX-based) PUFs including the original MUX PUF, the feed forward MUX PUFs, the altered feed-forward MUX PUFs, and multiplexer-demultiplexer (MUX/DeMUX) PUF.

The altered feed-forward MUX PUF structure is new structure and three categories of feed-forward PUFs are studied in the paper. Those are listed below:

- Feed forward

- · Feed forward cascade and

- Feed forward separate

The execution examination assesses between chip and intra-chip assortments as a component of the amount of stages; the system variety vacillation, the ecological clamor difference, and the referee skew for various PUFs. Three distinct estimations of execution are also introduced and analyzed in this paper, which consolidate dependability, uniqueness, and irregularity. A PUF will be more tried and true if there is less intra-chip variety. A PUF is more uncommon if the entomb chip assortment is more like half. A PUF is more arbitrary if its reaction bit is 0 or 1 with comparable likelihood. These factual examination shows that the intra-chip variety is less subject to the amount of stages, N, if N is more noteworthy than ten. Yet, the between

chip variety is dependent on N if N is under 100. It is exhibited that the sustain forward PUFs have higher intra-chip variety than MUX PUFs, regardless, the nourish forward PUFs have fundamentally bring down intra-chip variety than the bolster forward PUFs. This likewise exhibited the changed - forward course MUX PUF has the best peculiarity and capriciousness, though there is greater unwavering quality in the primary MUX. The examination presented in this paper can be used by the initiator to pick PUF has a legitimate PUF in base on the application's need. This expels the require for creation and testing of various PUFs for picking a reasonable PUF.

### • MIAOQING HUANG AND SHIMING LI

For hardware-oriented security point of view, Physically unclonable capacities (PUFs) have been a hot research point for a long time. Certain test has been given to the PUF as input, it creates a relating reaction, which can be dealt with as an extraordinary unique finger impression or mark for verification or authentication reason. Here, a delay-based PUF configuration including multiplexers in light of FPGA is introduced. Because of the characteristic contrast of the switching latencies of two chained multiplexers, a positive pulse might be delivered at the outcome of the downstream multiplexer. This pulse can be utilized to set the yield of a D flip-flop to '1'. Promote, it is projected to specifically fuse challenge bits into the primitive PUF configuration to bring another layer of arbitrariness for the reaction. Assessment comes about on different devices and under different working temperatures exhibit the applicability of the proposed PUF outline.

# • DAIHYUN LIM, JAE W. LEE, BLAISEGASSEND, G. EDWARD SUH, MARTEN VAN DIJK, AND SRINIVASDEVADAS:

Modern cryptographic protocols depend on the commence that lone approved members can get secret keys and access to data frameworks or information systems. In any case, different sorts of altering methodologies have been considered to concentrate mystery keys from unforeseen get to frameworks, for instance, smartcards and ATMs. Mediator based physical unclonable limits (PUFs) manhandle the factual defer assortment of wires and transistors across over circuits (ICs) in collecting methodology to manufacture unclonable one of a kind

or mystery keys. We made judge based PUFs in custom silicon and investigated the recognizing verification limit, consistency, and security of this arrangement.

Exploratory results and hypothetical audits delineate that a sufficient measure of bury chip exists to engage each IC to be perceived securely and dependably over a down to earth extent of ecological assortments, for instance, temperature and power supply voltage. It exhibit that referee based PUFs are possible and suitable to work, for instance, scratch cards that ought to be impervious to physical assaults.

# • KOTA FRUHASHI, MITSURU SHIOZAKI, AKITAKA FUKUSHIMA, TAKAHIKO.(2011):

Physical Unclonable Functions (PUFs) is projected as to deliver tamper-resistant device or make exclusive identifications of the protected frameworks or system. The regular essential arbiter-PUF was created with 0.18µm CMOS method, and the uniqueness of produced multibit reactions was estimated. The uniqueness is insufficient than anticipated on the grounds that a few of multi-bit reactions are never created. In this review, we recommend a novel arbiter-PUF using a RG-DTM (Response production as indicated by Delay Time Measurement) plot. The uniqueness is assessed by the standard deviation of the Hamming Distance dissemination between created 256-bitresponses. The standard deviation on the proposed PUFs is greatly enhanced to 8.45 from 31 on the traditional PUFs.

#### • DOMENIC FORTE AND ANKURSRIVASTAVA. (2013):

Silicon physically unclonable capacities (PUFs) are circuits that endeavor present day producing varieties to generate unique marks for chip authentication and cryptographic key era. Existing exploration has concentrated on improving PUF quality at structural or configuration levels, yet has unnoticed opportunities accessible amid fabrication, which is the source of systematic and random variation in (ICs)/PUFs. For typical ICs(where security is not a worry), optical proximity correction(OPC) is utilized to smother both these types of variations. Still, a few earlier works have demonstrated that lone systematic variations adversely affect PUF quality and arbitrary variations are helpful for PUFs. In this paper, we propose two PUF-aware OPC cost capacities: 1) P-OPC produces a PUF lithography mask

that expands all varieties in PUF circuitry (the inverse of state-of-the-workmanship OPC), and 2) SVC-OPC creates veil patterns that diminish the systematic variation found in PUFs for improved quality. Simulation comes about for ring oscillator (RO) PUFs illustrate that the proposed techniques can enhance PUF signature quality compares to current state-of-the-art OPC.

# • J. W. LEE, DAIHYUN LIM, BLAISEGASSEND, G. EDWARD SUH, MARTEN VAN DIJK, SRINIVASDEVADAS

This paper portrays a procedure that endeavors the statistical delay varieties of wires and transistors crosswise over ICs to construct a mystery key one of a kind to every IC. To investigate its practicality: we created a hopeful circuit to produce a reaction in light of its postpone qualities. We demonstrate that there exists enough defer variety crosswise over ICs actualizing the proposed circuit to distinguish singular ICs. Promote, the circuit capacities dependably over a commonsense scope of natural variety, for example, temperature and voltage.

# • BLAISEGASSEND, DWAINE CLARKE, MARTEN VAN DIJKY AND SRINIVASDEVADAS(2002)

Also present the thought of a Physical Random Function(PUF). A complex coordinated circuit can be viewed as a silicon PUF and depict a strategy to identify and verify individual integrated circuits (ICs). We show a few conceivable circuit acknowledge of different PUFs. These circuits have been executed in item Field Programmable Gate Arrays (FPGAs). We present tests which demonstrate that strong confirmation of individual FPGAs can be performed even inside seeing tremendous biological varieties. We depict how secure shrewd cards can be created, and furthermore quickly portray how PUFs can be associated with authorizing and affirmation applications.

# • JAE W. LEE, DAIHYUN LIM, BLAISEGASSEND, G. EDWARD SUH; MARTEN VAN DIJK, AND SRINIVASDEVADAS(2004):

This paper depicts a strategy that attempts the factual postpone varieties of wires and transistors across over ICs to collect a mystery key uncommon to each IC. To explore its reasonableness: we made a competitor circuit to make a reaction in view of its postpone qualities. We exhibit that there exists enough defer variety crosswise over ICs completing the proposed circuit to perceive particular ICs. The circuit capacities dependably over a handy scope of natural variety, for example, temperature and voltage.

# • MEHRDAD MAJZOOBI AND FARINAZ KOUSHANFAR MIODRAG POTKONJAK

System security has risen as a head design prerequisite. While there has been a huge group of remarkable work on testing integrated circuits (ICs) desiderata such as manufacturing rightness, delay, and power, there is no reported effort to systematically test IC security in hardware. The objective is to give a force to this line of innovative work by introducing strategies and strategy for thorough testing of physically unclonable functions (PUFs). Lately, PUFs received a incredible arrangement of consideration as security mechanisms because of their flexibility to frame various security protocols and intrinsic resiliency against physical and side channels attacks.

This paper focused on three classes of PUFs characteristic to plan pertinent test method:

- (i) predictability,

- (ii) sensitivity to component accuracy, and

- (iii) susceptibility to reverse engineering.

As our contextual investigations, we examine two prominent PUF structures, linear and feed-forward, and demonstrate that their security is not satisfactory from a few perspectives. The specialized highlights of the paper are the first non-dangerous procedure for PUF reverse engineering and another PUF structure that is able to do passing our security tests.

#### **CHAPTER 3**

#### RESEARCH METHODOLOGY

# 3.1 IMPLEMENTATION OF ARBITER PHYSICAL UNCLONABLE FUNCTION

Physical Unclonable Functions (PUFs) is an interestingly new circuit development in the field of hardware security. It takes the advantage of the uncontrollable intrinsic random features of physical objects during manufacturing process. The PUFs provides significantly higher identification and authentication by incurring hidden information from perplexed properties of physical material instead of storing them in non-volatile memory. The process varieties prompt one of a kind qualities of these circuits and these unique structure or properties are utilized as signature of the chip. In a multiplexer (MUX) PUF, the delay contrast between the two possible array of a MUX stage is distinctive for each phase in a chip. These varieties are essentially due to design jumble and process variation.

Fig 6: general description of a PUF.

An arbiter PUF is a delay based PUF which is an example of stong silicon PUF. The input to an arbiter PUF is known as a challenge, which is a binary vector whose length is ordinarily same as the quantity of stages in the PUF. The yield is known as a response, which relies upon the delay of their path in the circuit. A randomly picked set of challenge and their corresponding response are called challenge-response pair(CRPs). The PUF's element cannot be detected and its irreproducible attributes to the randomness and the arbitrariness of the manufactering PUF. The delay based PUFs have two preferences which empower to work

on-request and to uncover the PUF's trademark through simulation. We concentrate on delay arbiter PUF with respect to which two delay path are simulated at the same time, and the response is chosen by which signal reaches faster.

Fig 7: general block diagram of an arbiter delay PUF