# DESIGN OF LOW POWER SRAM ARCHITECTURE USING 18 nm FinFET TECHNOLOGY

А

Thesis

Submitted in partial fulfillment of the requirements for the

Award of the degree of

# DOCTOR OF PHILOSOPHY In

**Electronics and Communication Engineering**

By

# T.SANTOSH KUMAR

**Reg No: 41700043**

**Supervised By**

Dr.SUMAN LATA TRIPATHI

Transforming Education Transforming India

# LOVELY PROFESSIONAL UNIVERSITY PUNJAB 2021

### DECLARATION

I hereby declare that the thesis entitled "DESIGN OF LOW POWER SRAM ARCHITECTURE USING 18 nm FinFET TECHNOLOGY" is submitted by me for the Degree of Doctor of Philosophy in Electronics and Communication Engineering is the result of my original and independent research work carried out under the guidance of **Dr.Suman Lata Tripathi**, Professor, Lovely Professional University, Punjab. It has not been submitted for the award of any degree, diploma, and associateship, fellowship of any University or Institution.

Place: Punjab

Date: 1/3/2021

Signature of the Candidate

# CERTIFICATE

This thesis entitled "DESIGN OF LOW POWER SRAM ARCHITECTURE USING 18 nm FinFET TECHNOLOGY" submitted by **T.Santosh Kumar** of Lovely Professional University is a record of bona fide research work done by her and it has not been submitted for the award of any degree, diploma, associateship, fellowship of any University/Institution.

Place: Punjab Date: 1/3/2021

Semiler

Signature of the Guide

### Abstract

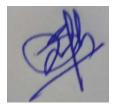

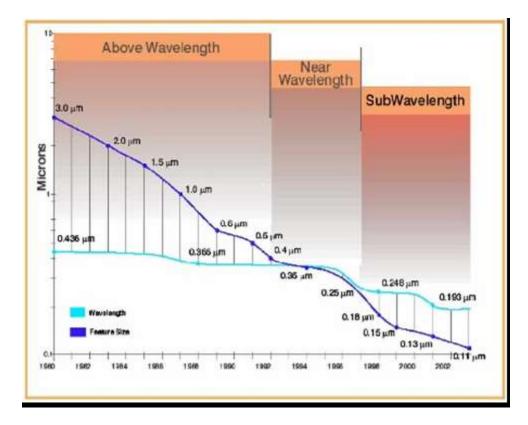

The scaling of transistors in to nanometre for better speeds and power consumption which is done according to the International Technology Roadmap for Semiconductor (ITRS)-2013 report, has a positive drive in the industry and also the usage of silicon based devices increased. , scaling trend of advanced commercial chips from 1950 to 2020 is identified. We have clearly observed the evolution of the microprocessor from 4004 to Core i7 with the increment in number of transistors per Integrated Circuit. To achieve this, the size of the transistor is reduced which further acts as a challenge for Nanoscale MOSFETS. These challenges influence the performance of the MOSFET based SRAM cells particularly below 65nm technologies. To overcome these challenges, various advanced MOSFETs were introduced such as DG-MOSFETs, TGFETs, SOI MOSFETS, FinFETs, etc. FinFET has been chosen as a transistor of choice because it is not affected by Short Channel Effects. The problems with FinFET have been observed and accordingly objectives have been decided. The present day semiconductor devices most part of the device is utilized by SRAMs so it is necessary to have these devices consuming less power and also dissipating less power.

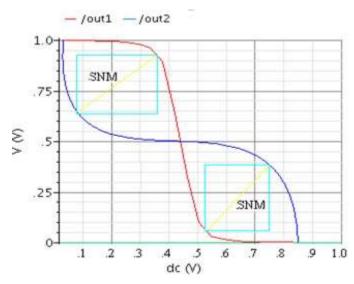

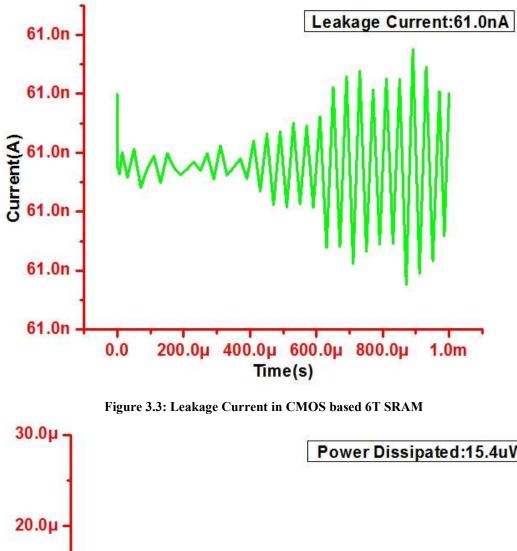

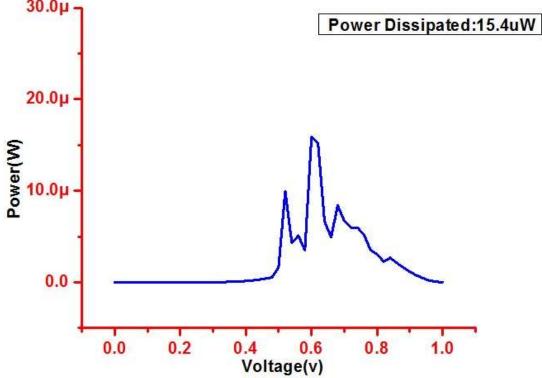

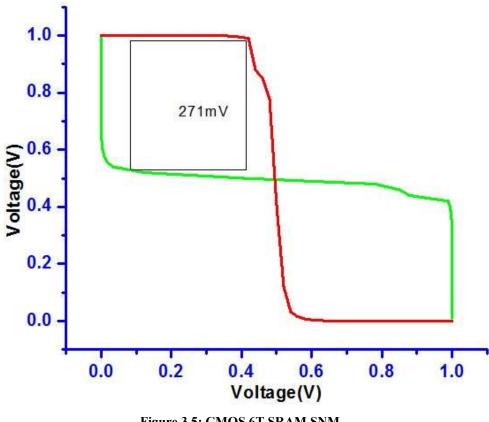

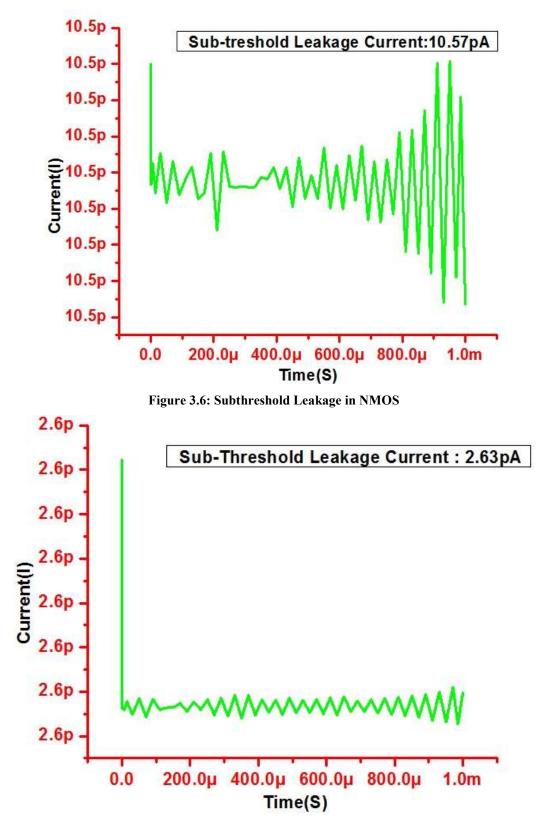

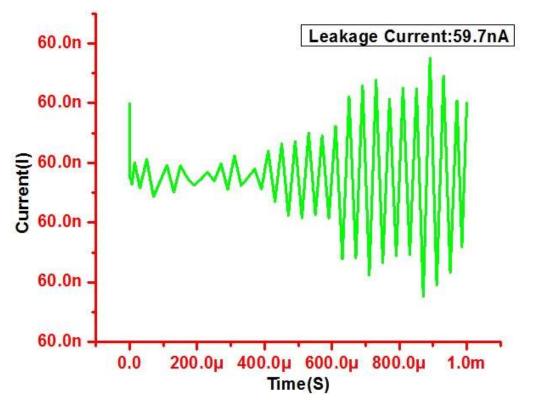

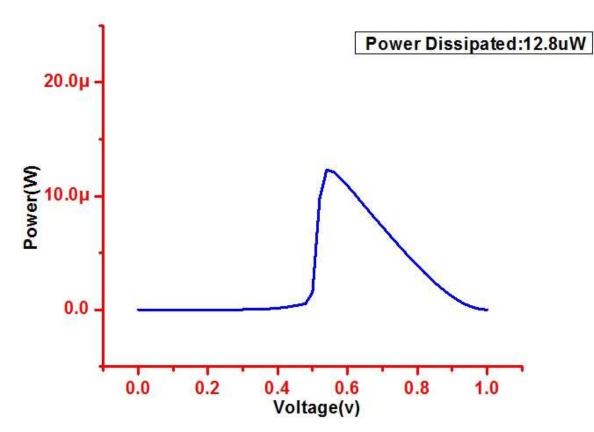

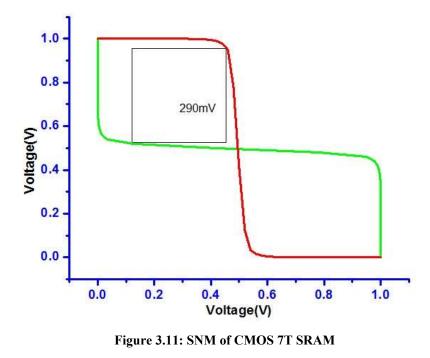

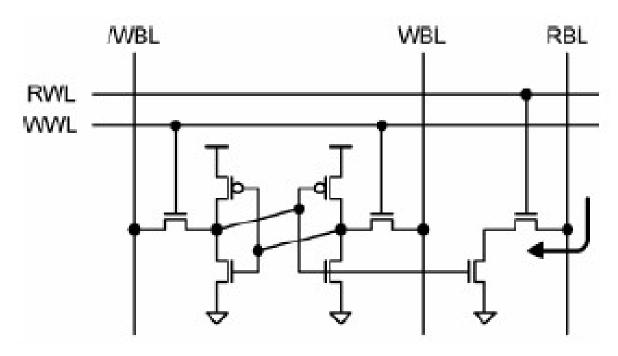

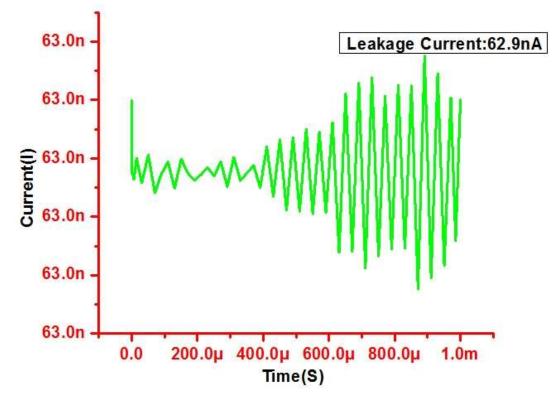

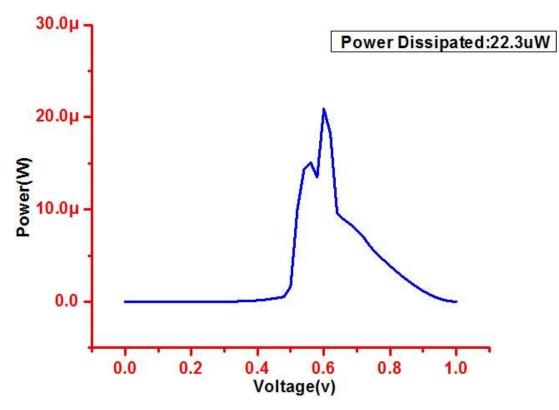

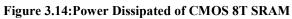

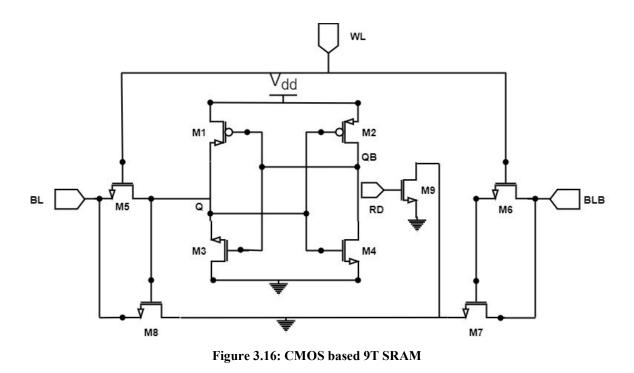

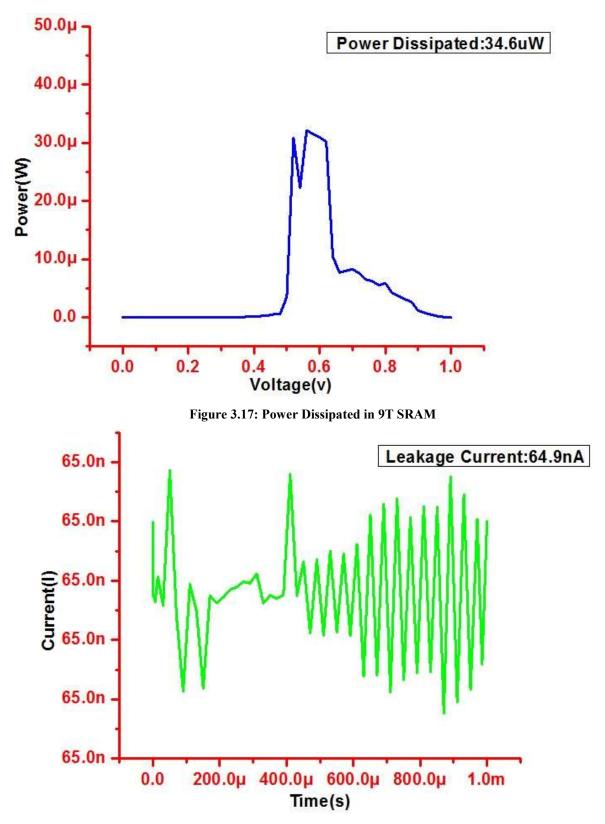

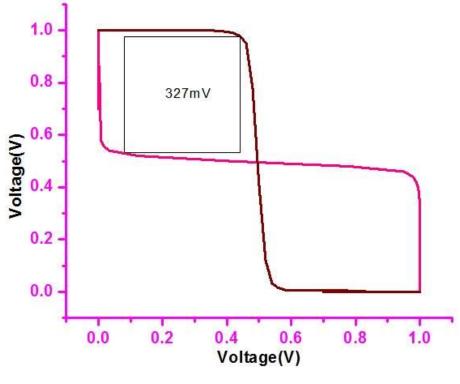

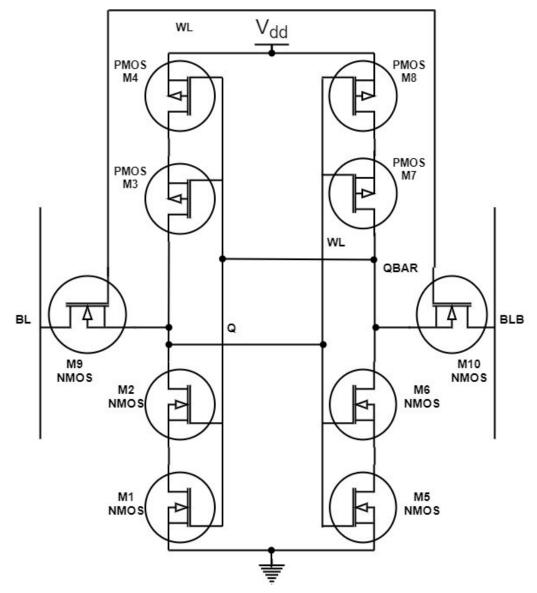

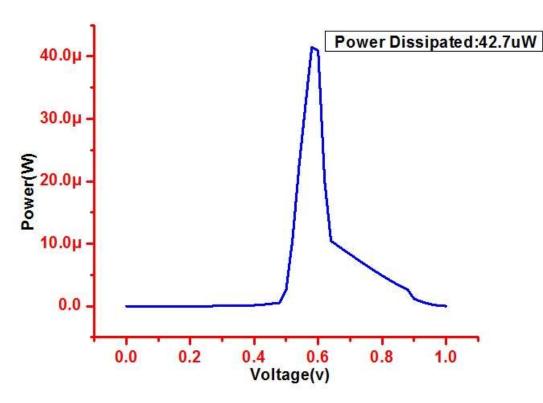

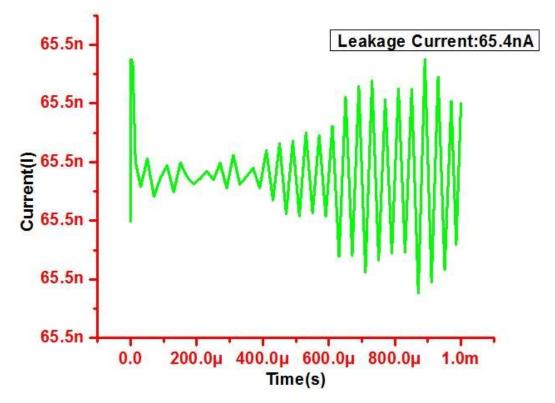

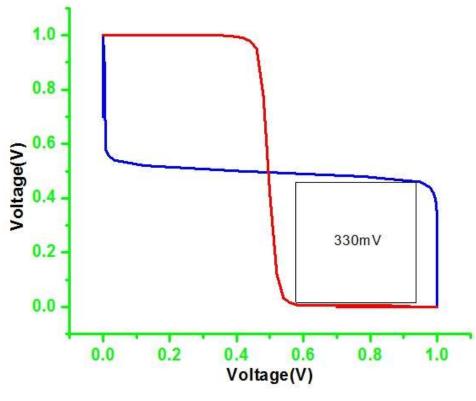

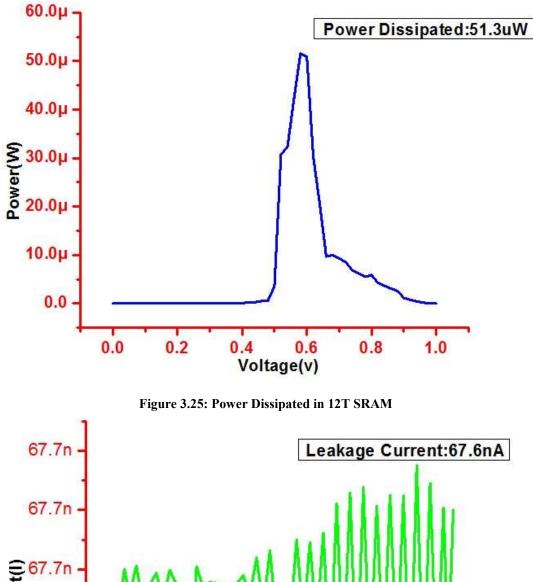

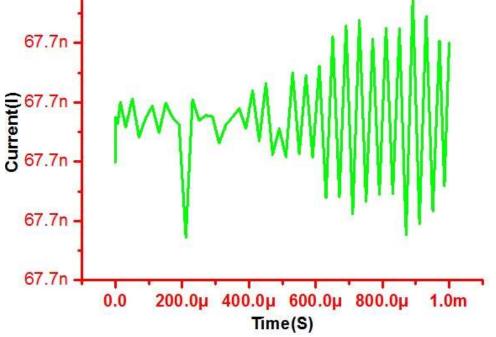

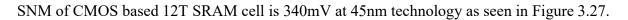

In this thesis, an extensive literature survey has been conducted to select a best procedure for proposing a SRAM which has better performance, stability and low power consumption. In this regard a detailed evaluation of CMOS based SRAM cells is done in terms of static noise margin, Leakage current, power consumption and power dissipation, Subthreshold leakage currents for 6T, 7T, 8T, 9T, 10T, 12T at 45nm CMOS technology and comparison of the above parameters is done where the leakage currents are 61nA,59.7nA,62.9nA,64.9nA,65.4nA,67.6nA respectively and power dissipation is found to be  $15.4\mu$ W,12.8  $\mu$ W ,22.3  $\mu$ W ,34.6  $\mu$ W ,42.7  $\mu$ W ,51.3  $\mu$ W respectively and found that 7T SRAM has better performance among all the transistor topologies.

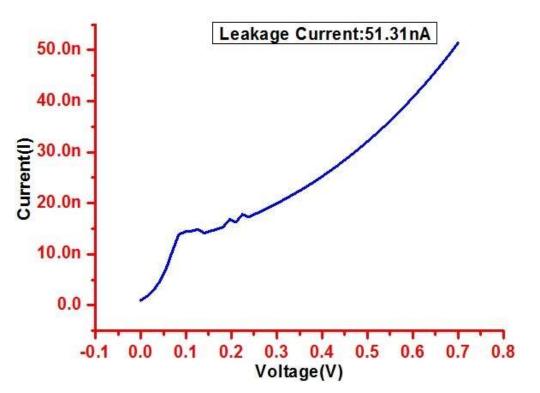

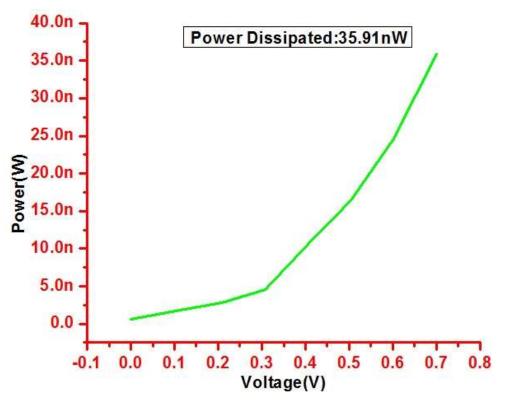

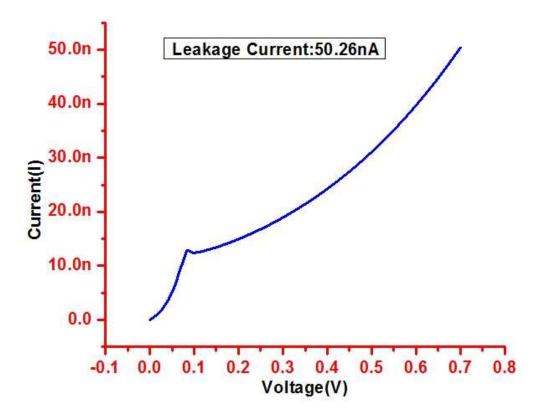

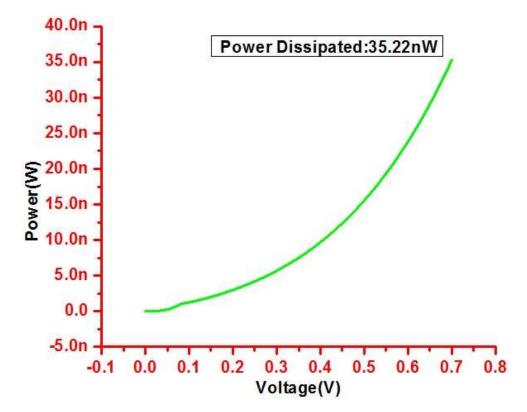

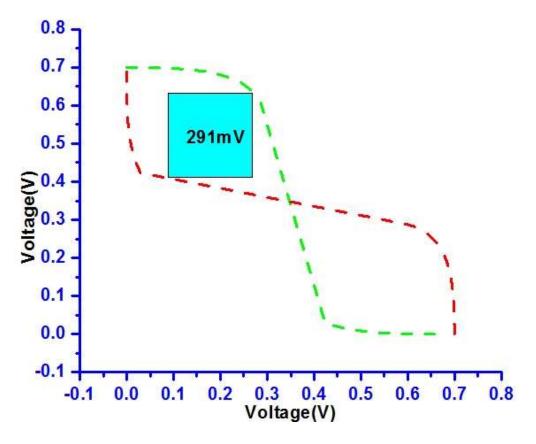

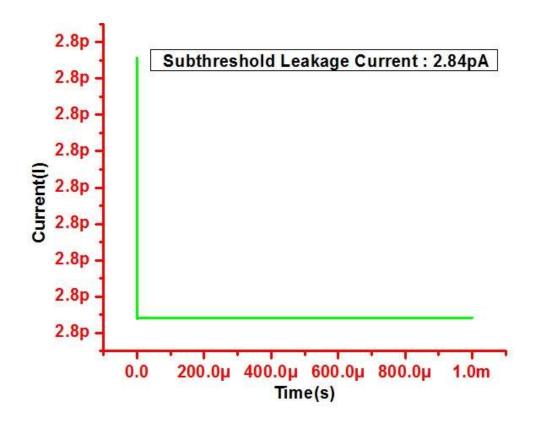

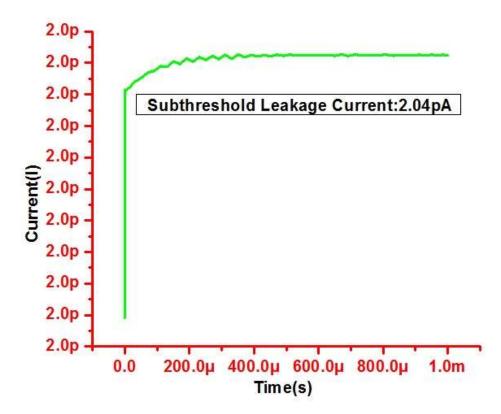

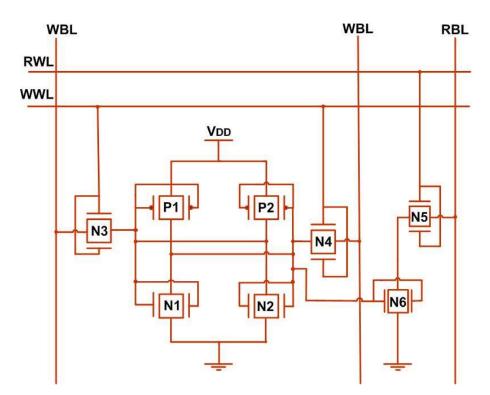

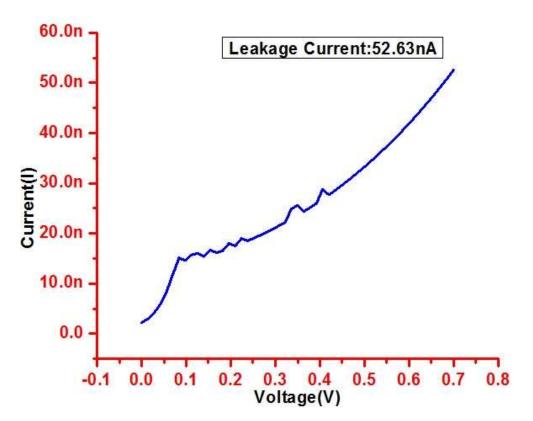

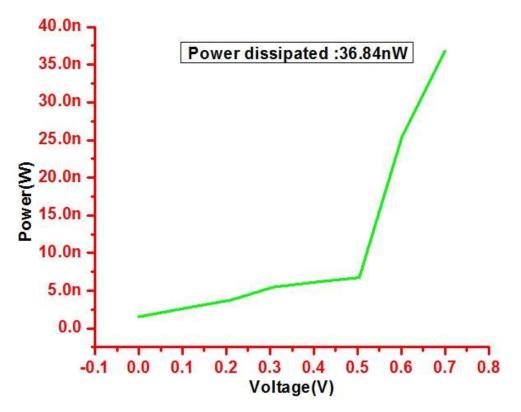

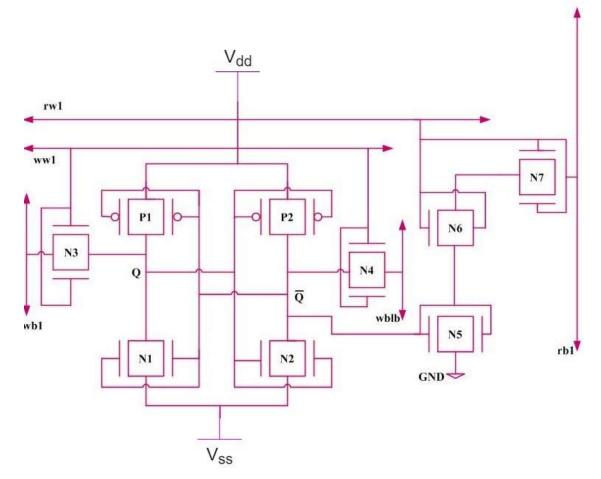

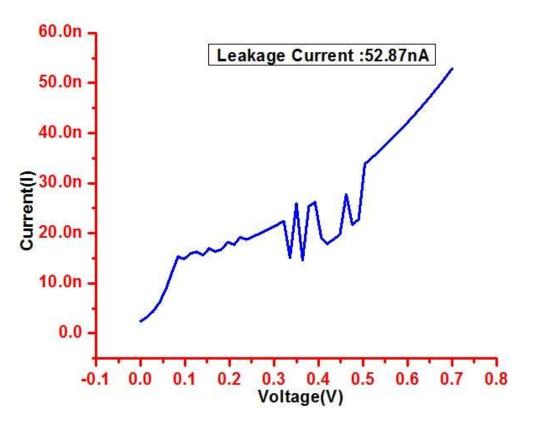

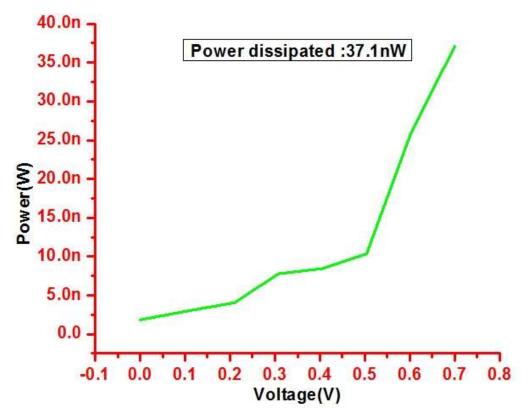

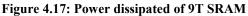

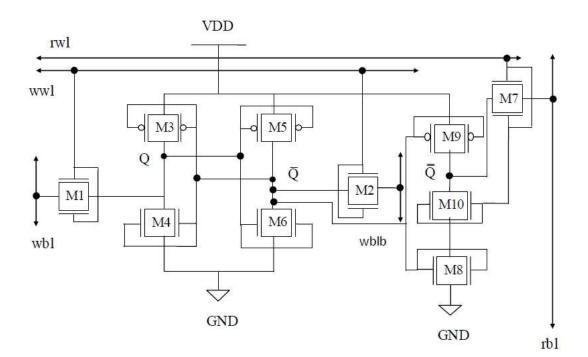

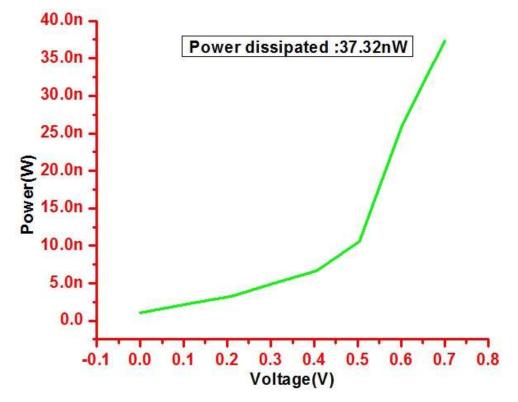

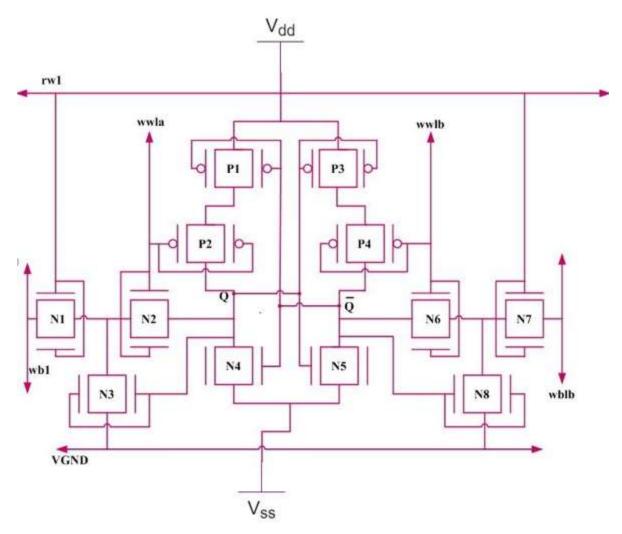

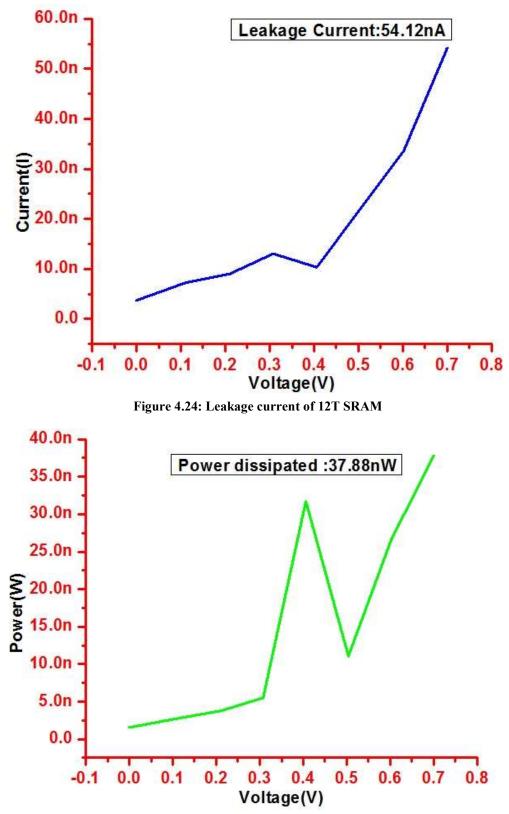

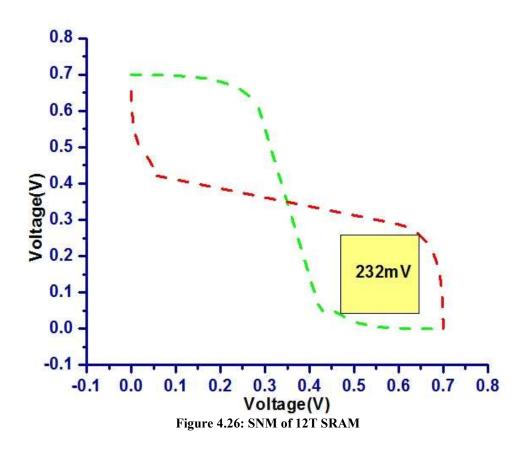

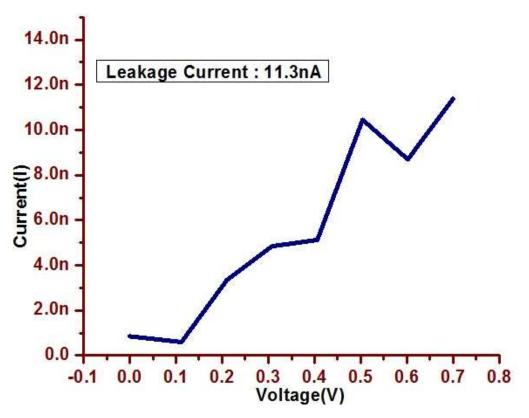

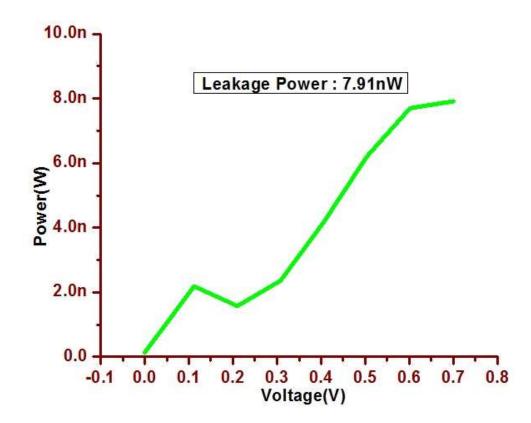

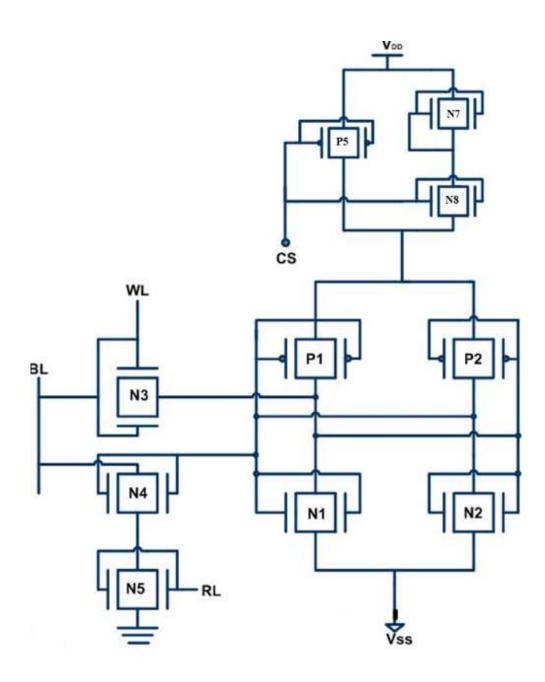

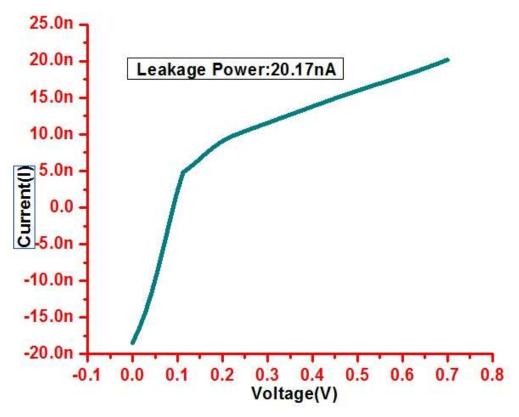

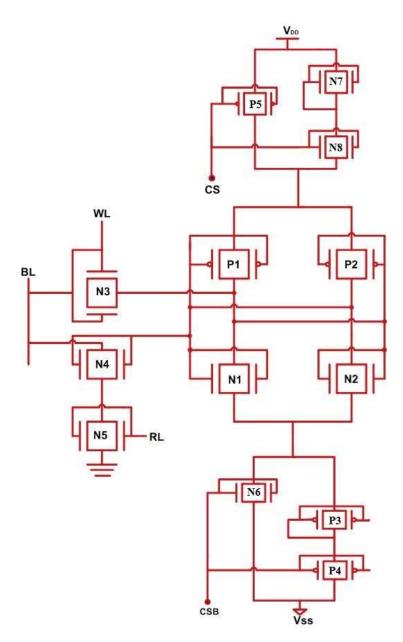

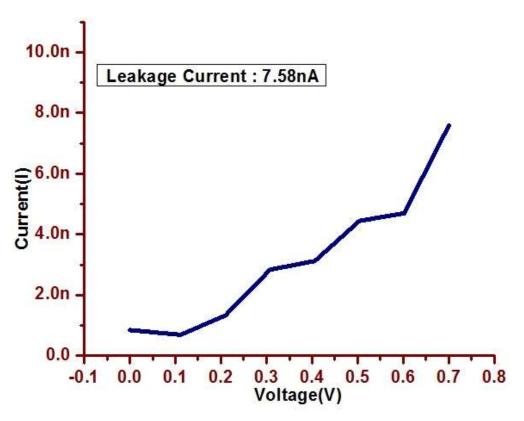

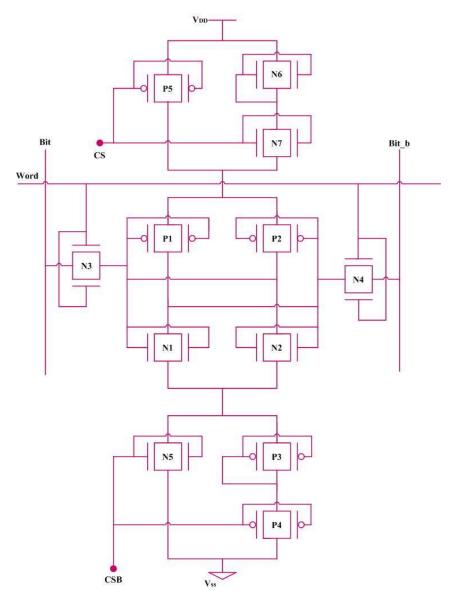

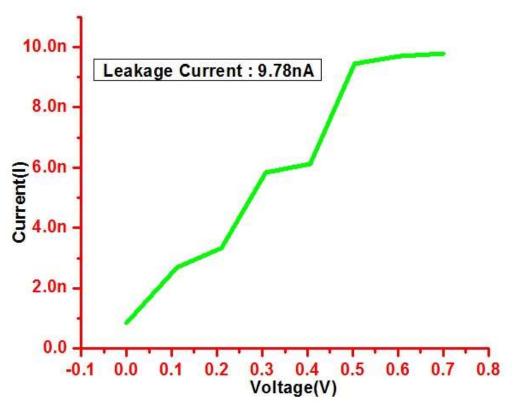

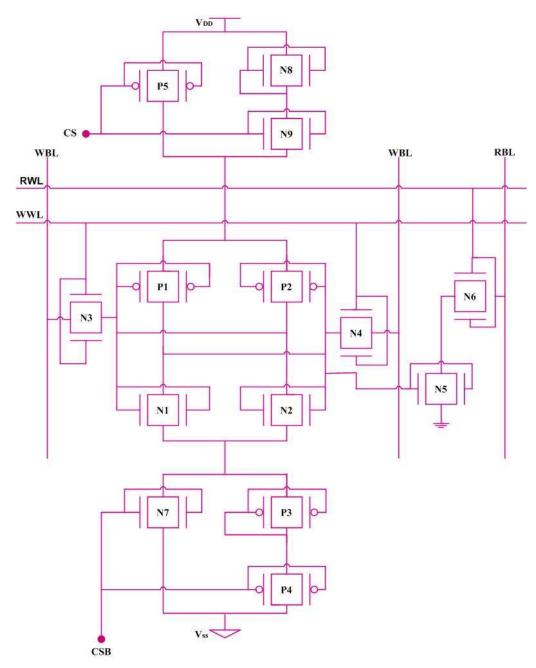

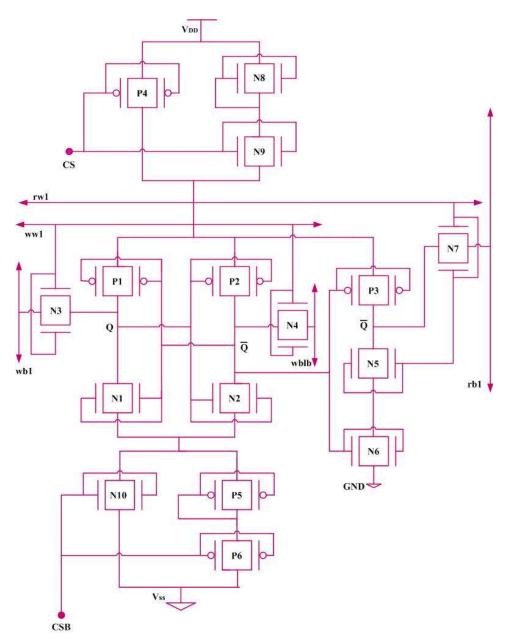

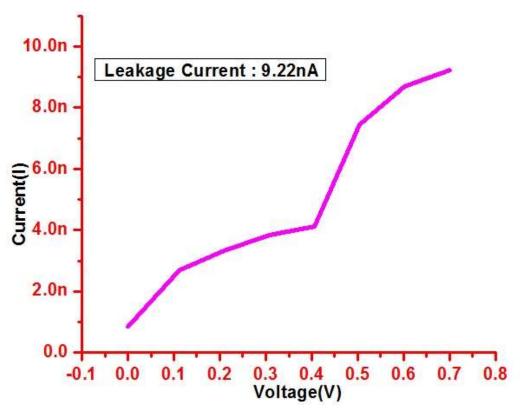

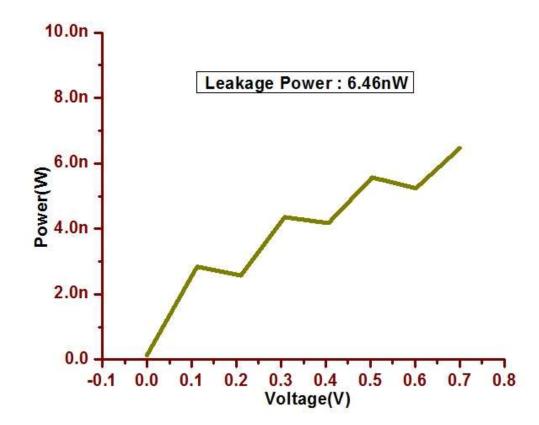

Further SRAM is designed by using 18nm FinFET technology ,where the designed 6T, 7T, 8T, 9T, 10T, 12T topologies have leakage current of 51.31nA, 50.26nA, 52.63nA, 52.87nA, 53.32nA, 54.12nA respectively and the power dissipation of 35.91nW, 35.22nW, 36.84nW, 37.1nW, 37.32nW, 37.88nW respectively. Its performance is compared with that of the same topologies designed in 45nm CMOS technology. The leakage currents and power consumption and dissipation of these SRAM cells are compared. It is found that the 7T SRAM has better performance than other SRAM because of the proposed design in which the power consumption is reduced by 40% because of the reduced switching activity employed in the design

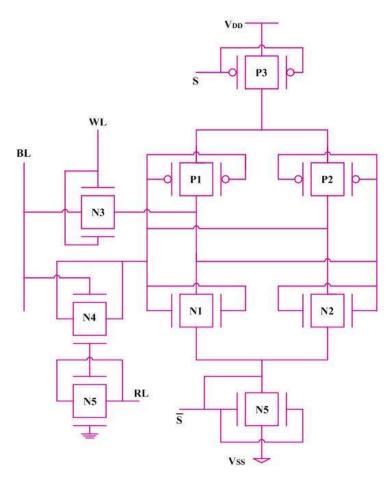

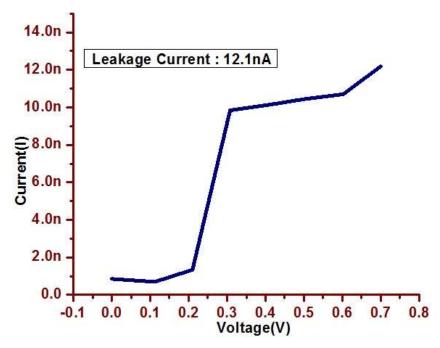

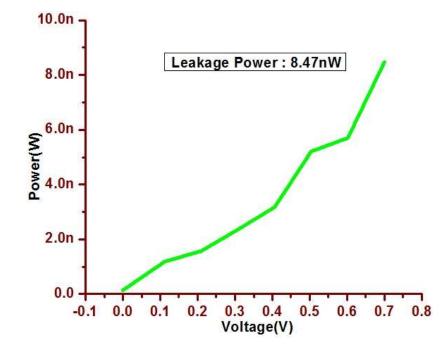

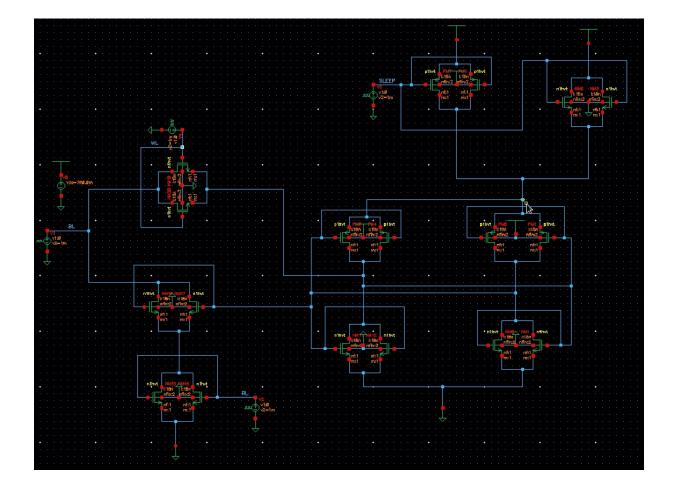

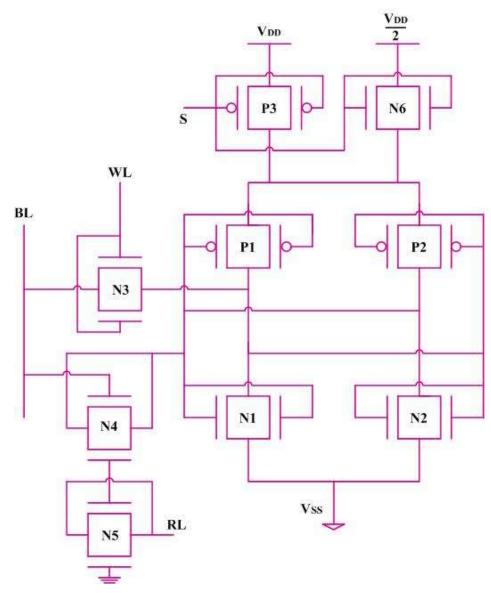

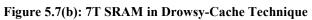

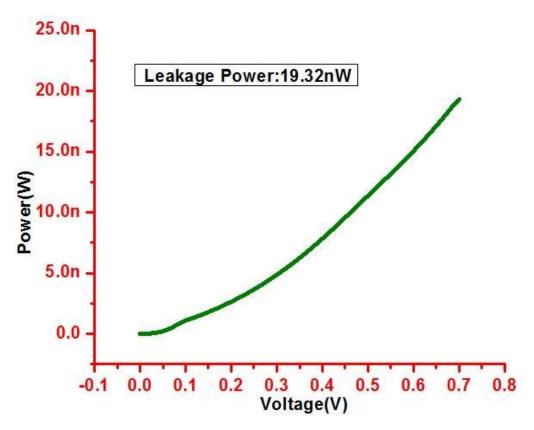

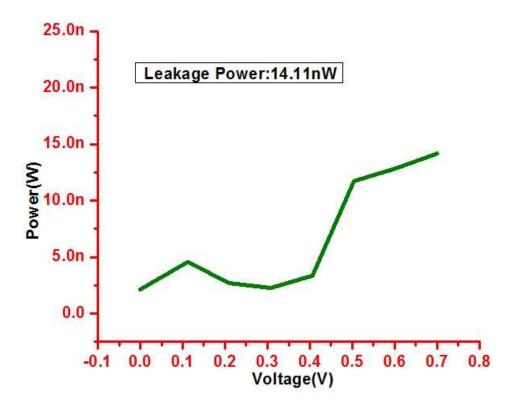

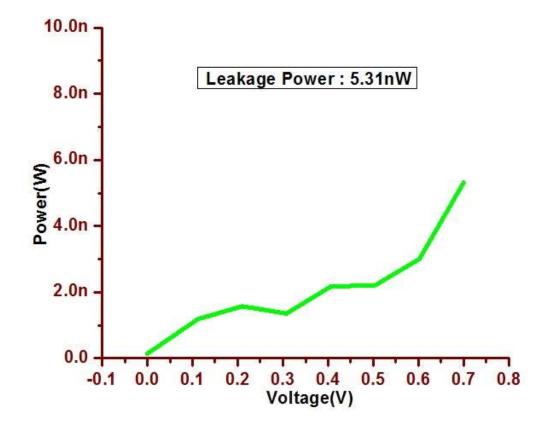

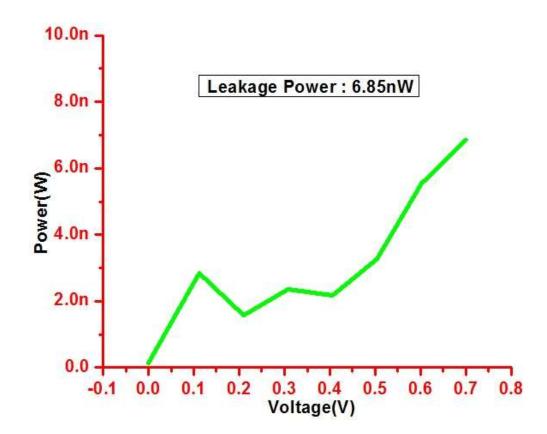

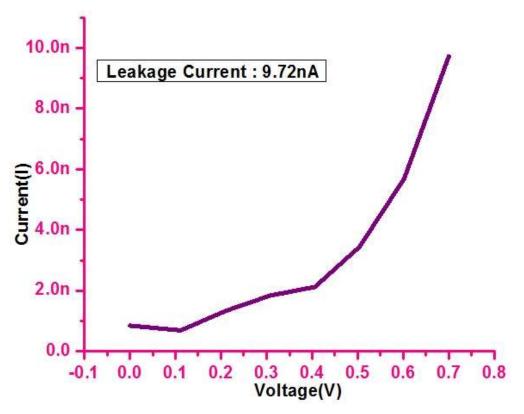

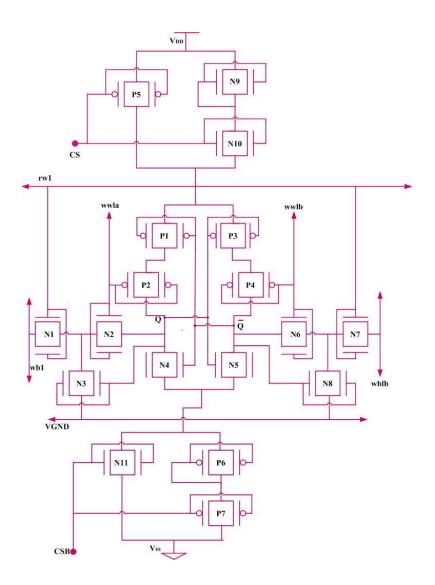

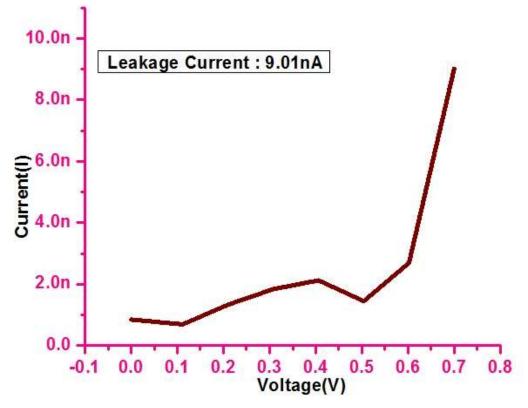

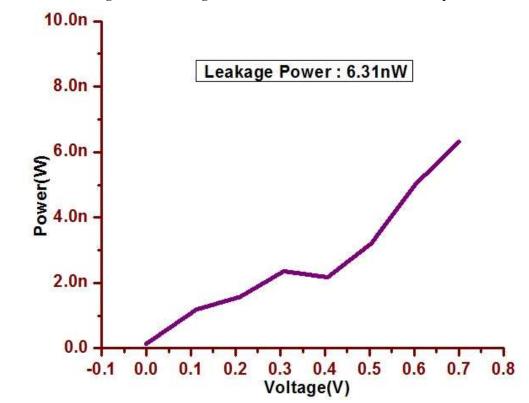

And to reduce the leakage currents the leakage reduction techniques are applied to the proposed 7T SRAM cell and by applying the SVL technique the leakage current is reduced by 84.9% and the leakage power is reduced by 87.3% in comparison to the 7T SRAM without applying the technique .whereas by applying MTCMOS method the leakage current is reduced by 75.9% and power by 70.1% and by AVL technique the leakage power has come down to 72.8% and current by 77.5% and another technique drowsy cache has brought down the leakage current by 82.6% and leakage power by 81.3% in comparison to 7T SRAM based on FinFET. It is evident that of all the techniques the SVL is better.

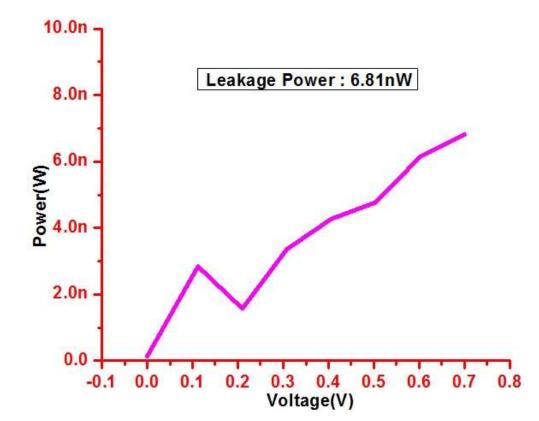

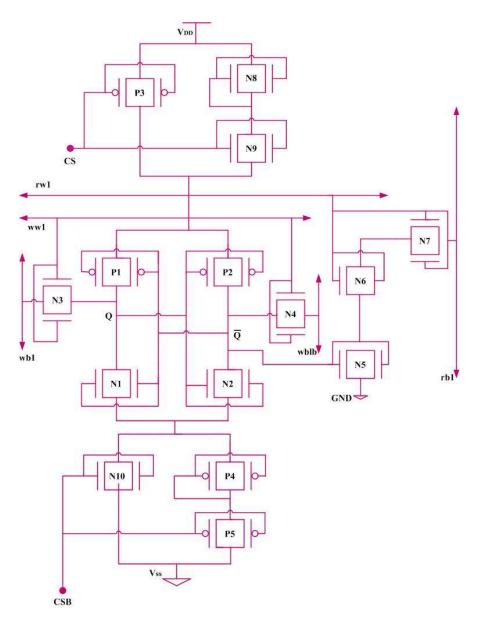

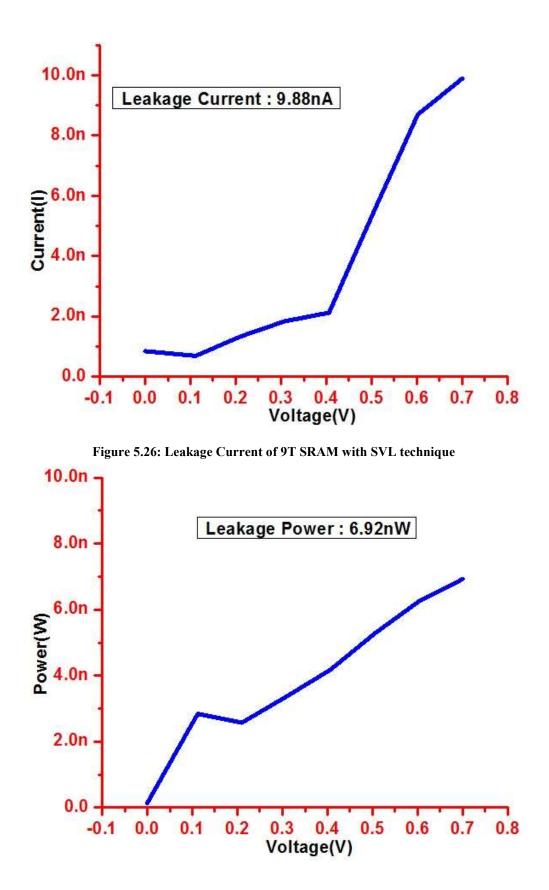

And the Proposed SVL method is applied to the circuits of other transistor topologies and it is found that the leakage current of 6T SRAM has reduced by 80.9% and power by 78.2%.and the 8T SRAM has a reduction of 81.5% of leakage current and 80.2% of leakage power. The 9T has 81.3% and 82.1% of reduction in leakage current and leakage power.10T and 12T SRAMs have 82.75%,80.72% and 83.3%,84.1% of the leakage current and leakage power respectively when compared to the 6T, 8T,9T,10T,12T FinFET based SRAMs respectively.

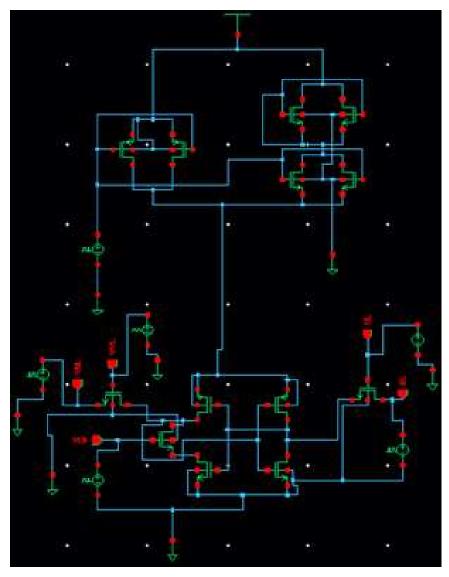

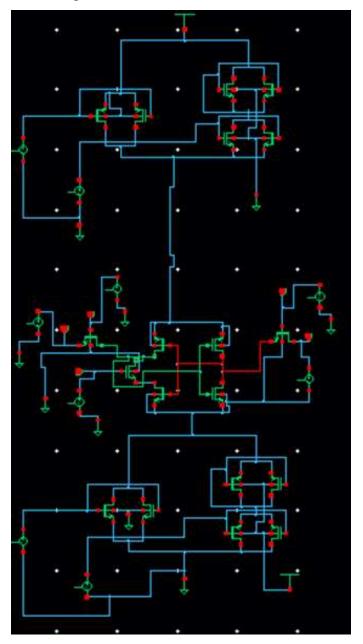

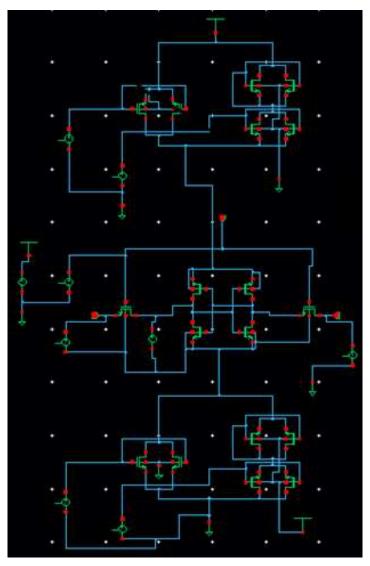

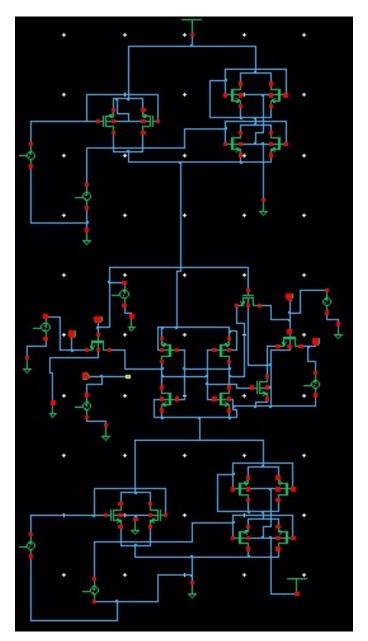

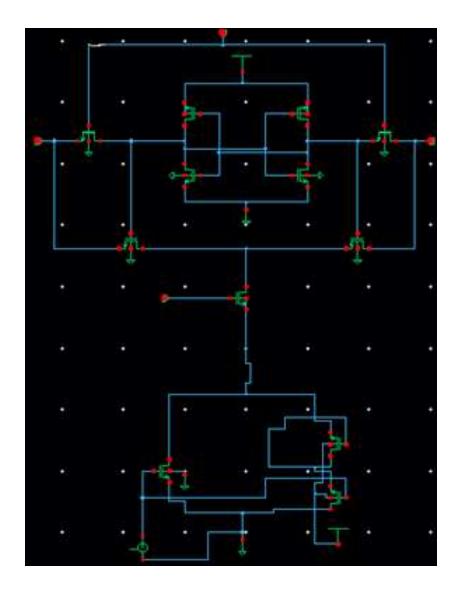

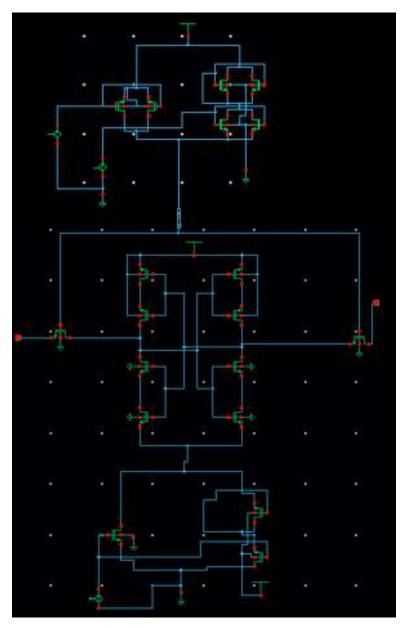

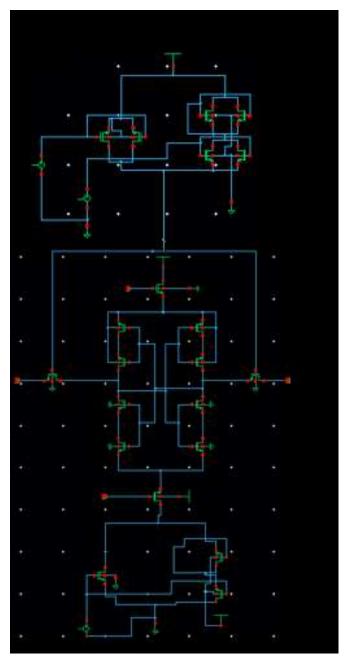

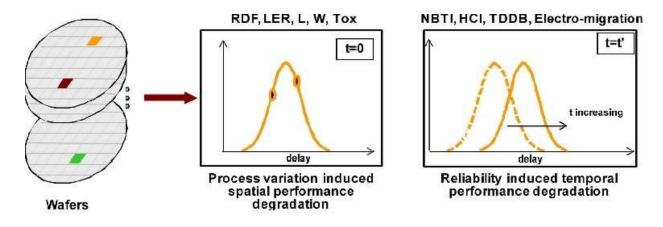

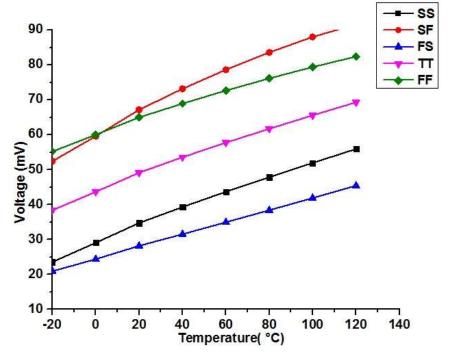

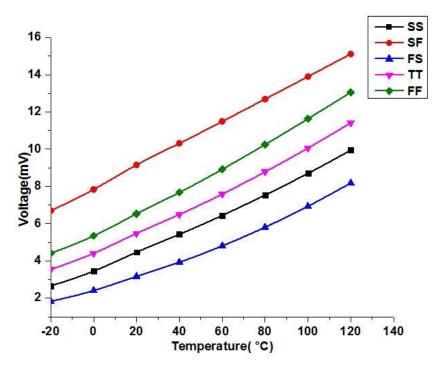

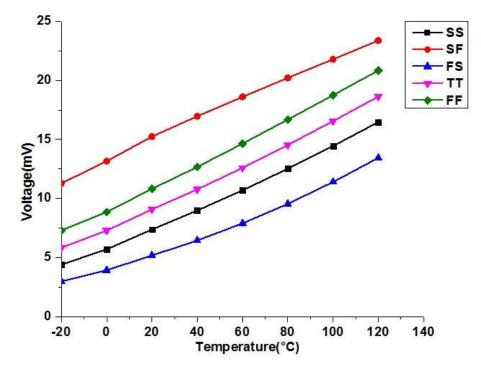

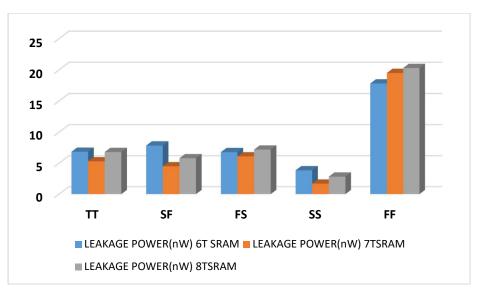

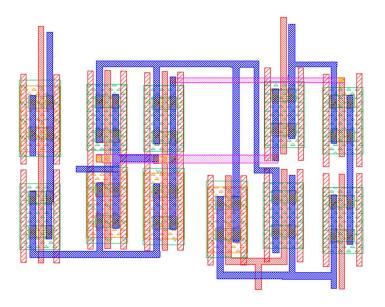

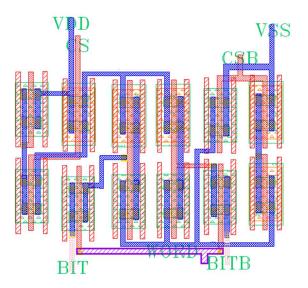

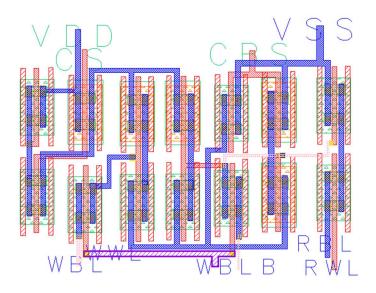

The process variation analysis is done for 6T, 7T and 8T SRAM cells related to the data retention voltage of SRAM cell to hold a Zero value.as the input is Zero to retain that value the voltage at the output should be less than 100mv as we are checking the device in OFF state .It is observed that in all the process corners at low temperatures the data retention voltage is minimum and as the temperature increases the data retention voltage also is increasing and at certain temperature it is constant for certain region and further increased to the maximum value at high temperatures. As observed the FS mode has least voltage for all three configurations, whatever voltage shown here is the leakage voltage and also it is found that whenever the device is operated in TT corner it has least leakage power compared to all other corners as both the transistors in this configuration operate evenly. Among all SRAM topologies 7T SRAM cell based on 18nm FinFET technology, have shown minimum power consumptions at all TT, SF, FS and FF corners. The layout of 6T, 7T, 8T are drawn and found the area to be 1.07, 1.2533, 1.286 µM<sup>2</sup> respectively.

### ACKNOWLEDGEMENT

First and foremost, I am thankful to almighty for making things possible at the right time. I owe my success to my supervisor and would like to sincerely thank **Dr. Suman Lata Tripathi** for her guidance. I greatly appreciate her support, positive attitude, and her vast knowledge in a wide range of topics. Her guidance not only in terms of giving ideas and solving research problems, but also in terms of giving freedom to do research in my own way has proved to be useful and invaluable. I am deeply influenced by my supervisor's way of guidance and sincerely thankful for standing by my side in tough times.

I also take this opportunity to thank all the Teaching and Non-Teaching members of Lovely Professional University, in particular members of School of Electronics and Electrical engineering Department.

I would like to thank my wife and Daughter for their unconditional love, support and encouragement. Last but not least, I would like to thank my parents and my friends for their continuous love and support.

Finally, special thanks to all the people who helped me in direct and indirect ways to accomplish this work.

# TABLE OF CONTENTS

|                                      | Page No.     |

|--------------------------------------|--------------|

| DECLARATION                          | i            |

| CERTIFICATE                          | ii           |

| ABSTRACT                             | iii-iv       |

| ACKNOWLEDGEMENT                      | $\mathbf{V}$ |

| TABLE OF CONTENTS                    | vi           |

| CHAPTER 1 INTRODUCTION               | 1-22         |

| 1.1 History Of CMOS Device           |              |

| 1.2 Complications In Scaling MOSFET  |              |

| 1.2.1 Scaling Of MOSFET              |              |

| 1.2.2 Effects of Scaling             |              |

| 1.3 Types of MOSFETs                 |              |

| 1.3.1 Double Gate MOSFET(DG MOSFET)  |              |

| 1.3.2 Triple-Gate MOSFETs(TG MOSFET) |              |

| 1.3.3 SOI MOSFET                     |              |

| 1.3.4 FinFET Devices                 |              |

| 1.4 Memory Organization              |              |

| 1.5 Conventional SRAM                |              |

| 1.6 Research Gap                     |              |

| 1.7 Research Objectives              |              |

| 1.8 Thesis Organization              |              |

| 1.9 Chapter Summary                  |              |

|                                      |              |

## **CHAPTER 2 LITERATURE SURVEY**

| 2.1 FinFET Device                                     |       |

|-------------------------------------------------------|-------|

| 2.2 Conventional 6T SRAM Cell                         |       |

| 2.3 Design of 6T SRAM Cell Using FinFET Device        |       |

| 2.4 Design Problems in Conventional SRAM              |       |

| 2.5 Power Reduction in SRAM Cell                      |       |

| 2.6 Process Variation                                 |       |

| CHAPTER 3 DESIGN AND ANALYSIS OF CMOS SRAM CELL       | 38-62 |

| 3.1 Conventional 6T SRAM Cell                         |       |

| 3.2 SRAM Operations                                   |       |

| 3.3 Performance Parameters                            |       |

| 3.3.1 Static Noise Margin                             |       |

| 3.3.2 Power Consumption                               |       |

| 3.3.3 Cell Area                                       |       |

| 3.3.4 SRAM Delay                                      |       |

| 3.4 Different Types of Leakage Currents in SRAM       |       |

| 3.5 Performance Analysis of 45nm CMOS Based SRAM Cell |       |

| 3.5.1 Power Dissipation and Leakage Current           |       |

| 3.5.2 Calculation of Static Noise Margin              |       |

| 3.5.3 Sub-Threshold Leakage Current                   |       |

| 3.6 SRAM Cell With Different transistor Topologies    |       |

| 3.6.1 7T SRAM Cell                                    |       |

| 3.6.2 8T SRAM Cell                                    |       |

| 3.6.3 9T SRAM Cell                                    |       |

| v                                                     |       |

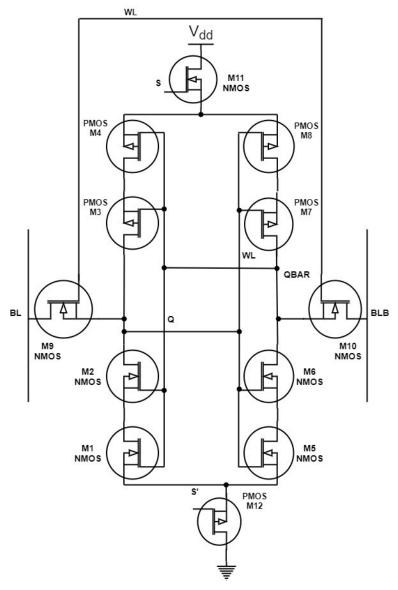

3.6.4 10T SRAM Cell

3.6.5 12T SRAM Cell

3.7 Result Analysis of SRAM Cell For Different Transistor Topologies

3.8 Conclusion of Chapter

### CHAPTER 4 DESIGN AND ANALYSIS OF FINFET BASED SRAM CELL 63-85

- 4.1 FinFET Based 6T SRAM Cell

- 4.2 SRAM Operation

- 4.2.1 Read Operation

- 4.2.2 Write Operation

- 4.2.3 Hold Operation

- 4.3 Performance Parameters

- 4.3.1 Static Noise Margin(SNM)

- 4.3.2 Power Dissipation

- 4.3.3 Power Consumption

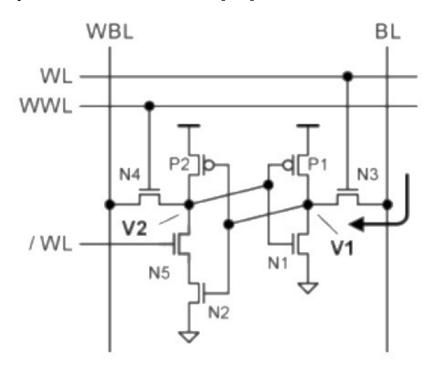

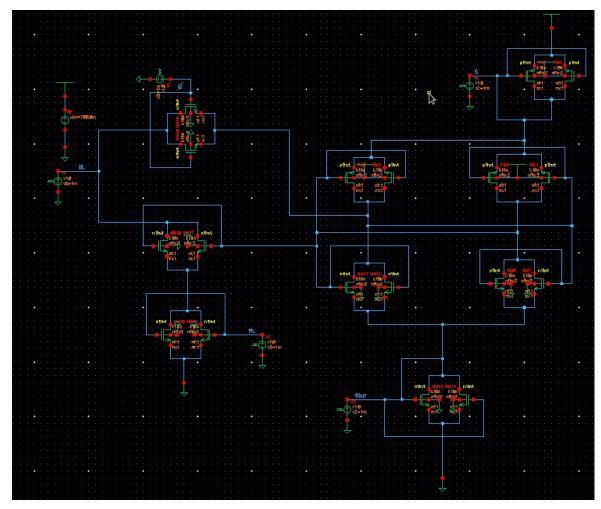

- 4.4 Design of Proposed FinFET Based 7T SRAM Cell

- 4.5 FinFET Based 8T SRAM Cell

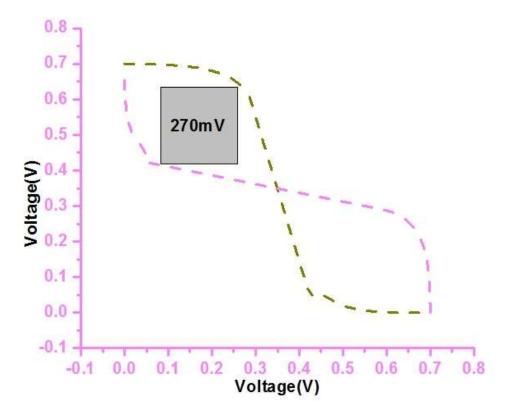

- 4.6 FinFET Based 9T SRAM Cell

- 4.7 FinFET Based 10T SRAM Cell

- 4.8 FinFET Based 12T SRAM Cell

- 4.9 Analysis Of FinFET Based SRAM Cells

- 4.10 Conclusion Of Chapter

## CHAPTER 5 LEAKAGE CURRENTS AND ITS REDUCTION 86-122 TECHNIQUES

5.1 Introduction

- 5.2 Leakage Reduction Techniques For 7T SRAM Cell

- 5.2.1 Multi-threshold CMOS (MTCMOS) Technique

- 5.2.2 Adaptive Voltage Level Technique(AVL)

- 5.2.3 Drowsy-cache Technique

- 5.2.4 Proposed Self-Controllable Voltage Level Technique(SVL)

- 5.3 Proposed Leakage Reduction Technique Implementation On

Different FinFET Based SRAM Cells

- 5.3.1 Self-Controllable Voltage Level Technique(SVL) Technique Implementation On FinFET Based 6T SRAM

- 5.3.2 Self-Controllable Voltage Level Technique(SVL) Technique Implementation On FinFET Based 8T SRAM

- 5.3.3 Self-Controllable Voltage Level Technique(SVL) Technique Implementation On FinFET Based 9T SRAM

- 5.3.4 Self-Controllable Voltage Level Technique(SVL) Technique Implementation On FinFET Based 10T SRAM

- 5.3.5 Self-Controllable Voltage Level Technique(SVL) Technique Implementation On FinFET Based 12T SRAM

- 5.4 Result Analysis

- 5.5 Advantages Of Proposed Leakage Reduction Technique

- 5.6 Chapter Summary

### CHAPTER 6 PROCESS VARIATION, TEMPERATURE EFFECTS ON 123-134 LOW POWER SRAM CELL AND LAYOUTS

6.1 FinFET Process Variation

6.1.1 Device Parameters

6.1.2 Process Variation at Device Level

6.2 Effect Of Temperature

6.3 Result Analysis Of Process Variation

6.4 Cell Area And Layout

6.5 Chapter Conclusion

## CHAPTER 7 CONCLUSION AND FUTURE SCOPE

135-136

7.1 Conclusion

7.2 Future Scope

#### REFERENCES

# List of Tables

| Table No | Name of The Table                                                                                                    | Page No |

|----------|----------------------------------------------------------------------------------------------------------------------|---------|

| 3.1      | Performance Comparison CMOS SRAM Cell                                                                                | 62      |

| 4.1      | Performance Comparison of CMOS and FinFET based SRAMs                                                                | 86      |

| 5.1      | Comparison of Leakage current and leakage power of 7T SRAM with different techniques                                 | 114     |

| 5.2      | Comparison of the leakage power and leakage current with proposed SVL technique applied to different transistor SRAM | 114     |

| 5.3      | Comparison of 7T SRAM with other Published Papers                                                                    | 115     |

| 6.1      | Data Retention Voltage vs Temperature in 6T SRAM                                                                     | 121     |

| 6.2      | Data Retention Voltage vs Temperature in 7T SRAM                                                                     | 122     |

| 6.3      | Data Retention Voltage vs Temperature in 8T SRAM                                                                     | 123     |

| 6.4      | Leakage Power vs Process Corners                                                                                     | 124     |

| 6.5      | Area of SRAMs                                                                                                        | 127     |

# List of Figures

| Figure<br>No | Name of The Figure                     | Page<br>No |

|--------------|----------------------------------------|------------|

| 1.1          | Moore's Law                            | 2          |

| 1.2          | Principle of Scaling                   | 3          |

| 1.3          | Voltage VS Channel length              | 7          |

| 1.4          | Hot Electron Effect                    | 10         |

| 1.5          | Double Gate MOSFET                     | 11         |

| 1.6          | Energy Band of DGMOSFET                | 12         |

| 1.7          | Energy Band of Asymmetrical DGMOSFET   | 13         |

| 1.8          | Triple Gate MOSFET                     | 14         |

| 1.9          | SOI MOSFET                             | 15         |

| 1.10         | FinFET 3D View                         | 16         |

| 1.11         | Memory Organization                    | 17         |

| 1.12         | 6T SRAM                                | 18         |

| 1.13         | Thesis Organization                    | 21         |

| 2.1          | FinFET Device                          | 24         |

| 2.2          | 6T SRAM                                | 27         |

| 2.3          | FinFET based 6T SRAM                   | 29         |

| 3.1          | CMOS based 6T SRAM                     | 39         |

| 3.2          | Butterfly Curve                        | 41         |

| 3.3          | Leakage Current in CMOS based 6T SRAM  | 45         |

| 3.4          | Power Dissipated in CMOS based 6T SRAM | 45         |

| 3.5  | CMOS 6T SRAM SNM                      | 47 |

|------|---------------------------------------|----|

| 3.6  | Subthreshold Leakage in NMOS          | 48 |

| 3.7  | Subthreshold Leakage in PMOS          | 48 |

| 3.8  | CMOS based 7T SRAM                    | 49 |

| 3.9  | Leakage Current of CMOS 7TSRAM        | 50 |

| 3.10 | Power Dissipated of CMOS 7TSRAM       | 50 |

| 3.11 | SNM of CMOS 7T SRAM                   | 51 |

| 3.12 | CMOS based 8T SRAM cell               | 52 |

| 3.13 | Leakage current of CMOS 8T SRAM       | 52 |

| 3.14 | Power Dissipated of CMOS 8T SRAM      | 53 |

| 3.15 | SNM of CMOS 8T SRAM                   | 53 |

| 3.16 | CMOS based 9T SRAM                    | 54 |

| 3.17 | Power Dissipated in 9T SRAM           | 55 |

| 3.18 | Leakage Current in CMOS based 9T SRAM | 55 |

| 3.19 | SNM of 9T SRAM                        | 56 |

| 3.20 | CMOS based 10T SRAM                   | 57 |

| 3.21 | Power dissipated in 10T SRAM          | 58 |

| 3.22 | Leakage Current in 10T SRAM              | 58 |

|------|------------------------------------------|----|

| 3.23 | SNM of 10T SRAM                          | 59 |

| 3.24 | CMOS based 12T SRAM                      | 60 |

| 3.25 | Power Dissipated in 12T SRAM             | 61 |

| 3.26 | Leakage Current in 12 T SRAM             | 61 |

| 3.27 | SNM of 12T SRAM                          | 62 |

| 4.1  | FinFET based 6T SRAM                     | 65 |

| 4.2  | Leakage Current of FinFET based 6T SRAM  | 67 |

| 4.3  | Power Dissipated of FinFET based 6T SRAM | 68 |

| 4.4  | 6T SRAM SNM                              | 68 |

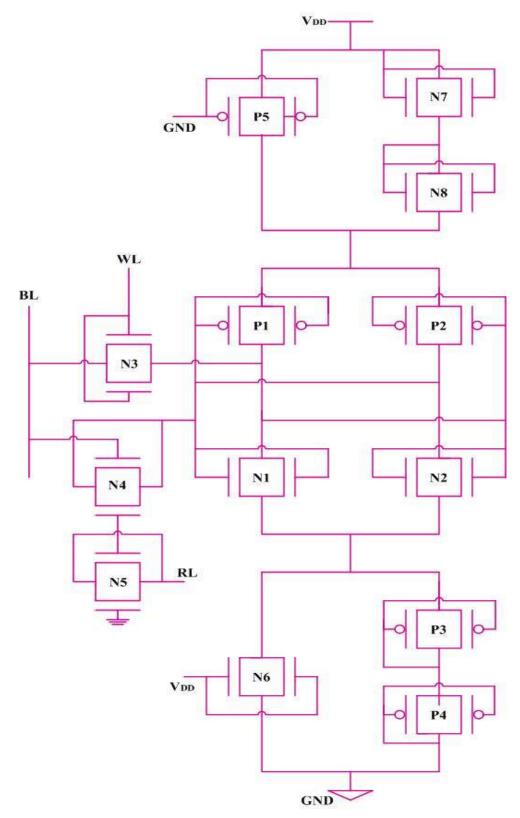

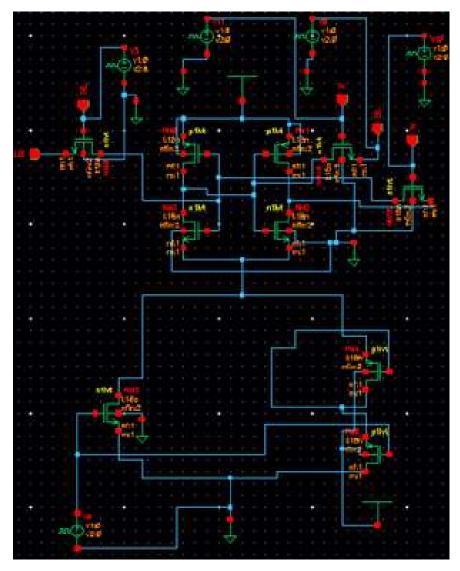

| 4.5  | Proposed FinFET based 7T SRAM            | 69 |

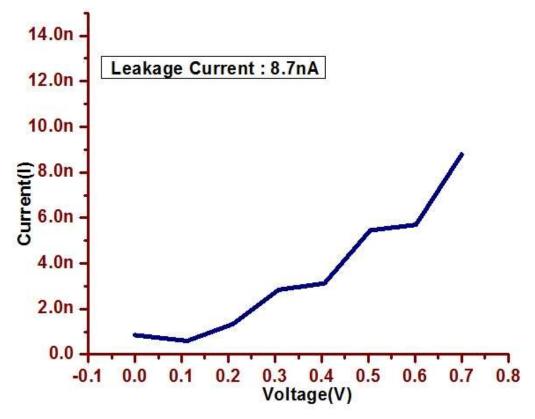

| 4.6  | Leakage Current of Proposed 7T SRAM      | 71 |

| 4.7  | Power Dissipation of 7T SRAM             | 71 |

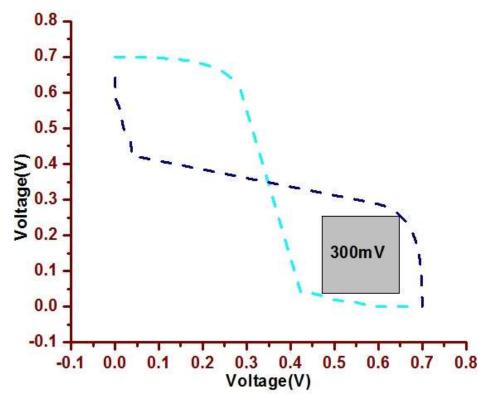

| 4.8  | SNM of 7T SRAM cell                      | 72 |

| 4.9  | Subthreshold leakage in N type FinFET    | 73 |

| 4.10 | Subthreshold leakage in P type FinFET    | 73 |

| 4.11 | FinFET based 8T SRAM                    | 74 |

|------|-----------------------------------------|----|

| 4.12 | Leakage Current of 8T SRAM              | 75 |

| 4.13 | Power dissipation of Current of 8T SRAM | 76 |

| 4.14 | SNM of 8T SRAM                          | 76 |

| 4.15 | FinFET based 9T SRAM                    | 77 |

| 4.16 | Leakage current of 9T SRAM              | 78 |

| 4.17 | Power dissipated of 9T SRAM             | 79 |

| 4.18 | SNM of 9T SRAM                          | 79 |

| 4.19 | FinFET based 10T SRAM                   | 80 |

| 4.20 | Leakage Current of 10T SRAM             | 81 |

| 4.21 | Power dissipated of 10T SRAM            | 81 |

| 4.22 | SNM of 10T SRAM                         | 82 |

| 4.23 | FinFET based 12 T SRAM                  | 83 |

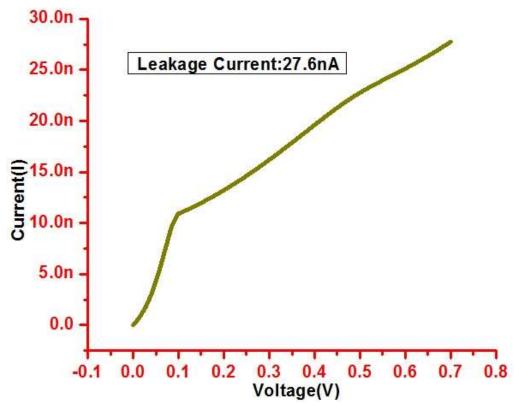

| 4.24 | Leakage current of 12T SRAM             | 84 |

| 4.25 | Power Dissipation of 12T SRAM           | 84 |

| 4.26 | SNM of 12T SRAM                         | 85 |

| 5.1  | 7T SRAM with MTCMOS Technique                        | 89  |

|------|------------------------------------------------------|-----|

| 5.2  | Leakage Current in 7T SRAM with MTCMOS technique     | 90  |

| 5.3  | Leakage Power in 7T SRAM with MTCMOS technique       | 90  |

| 5.4  | 7T SRAM with AVL technique                           | 92  |

| 5.5  | Leakage Current in 7T SRAM using AVL Technique       | 93  |

| 5.6  | Leakage Power of 7T SRAM using AVL technique         | 93  |

| 5.7  | 7T SRAM in Drowsy-Cache Technique                    | 94  |

| 5.8  | Leakage Power of 7T SRAM in Drowsy cache Technique   | 95  |

| 5.9  | Leakage Current of 7T SRAM in Drowsy cache Technique | 95  |

| 5.10 | 7T SRAM with LSVL technique                          | 97  |

| 5.11 | Leakage Current in 7T SRAM using LSVL technique      | 98  |

| 5.12 | Leakage Power in 7T SRAM using LSVL technique        | 98  |

| 5.13 | 7T SRAM with USVL Technique                          | 100 |

| 5.14 | Leakage Current in 7T SRAM with USVL technique       | 101 |

| 5.15 | Leakage Power in 7T SRAM with USVL technique         | 101 |

| 5.16 | 7T SRAM with SVL Technique                           | 102 |

| 5.17 | Leakage Current of 7T SRAM using SVL Technique | 103 |

|------|------------------------------------------------|-----|

| 5.18 | Leakage Power of 7T SRAM using SVL Technique   | 103 |

| 5.19 | 6T SRAM with SVL technique                     | 104 |

| 5.20 | Leakage Current in 6T SRAM with SVL Technique  | 105 |

| 5.21 | Leakage Power in 6T SRAM with SVL Technique    | 105 |

| 5.22 | 8T SRAM with SVL technique                     | 106 |

| 5.23 | Leakage Current of 8T SRAM with SVL technique  | 107 |

| 5.24 | Leakage power of 8T SRAM with SVL technique    | 107 |

| 5.25 | 9T SRAM with SVL technique                     | 108 |

| 5.26 | Leakage Current of 9T SRAM with SVL technique  | 109 |

| 5.27 | Leakage Power of 9T SRAM with SVL technique    | 109 |

| 5.28 | 10T SRAM with SVL Technique                    | 110 |

| 5.29 | Leakage Current of 10T SRAM with SVL technique | 111 |

| 5.30 | Leakage Power of 10T SRAM with SVL technique   | 11  |

| 5.31 | 12T SRAM with SVL technique                    | 112 |

| 5.32 | Leakage current of 12T SRAM with SVL technique | 113 |

| 5.33 | Leakage Power of 12T SRAM with SVL technique     | 113 |

|------|--------------------------------------------------|-----|

| 6.1  | Process Variation                                | 117 |

| 6.2  | Scaling trends                                   | 118 |

| 6.3  | Data Retention Voltage vs Temperature in 6T SRAM | 121 |

| 6.4  | Data Retention Voltage vs Temperature in 7T SRAM | 122 |

| 6.5  | Data Retention Voltage vs Temperature in 8T SRAM | 123 |

| 6.6  | Leakage Power vs Process Corners                 | 125 |

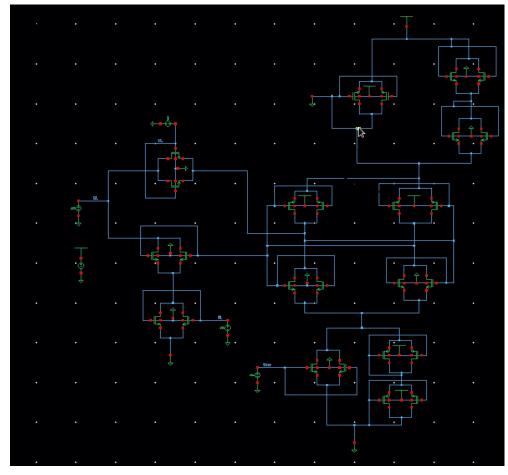

| 6.7  | Layout 7T SRAM Cell                              | 126 |

| 6.8  | Layout of 6T SRAM cell                           | 126 |

| 6.9  | Layout of 8T SRAM cell                           | 127 |

# LIST OF ABBREVIATIONS

| Abbreviation | Abbreviation Meaning                    |

|--------------|-----------------------------------------|

| VLSI         | Very Large Scale Integration            |

| CMOS         | Complementary Metal Oxide Semiconductor |

| MOS          | Metal Oxide Semiconductor               |

| FET          | Field Effect Transistor                 |

| DG FET       | Double Gate Field Effect Transistor     |

| TG FET       | Triple Gate Field Effect Transistor     |

| FinFET       | Fin type Field Effect Transistor        |

| SOI          | Silicon on Insulator                    |

| nMOS         | n – Channel MOSFET                      |

| pMOS         | p – Channel MOSFET                      |

| SCE          | Short Channel Effect                    |

| DIBL         | Drain Induced Barrier Lowering          |

| GIDL         | Gate Induced Drain Lowering             |

| SRAM         | Static Random Access Memory             |

| SNM          | Static Noise Margin                     |

| RNM          | Read Noise Margin                       |

| WNM          | Write Noise Margin                      |

| nW           | Nano Watt                               |

| μW           | Micro Watt                              |

| рА           | Pico Ampere                             |

| nA           | Nano Ampere                             |

| WL  | Word Line    |

|-----|--------------|

| BL  | Bit Line     |

| BLB | Bit Line Bar |

| VDD | Power Supply |

| GND | Ground       |

# CHAPTER 1 INTRODUCTION

In the present day electronics a device named Metal-Oxide-Semiconductor Field Effect Transistor i.e. (MOSFET) which has 3 terminals is used for numerous applications based on the requirement. The electronic signals are amplified or switched on. In the year 1925, Julius Edgar Lilienfeld first proposed the fundamental functioning of the device. In this device, the voltage that appears on an oxide insulated gate electrode may perhaps be a cause of conducting channel among the source terminal and a drain terminal. The transistor can be a P-type or an N-type or it can be a mixture of both P-type and N-type called Complimentary Metal-Oxide-Semiconductor (CMOS).

Over the past decades, the most used device is CMOS based transistor. Due to constant scaling of a CMOS technology, there has been an incessant and steady growth in a silicon-dependent semiconductor industry [1]. Though, CMOS devices face many serious issues when scaling of a technology enters a nanometer design a reduction in gate electrode is observed where it loses its control over a channel. The issues include increase of on-current, increased leakage currents, lower reliability and yield problem, huge parameter variations, huge manufacturing cost, etc. To survive the developments made historically, varied inventions in CMOS device materials and its structures are proposed as well as explained in the literature.

To overcome the problems evolved due to scaling the CMOS devices beyond 65nm a new device i.e. FinFET structure is introduced in order to overcome the issues that are discussed above and been faced by CMOS technology designers during the design of a device beyond 65nm. FinFET based devices have been designed for solving the limitation of performance through enveloping the gate electron around the channel in place of keeping the gate electron on top of the channel.

## **1.1History Of CMOS Device**

In 1930, the fundamental term Field Effect Transistor (FET) was been patented in the name of Lilienfeld [2]. He suggested a structure having three-electrode making use of copper-sulfide (Cu2S) semiconductor material. Nowadays, it is called FET. It was finally used with Si-SiO<sub>2</sub> by Kahng and Atalla after thirty years, [3].

At Bell Labs, M. M. Atala and D. Kahng achieved the first successful insulated-gate field effect Transistor (FET) in 1960. This had been extended predictable by prevailing over the surface states which obstructed electric fields from entering into the semiconductor material by Heil, Lilienfeld and Shockley. After examining the thermally developed silicon-dioxide layers, they discovered that these states could be clearly curtailed at the boundary stuck between the silicon and its oxide containing layers of metal, oxide and silicon. This is how it got its name MOSFET, commonly known as MOS. The MOSFET has been integrated into IC's after that and has become the most vital device in the field of microelectronics.

Figure 1.1: Moore's Law

As displayed in Figure 1.1, the count of transistors on a chip doubled every eighteen months in the last few decades. This rapid rate of changed behavior of CMOS advancement, widely termed as Moore's Law, primarily motivated by the scaling of extended MOSFET [4]. This pattern has continued for more than 50 years and will continue till 2020 as per the literature report in 2005 [5]. However, according to the latest update in 2010 to the ITRS, the growth will slow down by the end of 2013. After this the density and count and of transistors will double after every three years [6].

### **1.2 Complications In Scaling MOSFET**

The procedures beginning from a brief review of scaling pattern of bulk MOSFETs based on scaling and throwing light on the challenges to be resolved. Recent advancements to overcome these minute geometry impacts like threshold voltage variations, short channel impacts and increased leakage currents will also be discussed.

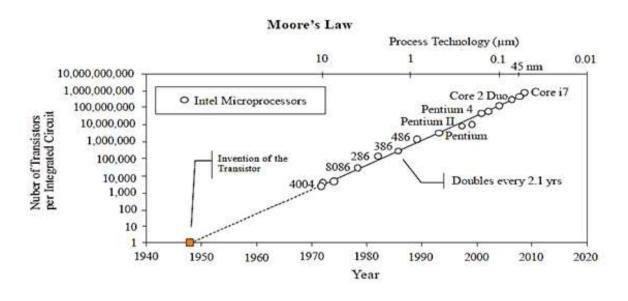

### 1.2.1 Scaling Of MOSFET

The notion of scaling is schematically illustrated in Figure 1.2 showing the doping concentration is scaling up and the device voltages and device measurements are scaled down using the similar feature. As per the electrostatics, the configurations of the electric field will be similar to that of unique device [7].

Using the same behavior, we can scale down a large FET to a small FET very easily. There are set of rules which only provide us a directive that is used to compress a device [8]. However, they will not inform us how small the devices can be made. As the length of a channel get diminishes, a MOSFET current augments while an inherent capacitance gets decreased for a given layer thickness and given supply voltage. Consequently, the switching speed of MOSFET is enhanced. Nonetheless, the device channel length cannot be randomly reduced owing to Short Channel Effects (SCEs) namely punch through, threshold voltage roll-offs, Induced Drain Leakage (GIDL), Drain Induced Barrier Lowering (DIBL), Hot Electron Effect gate etc. We have some other scaling limits enforced by a non-scalability of a silicon energy band gap and a thermal voltage, in addition to a scaling edge of channel length forced by SCEs. Non-scaling of silicon band gap energy results in non-scaling of build- in potential, short channel effect and width depletion. Furthermore, the non-scaling of thermal voltage results in subthreshold non-scaling. The physical aspects which are passed through the different barriers in a MOSFET device are controlled by a quantum mechanical tunneling currents. With the oxide thickness including 2 to 3 layers of SiO<sub>2</sub> atoms is being scaled towards 1.5nm, the oxide tunneling current leads to gate leakage, thus growing the standby power dissipation. Elements of these limitations have been concluded by D. J. Frank et.al [9]. There are different approaches to avoid these scaling limitations, carry on scaling down of MOSFEET without altering the thickness of an oxide; modify the structure of a device to be further scaled down while the effect of short channel is still under control for a physical insulator to have an effective thickness we need to change the material that is used at gate terminal.

As VLSI technology is reaching its edge there are some devices that need to be scaled down further. The three key devices are silicon on insulator, conventional bulk MOSFET and DG MOSFET. Most of the MOSFET's are affected by SCE when they are further scaled down [10]. In SOI MOSFET if it is fully depleted, then in channel region a drain electric field gets penetrated through an oxide layer. For DG MOSFET and bulk MOSFET the conducting layer present at the bottom of a channel can move the electric field away from it. Such that they achieve a better SCE than SOI MOSFET which is fully depleted. Whereas for a bulk MOSFET, the minimum length of the channel can be estimated roughly as [11].

$$L_{min} = 2\left(W_d + \frac{\varepsilon_{si}}{\varepsilon_{ox}} t_{ox}\right) \qquad -----1.1$$

Here  $W_d$  is the width of a depletion layer in bulk MOSFET from equation (1.1), during the scaling down of bulk MOSFET it is observed that  $t_{ox}$  and  $W_d$  both need to be reduced consequently. In bulk MOSFET for reducing the depletion width it requires an advanced doping in the substrate region. A junction capacitance is increased by the elevated doping that is done at substrate there by increasing the band to band tunneling current from a body to drain and declines the sub threshold slope by reducing the carrier mobility. In bulk MOSFET, Gauss law defines the surface electric field by the below equation.

$$\psi_S = \frac{Q_i + Q_d}{\epsilon_{si}} \qquad -1.2$$

Here Qd is the depletion charge concentration and Qi is the reversal charge sheet density. Due to the more amount of charge depletion, MOSFET devices are operated at a higher surface field for same Qi that rise the mobility degradation.

Another area of growing concern in Nano scale MOSFETs device for ON-chip caches is the enhanced leakage consumption, Due to leakage current, consumption of energy for active mode devices is more than 40% [12]. As more number of MOSFETs transistors are packed onto ICs with every passing novel technology era, energy consumption of an active mode will be surpassed by leakage energy. Besides, in an idle circuit, the only source available for energy consumption is leakage. For instance, SRAM cells are principal basis of leakage as most of the transistors in present time's high performance ICs are used for on-chip memory caches [13]. The expansion of innovative robust memory circuit and a low leakage technique is thus, essentially required.

### **1.2.2 Effects of Scaling**

The Short Channel Effects and threshold voltage variation are also important issues for nanoscale MOSFETs and affect directly the device speed, degrades the performance etc. These variations and its effects on MOSFETs are explained below in detail.

### a.Sub-threshold leakage current-weak inversion conduction current

It is defined as the current that flows among the drain terminal and a source terminal that is controlled by diffusion current. When  $|V_{gs}| < |V_{th}|$ . This situation is believed to be a unique feature of a non- ideal MOSFET that acts as switching device, it adds to the leading areas of the stand-by leakage power dissipation. This can be showed through Equation (1.3) [14],

$$I_{subthreshol} = \mu C_{dep} \left(\frac{W}{L}\right) V_T^2 \left( exp \left(\frac{V_{gs} - V_{th}}{\eta V_T}\right) \right) \left( 1 - exp \left(-\frac{V_{ds}}{V_T}\right) \right) - \dots - 1.3$$

Where

$$C_{dep} = \sqrt{\frac{\varepsilon_{si}qN_{sub}}{4\varphi_B}}, \quad V_T = \frac{KT}{q}$$

Here,  $\mu$  is the charge-carrier effective mobility,  $C_{dep}$  depletion region capacitance in the gate area, thermal voltage is denoted by  $V\tau$ ,Boltzmann Constant is represented by K, Absolute temperature is given by T, Electron charge is denoted by q and its value is (1.6×10-19 C),  $\eta$  is the sub-threshold parameter,  $V_{gs}$  signifies the gate to source voltage,  $V_{ds}$  signifies the drain to source voltage,  $V_{th}$  depicts the threshold voltage, W denotes a channel width of MOSFET and L displays the channel length of MOSFET [15].

#### **b.** Threshold voltage variation

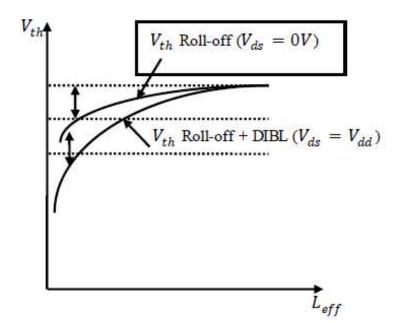

The variants of a threshold voltage (Vt) is correlated clearly with a sub-threshold leakage current and the device speed, which should be decreased and is normally explained in expressions of Vtfalloff (or roll-off). A transistors residing in a wafer with same die have a different length of a channel and threshold voltage. Here reduction in a threshold voltage denotes Vt roll-off, which is result of the reduced channel length. Furthermore, reduction in V<sub>t</sub> increases the drain voltage and it explains DIBL that is shown below in the Figure 1.3. Both the physical processes erupt from lower potential barrier amid the source and a drain because of comparatively increase of chargesharing impact among the source to drain depletion regions and channel depletion region that is compared with a device having a long-channel [16-17]. A transistor is been created by an effect of charge sharing that needs low voltage at gate terminal for reducing the substrate below the gate dielectric by decreasing the Vt that was generated.

In any given technology node like the 90nm CMOS process,  $V_t$  i.e. threshold voltage relies on preference of an oxide and depth of oxide. If the thickness of the oxide is thin the threshold voltage will be low. However, it may perhaps be an enhancement in the performance; it does not come without a price. As the thickness of oxide is thinner for a given device its sub threshold leakage current will also be higher. As a consequence, for 90nm design specification the thickness of a gate-oxide was set at 1nm for controlling the leakage current [18].

This method of tunneling is termed as "Fowler-Nordheim Tunneling" [19]. Basically tunneling effect is the interpretation of a single object moving beyond an occluding object and then reappearing after a certain amount of time on the other side of it where as In Fowler- Nordheim tunneling, during high electric field presence, electrons tunnel through a barrier. Sub-threshold leakage current is the current that drifts from source terminal to drain terminal in an idle condition

of the device. When we reduce the thickness of the oxide, threshold voltage also decreases. This reduction in threshold voltage allows the devices to turn on even in small value of current which normally flows in the device at ideal mode.

$$If_n = C_1 W_L (E_{ox2}) e^{-E_0 E_{ox}} - 1.4$$

Here, Electric field is denoted by Eox which lies across the gate oxide and  $C_1$  and Eo are constants. Before scaling down the features of the design to 90nm, the solution to this problem was to create an oxide thickness by an approach of dual-oxide. In some cases an approach of triple oxide thickness was adopted [20]. For most transistors a single standard thin oxide was used, one more thin oxide is for an input/output driver cells while the third one is for pass transistor and memory cells. These differentiations are based purely on some features of a threshold voltage and oxide thickness of a CMOS based technologies.

Figure 1.3: Voltage VS Channel length

### **C. Short-Channel Effect**

A MOSFET device is termed as short if a channel distance has same magnitude as that of a width of depletion-layer of a source terminal (xds) and drain junction (xdD). It is called as a short channel effects crop up as length of a channel length L and it is reduced to amplify the swiftness of process and the sum of modules present on a chip. [21-22].

Particularly, three different short-channel effects can be distinctly seen:

- i. Drain-Induced Barrier Lowering (DIBL) and punch-through

- ii. Impact Ionization

iii. Hot Electrons

#### i. Drain-Induced Barrier Lowering and Punch-Through

Punch-through takes place when a depletion regions that surrounds a drain extend to a source for merging its layers (i.e., when xds + xdD = L). Punch-through can be reduced by having a larger substrate doping, shallower intersections, thinner oxides and a clearly longer channel [23]. The equations for a width of drain junction and source junction are given below [23]:

$$X_{dD} = \sqrt{\left(\frac{2\varepsilon_{si}}{qN_A}\right)\left(V_{ds} + \phi_{si} + V_{SB}\right)} - \dots - 1.5$$

$$X_{dS} = \sqrt{\left(\frac{2\varepsilon_{si}}{qN_A}\right)\left(\phi_{si} + V_{DB}\right)} - 1.6$$

Here VDB is a voltage at drain-to-body, VSB is a voltage at source-to-body,  $\varepsilon_{si}$  is permittivity of silicon material = 11.7  $\varepsilon_0$ .  $\varepsilon_0$  is the absolute permittivity which is 8.854 × 10-12 F/m, NA is the concentration of the accepter ion and  $\phi_{si}$  is the built- in voltage of silicon material.

The channel's current flow is dependent on producing as well as holding an inverted layer on its surface. In a channel electrons will face a potential barrier which stops the flow of electrons, if the voltage at gate bias is not that sufficient enough for reversing a surface ( $V_{gs} < V_{th}$ ). By cumulative a gate voltage, the barrier is reduced, finally allowing the carrier flow in the channel in the control of an electric field. A potential barrier is operated by  $V_{gs}$  and  $V_{ds}$  voltages in the small geometry MOSFETs [24]. In the channel the potential barrier decreases if there is an increase drain voltage, proceeding to lower the drain- induced barrier (DIBL).Finally the electrons flow in among the source to drain terminals due to the potential barrier reduction, even if the threshold voltage ( $V_{th}$ ) is better than the gate-to-source voltage ( $V_{gs}$ ). Under these circumstances the flow of a channel current is identified as the sub-threshold current [25].

### ii. Impact Ionization

In NMOS, one more short-channel effect takes place in the electrons due to its high velocity in the existence of high longitudinal fields that generates an electron-hole pairs through impact ionization by having an impact on silicon atoms and ionizes them.

This is how it happens. Here drain attracts much of the electrons, whereas the holes move into a substrate region to be a portion of the substrate current. Furthermore, the region amid the drain and a source will work as base of a NPN transistor with a drain acting as a collector and a source as an emitter. Here the holes mentioned above are composed by a source terminal, and the current corresponding to holes generates a drop in the voltage of 0.6 V in a substrate material, a PN junction diode which is reversed-biased will efficiently conduct itself. From source terminal to substrate the electrons can then be inserted, as the electrons get inserted from an emitter terminal to a base terminal. Enough energy is attained as they move towards the drain terminal to create a pair of electron and hole. But the condition can deteriorate if few electrons escape the drain fields that were generated because of the high fields and move into a substrate, due to which other devices on chip gets affected. **[26]**.

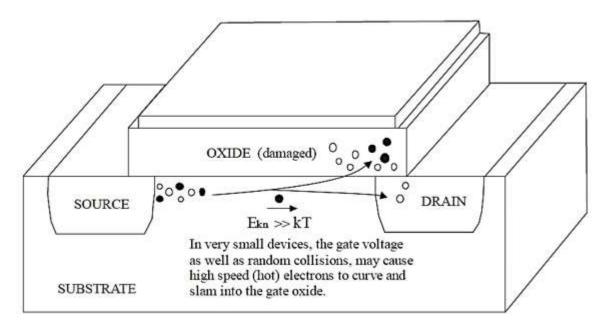

### iii. Hot Electrons

One more term called hot electrons is caused due to high electric fields. Generally, in a PN junction diode flow of electrons will be only in one direction. Normally flow of electrons cannot be either way, since there are junctions both ways between a drain terminal and a source terminal. When voltage is supplied to gate terminal, it produces an electric field below the gate pulling the electrons in and effectively changing the P-type silicon to N-type silicon. In addition, it also allows the current to flow. In the nanometer domain, fields and speeds have gone up, dimensions have shrunk so the electrons in the channels move very swiftly. The field in the gate draws the electrons, so they are pulled towards the gate rather than moving horizontally as depicted in Figure 1.4 [27].

On certain occasions, an electron will strike the oxide barriers quickly enough to partly break through and will ultimately wedge itself in the oxide. When this situation arises, the gate develops a permanent static charge. Depending on the type of device, this can result in the required gate voltage for electrons to either flow up or flow down. If it decreases, leakage currents shoot up and the power usage increases. In such a case, the previous device must supply a larger gate-source voltage difference whereas the chip will require a higher power rail. This is one of the most ordinary failure modes for devices and only one who faces consistent problems knows. Many of such problems have arisen in the nanoscale MOSFETs like scaling, threshold voltage variation, sub-threshold leakage current and short channel effects. For overcoming these problems, advance MOSFETs like Double Gate, Triple Gate MOSFETs and FinFET devices are used. [28]

Figure 1.4: Hot Electron Effect

## **1.3Types Of MOSFETS**

Novel technologies have been presented for continuous scaling of planar MOSFET device past the 60 nm. These comprise gate stacks of HK/MG and a technology based on channel stress (e.g. strained-silicon substrate [29], engravved-Si1-xGex (Si1-xCx) for a p and n-channels MOSFETs and raised source/drain [30-31]).

Meanwhile a channel region which is heavily doped or a halo doping is required by a planar bulk MOSFET in order to subdue the DIBL and a short channel effect it will suffer with a RDF effect. In order to avoid the usage of a heavy channel doping in recent years a new technique is been introduced called as Multi-gate transistor structures. [32].

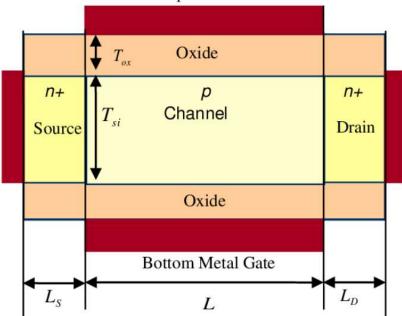

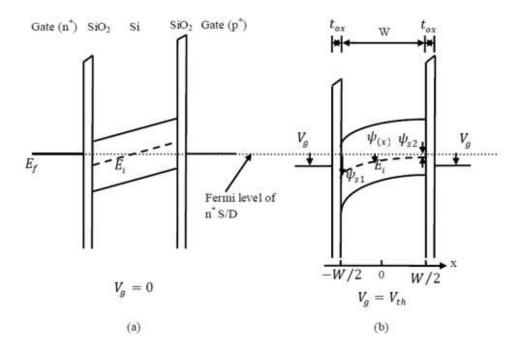

# 1.3.1 Double-Gate MOSFET (DG MOSFET)

A generic N-channel DG MOSFET schematic exhibited in Figure 1.5. Arrow in figure denotes the gate dielectric layer (and spacer),  $t_{ox,f}$  is thickness of a front gate dielectric layer and  $t_{ox,b}$  is the thicknesses of a back gate dielectrics layers and  $t_{si}$  is the silicon body thickness. In a DG MOSFET, the channel is controlled by two gates such as; a front gate (Vg,f) and a back gate (Vg,b). This reduces the drain field impact on the source, thus resulting in a reduced Short Channel Effect (SCE). Owing to the increase in share charge from source terminal to drain terminal there will be a shrink in length of the channel and there is a decrease in threshold voltage due to the gate voltage control. Hence, a reduction in threshold voltage occurs with a decrease in a channel length and Drain Induced Barrier Lowering (DIBL). These factors are noteworthy concerns and need to be taken care to provide the protection against a Short-Channel Effects (SCEs) [33-34]. A novel technique called Dual Material Gate (DMG) MOSFET was designed and suggested for improving the immunity in contrast to short channel effects. [35-38].

Top Metal Gate

Figure 1.5: Double Gate MOSFET

A Double Gate MOSFET having same thickness and material for a front gate electrodes, back gate electrodes and a dielectric material is named as symmetrical DG MOSFET. Conversely, a DG MOSFET that is not a symmetrical DG MOSFET is called an asymmetrical DG MOSFET [39].

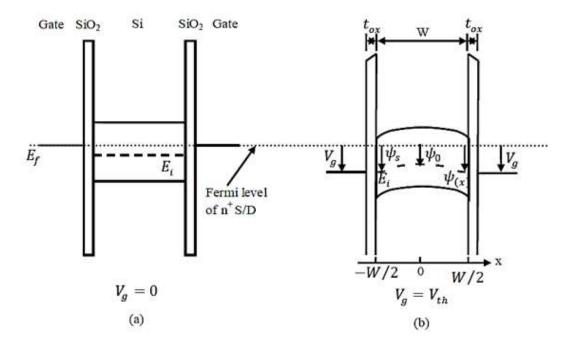

Figure 1.6: Energy Band of DGMOSFET

The two gate biases at a channel with their energy band illustrations for both symmetrical, asymmetrical DG MOSFETs are exhibited in below figure 1.6 and Figure 1.7. In a symmetrical DG MOSFET having a gate electrode at mid-gap, in a sub threshold region there exist flat bands in silicon, with a constant carrier concentration throughout the channel. When the gate bias is high the bands turn downwards in silicon region near to the sidewalls. When the bands are turned near or over the quasi Fermi level sufficiently, the density of the carrier near the sidewalls increases greatly. Thus, the transistor is powerfully inverted. Several definitions describe a precise inception of a robust reversal. The threshold voltage (Vth) is the gate bias that corresponds to an onset of a strong inversion [40].

Figure 1.7: Energy Band of Asymmetrical DGMOSFET

## **1.3.2 Triple-Gate MOSFETs (TG MOSFETs)**

A silicon body which is wrapped by gates and it is a non-planar narrow transistor is known as Triple-Gate MOSFET [41]. In this the gates control the two channels i.e. a top horizontal channel and a lateral channels. This MOSFET is made up of a thin film comprises of thin silicon base having a gate terminal on three edges.TG-MOSFET transistor find it's applications in a fully depleted transistors ideally. A TG MOSFET substrate has a thin body of semiconductor on it, with a gate dielectric on the top of surface and on the side walls of it. On a semiconductor body source region and drain regions are created at an opposite side of a gate electrode. A transistor has three distinct channels and gates because three sides of a semiconductor body is enclosed by a gate dielectric and gate electrode [42]. Here width of the transistors gate corresponds to the sum of three individual sides of a semiconductor body. A TG MOSFET 3D structure has been depicted below in Figure 1.8 that explains the dimension of a basic transistor.

Figure 1. 8: Triple Gate MOSFET

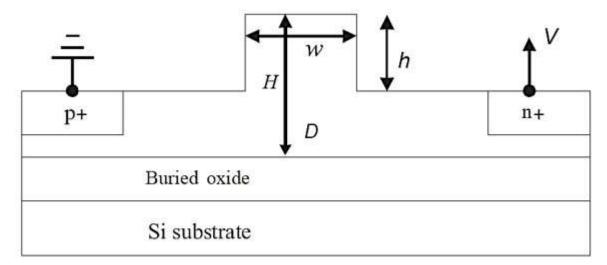

### **1.3.3 SOI MOSFET**

Silicon on Insulator (SOI) technology includes a usage of layered silicon-insulator i.e. instead of using conventional silicon substrate it make use of silicon substrate during the semiconductor manufacturing, specifically in microelectronics in order to progress the performance by reducing the parasitic capacitance of a device.[43]. SOI-MOSFET devices are different from conventional based silicon devices. This is for a reason that the electrical insulator is just below the silicon junction i.e. either a sapphire or a silicon dioxide. The selection of an insulator purely based on a proposed design application, like for short channel effects we can use silicon dioxide in microelectronics devices and for a high performance based radiation-sensitive applications and Radio Frequency we can use sapphire [44]. The top most silicon layer and the insulating layer also vary widely due to application [45]. Benefits of SOI MOSFETs over conventional MOSFETs are: due to isolation of bulk silicon a lower parasitic capacitance will enhances the consumption of power at matched performance; Due to complete isolation of both p-well and n-well there is a resistance to latch up; working on lower VDD and higher performance at equivalent VDD; Because of non-doping present there is a reduction in temperature; better wafer utilization, decreased antenna concerns; better yield due to high density; no need of well taps or body taps; due to isolation the leakage currents are lower with a high power efficiency; inherent hardened radiation (it is resistant for soft errors), need of a redundancy is reduced.

SOI MOSFETs manufacturing is well-suited with a most conventional fabrication process [46]. Generally, an SOI-based process can be applied without a help of any specific device. The main obstacle in the implementation of a SOI is the substrate cost which is increasing drastically, that leads an estimated increase in the value 10–15% of an overall manufacturing costs [47].SOI based MOSFET devices are used by the computer industry. SOI devices are basically of two types: PDSOI (Partially Depleted SOI) and FDSOI (fully depleted SOI) MOSFETs [48]. For an n-type based PDSOI MOSFET, a p-type film which is inserted in between a buried oxide (Box) material and gate oxide (tox) material is large; therefore whole p region cannot be covered by the depletion region. PDSOI up to some extent acts similar to a bulk MOSFET. FDSOI is more advantageous compared to bulk MOSFET. In FDSOI devices, as it contains a thin film so it covers a whole depletion region. A front gate (tox,f) supports a less depletion charges compared to the bulk MOSFET in FDSOI so inversion charge get increases which helps to achieve a switching speed at higher rates. Other disadvantages in a bulk MOSFETs are high sub-threshold slop, threshold voltage roll off, body effect, etc. and are decreased in Fully Depleted SOI because the source electric field and drain electric fields may not be able to interfere with each other due to Box. In PDSOI the main fault is a "Floating Body Effect" (FBE) as the film in it is not associated to any of the given supplies. The 3D-structure of a SOI MOSFET is shown in Figure 1.9.

#### Figure 1. 9: SOI MOSFET

In Bulk silicon MOSFET, parasitic capacitances between drain / source junction and interconnects are formed which degrade the performance of the circuit. Latch up was also a serious issue for bulk CMOS circuit [49]. In Figure 1.9, a buried oxide layer has been introduced between the substrate and p+n+. With this implementation, junction capacitance is found to be smaller than the bulk silicon MOSFET. Other than this advantage, SOI MOSFETs provide latch-up free CMOS

technology, and has an ability to get operated in harsh environments having a higher radiation rate and high temperature, operated at a low voltage, etc. [50].

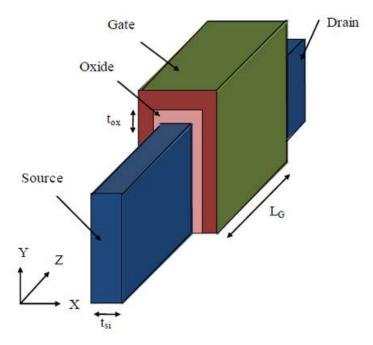

### **1.3.4 FinFET Devices**

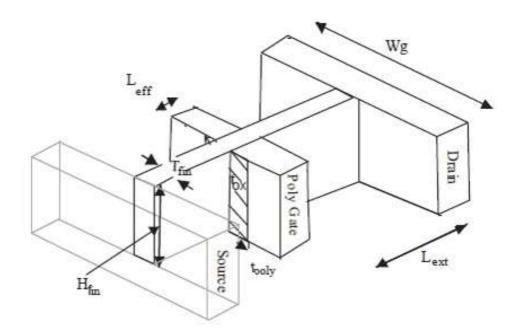

It is difficult to fabricate planar DG MOSFETs [51-52]. The difficulties faced are alignment of a gate at top region and bottom region and to make a low resistance contact with a gate at bottom region. Another variation of a DG MOSFET is fabricating it easily as FinFET [53-54]. Figure 1.10 depicts a FinFET structure. In order to construct a DG FinFET the oxide present on top is abundant denser than the side walls to disable the top gate effectively.

Figure 1.10: FinFET 3D View

Evidently, a double-gate FinFET width is defined by an equation as W = 2Hfin + Wfin. In most of the cases, to have a short channel effect sufficiently smaller, Wfin is of a small order. Moreover, a top gate in DG FinFET is ineffective so, W is nearly 2Hfin. Accordingly, the behavior of FinFET device turns out to be large, same like a DG MOSFET. Thus, the literature that been studied gives the compact idea of designing a DG MOSFET's model and it can be easily implemented with a small adjustment of parameter i.e. (Hfin) to FinFETs, as it is done in [55].

An extension region in fin is a long narrow portion that is not in the gate. This region is technologically unavoidable because there is no probability of having a doping gradient of steep lateral, which starts from a highly doped region and ends at lightly doped region. Basically a body that is blithely doped is chosen as it will decreases the corner effects [56- 58], effect of a mobility degradation and a random dopant fluctuations. Therefore, FinFET devices typically will have large parasitic series resistance.

# **1.4 Memory Organization**

Address Decoder-Y Matrix X-bpog Word Sense amplifier Data

Memory organization mainly consists of three basic parts as shown in Figure 1.11

Figure 1.11: Memory Organization

At first the actual data is stored in cell matrix in word format whose length is predefined. Based on the two inverters and there positive feedback loop the data is stored in cell. The positive loop here provides the static retention of data without refreshing it. In order to access the cell we do it through bit lines to a sense amplifier. Here sense amplifier is the secondary part of a cell matrix used for translating a signal with low swing i.e. generated on a bit lines by a cell to a digital signals having full levels. Decoder is a third main part used for decoding the given address into a physical position. Some other peripheral circuits like timing and control unit, write system and pre-charge system are needed. One of the critical situations is to activate all the subcomponents at a particular time in the given memory. As it play a dynamic role in the functionality of device, consumption of power, delay in memory. A word line that is turned ON will cause an access of wrong address. If it is turned ON late it will have a delay of overall memory. The timing of activating a sense amplifier is critical, as if the activation is done too soon, will prompt a bit-line pair to generate the differential voltage i.e. needed. Throughout a write process all the bit lines will be fetched to correct levels before the pass transistors are enabled. For a conventional cell, one of the bit line is discharged fully whereas the complementary vit line is kept high. [59].

# **1.5 Conventional SRAM Cell**

The SRAM cell includes a latch consisting of 2 inverters which are connected cross coupled, such that it need not be refreshed periodically to retain the data that is stored. Based on the condition that for a given SRAM cell an ample of power supply voltage is present. [60-61].

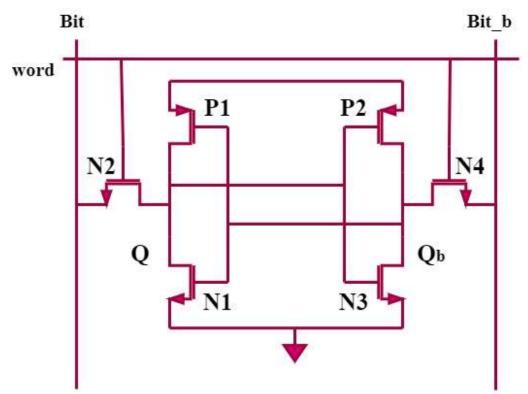

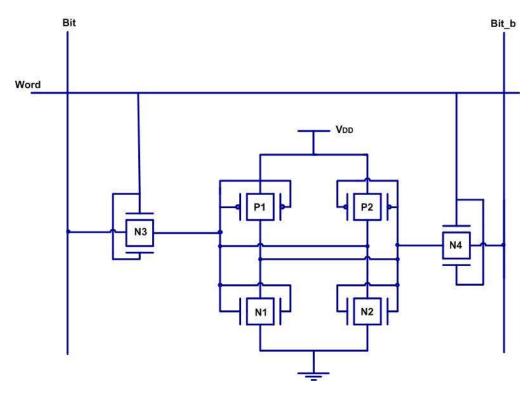

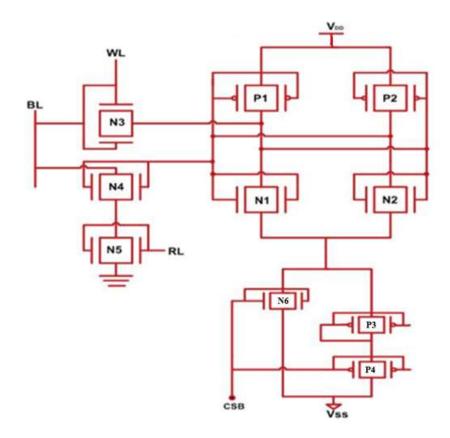

Figure 1.12: 6T SRAM

A 6T SRAM is shown in Figure 1.12 which has 2 inverters connected to each other and 2 more transistors which decide the functionality of these two inverters. The two transistors N2 and N4 are connected to a bit and bit\_b line and both together are connected to word line. [62-65] Here a read, write and hold operations are performed depending on the modes of selection of the bit and bit\_b lines. And data input to the device depends on the bit given through word line.

# 1.6 Research Gap

The prediction of device performance of FinFET structure for SRAM cell design, simulation of 2D/3D device is inevitable. In some research papers, FinFET 2D/3D model has been proposed, and a detailed study of output characteristics variation with process parameters variation, device structure, temperature effect, etc have been not carried out.

To the best of our knowledge, very few research papers have actually dealt with the leakage aspect of FinFET. The study is critical in order to analytically estimate simulation otherwise the power dissipation of Fin FET is under bias. Band to Band Tunneling (BTBT) and Evaluation of Edge Direct Tunneling (EDT) have not been reported extensively for the FinFET device.

It is felt that the conventional bulk CMOS SRAM should be preceded by Nano scale semiconductor novel devices in order to appreciate the qualitative behavior of FinFET under various bias/process condition. There are few reported research papers in the area of process variation which are aware of the SRAM cell based on FinFET. No advanced SRAM cell has been proposed for FinFET based structure.

The study of advanced SRAM cells i.e. 7T, 8T, 9T, 10T and 12T SRAM under all conditions of temperature/process parameters variation would be required for determining the driving capability of FinFET structure for low power applications. At subsystem level, very small number of work has been reported on FinFET based SRAM design with process variation and temperature effects. Most of the papers in this area are based on fabrication/process technology for generation of SRAM cell by bulk MOSFET or DG MOSFET. The Static Noise Margin (SNM) has been reported in number of papers but its variation with process parameters and device structure is not elaborated. The evaluation of RNM and WNM is highly appreciable from stability point of view.

There are possibilities to extend research work in all area of work, as no work is complete as knowledge is infinite. To go further, we briefly point out some directions in which further research may be carried on.

- i. The analysis of FinFET device structure with single Fin is available. Multi-Fin FinFET device can be used to enhance the driving capability of the device. However the fabrication techniques required to meet such stringent guidelines would be an issue which can be looked into in future.

- ii. The available design of FinFET based SRAM cells, gave reasonably good results.However, if even better results are required then technology must be scaled down.

- iii. A substantial decrease in leakage current and power dissipation has been witnessed in available SRAM cells. As the leakage will be more significant in scaled down technology like 18nm, so this work further may be extended to scaled technologies such as 7nm or beyond.

- iv. There can be several other leakage reduction techniques apart from those which are proposed. So in order to further improve the performance, new leakage reduction techniques may be proposed and implemented for future work.

- v. The different spacer materials can change the potential modeling and hence various leakage components estimation is expected to change in FinFET device. This might be a good area of further research.

# **1.7 Research Objectives**

The objectives of the proposed research work are as follows:

- Analysis and design of advanced SRAM cell (i.e. 7T, 8T, 9T, 10T, and 12T) based on CMOS and FinFET device in Nano scale domain.

- Performance evaluation of FinFET based SRAM cells at 18nm technology node for low power applications.

- 3. Modelling and estimation of total leakage current in Nano scale FinFET based SRAM cell considering the effect of parameter variation using different leakage reduction techniques.

# **1.8 Thesis Organization**

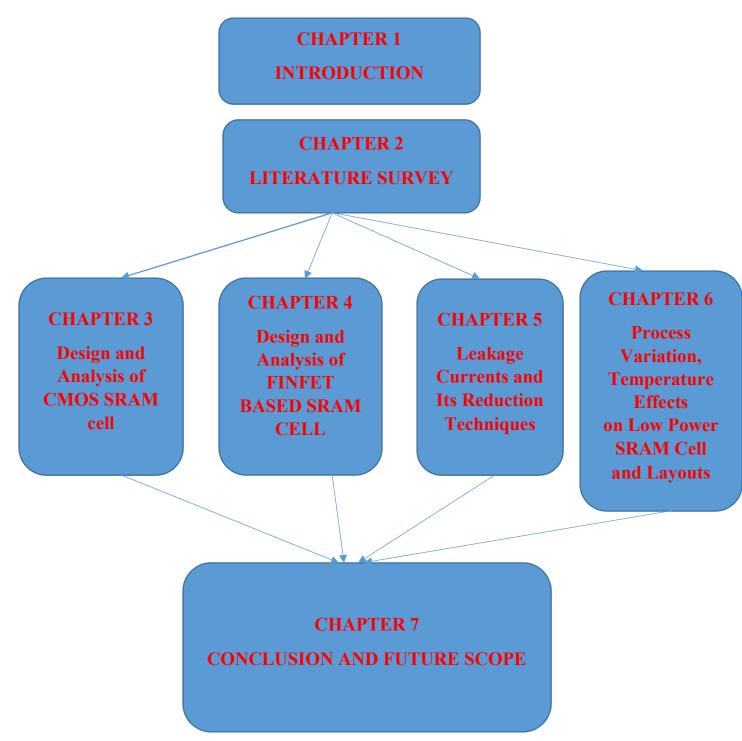

A Continuous literature survey was done for identifying the problems associated in convention SRAM cell and also the problems associated with scaling of MOSFET. And the alternate devices for MOSFET that can replace the devices and with great stability, speed and low power consumption. The existing gaps were identified related to the existing architectures through the literature survey and are presented in Chapter 2.In Chapter 3 the design of 45nm CMOS based 6T, 7T, 8T, 9T, 10T, 12T SRAM is done and analysis of these SRAMs in terms of SNM,Power consumption is done . In Chapter 4, the study of 18nm FinFET based 6T, 7T, 8T, 9T, 10T, 12T SRAM is illustrated. Various leakage reduction techniques are proposed in Chapter 5 to reduce sub-threshold and total leakage current on different FinFET based SRAM cell. In Chapter 6, effects of process variation on SRAM and layouts of 6T, 7T and 8T have been explained and the outcome

of temperature on power consumption is also presented. Finally, conclusion and future scope are presented in Chapter 7.

Figure 1.13: Thesis Organization

# **1.9 Chapter Summary**

In this Chapter, scaling trend of advanced commercial chips from 1950 to 2020 is identified. We have clearly observed the evolution of the microprocessor from 4004 to Core i7 with the increment in number of transistors per Integrated Circuit. To achieve this, the size of the transistor is reduced which further acts as a challenge for Nanoscale MOSFETS. These challenges influence the performance of the MOSFET based SRAM cells particularly below 65nm technologies. To overcome these challenges, various advanced MOSFETs were introduced such as DG-MOSFETs, TGFETs, SOI MOSFETS, FinFETs, etc. FinFET has been chosen as a transistor of choice because it is not affected by Short Channel Effects. The problems with FinFET have been observed and accordingly objectives have been decided.

# CHAPTER 2 LITERATURE SURVEY

Over a year there is an increase in the cache memories that are designed based on SRAM used for different applications that requires high speed such as multimedia devices, mobile phones and few portable devices. As we know that in an integrated circuit the major concern is speed and low power performance at a Nano scale technologies as demand of VLSI chips is increasing in computing devices mobile communications. As there is an increase in battery powered smart devices and its usage is wide spread similarly a Nano medical devices, where a low power is turned to be a big problem for system on chip design (SOC). For analyzing a SOC, a low power based SRAM is considered as it occupies a large portion in SOC chip and increases the overall power of the device. If a SRAM cell is used at higher frequencies it will consume more power and if we use SRAM cell for less speed applications then it will consume a negligible power. There are various techniques in SRAM based cells for managing the power.

# 2.1 FinFET Device

Kumar Gupta et al. has discussed a problem based on conventional planar MOSFET that are shrinking more when compared to CMOS devices in a nanoscale regime. In transistor one of the limit that effects the scaling is short channel effect (SCEs). Some effects like Gate Induced Drain Leakage (GIDL), hot carrier effects, Vth roll off, sub-threshold leakage, gate direct tunneling leakage, Drain Induced Barrier Lowering (DIBL) will result in degrading the performance of a BULK CMOS device. Different methods like a shallow source/drain junctions, having a high channel doping with a thin di-electric gate electrics that are deployed for improving the control on gate and thereby enhancing a performance by scaling down the gate length. With a reduction in power supply, hot carrier and power effects are downgraded but it will degrade the performance, and it can be improved by decreasing the threshold voltage Vth, but it will affect the leakage obtained at Source/Drain terminals. [66].

The thickness of oxide can be reduced by decreasing a DIBL and will increase the adequate channel control with a change in gate terminal but it also increase the leakage current produce at gate terminal. [67]. Hence solving one issue will create another issue. Hence efforts are made to for finding a high K gate dielectric by a thick oxide which will reduce a gate leakage, and will

have a sufficient control on channel. A problem based on band alignment and instability problem of band is studied by various researchers for replacing a metal gate electrode by a polysilicon [68-69] and here insufficient activation will rise the poly depletion effects.

Here based on various work functions a metal gate has not been founded. In its absence a poly silicon gate can be used wherever the threshold voltage is established to high by doping the channel. It leads to a Random Dopant Fluctuations (RDF) (where length of the gate is small) it will reduce the mobility with an increase in impurity scattering. So , it is strongly recommended that in place of planar MOSFET a Field Effect Transistor (FET), Fin Field Effect Transistor (FinFET), Ultra-thin body (UTB) and Double- Gate Metal Oxide Semiconductor Field Effect Transistor (DG MOSFET) may be used for continuous scaling down of gate length to 32 nm technology [70]. FinFETs devices are utmost promising devices instead of other bulk CMOS devices at nanoscale regime as they have double gates in it. These two gates can be independently organized to decrease the leakage or to enhance the performance or to decrease the count of transistor used for a design. [71].

Figure 2.1: FinFET Device

Here author has proposed a novel model of schottky MOSFET i.e. double gate metal source/drain (MSD) and simulated it. The designed structure novelty is it realizes a CMOS inverter completely,

that is generally realized by grouping MOS transistors a P-type transistor and N-type transistor in conventional CMOS technology. By using the designed structure we can reduce the number of transistors used for an implementation of sequential and combinational circuits and also regions and junctions required are reduced when compared to CMOS technology. Hence a designed device is termed as Sajad-Sunil-Schottky device (SSS) and its design is compact and also consumes very low power. For proposed design a mixed mode circuit analysis has shown that a conventional CMOS inverter with logic level high i.e. (V<sub>OH</sub>) as V<sub>DD</sub> and low logic level i.e. (VOL) as GND. [72]

In paper [73], for improving the Figure of merit an exploration of a (Dual-KS) Trigate FinFET structure was used by considering only source for operating low power devices at gate length of 20nm, it is observed that the design rises the combination of gate and underlap region to source side and also improves an output conductance ( $g_{ds}$ ) and trans conductance ( $g_m$ ). During the observation it is found that at drain it increases the coupling of gate field to an underlap region to drain side and that makes the drain field to move away from a gate by improving the output conductance ( $g_{ds}$ ) only when there is an increase in miller capacitance. [73]

Fin type FET's are most favorable alternate for a bulk CMOS devices at nanoscale operation. In general FinFET's are termed as double gate devices. Here the FinFET dual gates are shortened for achieving a high performance and the gates are controlled independently to achieve low leakage current or to decrease the number of transistor. This parameter will also give a compact design. This particular paper gives an overview on different set of design styles of FinFET logic, novel design and its layout's. [74]

In this paper a FinFET architecture that has been designed at 22nm has provided an improvement of MOSFET electrostatics and also enable L gate i.e. length of gate and it is scaled down at 48-nm technology, contacted gate pitch (CGP) scaled down at 7 nm technology by "Fin Effect" an enhanced performance gain has been achieved that has improved a drive current for the applied load capacitance. An approach on limiting the thickness of Fin is on study that will limit the scaling of L gate further and results in the size reduction of source and drain with CPP. An increase in the combination of L gate plateau and Fin effect place an extreme force on the conduction of vertical path from contacts towards source/drain. Based on contact resistivity values for a metal layer to dope the silicon degenerately of  $-2 \times 10^{-9}$ . The performance of FinFET will drastically decreases below -40nm that of CPP, while an ohmic floor of  $\sim 1 \times 10^{-10} \Omega$ -cm<sup>2</sup> can push the CPP under 30nm. Therefore from this a conclusion is made that electronic industry will have high pressure for adopting a novel architecture for designing a circuit or for scaling it in CPP region of 30-40nm, for carrying the benefits of power and performance of CMOS device scaling. [75]

In FinFET a scalable model and analytical model for a threshold voltage is developed by a 3-D Poisson equation and solving it by various techniques, as the model is based on an investigation of transmission path and a movable charge need be solved that was considered in Poisson 3D equation. Whereas the threshold voltage is termed as a voltage charge density. As the FinFET has a 3-D basis and a design model has an influence of short channel and roll off the threshold voltage and DIBL effect. A 3-D simulation of FinFET is observed. [76]

As CMOS basic IC technology scales down to a 14nm technology and sub 14nm technology based on Moore's law, one of the most favorable architecture selected is Si-Bulk FinFET as it has quiet few advantages as high transmitter performance, low leakage and high density. Thought the length of gate continuously scales down, a short channel effect and rolling of Vth is a serious issue that needs to take care off. This paper demonstrates two different mechanism, where a n-type FinFET are induced by a fluorine diffusion from a tungsten to a gate layer which is of metal and in situ a high phosphorous is deposited that will give a meaningful development of FinFET beyond 14nm technology.[77]

As planar MOSFET faces an issue of getting scaled at nanometer regime, FinFET devices and Trigate FET's have emerged as there successor that owns two or three gates in it and are capable to handle the short channel effect better than a general MOSFET structure at deep scaled down technology and enable for continuous scaling of transistor. Here a review is done on FinFET from device level to architecture level based on the various types of FinFET and it is possible asymmetric, their impact, novelty and trade-offs. [78]

When compared with conventional MOSFET, a FinFET based device is more suitable for decreasing the leakage current and power dissipation by improving the performance. While to move forward with parameters such as performance, integration, low-power and stability. A perfect FinFET is the solution for designing a SRAM cell. A proposed nanoscale based FinFET at

low-power 6T SRAM is been designed at 32nm and 45nm technology in Cadence Virtuoso Simulator.

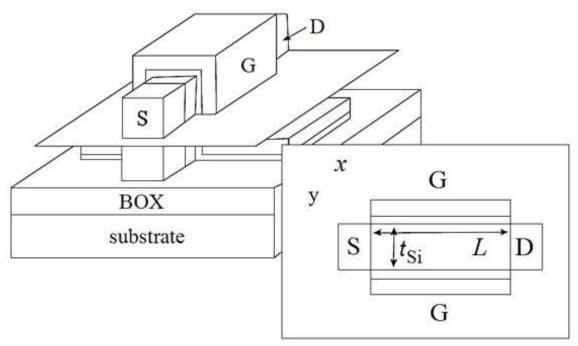

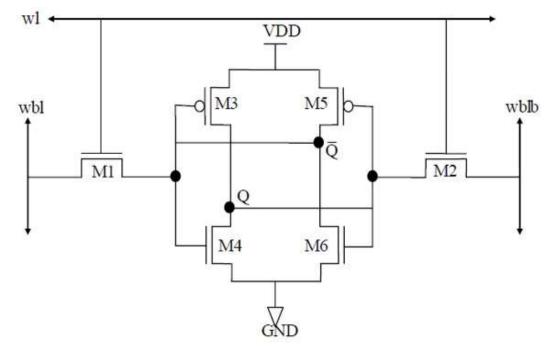

# 2.2 Conventional 6T SRAM Cell

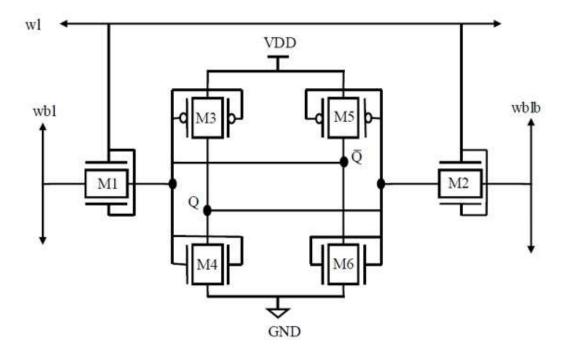

A conventional 6T based SRAM represented in Fig 2.2, consist of dual transistors that remain cross coupled and two excess transistors; here an inverter is crossly coupled and it is called as latch. Here two inverters that are cross coupled consist of four transistors (M3, M4, M5 and M6), where an each bit is stowed on all four transistors. M1 and M2 an excess transistor has its source terminals connected to input latch whereas drain terminals of transistor is connected to the Write Bit Line (wbl) and Write Bit Line Bar (wblb), and when Word Line is made low (wl = 0), the bit lines will be detached from a latch by turning OFF the excess transistor. During this state a latch will able to hold a bit as long as voltage is  $V_{DD}$  and GND. When a Word Line is made high (wl = 1), the bit lines (wbl and wblb) both are attached to latch and excess transistor will turn ON. At this point the bit lines will transfer the data for both the operations read and write.

Figure 2.2: 6T SRAM

# 2.3 Design of 6T SRAM Cell using FinFET Device

Here a FinFET is proposed for low power based robust SRAM's that has an unequal drain doping and source concentrations i.e. asymmetrically doped FinFETs. Where an effect of its doping on characteristics of device is examined and the elementary changes among conservative FinFETs and AD FinFETs are shown. In device an asymmetry leads to an unequal current for both drain biases i.e. positive and negative and it exploits for achieving easing of read-write conflict in 6T SRAMs. A proposed design exhibits a higher short channel features related to a conventional FinFET because of reduction in electric fields from a terminal which has low doping and will result in a low leakage current. [79]

In conventional 6T SRAM few of the major challenges are reducing the leakage current, power dissipation by enhancing the performance of design. Figure 2.3 shows the displays the advised structure of 6T SRAM cell by using a Double Gate FinFET device. A proposed design of SRAM having 6T will reduce power dissipation, leakage current and has improved the performance too. Hence it is clear that optimizing a FinFET device properly is essential for leakage reduction and to provide stability. Therefore a supply voltage ( $V_{DD}$ ), threshold voltage ( $V_{th}$ ) optimization and Fin height Hfin is applied FinFET based SRAMs for leakage reduction thereby increasing the Fin height that reduces a supply voltage ( $V_{DD}$ ) [80].

As  $V_{DD}$  gets reduced there will be a negative effect on stability of cell with various parametric variations. Thus an optimization technique is required by a FinFET for reducing a standby leakage current and for improving a stability in design of SRAM cell.[81].

SRAM contains a significant proportion of area and power that is used as cache memory in all VLSI chips and in SOC. It is considered as more intense handy devices and the processors that are high end. SRAM plays a vital role in world of microprocessors as there is scale down in technology in nanometer mode. The problems that affects the SRAM are leakage power, leakage current and delay present for low power based applications. Hence with a use of low-power FinFET SRAM based cell for handy operated devices a faster speed, improved battery life is accomplished. A key objective of present paper is to reduce the delay, power consumption in a desired nanoscale 6T FinFET SRAM cell structure [82]

SRAM cells based FinFET are used in memories that need a shorter access time having a low tolerance to the atmospheric conditions with less power dissipation. Such SRAM cell are most popular because of its lower dissipation among various circuits and there configurations based on logic processes. Moreover it offers a high noise margin with high switching speed.[83].

Figure 2.3: FinFET based 6T SRAM

#### **2.4 Design Problems in Conventional SRAM**

One of the key obstacles in 6T based SRAM is both a read operation and writes operation doesn't go hand in hand. Here cell that has read of lower Static Noise Margin (SNM) will leave an improved write ability and vice-versa. Hence if a decoupling is provided between a read and write operation then a designer will have flexibility for optimizing the operations read and write independently.

In previous SRAM proposed on average-8T is having a modest area such that it doesn't require a scheme of write-back. Its architecture has bit line (BL) and it is directly attached to gate terminal of read buffer and is succeeded by a boosted voltage of word line (WL). Though, in an average 8T based SRAM of 22nm based FinFET there is a large threshold voltage variation and voltage appeared at WL is not used as it will degrade the read stability. Hence, we cannot achieve the full-swing output, gate terminal of a read buffer will not able to drive Vdd which causes an increased read delay.[84]

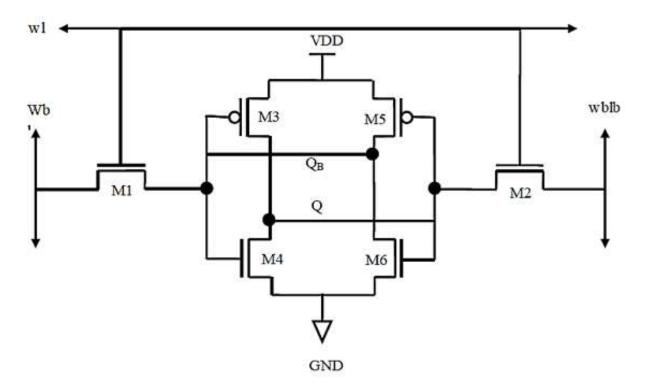

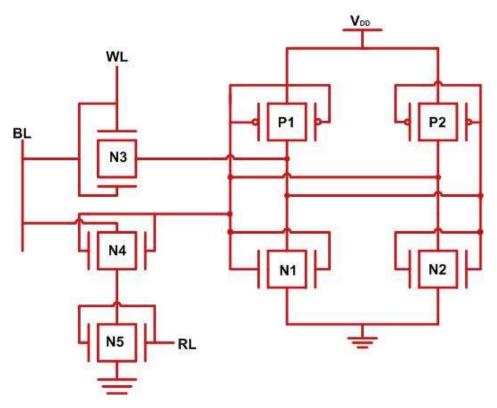

Here in the present paper a 7T based SRAM is proposed and then designed as shown in Figure 2.3 with a single ended read and differential write operations that work near to threshold region. The proposed structure is a modification of 5T cell that uses low and high threshold voltage transistors for improving the stability to read and write. For enhancing a RSNM by maintaining a low write time and high write time, n additional transistor used known as access transistor by setting the threshold voltages of it, and for maintaining cell's low leakage power we need to increase a ratio *Ion/Ioff* of an access transistors and a high *VTH* will be used for pulling down a cell path. For evaluating the efficiency of proposed design, the features of a proposed design are matched with 5T, 6T, 8T, and 9T based SRAM. [85]

A SRAM cell design based on nanoscale regime is becoming challengeable increasing day by day due to its more leakage power, weak write ability and a degradation of data stability and intensified process variation parameter in every generation of a CMOS technology. A new technique termed as asymmetrically ground-gated seven-transistor (7T) based SRAM cell was planned that provides high data stability and a low leakage current and also has a sleep mode. A proposed method has an enhanced data stability of 7.03x for reading operations and 2.32x for idle status and it is compared with a 6T based SRAM designed at 65 nm based CMOS technology. Here in 7T SRAM cell for transferring data a specialized circuit for write assist is designed. [86]

Here In the paper, a new design of SRAM cell having 8T based on a Si technology that provides a low leakage power when compared to conventional design. Its design consists of fully functional design that has small supply voltages when compared with 6T based SRAM. In order to verify a design of a proposed system a 32 kb of SRAM cell is considered and simulated in 90nm based CMOS technology. During the operation of circuit at V<sub>dd</sub> minimum simulation results show an improvement of 58% during write operation, 67% during read power per operation. During a write operation a half selection challenge is overcome by a low power internal write back scheme.[87]

For most of the performance oriented applications a near threshold voltage (Vth) based operation will be an effective method. For SRAM cells its get affected due to circuit stability. Hence a near threshold voltage based 9T SRAM is implemented at 22nm based FinFET technology. In this cell read stability is ensured by a read buffer by decoupling a stored node from a read bit line and thus improves the read performance by using a single transistor path of read. In read buffer with the elimination of sub threshold leakage will reduce the standby power and energy a new method of