# DESIGN OF A NARROW BAND GAP MATERIAL HETEROJUNCTION TUNNEL FIELD EFFECT TRANSISTOR WITH IMPROVED SHORT CHANNEL PARAMETERS

A Thesis

Submitted in partial fulfillment of the requirements for the award of the degree of

## **DOCTOR OF PHILOSOPHY**

in

**Electronics and Communication Engineering By**

Irfan Ahmad Pindoo 41700104

Supervised By

Dr. Sanjeet Kumar Sinha

LOVELY PROFESSIONAL UNIVERSITY

PUNJAB

2021

**DECLARATION**

I hereby declare that the work being presented in this thesis report entitled "DESIGN OF

A NARROW BAND GAP MATERIAL HETEROJUNCTION TUNNEL FIELD

**EFFECT** TRANSISTOR WITH **IMPROVED SHORT CHANNEL**

PARAMETERS", is an authentic record of my own work carried out in fulfilment of

requirements for the award of degree of Doctor of Philosophy in Electronics & Electrical

Engineering at Lovely Professional University, Phagwara under the supervision of **Dr.**

Sanjeet Kumar Sinha, Associate Professor, Department of Electronics and

Communication Engineering. The matter presented in this thesis has not been submitted

elsewhere in part or fully to any other University or Institute for the award of any degree.

Irfan Ahmad Pindoo

Registration Number: 41700104

School of Electronics and Electrical Engineering

Lovely Professional University

Phagwara, Punjab, India.

## **CERTIFICATE**

This is to certify that Irfan Ahmad Pindoo (Registration Number: 41700104) has completed objective formulation of his thesis titled, "DESIGN OF A NARROW BAND GAP MATERIAL HETEROJUNCTION TUNNEL FIELD EFFECT TRANSISTOR WITH IMPROVED SHORT CHANNEL PARAMETERS" for the award of degree of Doctor of Philosophy in Electronics & Electrical Engineering at Lovely Professional University, Phagwara under my guidance and supervision. The matter presented in this thesis has not been submitted elsewhere in part or fully to any other University or Institute for the award of any degree.

Dr. Sanjeet Kumar Sinha

Associate Professor

Department of VLSI Design

School of Electronics and Electrical Engineering

Lovely Professional University

Phagwara, Punjab, India.

## **ABSTRACT**

The device dimensions have now crossed the nanometer scale, thanks to continuous advances in complementary metal oxide semiconductor (CMOS) technology. This miniaturization has been made possible with the scaling of the device parameters as per Dennard's rule of scaling. As the size of the transistors go below 100 nm due to the scaling, it becomes a tough task for a transistor to switch the state form OFF to ON or vice-versa, without the significant power dissipation. Further, some short channel effects are also getting introduced like a drain induced barrier lowering, leakage current, subthreshold slope conduction, etc. into a picture. Thus, it becomes difficult to switch from OFF state to ON state while maintaining smaller supply voltages. This is mostly due to a metal oxide semiconductor field effect transistor's physical limitations (MOSFET). The current transport mechanism in a MOSFET is based on the thermal injection of electrons. Thus, it can be concluded that the simple miniaturization of transistors with the continuous CMOS scaling will not help in improving energy efficiency. This has compelled researchers to explore the new architectures with better performance and also explore new materials, e.g., non-silicon and others, so as to overcome the limitations available in the conventional MOSFET technology.

Tunnel Field Effect Transistors (TFET) have been presented by researchers as a potential device that can replace MOSFETs in future. TFET functions on the basis of band to band tunneling phenomenon, rather than the thermal generation of electrons. So, it becomes possible to achieve a steeper subthreshold swing, thus removing limitation of a conventional MOSFET. However, simple silicon based p-i-n gated TFET structures suffered from low ON current (I<sub>ON</sub>) and higher subthreshold swing. To overcome these limitations, new architectures, materials have been explored in the past. Double gated TFET structure with high-k dielectric materials were used to enhance the performance characteristics of an ON current in TFETs. Addition of the pocket layer at the source has also been earlier to boost the ON current in TFETs. Higher source doping have also been suggested by many to increase ON current by many folds. However, leakage current also rise thus putting a constraint on this method. Heterojunction structures have also been

explored, where low energy band gap materials are used at the source region. This increases the ON current as the effective band gap reduces thus allowing higher band to band tunneling. The materials being explored are InGaAs, InP, GaAs, GaAsSb, InAs, etc. Such structures have been successful in achieving high ON current along with a steeper subthreshold swing. However, the poor quality interface, trapped charges in the oxide layer, and other defects still pose some serious challenges during the fabrication of such structures.

The other limitation in TFET structures is the ambipolar current. In a TFET, unlike a MOSFET, the drain and source terminals are oppositely doped. Thus, if a positive gate to source  $V_{GS}$  voltage is applied, tunneling would happen at the gate-source junction. But, if the negative gate to source  $V_{GS}$  voltage is applied the tunneling would happen at the drain side as well. The leakage current would get increased. So, to overcome this limitation in TFETs, several device architectures have been proposed earlier, such as, gate-drain overlap, low-drain doping, asymmetry between source and drain. Although such structures have reported the reduction in the ambipolar transport, but the low ON current would be the trade-off parameter.

Furthermore, it was learnt that tunnel FETs can be used in several applications like A/D converters, memories, low power analog circuits, sensors, and various other application areas. However, due to its ability of operating a lower supply voltages and obtaining higher sensitivity have compelled researchers to explore TFETs for the use of biosensors in the bio-medical field for the early disease diagnosis. This is done by the study of the biomarkers while screening the patient for various diagnostic tests. Many of the TFET based biosensors have been reported by the researchers. However, the structures like ion sensitive field effect transistor, conventional DG TFET experience performance degradation due to the short channel effects and ultra sharp doping profile.

Based on the prospective of the tunnel FETs and the major limitations and challenges that researchers have faced, we have formulated the objectives of our thesis. An effort has been made to enhance the overall performance of the device by addressing its limitations. The

brief description regarding the objectives and the work done to achieve the objectives have been summarized as under:

# Objective 1: Achieve high Ion/Ioff ratio using narrow band gap heterostructure junction TFET

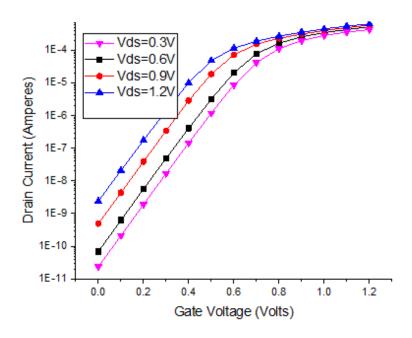

TFETs are considered to be one of the strong candidates which can replace MOSFETs in the future, so it is incumbent to ensure that TFETs have an ON current of the order of 100  $\mu$ A/ $\mu$ m, while maintaining (I<sub>ON</sub>/I<sub>OFF</sub>) ratio of around 10<sup>6</sup>, for lower gate voltages. However, the limitation of TFETs is that due to its inherent physical phenomenon of band to band tunneling (BTBT), it supports low ON current. Therefore, the conventional TFET structures suffer with the major limitation of low ON current. In order to overcome this disadvantage, a lot of research is now-a days focused on boosting the ON current of the TFET.

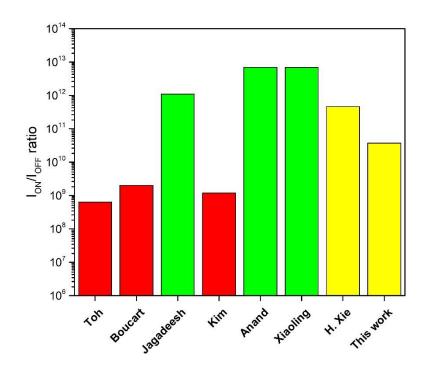

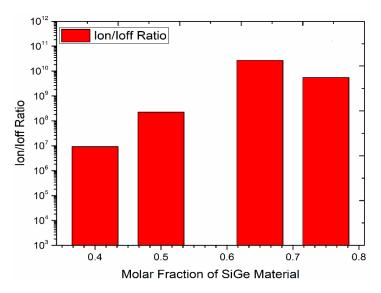

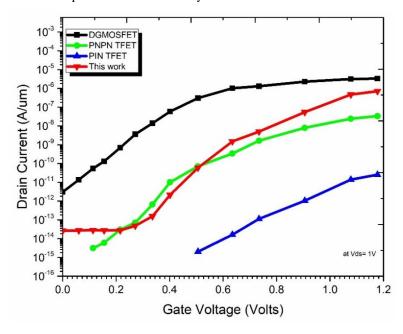

For achieving this objective, the aim has been to explore all the heterojunction TFET devices. With literature review, it was concluded that SiGe would be a better choice when compared to the other material like InGaAs, InP, etc., as these materials suffer from interfacial defects, which ultimately degrades the subthreshold swing of the device. Moreover, it was found that the OFF current was also high for SiGe based device. Then the techniques like, hetero dielectric layer and the use of buried oxide layer was explored to improve the performance of our proposed devise. The device being proposed demonstrates a better results in terms of the  $\frac{I_{ON}}{I_{OFF}}$  ratio. The value comes around  $3.72 \times 10^{10}$  which is considerably high, when compared to the most of the existing architectures.

#### Objective 2: To decrease the subthreshold slope for steeper transition of the device

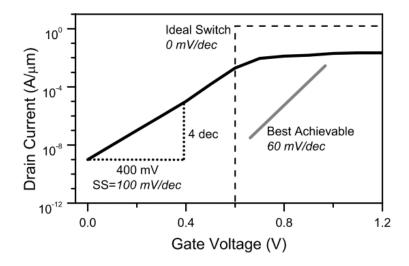

The current flows in the MOSFET on the basis of thermally generated electrons. The sub threshold swing is the parameter that indicates the steepness with which the given transistor turns ON from the state or vice versa. Once the gate voltage on which a device operates becomes very low, it means that the transition is required to be very sharp. However, it has been observed in the MOSFET technology that the subthreshold swing lesser than 60

mV/decade is not achievable. Wile as in the practical circuits, it is often worse than 60 mV/decade, and can rise even up to more than 100 mV/decade. One of the excellent features of TFET is that it is possible that the subthreshold swing can be achieved as lesser than 60 mV/decade due to its different current transport mechanism which is based on band to band tunneling (BTBT).

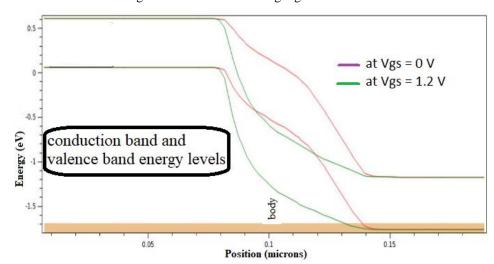

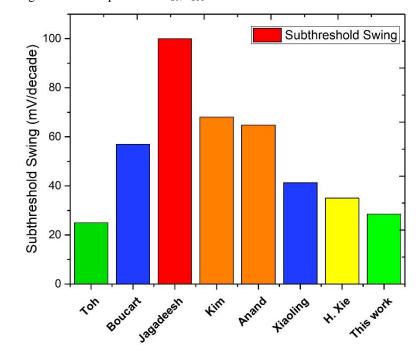

In order to achieve this objective, we have explored different techniques used by researchers to make the transition steeper from ON to OFF state or vice versa. For our device, since the material being used was heterojunction, so a large band gap material was used from the drain region, to reduce the OFF current, while as the lower energy band gap material was used at the source region, so that we can achieve higher tunneling at the source-channel interface region. Besides, the minimum tunneling width is also desirable for obtaining a lesser subthreshold swing. For the proposed device, average subthreshold swing has been calculated as 28.57 mV/decade.

# Objective 3: Reducing the effect of short channel parameters in device performance:

Short Channel effects have proved to be a major bottleneck in the sub nanometer devices. Our aim in the research has been to minimize the parameters like drain induced barrier lowering, subthreshold conduction, etc. Although heterojunction structures provide a larger ON state current, they suffer from large tunneling leakage due to the small bandgap at short channel lengths.

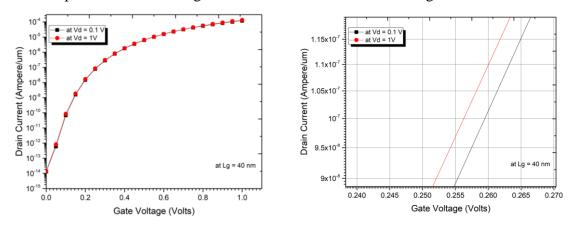

To achieve this objective, energy band gap was one of the parameters on which we laid a focus upon. By default the off current in Ge based material remains high. So, we calibrated the molar fraction x of  $Si_{1-x}Ge_x$  so as to optimize the values of  $I_{ON}$  and  $I_{OFF}$  of the device. Moreover, it was observed that the short channel parameter effects reduce, when the drain-source voltage is decreased. The value of DIBL obtained in our device is of the order of 3.636 mV at 50 nm length and 2.222 mV at 40 nm length. Moreover,

threshold voltage obtained at the drain current of  $10^{-7}$  is about 0.256 V at 50 nm length and 0.248 at 40 nm length.

## Objective 4: Reduction of the ambipolar current transport in Tunnel FETs

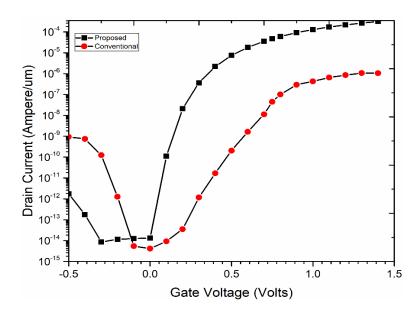

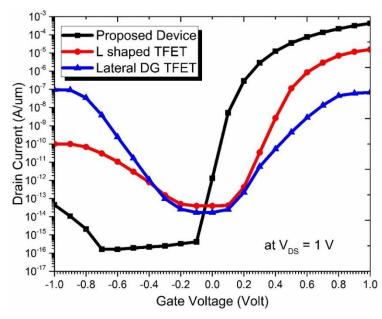

The other serious limitation in a conventional TFET is that of an ambipolar conduction. If the TFET structure is given a negative gate voltage, again due to BTBT at the interface of drain-channel, the drain current begins to flow. This phenomenon is called as ambipolar transport. This limitation restricts the use of TFETs in a complementary devices for digital applications. Our objective has been to reduce this limitation in TFETs.

For achieving this objective, the source terminal has been kept at the higher doping as compared to that of the drain terminal. A sharp doping profile on the source side was required to achieve high ON current. BTBT will be repressed by lower drain doping, when the negative gate-source voltage is being applied at the gate terminal. Besides, a buried oxide layer has also been used in our proposed device. An effort has been made to suppress the ambipolar current up to  $V_{GS} = -0.3$  volts.

## Objective 5: Increased Sensitivity of Tunnel FET Biosensors for biomolecules

The biosensors which were designed with MOSFET and ISFET were unable to detect the biomolecules which were positively or negatively charged. Further, the amount of current carried by ISFET is dependent on the charge density of biomolecules on the surface of the gate region. Therefore, if the size of the biomolecule is small, it cannot be detected by the FET based sensor. The situation remains the same whether the biomolecule is charged or uncharged. Moreover, the short channel effects, the scaling difficulties and the thermal injection transport mechanism of FETs degrade the performance of such sensors. Thus, the focus of the researchers is now to explore new technologies in a FET based biosensors. Tunnel FET based biosensors is on such example.

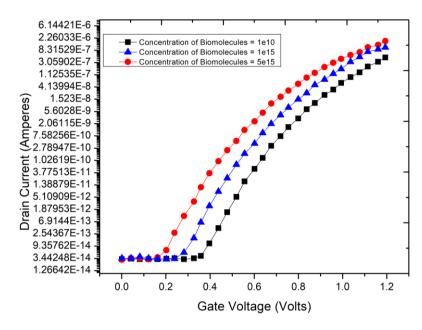

To achieve this objective, we have introduced a nano gap cavity below the gate terminal for the binding of the biomolecules. The nanogap cavity of 30 nm length has been created just below the gate terminal for the conjugation of the biomolecules. The highest  $\frac{I_{ON}}{I_{OFF}}$  ratio achieved was  $1.68 \times 108$  (with  $I_{ON}=2.308 \times 10^{-6}$  and  $I_{OFF}=1.374 \times 10^{-14}$ ). The results have been compared with the double gated SiGe source based heterojunction TFET and few other designs. The cavities help in conjugating biomolecules and hence detect their dielectric constants and the currents that they carry. The presence of biomolecules will cause the device's electrical parameters to change, and that would be detected by changes in the characteristics of the device. Charge density inside the cavity region and the variations in the dielectric constant reflect biomolecule conjugation. The barrier between the source and the channel is reduced when biomolecules are trapped within the cavity, therefore changes the BTBT current. Due to the introduction of biomolecules, the tunneling barrier width will decrease as the dielectric constant increases. This will lead to an increase in an ON current.

## **ACKNOWLEDGEMENT**

During the pleasant journey of this thesis work, I have come across many people who have supported and motivated me all throughout my research work and thesis preparation.

First of all, I would like to express my gratitude to my supervisor **Dr. Sanjeet Kumar Sinha** Associate Professor, School of Electronics & Electrical Engineering, Lovely Professional University (Phagwara, Punjab) for his constant support, encouragements, constructive discussions and critical analysis of the research topics. His positive attitude and belief have always motivated me to carry forward my research even during the days of my struggle. I am truly very fortunate to have the opportunity to work with him.

I am thankful to **Dr. Sandeep Dhariwal**, Associate Professor, Alliance College of Engineering and Design, Alliance University, (Bengaluru), for his guidance during my initial phase of research work. His guidance and encouragement has instilled a positive attitude in me.

I would also like to thank **Dr. Sweta Chander**, Assistant Professor, School of Electronics & Electrical Engineering, Lovely Professional University (Phagwara, Punjab) for her guidance and support. I had many fruitful discussions about my device with her. Her scholastic discussions have encouraged me to work on my limitations and constantly improve my work.

I am thankful to **Dr. Loviraj Gupta**, Executive Dean, and **Prof. Bhupinder Verma**, Head of School, Lovely Faculty of Technology & Sciences, Lovely Professional University (Phagwara, Punjab) for providing me the consent for the extension of lab timings. With their permission, I was able to utilize the resources of the research lab after 5 PM as well as on Sundays.

I am highly thankful to **Mr. Ashok Mittal**, Honorable Chancellor, Lovely Professional University (Phagwara, Punjab) for making all the necessary research related licensed softwares available at my disposal.

I am also thankful to all my colleagues of Electronics and Communication Engineering Department and my friends who contributed directly or indirectly through their constructive criticism in my research work.

I extend my deepest gratitude to my parents and my brother for their love, affection, encouragement and support during this whole journey.

My acknowledgements would not be complete without expressing my gratitude towards Almighty God. I feel very fortunate to come to know Him during all these months of my life and have continually been blessed by His endless love ever since. I thank God for blessing me with sound health and strength to carry out my work.

Irfan Ahmad Pindoo

## TABLE OF CONTENTS

| ABSTRACT                                      | iv    |

|-----------------------------------------------|-------|

| ACKNOWLEDGEMENT                               | X     |

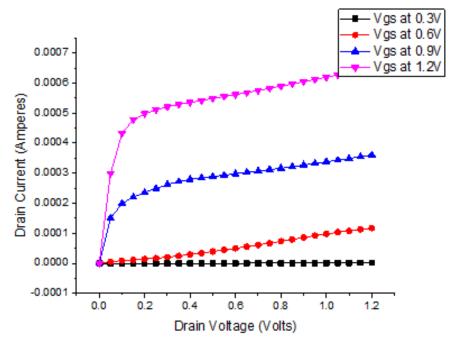

| TABLE OF CONTENTS                             | xii   |

| LIST OF TABLES                                | xvii  |

| LIST OF FIGURES                               | xviii |

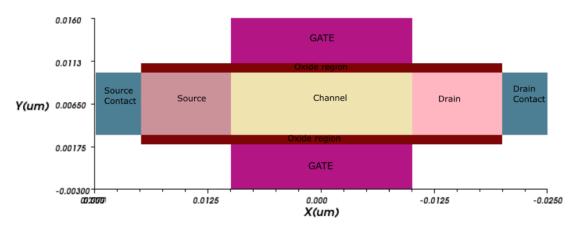

| LIST OF SYMBOLS                               | xxiii |

| LIST OF ABBREVIATIONS                         | xxvi  |

| CHAPTER 1: INTRODUCTION                       | 26    |

| 1.1 Basics of Conventional MOSFETs            | 26    |

| 1.2 CMOS Scaling                              | 28    |

| 1.3 Short Channel Effects in MOSFET           | 30    |

| 1.3.1. Drain Induced Barrier Lowering Effect  | 31    |

| 1.3.2. Threshold Voltage Roll-off             | 31    |

| 1.3.3. Boltzmann Tyranny                      | 32    |

| 1.4 Evolving FET Devices                      | 33    |

| CHAPTER 2: TUNNEL FILED EFFECT TRANSISTORS    | 34    |

| 2.1 Basics of Tunnel Field Effect Transistors | 34    |

| 2.1.1. TFET Structure                         | 34    |

| 2.1.2. TFET Operation                         | 35    |

| 2.2 Quantum tunneling phenomenon in TFETs     | 39    |

| 2.3 Subthreshold swing in TFET                | 40    |

| 2.4 Ambipolar Current in a TFET               | 44    |

| C | HAPTER 3: LITERATURE REVIEW OF TUNNEL FET STRUCTURES            | 46 |

|---|-----------------------------------------------------------------|----|

|   | 3.1 Introduction                                                | 46 |

|   | 3.2 All Silicon TFETs                                           | 46 |

|   | 3.2.1. Thickness and Dielectric Constant:                       | 48 |

|   | 3.2.2. Multiple Gates:                                          | 50 |

|   | 3.2.3. Use of Spacers:                                          | 51 |

|   | 3.3 Group III–V-semiconductor-based TFETs                       | 52 |

|   | 3.4 Germanium as a material                                     | 55 |

|   | 3.5 Carbon based Tunnel FETs                                    | 55 |

|   | 3.6 Tunneling Junction:                                         | 56 |

|   | 3.6.1. Source Doping:                                           | 56 |

|   | 3.6.2. Use of Pockets:                                          | 57 |

|   | 3.6.3. Vertical TFETs:                                          | 57 |

|   | 3.7 Junctionless TFETs:                                         | 61 |

|   | 3.8 Problem Statement and Research Gaps:                        | 62 |

| C | HAPTER 4: MODEL TOOLS, METHODOLOGY AND RESEARCH PROCESS         | 64 |

|   | 4.1 Models Included and the Underlying Physics:                 | 64 |

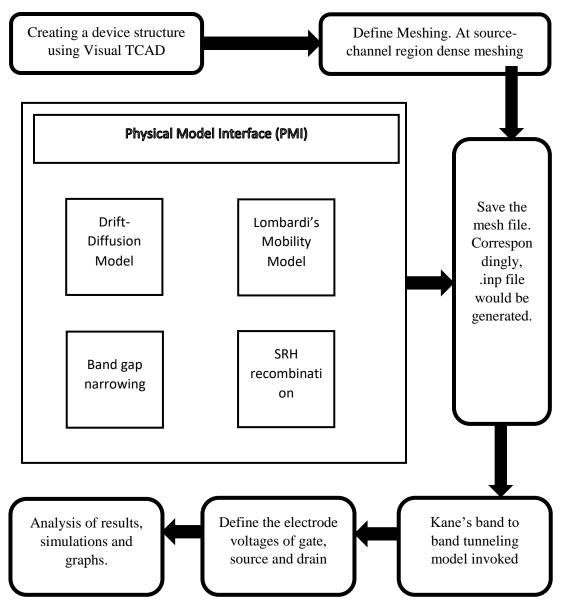

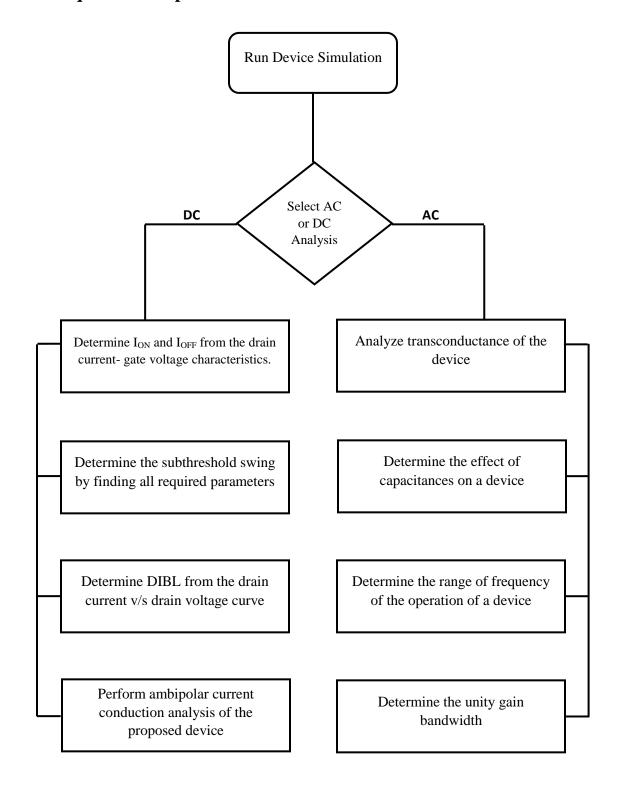

|   | 4.2 Device Calibration                                          | 67 |

|   | 4.3 Methodology followed for carrying out the work:             | 69 |

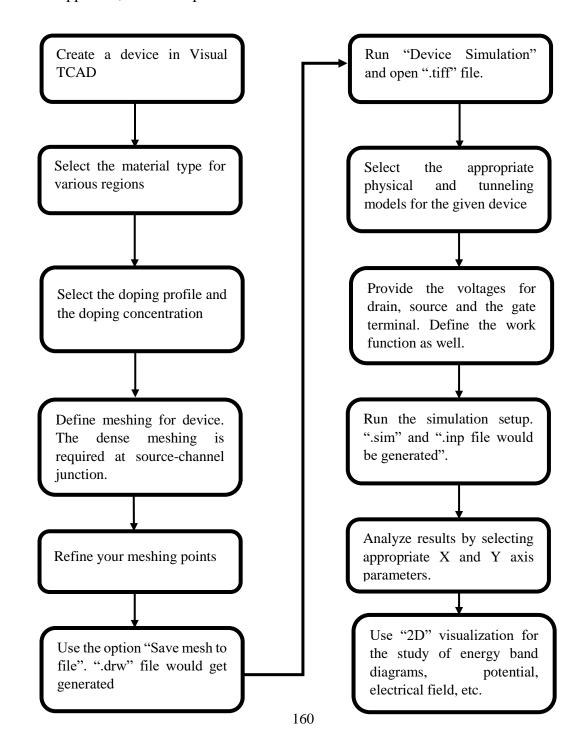

|   | 4.4 Sequence of steps followed in the Visual TCAD:              | 70 |

| C | HAPTER 5: ELECTRICAL CHARACTERISTICS OF PROPOSED                |    |

| Н | ETEROJUNCTION TFET                                              | 72 |

|   | 5.1 Introduction                                                | 72 |

|   | 5.2 Implementation of Previous TFET Structures and a Comparison | 72 |

| 5.3 Implementation of proposed SiGe based heterojunction based TFET       | 78       |

|---------------------------------------------------------------------------|----------|

| 5.3.1. Device Architecture and Simulation Set up                          | 78       |

| 5.4 Electrical Characteristics of the device:                             | 80       |

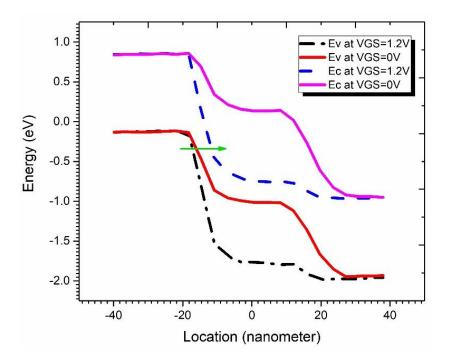

| 5.4.1. Energy Band Diagram                                                | 81       |

| 5.4.2. Electrical Field and Surface Potential of the device               | 82       |

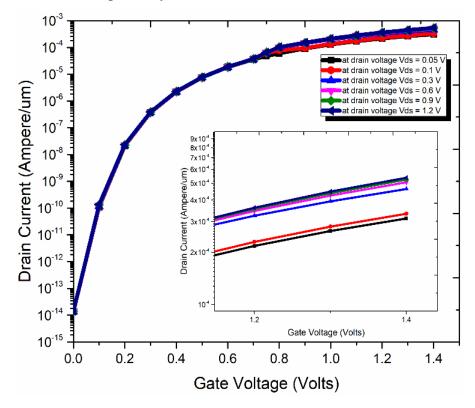

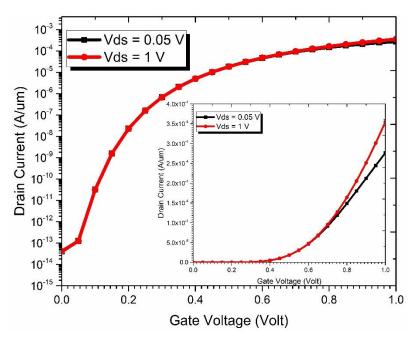

| 5.4.3. Transfer Characteristics: Drain Current v/s Gate-Source Voltage    | 83       |

| 5.4.4. Subthreshold Swing                                                 | 87       |

| 5.5 Short Channel Parameter Study Of SiGe Based TFET Structure            | 87       |

| 5.5.1. Drain Induced Barrier Lowering                                     | 87       |

| 5.6 Suppression of Ambipolar Transport                                    | 90       |

| CHAPTER 6: PARAMETER VARIATIONS OF SIGE BASED TFET STRUCTU                | JRE . 92 |

| 6.1 Introduction                                                          | 92       |

| 6.2 Work Function Variation of Gate Material                              | 92       |

| 6.3 Molar Function Variation of <b>Si1 – xGex</b> at the Source Region    | 94       |

| 6.4 Spacer Length Variation at the source and the drain regions           | 96       |

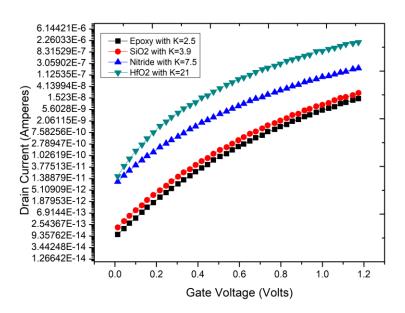

| 6.5 Gate Dielectric layer Material Variations                             | 99       |

| 6.6 Buried Oxide Layer Material Variations                                | 101      |

| CHAPTER 7: STUDY OF ANALOG PERFORMANCE AND TEMPERATURE                    | ļ        |

| ARIATIONS IN SiGe SOURCE BASED TFET STRUCTURE                             | 102      |

| 7.1 Introduction                                                          | 102      |

| 7.2 RF/Analog Parameter Analysis of SiGe source based Heterojunction TFET |          |

| structure:                                                                | 102      |

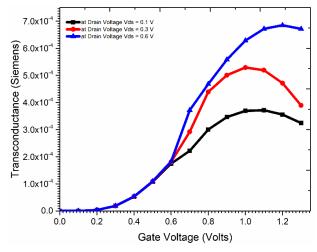

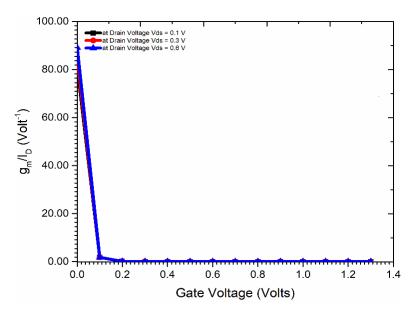

| 7.2.1. Transconductance and Device Efficiency of the device:              | 102      |

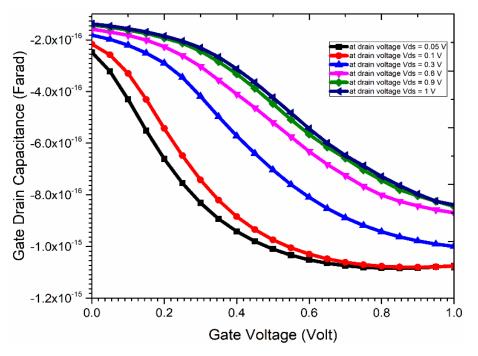

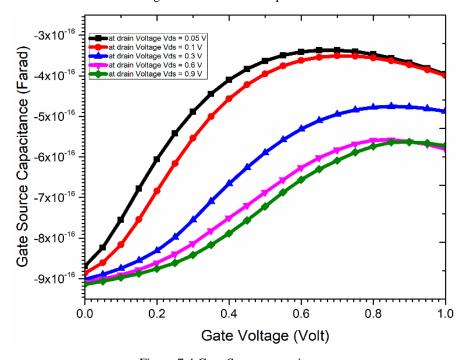

| 7.2.2. Gate-Source Capacitance and Gate-Drain Capacitance of the device:  | 104      |

| 7.2.3. Cut-off Frequency and gain-bandwidth product calculation of the device 10 | 6 |

|----------------------------------------------------------------------------------|---|

| 7.3 Temperature Variations Analysis of the proposed Device:                      | 8 |

| 7.3.1. Effect on I <sub>D</sub> -V <sub>GS</sub> Transfer Characteristics        | 8 |

| 7.3.2. Energy band gap variations                                                | 3 |

| 7.3.3. Variations in subthreshold Swing                                          | 4 |

| 7.3.4. Variations in gate capacitance                                            | 5 |

| 7.4 Conclusion                                                                   | 7 |

| CHAPTER 8: INCREASED SENSITIVITY OF TFET BIOSENSORS BASED ON SiGe                | Э |

| HETEROJUNCTION SOURCE                                                            | 8 |

| 8.1 Introduction                                                                 | 8 |

| 8.2 Principles of FET based biosensing:                                          | 9 |

| 8.2.1. MOSFET                                                                    | 9 |

| 8.2.2. ISFET                                                                     | 1 |

| 8.2.3. Silicon Nanowire FET                                                      | 2 |

| 8.2.4. Carbon Nanotubes                                                          | 2 |

| 8.3 TFET Based Biosensor                                                         | 4 |

| 8.3.1. TFET device architecture and simulation setup                             | 7 |

| 8.3.2. Results and Discussions                                                   | 9 |

| 8.4 Challenges                                                                   | 6 |

| CHAPTER 9: CONCLUSION AND FUTURE SCOPE OF THE WORK 13'                           | 7 |

| 9.1 Conclusion                                                                   | 7 |

| 9.2 Future Scope of the Work                                                     | 0 |

| REFERENCES                                                                       | 2 |

| APPENDIX                                                                         | 0 |

| LIST OF PUBLICATIONS | 16 | 64 |

|----------------------|----|----|

|----------------------|----|----|

## LIST OF TABLES

| Table 4-1 Recombination parameters default values                                                            | 65 |

|--------------------------------------------------------------------------------------------------------------|----|

| Table 5-1 Parameter values for the simulated devices                                                         | 74 |

| Table 5-2 Device Parameter and their values used during the simulation                                       | 80 |

| Table 5-3 Comparison of existing TFET architectures with the proposed device at the drain voltage of 1 volts | 85 |

| existing TFET structures                                                                                     | 08 |

| Table 8-1 Comparison of device parameters at 30 nm and 20 nm cavity length 1                                 | 31 |

| Table 8-2 Sensitivity comparison of the proposed biosensor with other research works 1                       | 34 |

## LIST OF FIGURES

| Figure 1.1. MOS transistor (a) n-channel (b) p-channel                                                                           | 27 |

|----------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2 Illustration of Moore's law [10]                                                                                      | 29 |

| Figure 1.3 DIBL effect in MOSFET [19]                                                                                            | 31 |

| Figure 1.4 A typical NMOS switch's characteristics and a comparison to an ideal switch (shown in dashed line)                    |    |

| Figure 2.1 Biasing method and structure of: (a) n- TFET (b) p- TFET                                                              | 34 |

| Figure 2.2 Representation of an OFF state and ON state in n-type TFET                                                            | 36 |

| Figure 2.3 Representation of p-type SOI TFET. The Energy band diagram depicts the triangular barrier approximation at the source | 38 |

| Figure 2.4 Representation of conduction band at two separate gate voltages in the MOSFET                                         | 41 |

| Figure 2.5 Fermi–Dirac distribution at different temperatures T <sub>3</sub> , T <sub>2</sub> and T <sub>1</sub> . As the        |    |

| temperature rises, the exponential tail becomes more prominent [35]                                                              | 43 |

| Figure 2.6 Band diagram at subthreshold region of p-type TFET at two different gate voltages [34]                                |    |

| Figure 2.7 Representation of Energy band diagram when the Fermi energy level is high                                             | ;h |

| from the source side in TFET [34]                                                                                                | 44 |

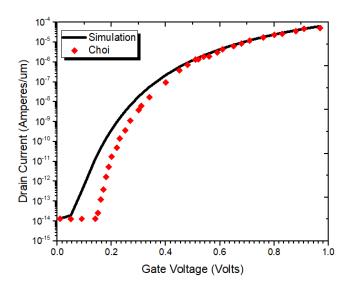

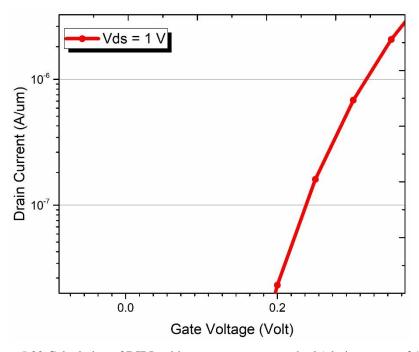

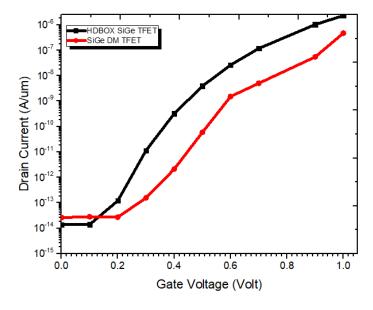

| Figure 4.1 Calibration of the device with [43] representing I <sub>D</sub> -V <sub>GS</sub> characteristics                      | 68 |

| Figure 5.1 Schematic of Single gated TFET                                                                                        | 73 |

| Figure 5.2 Energy Band Diagram of a single gate TFET                                                                             | 73 |

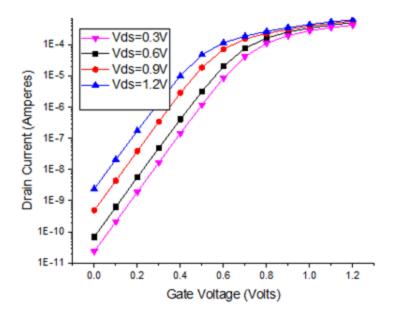

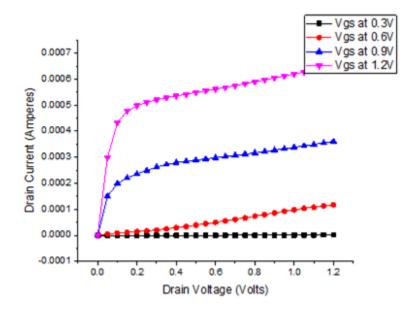

| Figure 5.3 log $I_D$ v/s $V_{GS}$ curve for Single Gate TFET                                                                     | 74 |

| Figure 5.4 I <sub>D</sub> v/s V <sub>DS</sub> curve for Single Gate TFET                                                         | 75 |

| Figure 5.5 Schematic of double gated TFET                                                                                        | 76 |

| Figure 5.6 Band diagram of double gated TFET structure                                                                                      | 76 |

|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.7 log I <sub>D</sub> -V <sub>GS</sub> characteristics of double gated TFET structure                                               | 77 |

| Figure 5.8 I <sub>D</sub> -V <sub>GS</sub> characteristics of double gated TFET structure                                                   | 77 |

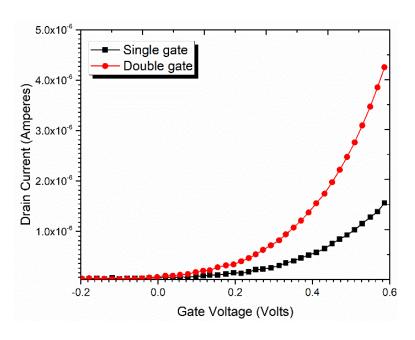

| Figure 5.9 I <sub>D</sub> -V <sub>GS</sub> comparison curves for single and double gate TFET                                                | 78 |

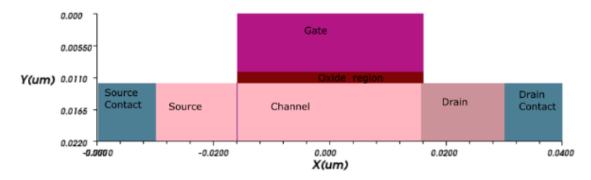

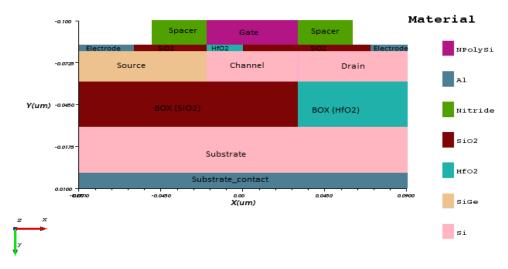

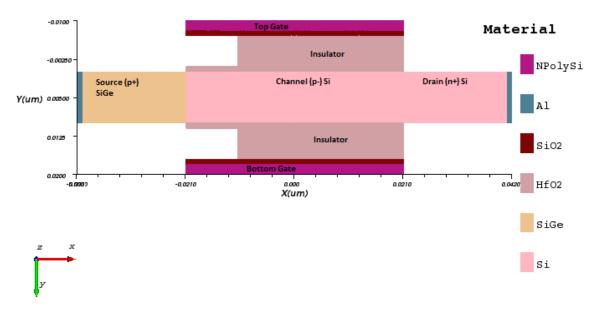

| Figure 5.10 Proposed SiGe based heterostructure tunnel FET                                                                                  | 79 |

| Figure 5.11 Representation of dense meshing at the source-channel tunneling junction of the device                                          |    |

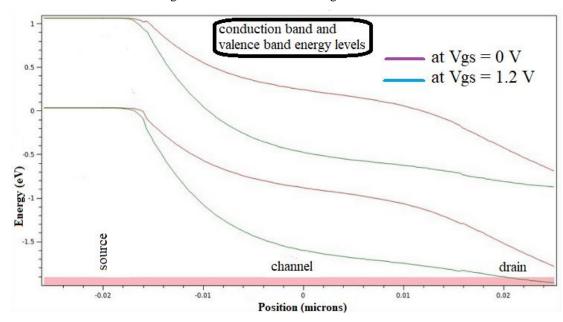

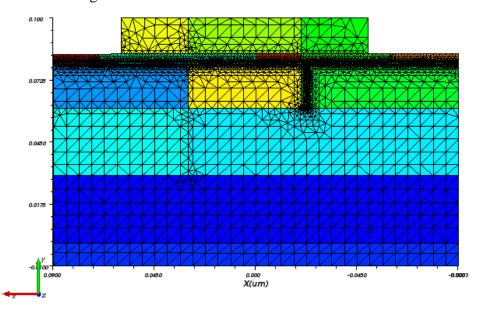

| Figure 5.12 SiGe based TFET energy band diagram (a) at $V_{GS} = 0 \ V$ (b) at $V_{GS} = 1.5 \ V$                                           |    |

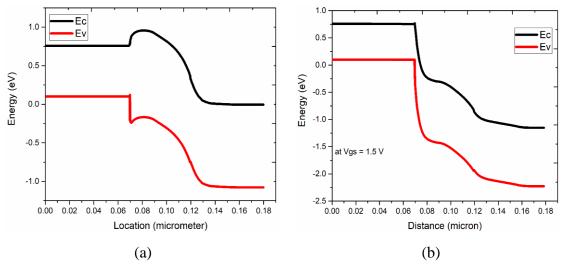

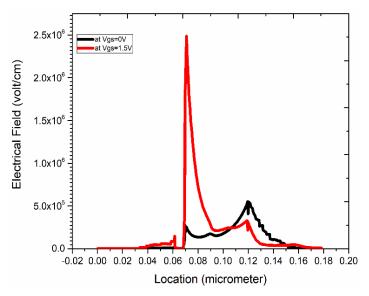

| Figure 5.13 Electric Field Variations at the source                                                                                         | 82 |

| Figure 5.14 Surface Potential of a device                                                                                                   | 82 |

| Figure 5.15 Transfer characteristics I <sub>D</sub> vs V <sub>GS</sub> of a device.                                                         | 84 |

| Figure 5.16 log I <sub>D</sub> vs V <sub>GS</sub> Transfer characteristics of a device                                                      | 84 |

| Figure 5.17 Comparison of the work with conventional DGTFET, Group III-V and vertical tunnel FET devices                                    | 85 |

| Figure 5.18 Comparison of $I_{ON}/I_{OFF}$ for various TFET device architectures                                                            | 86 |

| Figure 5.19 Comparison of subthreshold swings for various TFET device architectures                                                         | 86 |

| Figure 5.20 I <sub>D</sub> -V <sub>GS</sub> Transfer characteristics curve                                                                  | 88 |

| Figure 5.21 Graph extraction at linear and saturation regions                                                                               | 89 |

| Figure 5.22 Calculation of DIBL with constant current method ( drain current of $10^{-7}$ ).                                                | 89 |

| Figure 5.23. DIBL calculation with constant current method at $Lg == 40$ nm. (a) Log scale (b) Zoom in of image at $10^{-7}$ drain current. |    |

| Figure 5.24 comparison of ambipolar current with conventional TFET device                                                                   | 91 |

| Figure 5.25 comparison of ambipolar current with DGTFET and L-shaped TFET device                             |

|--------------------------------------------------------------------------------------------------------------|

| 91                                                                                                           |

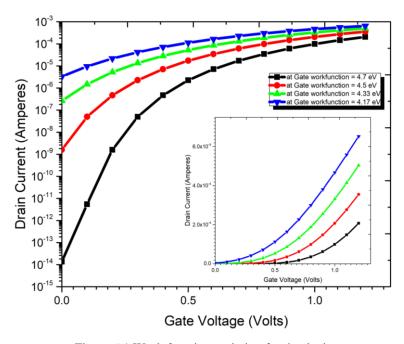

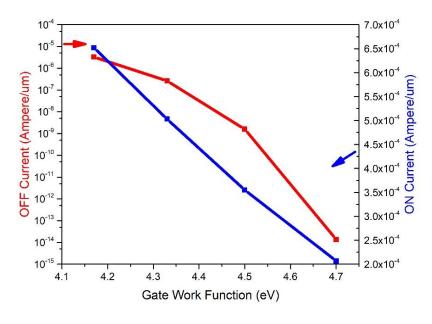

| Figure 6.1 Work function variation for the device                                                            |

| Figure 6.2 ON current and OFF current variations with gate work function                                     |

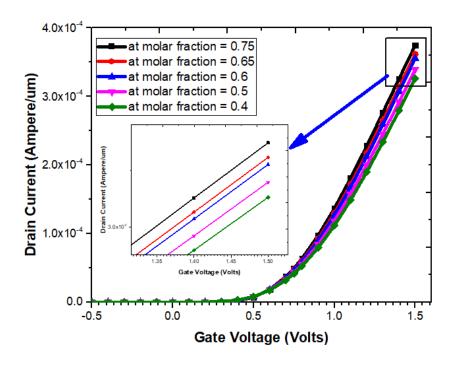

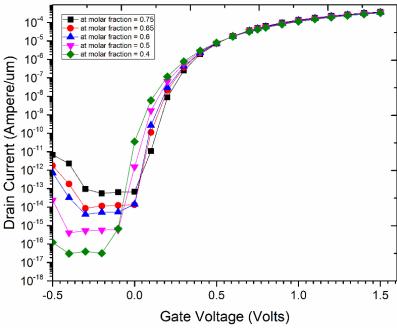

| Figure 6.3 Drain current characteristics with molar fraction variation                                       |

| Figure 6.4 Drain current characteristics with molar fraction variation on (a) Linear scale                   |

| (b) Log scale95                                                                                              |

| Figure 6.5 I <sub>ON</sub> /I <sub>OFF</sub> ratio changes with molar fraction variation                     |

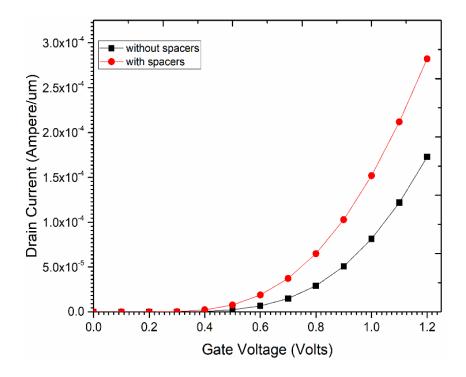

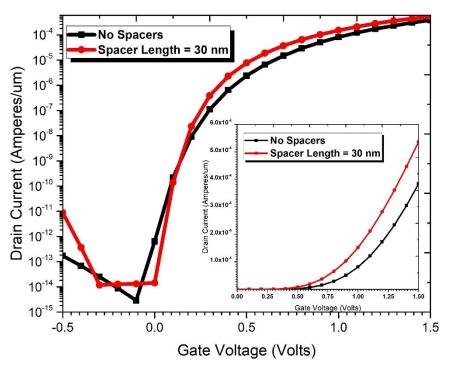

| Figure 6.6 Comparison of Drain current with and without spacers                                              |

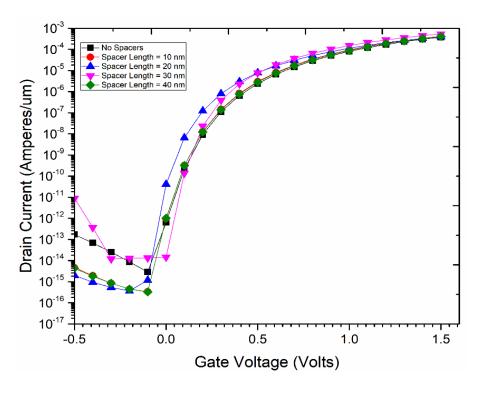

| Figure 6.7 Spacer length variation effect on drain current                                                   |

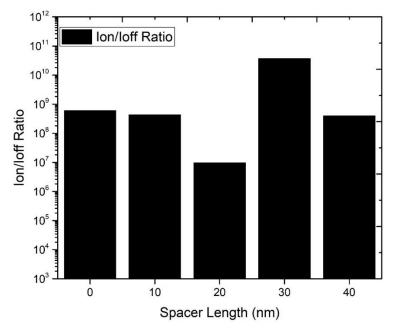

| Figure 6.8 I <sub>ON</sub> /I <sub>OFF</sub> ratio changes with spacer length variation                      |

| Figure 6.9 I <sub>ON</sub> /I <sub>OFF</sub> ratio changes with spacer length                                |

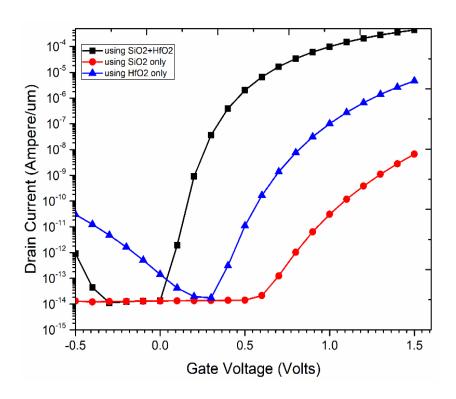

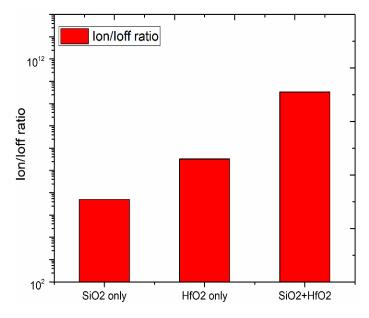

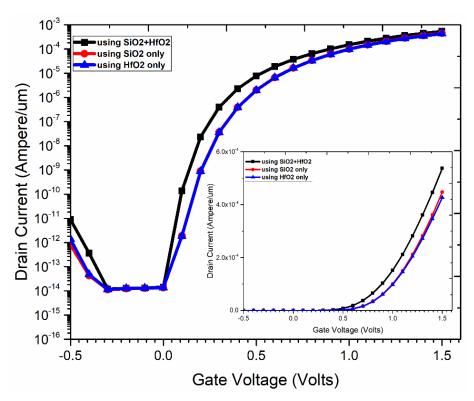

| Figure 6.10 Drain current characteristics with variations in gate dielectric material 100                    |

| Figure 6.11 Variations in I <sub>ON</sub> /I <sub>OFF</sub> ratio                                            |

| Figure 6.12 Drain current characteristics with variations in BOX layer 101                                   |

| Figure 7.1 Transconductance vs Gate voltage curve                                                            |

| Figure 7.2 Device Efficiency g <sub>m</sub> /I <sub>D</sub> vs Gate Voltage curve                            |

| Figure 7.3 Gate-Drain capacitance curve                                                                      |

| Figure 7.4 Gate-Source capacitance curve                                                                     |

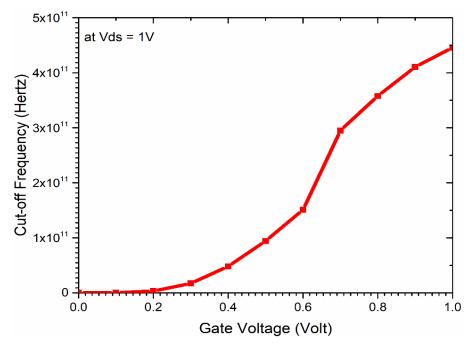

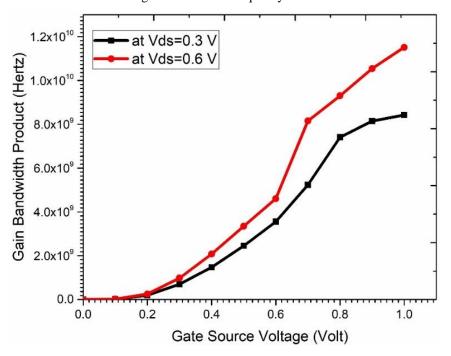

| Figure 7.5 Cut-off frequency curve                                                                           |

| Figure 7.6 Gain Bandwidth Product Plot                                                                       |

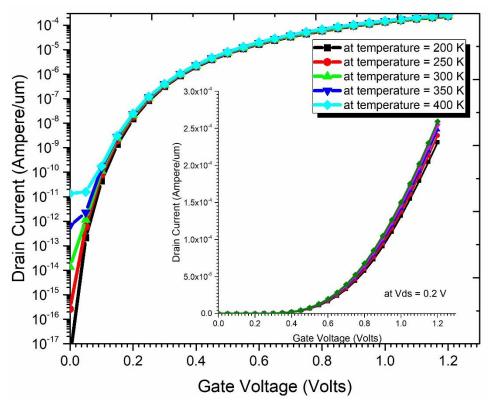

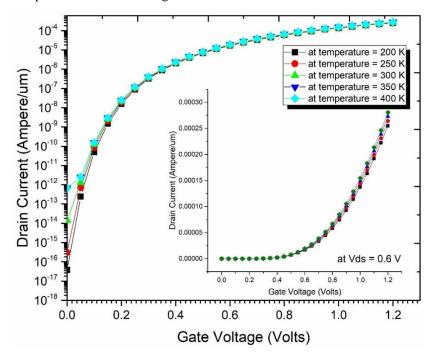

| Figure 7.7 Temperature variations in $I_{D}\text{-}V_{GS}$ Transfer characteristics curve at $V_{DS}=0.2\ V$ |

|                                                                                                              |

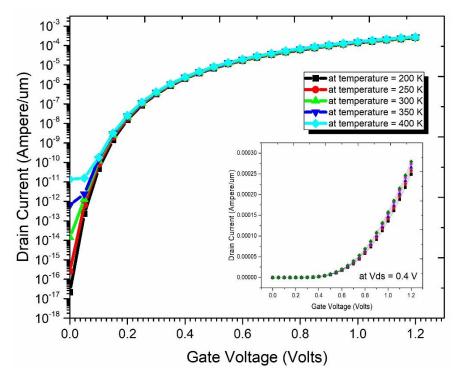

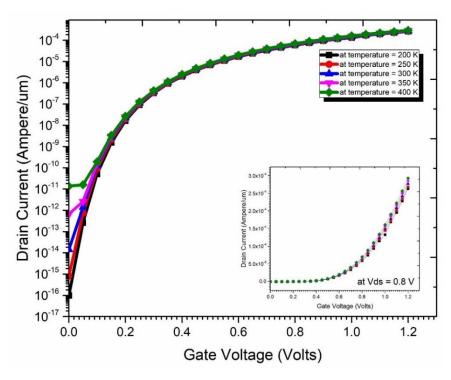

| Figure 7.8 Temperature variations in log $I_D$ - $V_{GS}$ Transfer characteristics curve $V_{DS} = 0.4$  |

|----------------------------------------------------------------------------------------------------------|

| V                                                                                                        |

| Figure 7.9 Temperature variations in $I_D$ - $V_{GS}$ Transfer characteristics curve $V_{DS} = 0.6 \ V$  |

|                                                                                                          |

| Figure 7.10 Temperature variations in log $I_D$ - $V_{GS}$ Transfer characteristics curve $V_{DS} = 0.8$ |

| V                                                                                                        |

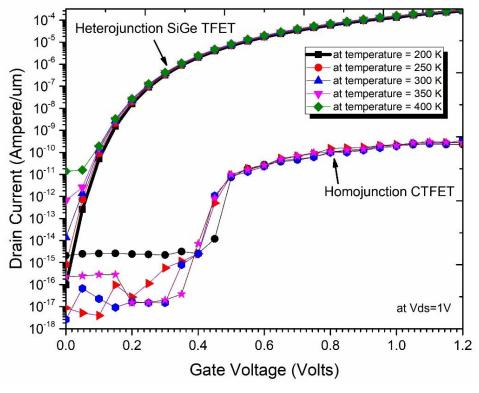

| Figure 7.11 Temperature variations comparison with the homojunction TFET device . 111                    |

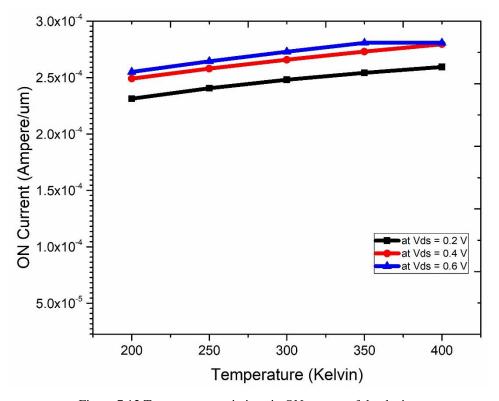

| Figure 7.12 Temperature variations in ON current of the device                                           |

| Figure 7.13 Temperature variations in OFF current of the device                                          |

| Figure 7.14 Temperature variations in the Energy band gap                                                |

| Figure 7.15 Temperature variations in the subthreshold swing                                             |

| Figure 7.16 Temperature variations in Gate-Drain capacitance curve                                       |

| Figure 7.17 Temperature variations in Gate-Source capacitance curve                                      |

| Figure 8.1 The MOSFET Structure (a) cross sectional view of n-type MOSFET (b)                            |

| Physical structure of n-type MOSFET                                                                      |

| Figure 8.2 The ISFET Structure (a) n-type ISFET cross sectional view (b) Physical                        |

| structure of n-type ISFET                                                                                |

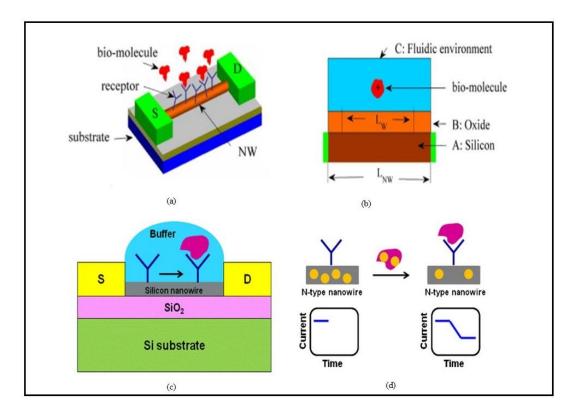

| Figure 8.3 (a) Representation of nanowire biosensor (b) Demonstration of three regions                   |

| (c) Immobilization of a receptor molecule on the SiNW surface (d) When a negatively                      |

| charged target molecule binds to the receptor, the conductance of n-type doped SiNW                      |

| decreases                                                                                                |

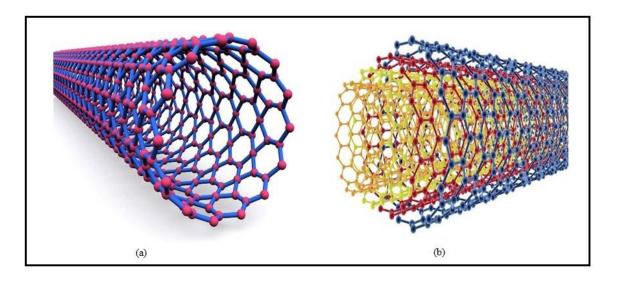

| Figure 8.4 (a) Single walled CNT (SWCNT) (b) Multi walled CNT (MWCNT)                                    |

| 123                                                                                                      |

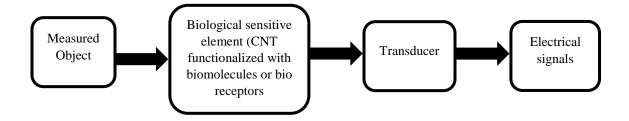

| Figure 8.5 Step wise description of CNT based sensors                                                    |

| Figure 8.6 (a) Transfer characteristics of MOSFET representing increase in an OFF                                         |

|---------------------------------------------------------------------------------------------------------------------------|

| current exponentially (10 folds increase for every 60mV at T=300K). (b) Comparison of                                     |

| MOSFET, Silicon Bulk TFET, multi-gate devices (MuG) and SiGe TFET. (c) For a sub-                                         |

| thermal swing, the minimum switching energy and the corresponding voltage supply are                                      |

| needed at the same $I_{\text{ON}}/I_{\text{OFF}}\left(d\right)$ Steep swing in TFET offering better energy efficiency for |

| low voltage operations [3]                                                                                                |

| Figure 8.7 Schematic of Dielectrically modulated TFET                                                                     |

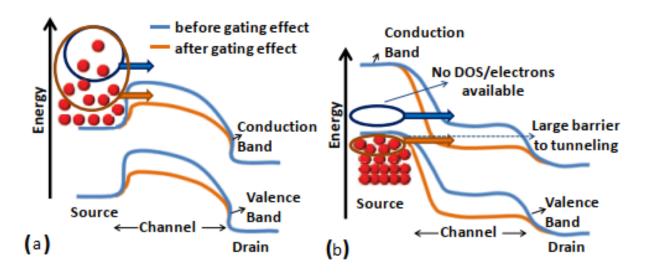

| Figure 8.8 Energy band profile of (a) Conventional FET (b) Tunnel FET demonstrating                                       |

| band to band tunneling (BTBT) phenomenon between channel's conduction band and                                            |

| source's valence band. Once the bio biomolecules are trapped due to the gating effect, the                                |

| bands bend down reducing the barrier the channel and the source, therefore increasing the                                 |

| BTBT current. 128                                                                                                         |

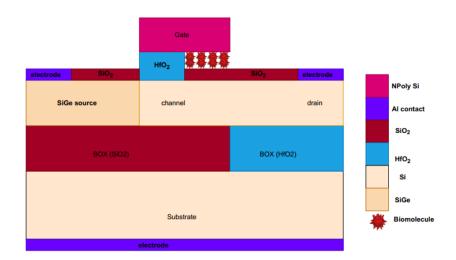

| Figure 8.9 Hetero gate dielectric hetero BOX based proposed SiGe heterojunction                                           |

| biosensor                                                                                                                 |

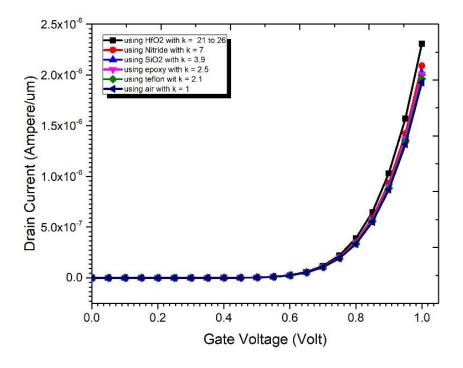

| Figure 8.10 Drain Current characteristics representing the effect of neutral biomolecules                                 |

| at the cavity length of 30 nm                                                                                             |

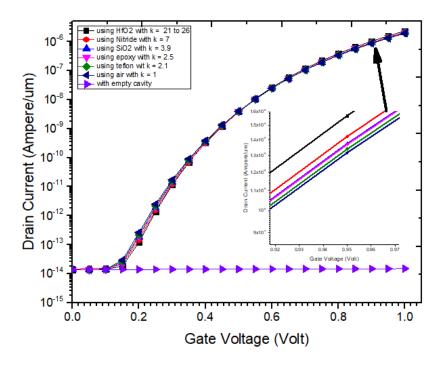

| Figure 8.11 Drain Current characteristics on the log scale representing the effect of                                     |

| neutral biomolecules at the cavity length of 30 nm                                                                        |

| Figure 8.12 Energy band diagram for double gate DMTFET                                                                    |

| Figure 8.13 Comparison of the sensitivity of MOSFET and TFET based biosensors 133                                         |

| Figure 8.14 Variation of a drain current with concentration of biomolecules                                               |

| Figure 8.15 Variations in the drain current sensitivity with variation in Dielectric constant                             |

|                                                                                                                           |

| Figure 8.16 Drain current sensitivity of HDBOX SiGe TFET and SiGe DM TFET                                                 |

| hiosansor 125                                                                                                             |

## LIST OF SYMBOLS

| $I_{ON}$   | On current                                  |

|------------|---------------------------------------------|

| $I_{OFF}$  | Off current                                 |

| $V_{Th}$   | Threshold Voltage                           |

| $V_{GS}$   | Gate to source voltage                      |

| $L_g$      | Gate length                                 |

| $C_{ox}$   | Oxide capacitance                           |

| $P_S$      | Static power dissipation                    |

| $P_D$      | Dynamic power dissipation                   |

| $V_{DD}$   | Supply voltage                              |

| $C_L$      | Load capacitance                            |

| α          | Switching probability                       |

| f          | Device operational frequency                |

| e          | Electronic charge                           |

| h          | Planck's constant                           |

| $f_s(E)$   | Source fermi energy function                |

| $f_d(E)$   | Drain fermi energy function                 |

| $T_{tot}$  | Transmission function                       |

| ħ          | Reduced Planck constant                     |

| $m^*$      | Reduced mass of an electron                 |

| $E_g^*$    | Effective energy band gap                   |

| ΔΦ         | Energy overlap window                       |

| $\in_{Si}$ | Electrical permittivity of silicon material |

| $\in_{ox}$ | Electrical permittivity of oxide layer      |

| $t_{ox}$   | Oxide thickness                             |

| $t_{Si}$   | Silicon body thickness                      |

| $I_D$      | Drain current                               |

|            |                                             |

| Ψ             | Wave function                                            |

|---------------|----------------------------------------------------------|

| $\Psi(x)$     | Denotes the spatial component of $\Psi(x,t)$ which is a  |

|               | function of only $x$                                     |

| $\Psi(t)$     | Denotes the temporal component of $\Psi(x,t)$ which is a |

|               | function of only t                                       |

| D(E)          | Density of State                                         |

| T             | Temperature                                              |

| k             | Boltzmann constant                                       |

| SS            | Subthreshold swing                                       |

| $f_F(E)$      | Fermi–Dirac distribution function                        |

| $G^{BB}$      | Generation rate                                          |

| μ             | Mobility                                                 |

| $E_{\perp}$   | Transverse component of the electrical field.            |

| $N_S$         | Doping at the source region                              |

| $N_D$         | Doping at the drain region                               |

| $N_{ch}$      | Doping at the channel region                             |

| Е             | Electrical field                                         |

| $C_D$         | Depletion capacitance                                    |

| $V_{D_{SAT}}$ | Supply voltage during saturation mode                    |

| $V_{D_{LIN}}$ | Supply voltage during linear mode                        |

| $V_{T_{LIN}}$ | Threshold voltage during linear mode                     |

| $V_{T_{SAT}}$ | Threshold voltage during saturation mode                 |

| φ             | Gate work function                                       |

| $C_{GS}$      | Gate-source capacitance                                  |

| $C_{GD}$      | Gate-drain capacitance                                   |

| $C_{GG}$      | Total gate capacitance                                   |

| $f_T$         | Cut-off frequency                                        |

| GBP           | Gain Bandwidth product                                   |

| $g_m$        | Transconductance  |

|--------------|-------------------|

| $g_m/I_{DS}$ | Device efficiency |

| $V_T$        | Thermal voltage   |

## LIST OF ABBREVIATIONS

| BOX    | Buried oxide layer                                |

|--------|---------------------------------------------------|

| BTBT   | band to band tunneling                            |

| CMOS   | complementary metal oxide semiconductor           |

| DD     | Drift-diffusion                                   |

| DGTFET | Double gated Tunnel Field Effect Transistor       |

| DIBL   | drain induced barrier lowering                    |

| GBP    | Gain-bandwidth product                            |

| IC     | Integrated Circuit                                |

| JLTFET | Junction less Tunnel Field Effect Transistor      |

| LTFET  | Lateral Tunnel Field Effect Transistor            |

| MOSFET | metal oxide semiconductor field effect transistor |

| NEGF   | Non energy green function                         |

| NMOS   | N channel metal oxide semiconductor               |

| PDA    | Personal Digital Assistant                        |

| PMI    | Physical Model Interface                          |

| PMOS   | P channel metal oxide semiconductor               |

| QC     | Quantum confinement                               |

| RF     | Radio frequency                                   |

| SCE    | Short channel effects                             |

| SOI    | Silicon on Insulator                              |

| SRH    | Shockley-Read-Hall                                |

| SS     | Subthreshold swing                                |

| TCAD   | Technology computer-aided design                  |

| TFET   | Tunnel Field Effect Transistor                    |

| VLSI   | Very Large Scale Integrated Circuit               |

| VTFET  | Vertical Tunnel Field Effect Transistor           |

## **CHAPTER 1: INTRODUCTION**

Over the last four decades, electronics have evolved from bulky vacuum tubes to lighter and lower-cost bipolar junction transistors, unipolar FETs, and now CMOS technology. The reason that one technology was superseded by the other was when their power consumption became excessively high [1, 2]. By increasing power density and the number of transistors in a given IC, CMOS scaling faces several challenges. Therefore, the need arises to explore new emerging devices that can improve the limitations of CMOS technology and can be seen as a future and successor of conventional MOSFET [3, 4]. The methods of scaling are by decreasing gate length  $L_G$  and increasing oxide capacitance  $C_{\rm ox}$  such that the current  $I_{\rm ON}$  increases. However, even using optimized materials, sometimes result in short channel effects.

## 1.1 Basics of Conventional MOSFETs

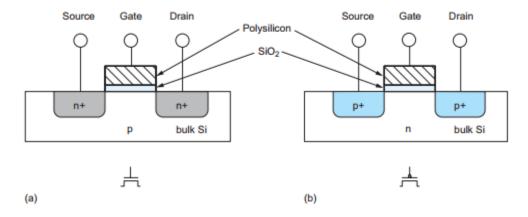

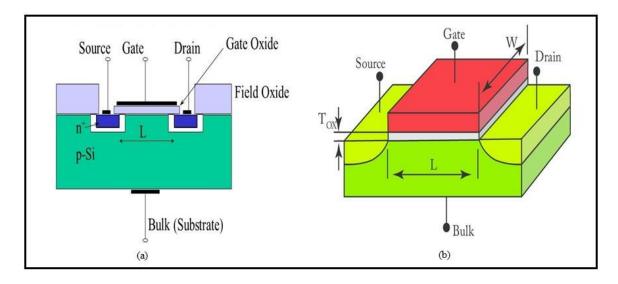

A MOSFET is the structure consisting of the base material as a silicon called as body or substrate. It is the foundation over which whole device would be constructed. Over the substrate, a thin silicon dioxide layer is deposited over the material. The drain and the source are being doped with the same type of the material. The source and the drain terminals are attached through the metallic contacts. The gate terminal is made up of polysilicon and remains insulated from the channel due to the SiO<sub>2</sub> layer. MOSFETs can be of two categories: n-channel MOSFET and p-channel MOSFET. The drain and source regions of an n-channel MOSFET are heavily doped with n+ type dopants, as a result the current conduction would be due to the electrons as charge carriers. While as, in the p-channel MOSFET, The drain and source are both heavily doped with p+ style dopants., as a result the current conduction would be due to the holes as charge carriers [5, 6]. The cross sectional diagram provided in figure 1.1 represents both N-channel and P-channel MOSFETs.

Figure 1.1. MOS transistor (a) n-channel (b) p-channel

The current conduction from source terminal to drain is controlled by the application of the gate-source voltage. The p-type substrate is used in NMOS transistors and is usually connected to the ground. The voltage at drain side would be greater as compared to the source. Due to the absence of the channel, no current would flow from source to drain if the gate-source voltage was zero. Therefore, we assume the transistor is turned off. If the voltage at gate is gradually increased, an electric field is developed across the channel, as a result free electrons are attracted at the Si-SiO<sub>2</sub> interface. When a gate voltage becomes sufficiently high, a situation is created where the number of free electrons available in the channel is greater than the number of holes in the p-substrate. This phenomenon is referred as an inversion. Now that, the channel has become N-type electrons can move from the source side to the drain terminal, and there would be rise in the drain current.

Similarly the n-type substrate of a PMOS transistor is normally connected to the drain voltage. The voltage at drain side would be lesser than that of the source. If the gate-source voltage is zero or even at the positive voltage, then no current would travel from source to drain, due to absence of the channel. Thus, we assume that the transistor has turned off. When the voltage applied at gate is in negative (lesser than 0 volt), an electric field is developed across the channel, as a result free holes are attracted at the Si-SiO<sub>2</sub> interface. When a gate voltage becomes sufficiently negative in magnitude, a situation is created where the amount of free holes at the channel outnumbers the electron numbers available

in the n-substrate. Again, the channel has become inverted (p-type), it would be feasible for holes to move from the source to the drain terminal, and drain current starts to rise.

Thus, whenever the gate voltage applied is higher than the MOSFET's threshold voltage, a strong channel inversion occurs below the gate. The material used to build the MOS structure determines the threshold voltage. There occurs a deposition of holes in PMOS and electrons in NMOS below the gate. Then, the drain voltage sweeps the charge carriers, and hence the current flows in the MOSFET.

One of the applications of the MOSFET is that, they act as a switch when operated under cut-off and saturation regions. As an ideal switch, it is expected that when a transistor is turned off, it does not dissipate any power, and when turned on, it would deliver a large amount of current. However, the MOSFET used in practical applications exhibit a small leakage current as well, thus even when turned OFF, some power would get consumed. It is referred as static power dissipation (P<sub>s</sub>), and is represented by:

$$P_S = V_{DD}I_{OFF} \tag{1.1}$$

In the above equation, V<sub>DD</sub> represents the supply voltage and I<sub>OFF</sub> represents the leakage current. Besides, When a MOSFET transitions from ON to OFF state or vice versa, a significant power gets consumed as well. This type of power consumption is called as dynamic power dissipation (PD) and is given by the following relation:

$$P_D = V_{DD}^2 C_L \alpha f \tag{1.2}$$

In the above equation,  $V_{DD}$  represents the supply voltage, f denotes operational frequency,  $C_L$  is the load capacitance and  $\alpha$  is the switching probability.  $C_L$  represents the combination of the input capacitances and interconnect capacitances [5].

## 1.2 CMOS Scaling

CMOS scaling is the process in which the dimensions of the MOSFET are decreased in such a manner that the functionality of the device does not get affected. Scaling MOS transistors is the process of reducing the overall dimensions of devices as much as

technology allows while maintaining the geometric ratios similar to as in larger devices. The scaling theory was put forward by Dennard in 1974 [7].

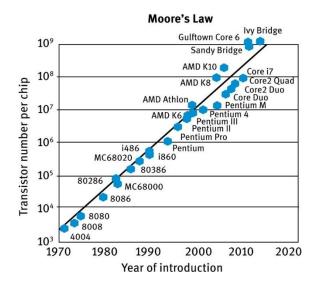

Until recent past, the main aim of researchers in the MOSFET technology has been to miniaturize the size of the transistors, so that more and more components can be accommodated on a given area. This would also increase the functionality of the given chip, as the number of operations it can perform would increase as represented in figure 1.2. This exponential trend in miniaturization was predicted by G. Moore, which states: "After every 18 months, the number of components in an integrated circuit doubles". From the past five decades, Moore's law has stood true and this law is being seen as a benchmark of industry progress [8]. Moreover, the advantages of the CMOS scaling are that the input capacitance of the MOSFET decreases and the current driving capability of MOSFET increases. However, the constraint remains that despite the fact that the drive current of MOSFETs increases, but because of its limitation due to the short channel effects, the OFF current also rises due to the shorter gate length [9]. As a result of the increase in OFF current, an increase in the static power dissipation occurs. The aggressive pace at which the CMOS scaling is done, it is predicted by the researchers that the range of static power dissipation in conventional MOSFETs will soon surpass the range of dynamic power dissipation.

Figure 1.2 Illustration of Moore's law [10]

The other major limitation of static power dissipation is that it would drain large power from the battery even when the device is turned OFF. This would result in the draining of the battery although the device is not in use. For a handheld devices like PDA, smartphones, etc., it would be detrimental in terms of their battery performance. Furthermore, the static power dissipation would also result in the heat getting produced in the IC resulting in the temperature rise, although the gadget might have been optimized for the best performance with respect to the ambient room temperature. Equations (1.1) and (1.2) provides us some parameters with which the power dissipation could be reduced. However, the fundamental limitation of MOSFET is that: to increase current by tenfold, around 60 mV of voltage is required (ideally). This constraint occurs due to the Maxwell-Boltzmann distribution, and is more popularly referred as "Boltzmann tyranny". It is important in the MOSFET to achieve the current in the range of around ( $\sim 10^4$  to  $10^6$ ) so that OFF state can be distinguished from ON state. Thus, accordingly we can say, that the minimum amount of supply voltage required would be  $60 \times \log (10^6) = 360 \text{ mV}$ . This results also indicates that if the supply voltage is scaled aggressively to a smaller value, it would be extremely difficult to distinguish between the OFF-ON switching. This would prevent the MOSFET to act as a switch. Therefore, we can conclude that due to the "Boltzmann tyranny" the conventional MOSFETs cannot be used as a switch at ultra-low supply voltages.

## 1.3 Short Channel Effects in MOSFET

The reasons for the occurrence of short channel effects in the MOSFET are as follows: (1) Limitations on electron drift characteristics (2) When the channel length is shortened, the threshold voltage changes. By definition, a short channel device is one in which the channel length and the depletion region thickness is almost off the same order in magnitude [11, 12]. As the channel length decreases, the lateral electrical field increases. For lower field values, the drift velocity is directly proportional to the electrical field, but as the electrical field increases, it begins to saturate. It is known as velocity saturation, and has a major impact on short channel MOSFETs' current voltage characteristics. [13-15].

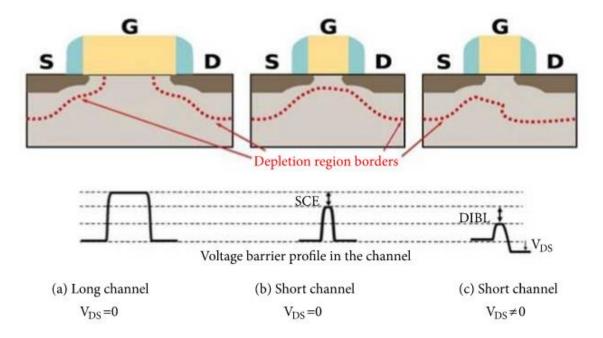

## 1.3.1. Drain Induced Barrier Lowering Effect

In the long channel MOSFET, the source to drain channel is exclusively controlled by the gate voltage. Barrier height at source to channel modulates the gate voltage, causing the electrons to drift from the source to the drain. But, due to CMOS scaling, the channel length is shortened aggressively, thus the drain-channel and the source-channel interface interact with each other. So the gate voltage regulates the height of the barrier between the source and the channel. The electron energy levels would be reduced, as well as the source to channel barrier height as shown in figure 1.3. This leads to the phenomena called as drain induced barrier lowering (DIBL) effect. The result would be an increase in the leakage current [16-18]. This effect is not so prominent in long channel devices simply because there is no interaction between the two depletion regions.

Figure 1.3 DIBL effect in MOSFET [19]

## 1.3.2. Threshold Voltage Roll-off

Because of the heavy doping at drain and source regions of MOSFET, there is an overlap with the p-channel substrate. Since the gate length has already been shortened due to the scaling, so the width of the depletion junctions become significant. As a result, the channel is not any longer solely controlled by the applied gate voltage. Besides, the control over

the charge on the channel by the gate voltage also reduce. In comparison to an undepleted MOS capacitor, the voltage required to invert the channel is significantly lower. The "threshold voltage roll-off" is a well-known short channel effect that results in a decrease in threshold voltage as gate length decreases [20].

The potential barrier is decreased although gate-source voltage is less than the threshold voltage, allowing current to flow across source and drain. The subthreshold current  $(V_{GS} < V_{T0})$  is the current that flows in the channel under such conditions. The approximate equation for subthreshold current is given by:

$$I_D(weak) = I_{ON}e^{(V_{GS} - V_{ON}) \cdot \left(\frac{q}{nkT}\right)}$$

(1.3)

From the equation, it can be identified that the subthreshold current has the exponential dependence on both the drain and the gate voltages. A lower  $V_T$  would mean significant rise in the subthreshold leakage current. Thus, if the threshold voltage roll-off occurs, the OFF current would increase exponentially. This would decrease the  $I_{ON}/I_{OFF}$  ratio significantly as well [21].

#### 1.3.3. Boltzmann Tyranny

A steep transition is required from ON to OFF state in the current, and vise - versa, for any device to act as a switch. However, as discussed at the beginning of the chapter, a fundamental limit for the rate at which current changes in accordance to the applied gate voltage is characterized by thermal current transport across the source—channel barrier height in case of a MOSFET.

An ideal MOSFET switch, should do a smooth and abrupt transition from ON state to OFF state, when voltage at gate terminal is lesser to the threshold voltage and should go from OFF state to ON state, when the voltage at gate side is higher than the threshold voltage as shown in figure 1.4. Subthreshold swing is the important parameter which measures the degree of abruptness of the transition from ON state of the transistor to the OFF state, and vice versa. It represents the minimum quantity of gate voltage needed to ten-fold the drain current [22].

Figure 1.4 A typical NMOS switch's characteristics and a comparison to an ideal switch (shown in dashed line)

## 1.4 Evolving FET Devices

In the earlier discussion, we have explained the basics of MOSFET, the various short channel effects that arise because of the continuous scaling, the limitation in terms of the thermal injection mechanism of current transport in MOSFET, unable to have a sharp doping profile, etc. All these shortcomings prevents the use of MOSFETs at sub-10 nm scale regime. Thus, researchers have explored the alternate technologies based on different mechanisms like BTBT, impact ionization, etc. to improve performance [4, 23, 24].

This in turn provides a lot of scope for the researchers to explore the new fields and develop the novel technologies in order to possibly replace conventional MOSFETs in future. TFET is one such novel device which can be explored with respect to its characteristics and the performance and would prove as one of the strong candidates to substitute conventional MOSFET in future.

## **CHAPTER 2: TUNNEL FILED EFFECT TRANSISTORS**

## 2.1 Basics of Tunnel Field Effect Transistors

## 2.1.1. TFET Structure

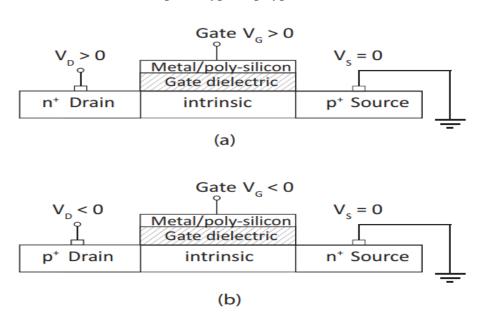

The basic TFET is a gated reverse biased P-I-N structure. Both N-type, as well as P-type TFETs, are illustrated in figure 2.1. The opposite doping of drain and source terminals is most distinguishing feature of TFETs. This feature is in contrast to a conventional MOSFET where drain and source terminals are interchangeable due to the same doped structure. The breakdown of a reverse biased p-n junction occurs due to two mechanisms: impact ionization and BTBT. Both require high electrical field and induces a significant current change corresponding to a small change in the voltage. Here we explore steep slopes by studying TFETs. As evident in the figure, for a p-type TFET  $p^+$  doping is done from drain side and  $n^+$  doping is done from source side. For n-type doped, the type of dopant is reversed for the drain and the source. Moreover, the channel is formed of an intrinsic semiconductor or low doped n-type or p-type semiconductor.

Figure 2.1 Biasing method and structure of: (a) n- TFET (b) p- TFET

Figure 2.1 represents the biasing methods of n-TFET and p-TFET. The source is grounded in an n-TFET, and the drain and gate terminals are both provided a positive voltage. Electrons are the dominant charge carriers inside, and flow of electrons is from the source terminal toward the drain terminal along the channel. While as in p-TFET, negative voltage is given to drain and gate terminals after source being grounded. Holes are the dominant charge carriers inside, and flow of electrons is from the source terminal toward the drain terminal along the channel. Both the types of TFET have a current transport mechanism being directed by band to band tunneling phenomenon (BTBT).

There are a few issues with this conventional design, like ambipolar behavior and weak drive current when compared to CMOS technology. To improve the parameters of a TFET, a double gate TFET (DGTFET) is implemented.  $n^+$  doping is done from drain side and  $p^+$  doping is done from source side. To suppress ambipolar behavior of TFET the source terminal is kept at the higher doping as compared to that of the drain terminal. Moreover, to attain greater ON current, a sharp doping profile on the source side is needed. The silicon body thickness is kept small to increase ON current. Since the gate is present on the two sides of the structure, its control over the channel is improved. The tunneling current improves nearly by the double as compared to single gated lateral TFET structure [25-28].

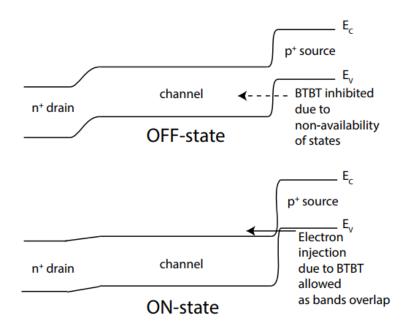

#### 2.1.2. TFET Operation

The band diagrams given in figure 2.2 represents the OFF condition and the ON condition for n-type TFET. The TFET is said to be in the OFF condition if gate to source voltage is nearer to zero. Valence band in the source lies below the channel's conduction band. In this case, BTBT is inhibited resulting in extremely low drain current. As the gate voltage is increased gradually, the carrier density gets modulated due to the gate voltage which in turn pushes down the conduction band in the channel. When the gate voltage becomes sufficiently high, bending of the band occurs at the source, as a result, the channel's conduction band gets aligned with the source's valence band. Electrons from source's valence band start to tunnel to the channel's conduction band. The positive drain bias voltage further sweeps these tunneled electrons towards the drain terminal. This explains the operation of n- type TFET.

Figure 2.2 Representation of an OFF state and ON state in n-type TFET.

It's worth noting that, unlike MOSFETs, TFETs are ambipolar devices. Hence, if the negative voltage is applied then the behaviour of the device would be like holes behaving as the dominant charge carriers essentially making the device p-type.

When a TFET is turned OFF, all the drain voltage drops across channel region and across the channel to drain and source to channel depletion region widths. While as, when the TFET is turned ON due to the sufficient amount of gate to source voltage, the channel resistance is significantly reduced as an inversion layer is formed. As a result, the large lateral electrical field is developed at interface of source-channel, thus, creating superior bending of bands at the source to channel interface. As a consequence, electrons from the source terminal would be injected into the channel region.

Landauer equation is used to obtain an equation for a drain current in a TFET analytically. It represents one-dimensional energy-conservation transport and is quite popular for nano scale integration devices. By performing an integration of the Landauer equation over the

energy range, we can obtain a drain current in the TFET [29, 30]. The electrons which are apart of energy overlap window of  $\Delta\Phi$  only can contribute to the significant drain current.

$$I_{D} = \frac{4|e|}{h} \sum_{k_{trans}} T_{tot} k_{trans} \int_{0}^{\Delta\emptyset} dE \left( f_{s}(E) - f_{d}(E) \right)$$

(2.1)

In the above equation,  $f_s$  and  $f_d$  represent the source and the drain fermi functions, and  $T_{tot}$  is the transmission function, e denotes the electronic charge while h represents the Planck's constant. Total transmission function  $T_{tot}$  is a parameter on which there is a heavy reliance of the drain current. The scattering event in the TFET can be due to tunneling and scattering within the channel, but, band to band tunneling (BTBT) is the dominant one, so we write

$$T_{\text{tot}} \approx T_{\text{RTRT}}$$

(2.2)

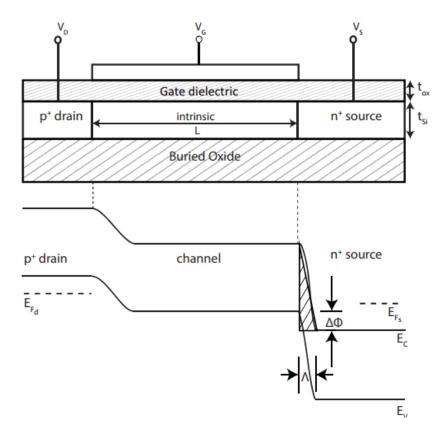

In the equation, BTBT represents tunnelling probability, and can be calculated by considering the barrier region as a triangular, as given in figure 2.3, and applying KWB approximation.

Considering a triangular barrier, the equation for the tunneling probability can be represented as:

$$P_{t} = \exp\left[-\frac{4\sqrt{2m}}{3\hbar F}(U_{0} - E)^{\frac{3}{2}}\right]$$

(2.3)

In the equation,  $P_t$  denotes the tunneling probability,  $(U_0 - E)$  denotes the difference between the particle's energy and the height of the barrier, m is the particle's mass,  $\hbar$  is the reduced Planck constant and F is the electric field in the region. By utilizing equation (2.3), we can find out the tunneling probability of the device represented in figure 2.3 as:

$$T_{BTBT} = \exp\left[-\frac{4\sqrt{2m^*}}{3|e|\hbar F} \left(E_g^*\right)^{\frac{3}{2}}\right]$$

(2.4)

Figure 2.3 Representation of p-type SOI TFET. The Energy band diagram depicts the triangular barrier approximation at the source

The effective bandgap, can therefore be expressed as [30]:

$$E_{g}^{*} = E_{g} + 2 \frac{\hbar^{2} k_{trans}^{2}}{2m^{*}}$$

(2.5)

In the given region, the electrical field is represented as:

$$F = \frac{E_g + \Delta \emptyset}{\Lambda} \tag{2.6}$$

where  $\Lambda$  denotes the transition region width at the interface of source to channel.

So, it can be written:

$$T_{\text{BTBT}} \approx \exp \left[ -\frac{4\sqrt{2m^*}E_g^{\frac{3}{2}}}{3|e|\hbar(E_g^* + \Delta\Phi)} \sqrt{\frac{\epsilon_{\text{Si}}}{\epsilon_{\text{ox}}}t_{\text{ox}}t_{\text{Si}}} \right]$$

(2.7)

Equation (2.1) demonstrates that the drain current is approximately **proportional** to the energy overlap window  $\Delta\Phi$  and  $T_{BTBT}$ . Thus, from eq. (2.7), we can say that:

$$I_D \propto \exp \left[ -\frac{4\sqrt{2m^*}E_g^{\frac{3}{2}}}{3|e|\hbar(E_g^* + \Delta\Phi)} \sqrt{\frac{\epsilon_{Si}}{\epsilon_{ox}} t_{ox} t_{Si}} \right] \Delta\Phi$$

(2.8)

## 2.2 Quantum tunneling phenomenon in TFETs

During the early 20th century, when the physicists performed the experiments at the atomic level, the results were quite astonishing. For example, the wave-particle duality was established based on the experiment of black body radiation and photoelectric effect. New theories were being put forward by physicists, like, Broglie's wave-particle duality principle, Bohr's atomic model, the Heisenberg uncertainty principle, and the Schrodinger equation etc. These theories were at times contrary to the classical physics, however they were backed by strong experimental evidences and hence were gradually accepted by the scientists by accepting the inadequacies in the classical physics.

In contrast to classical physics, the value of any physical quantity is calculated probabilistically in quantum mechanics. In fact, the phenomenon of BTBT is also possible because of the probabilistic behavior of nature. Newton's laws of motion is widely used in classical mechanics to determine the position or state of any particle, given its initial state and forces being applied are known. The similar kind of analogy is applicable to quantum mechanics as well. We can use, Schrodinger's quantum, equations to explain the nature of the wave function and how it varies with respect to time [31, 32]. However, the wave function representations are just probabilities or the expectation value. The Schrödinger equation is given for a particle restricted through the x-axis, as:

$$i\hbar \frac{\partial \Psi}{\partial t} = -\frac{\hbar^2}{2m} \frac{\partial^2 \Psi}{\partial x^2} + V\Psi \tag{2.9}$$

In the equation, i represents an imaginary number, t is time,  $\Psi$  is the wave function, V denotes potential energy and x is the position along the x-axis. Schrodinger's equations can be used to find out the value of the wave function  $\Psi$ . The particle's expectation values can be calculated as below:

$$\langle x \rangle = \int_{-\infty}^{+\infty} x |\Psi(x, t)|^2 dx \tag{2.10}$$

The Schrödinger's equation can be solved with the method of separation of variables, when the energy potential function V is time independent. The wave function of the Schrödinger equation can be expressed as:

$$\Psi(x,t) = \psi(x) \,\varphi(t) \tag{2.11}$$

where  $\psi(x)$  denotes the spatial component of  $\Psi(x,t)$  which is a function of only x, while  $\varphi(t)$  denotes temporal component of  $\Psi(x,t)$  which is a function of only t. Thus, following equations can be derived:

$$\varphi(t) = e^{\frac{iEt}{\hbar}} \tag{2.12}$$

$$\frac{\hbar^2}{2m}\frac{\partial^2 \Psi}{\partial x^2} + (E - V)\psi = 0$$

(2.13)

This equation represents the steady-state form of the Schrodinger equation. Equation (2.9) can be solved with the above equation, provided that the potential profile is independent of time. The solution that can be obtained for equation (2.13) won't be unique. Therefore, each solution would correspond to the specific value of the energy  $E_n$ . Consequently, the eigenvalues are the energy values  $E_n$  for which the Schrodinger Equation (2.13) can be solved and the respective wave functions ( $\Psi_n$ ) represent the Eigen functions.

## 2.3 Subthreshold swing in TFET

Steeper subthreshold swing is one of the most significant and the desired characteristics of the TFET, which distinguishes it from the conventional MOSFET. The energy band diagram in the subthreshold region at two separate gate voltages is shown in figure 2.4.

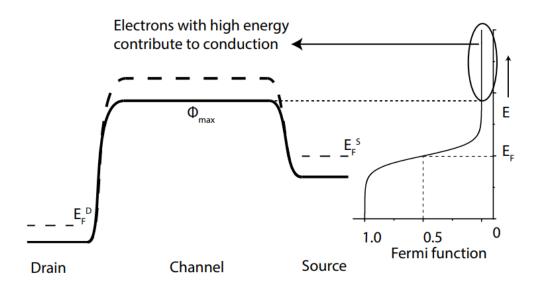

The transport of the current in the MOSFET is by the thermal injection of charge carriers from source towards drain with an application of sufficient gate voltage. Only those carriers which are having energies greater than  $\Phi_{max}$  at the source's exponential tail would add to the current near the subthreshold zone [33, 34]. In a conventional MOSFET, the drain current is proportional to source "Fermi–Dirac distribution function"  $f_s(E)$  density of state D(E), and the velocity of the carriers v(E) (E representing the electron energy) [34]:

$$I_d \propto \int dE. D(E). v(E). f_s(E).$$

(2.14)

Figure 2.4 Representation of conduction band at two separate gate voltages in the MOSFET

A Boltzmann approximation can be used to derive the source Fermi–Dirac distribution function  $f_s(E)$  in the exponential tail region:

$$f_s(E) \approx \exp\left(-\frac{E - E_F^s}{kT}\right)$$

(2.15)

In the above equation,  $E_F^s$  represents Fermi energy level at the source, T denotes the temperature and k represents the Boltzmann constant. The product of  $D(E) \times v(E)$  can be

considered as the constant for simplicity purpose, assuming just one spatial direction of transport. Likewise, it can be assumed for a MOSFET that whenever the gate to source voltage changes, there would be shift in the conduction band. Thus, it can be written:

$$\frac{\partial I_d}{\partial V_{GS}} = |e| \frac{dI_d}{dE} \tag{2.16}$$

where *e* represents the electronic charge. Using Equation (2.15) and Equation (2.16), in an ideal MOSFET, the subthreshold swing can be calculated as:

$$SS = \left(\frac{\partial \log(I_d)}{\partial V_{GS}}\right)^{-1} = \ln(10) \left(\frac{1}{I_d} \frac{\partial I_d}{\partial V_{GS}}\right)^{-1} \approx \ln(10) \frac{kT}{e}$$

(2.17)

For a conventional MOSFET, an ideal value of subthreshold swing at the room temperature is around 60 mV/decade, which is also being depicted from equation (2.17). The experimental results of the subthreshold swing for a MOSFET would have been worse than that of equation (2.17) simply because the gate voltage control over the potential of the channel and profile of the conduction band will be imperfect.

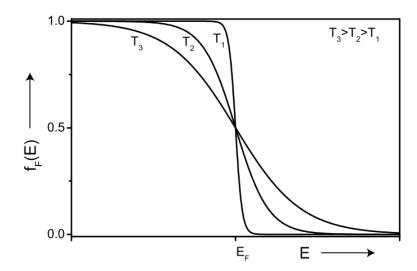

Equation (2.17) also illustrates that as the temperature rises, there would be an increase in the ideal subthreshold swing. The Fermi–Dirac distribution function  $f_F(E)$  can be written by the following expression:

$$f_F(E) = \frac{1}{1 + exp\left(\frac{E - E_F}{kT}\right)}$$

(2.18)

The temperature's effect on the distribution function of Fermi-Dirac is shown in the figure 2.5. The probability of carriers occupying higher energy states would increase as the temperature would rise. In a conventional MOSFET, the subthreshold current is caused by higher-energy carriers across the energy barrier. As a result, the temperature-dependent enlargement of the Fermi-Dirac distribution function of the carriers is responsible for the limit defined in Equation (2.17). Now we'll look at how TFETs get around this limitation.

Figure 2.5 Fermi–Dirac distribution at different temperatures T<sub>3</sub>, T<sub>2</sub> and T<sub>1</sub>. As the temperature rises, the exponential tail becomes more prominent [35]

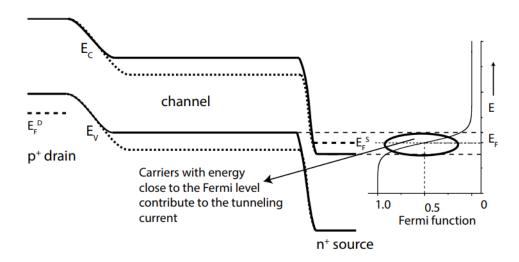

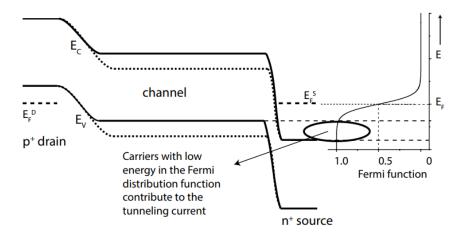

Figure 2.6 Band diagram at subthreshold region of p-type TFET at two different gate voltages [34].

The energy band diagram in subthreshold region of a p-TFET, at two separate gate voltages is shown in figure 2.6. The holes would tunnel into the channel, whenever a negative gate voltage is given, as at source, the channel is drawn above conduction band. If the valence band is lower than the conduction band, no tunnelling occurs. The channel prevents carriers from tunneling with energy in the Fermi– Dirac distribution's high-energy tail. The Fermi– Dirac distribution's low-energy tail is cut off at the source contact by the semiconductor

bandgap as shown in figure 2.7. When the channel's valence band gets aligned with source's conduction band, however, BTBT is activated, causing the state to switch from OFF condition to ON state abruptly.

Figure 2.7 Representation of Energy band diagram when the Fermi energy level is high from the source side in TFET [34].

## 2.4 Ambipolar Current in a TFET

In a TFET, there are two tunnelling junctions: first at the drain—channel interface while as second at source-channel interface. Usually, in a TFET, the BTBT is suppressed in the drain-channel junction by reducing the doping of the drain terminal or by means of some other methods. When the TFET is symmetric, that is, when the doping concentration remains on the source and drain sides but in the opposite manner, the TFET exhibits ambipolar behaviour [36-38]. Ambipolar behaviour denotes the presence of n-type behaviour in the same TFET, when the main contribution to the current transport is due to electrons and a p-type behavior at the same drain voltage V<sub>DS</sub> when the main contribution to the current transport is due to electrons. For an n-TFET, if the gate to source voltage is positive, there would be a tunneling phenomenon at the source region side, while as if the applied gate to source voltage is negative, at that time again there would be a tunneling phenomenon at the drain side, while maintaining the same drain source voltage.

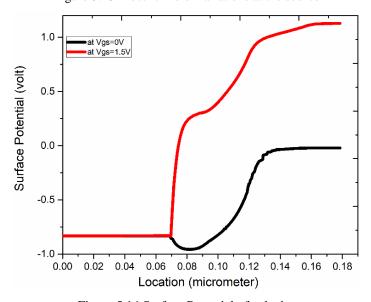

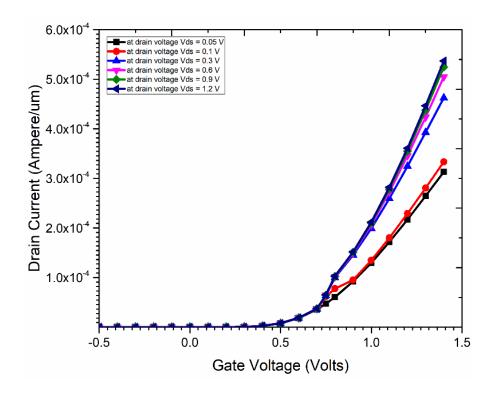

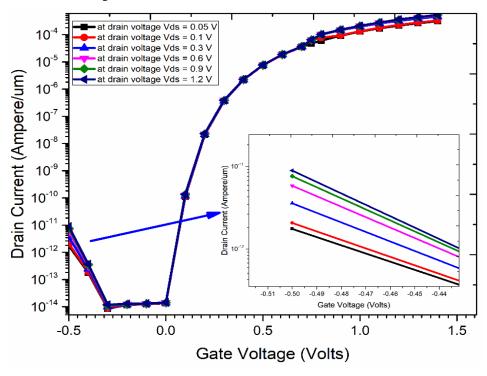

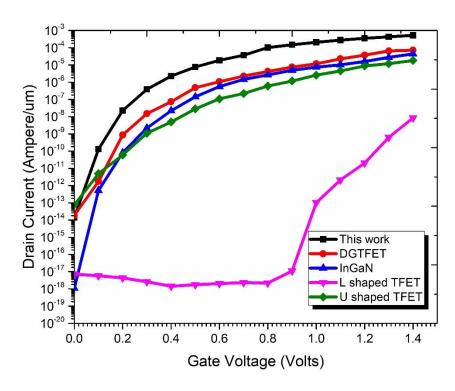

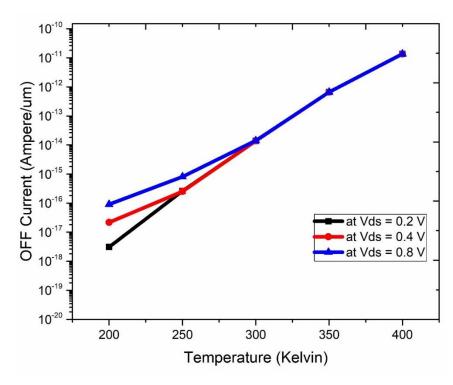

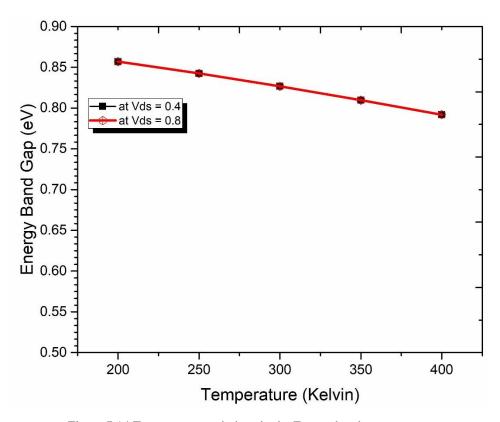

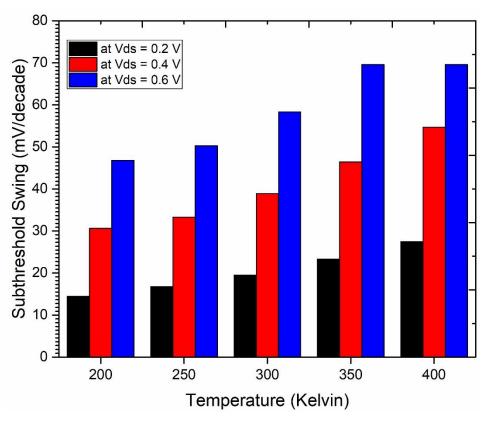

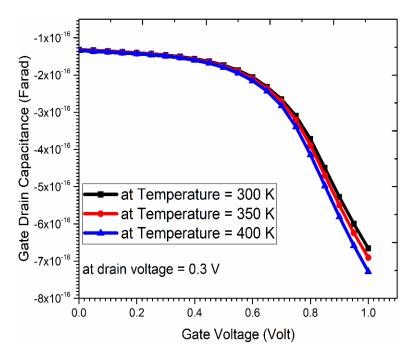

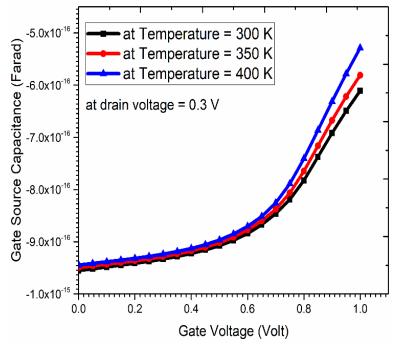

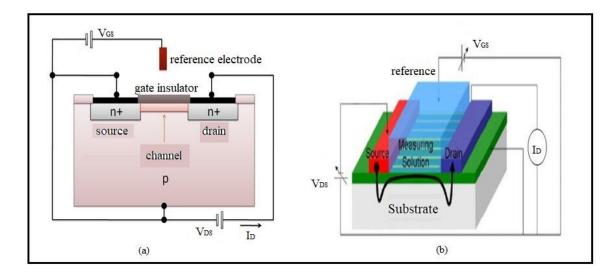

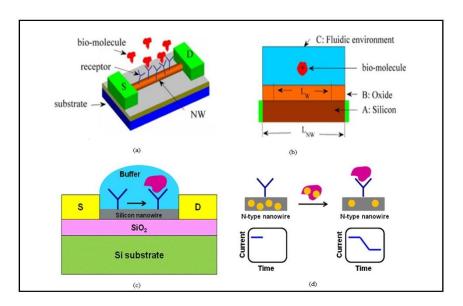

When  $V_{GS}$  is positive, as it is in the DGTFET's regular n-type mode of operation, the valence band, conduction band get aligned on source side. When  $V_{GS}$  is negative, however, on the drain side, the bands are matched, as a consequence of which there is a BTBT from the drain side. Thus, it can be observed that whenever  $V_{GS}$  is positive, electrons are the primary cause of conduction and the conduction is primarily owing to the holes when  $V_{GS}$  is negative.