# DESIGN & ANALYSIS OF A NOVEL HYBRID 8 × 8 BIT MULTIPLY AND ACCUMULATE (MAC) ARCHITECTURE USING CLOCK GATING SCHEME FOR PIPELINED PROCESSING

А

Thesis

#### Submitted to

# For the award of **DOCTOR OF PHILOSOPHY (Ph.D.)**

in

### **Electronics & Electrical Engineering**

By

### Rajkumar Sarma 41400103

Supervised by

Co-supervised by

Dr. Cherry Bhargava

Dr. Shruti Jain

### LOVELY FACULTY OF TECHNOLOGY & SCIENCES LOVELY PROFESSIONAL UNIVERSITY PUNJAB 2020

### **CANDIDATE DECLARATION**

I hereby certify that the work which is being presented in the thesis, entitled "**Design** & analysis of a novel hybrid  $8 \times 8$  bit Multiply and Accumulate (MAC) architecture using clock gating scheme for pipelined processing" in fulfilment of requirements for the award of degree of Doctor of Philosophy in Electronics & Electrical Engineering is an authentic record of my own research work carried out under the supervision of Dr. Cherry Bhargava & co-supervision of Dr. Shruti Jain. The matter presented in this thesis has not been submitted elsewhere in part or fully to any other University or Institute for the award of any degree.

#### **Rajkumar Sarma**

(**Registration No: 41400103**) School of Electronics & Electrical Engineering Lovely Professional University Phagwara. Punjab, India Date:

### CERTIFICATE

I hereby certify that **Rajkumar Sarma** (**Registration No: 41400103**) has prepared thesis entitled "Design & analysis of a novel hybrid  $8 \times 8$  bit Multiply and Accumulate (MAC) architecture using clock gating scheme for pipelined processing", for the award of degree of Doctor of Philosophy in Electronics & Electrical Engineering, under my guidance. The matter presented in this thesis has not been submitted elsewhere in part or fully to any other University or Institute for the award of any degree.

#### **Dr. Cherry Bhargava**

Associate Professor & Head VLSI Design School of Electronics & Electrical Engineering Lovely Professional University Phagwara, Punjab, India Date:

#### Dr. Shruti Jain

Associate Professor

Department of Electronics & Communication Engineering Jaypee University of Information Technology Waknaghat, Solan, HP, India Date:

### ABSTRACT

In the era of digital signal processing, like graphics and computation systems, multiplication-accumulation (MAC) is one of the prime operations. A MAC unit is a vital component of a digital system, like different FFT algorithms, convolution, image processing algorithms, etcetera. In this research work, various MAC architectures, along with its sub-blocks such as adder and multiplier, are reviewed thoroughly. The study shows that the efficiency of a MAC unit, along with its sub-blocks is mainly dependent upon the speed of operation, power dissipation, and chip area of the circuit along with the complexity level of the circuit. Many of the researchers have also emphasized on optimization of these design constraints to make the MAC efficient. Earlier studies have stressed on increasing the efficiency of the overall MAC unit, whereas some have presented the techniques to produce remarkable efficiency of the sub-blocks. In this research work, the effectiveness of the MAC is further improved by adopting both the approaches, i.e., the overall architecture of the MAC unit is optimized by applying a novel algorithm and the performance of the sub-blocks of the MAC is maximized by choosing hybrid design techniques. Techniques such as block enabling and pipelining are adopted in the proposed MAC architecture to make the overall unit efficient. A novel Universal Compressor based Multiplier (UCM) architecture is also proposed to make the sub-blocks of the MAC more efficient.

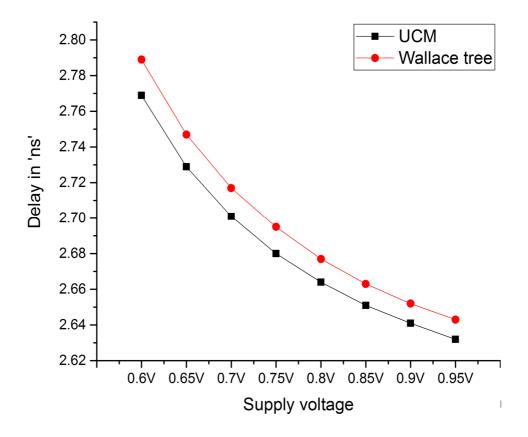

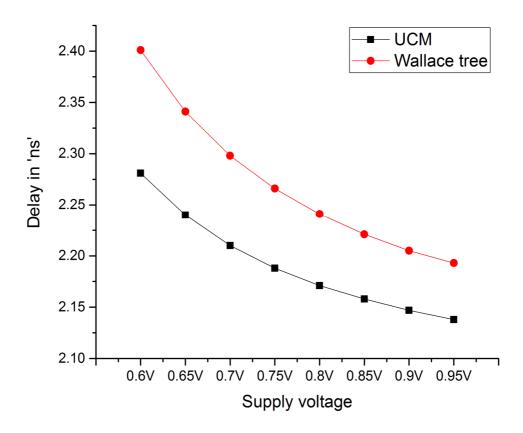

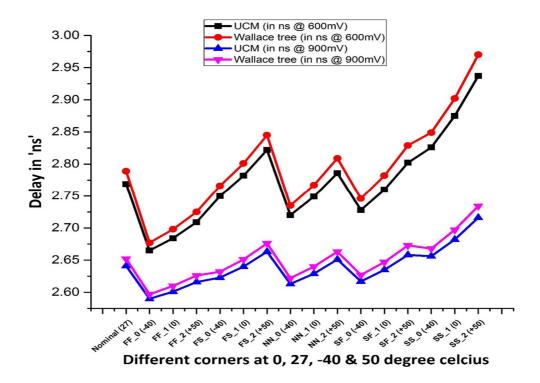

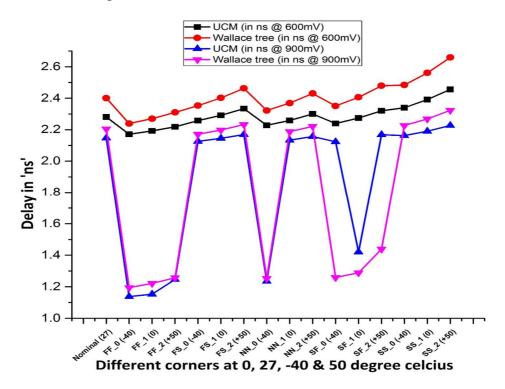

The proposed UCM yields a high-speed operation, and hence, the enhanced performance is reported. The novel design of UCM is analyzed using the Cadence Spectre tool in 90 nm CMOS technology, which is further prototyped on the Nexys-4 Artix-7 FPGA board. Also, a Process-Voltage-Temperature (PVT) variation analysis is performed on the UCM architecture using Cadence ADE-XL for proper validation, which results in faster operation in ultra-low supply voltages (less than 0.9 V) for higher-order bit multiplication. In comparison to Wallace tree-based architecture (in 0.6 V to 0.9 V supply voltages), the proposed design has reduced the delay by 0.73% and 5.05% for  $5 \times 5$ -bit and  $9 \times 9$ -bit operations respectively.

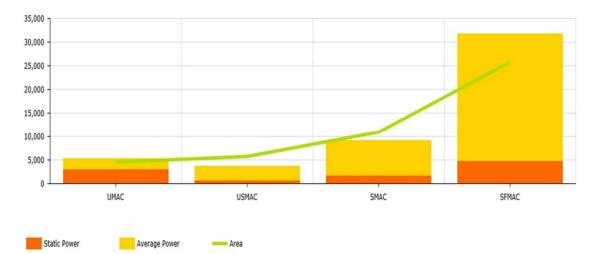

The novel architectures for Unsigned MAC (UMAC), Unsigned Synchronized MAC (USMAC), Signed MAC (SMAC), and Signed Floating-point MAC (SFMAC) are designed using proposed UCM architecture. The designed architectures are simulated on CMOS 90nm technology using Cadence Virtuoso. The UMAC, USMAC, and SMAC can accommodate two 8-bit inputs and produces 16-bit output. Additionally, an extra bit is used in the case of SMAC architecture for representing a signed number.

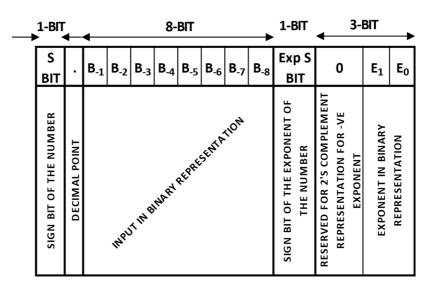

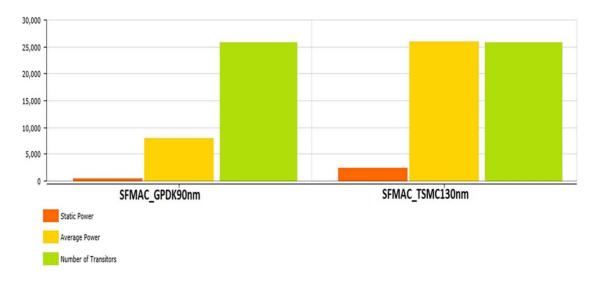

On the other hand, each input of the SFMAC representation is of 13 bits, in which two bits are reserved for the sign bits of the number and its exponent. Remaining eleven bits are used for 8-bit binary representation and 3-bit exponent representation. Therefore, the input numbers in the proposed SFMAC have a range from  $-(0.1111111)_2 \times 2^{+3}$  to  $+(0.11111111)_2 \times 2^{+3}$  and hence, the range of the inputs in a decimal number system is from  $-(7.96872)_{10}$  to  $+(7.96872)_{10}$ . The performance of UMAC, USMAC, SMAC, and SFMAC architectures are compared on the basis of power at 2V supply voltage, 20 ns simulation period, and 333.33 MHz clock frequency. It is inferred that the SFMAC results in maximum static and average dynamic power in comparison to other proposed MAC architectures because the transistor count in SFMAC is 2.5 and 5 times more than SMAC and USMAC architecture respectively. Furthermore, a power comparison of SFMAC architecture at different CMOS technologies (TSMC 130 nm and GPDK 90 nm) in a specific input vector is studied at a frequency of 83.33 MHz. Finally, a performance comparison of the proposed MAC architectures and the existing architectures are discussed in detail, which shows significant improvement in terms of static as well as average power.

**Keywords:** Compressor-based Multiplier; Low power; High speed; Nexys-4 Artix-7 FPGA; Cadence Virtuoso; Signed-Floating-point MAC; Block Enabling; Clock Gating.

## ACKNOWLEDGEMENT

I am deeply indebted and grateful to many people who supported me during the research work and preparation of the thesis.

First and foremost, I give special thanks and glory to the God Almighty for giving me the wisdom and health to complete this endeavor.

I would like to express sincere gratitude and appreciation to my supervisor **Dr. Cherry Bhargava**, Associate Professor, School of Electronics & Electrical Engineering, Lovely Professional University (Phagwara, Punjab) for her constant encouragement, support and guidance. Her sincerity, positive and supportive attitude, calmness and scholarly advice have been a steady source of inspiration to me. Her guidance helped me all the time during my research work. I could not have imagined having a better advisor and mentor for my Ph.D. study.

It is an honor and great privilege to pay ineffable gratitude to **Dr. Shruti Jain**, Associate Professor, Department of Electronics & Communication Engineering, Jaypee University of Information Technology (Waknaghat, Solan, HP), for her guidance and assistance as co-supervisor. Her creative comments and suggestions from the initial conception till the completion of this work are highly appreciated. I am greatly indebted to her for her valuable advice, constructive criticism and their extensive discussions around my work.

I will forever be thankful to **Dr. Sandeep Dhariwal**, Associate Professor, Alliance College of Engineering and Design, Alliance University, (Bengaluru), for his encouragement and support. His invaluable and scholastic insights always motivated me.

I want to thank **Dr. Loviraj Gupta**, Executive Dean, Lovely Faculty of Technology & Sciences, Lovely Professional University (Phagwara, Punjab) for providing me valuable suggestion during my patent filing. This has helped me to expand my work in a different level.

I am greatly thankful to **Mr. Ashok Mittal**, Honorable Chancellor, Lovely Professional University (Phagwara, Punjab) for providing me required facilities to carry out my research work.

I express my veneration to **Prof. Bhupinder Verma**, Head of the School and all my colleagues of School of Electronics & Electrical Engineering, Lovely Professional University (Phagwara, Punjab) for their encouragement and support. I acknowledge the contribution of the technical and non-technical staff in the School of Electronics & Electrical Engineering, Lovely Professional University (Phagwara, Punjab) for providing necessary facilities during the pursuit of my research.

Nobody has been more important to me in the pursuit of this research work than the members of my family. I owe heartfelt thanks to my parents, my siblings and my inlaws for their love, motivation, encouragement and guidance when it was mostly required. Most importantly, I owe a lot to my ever supporting and caring wife **Dr**. **Subha Lakshmi Saikia**, who have provided me unending inspiration emotionally and mentally. I always fall short of words and felt impossible to describe her support in words.

Rajkumar Sarma

# **TABLE OF CONTENTS**

| ABSTRACTiii                                               |

|-----------------------------------------------------------|

| ACKNOWLEDGEMENTv                                          |

| LIST OF FIGURESx                                          |

| LIST OF TABLESxii                                         |

| LIST OF ABBREVIATIONS xiii                                |

| CHAPTER 1: INTRODUCTION1                                  |

| 1.1 NEED FOR LOW-POWER DESIGN                             |

| 1.1.1 Causes for power dissipation4                       |

| 1.2 FACTORS AFFECTING HIGH-SPEED DESIGN                   |

| 1.3 INTRODUCTION TO MULTIPLY & ACCUMULATE (MAC)           |

| ARCHITECTURE                                              |

| 1.3.1 Multiplier10                                        |

| 1.3.2 Accumulator                                         |

| 1.3.3 Adder13                                             |

| 1.3.4 Block enabled technique & pipelined architecture13  |

| 1.4 SIGNIFICANCE OF THIS RESEARCH15                       |

| 1.5 ROADMAP OF THE THESIS16                               |

| CHAPTER 2: REVIEW OF LITERATURE                           |

| 2.1 ADDER AND MULTIPLIER17                                |

| 2.2 MULTIPLY AND ACCUMULATE UNIT                          |

| 2.3 MOTIVATION & TECHNICAL GAP                            |

| 2.4 OBJECTIVE OF THE RESEARCH                             |

| CHAPTER 3: UCM-A NOVEL APPROACH FOR DELAY OPTIMIZATION 37 |

| 3.1 INTRODUCTION                                          |

| 3.2 WALLACE TREE MULTIPLIER ARCHITECTURE                      | .39 |

|---------------------------------------------------------------|-----|

| 3.3 DESIGN PROCESS OF UCM ARCHITECTURE                        | .40 |

| 3.3.1 UCM architecture                                        | .41 |

| 3.3.2 Addition of partial products                            | .42 |

| 3.3.3 Special cases                                           | .44 |

| 3.4 CONCLUSIVE REMARKS                                        | .45 |

| CHAPTER 4: UNSIGNED/SIGNED FIXED-POINT MAC ARCHITECTURE       | C   |

| (UMAC, USMAC & SMAC)                                          | .46 |

| 4.1 INTRODUCTION                                              | .46 |

| 4.2 BASIC BUILDING BLOCKS OF MAC                              | .47 |

| 4.2.1 Multiplier                                              | .48 |

| 4.2.2 Adder                                                   | .49 |

| 4.3 EXISTING ARCHITECTURES OF MAC UNIT                        | .50 |

| 4.4 PROPOSED MAC ARCHITECTURES                                | .55 |

| 4.4.1 Proposed Unsigned MAC architecture (UMAC)               | .56 |

| 4.4.2 Proposed Unsigned Synchronized MAC architecture (USMAC) | .57 |

| 4.4.3 Proposed Signed MAC architecture (SMAC)                 | .60 |

| 4.5 CONCLUSIVE REMARKS                                        | .62 |

| CHAPTER 5: MUX BASED SIGNED FLOATING-POINT MAC (SFMAC)        |     |

| ARCHITECTURE                                                  | .63 |

| 5.1 INTRODUCTION                                              | .63 |

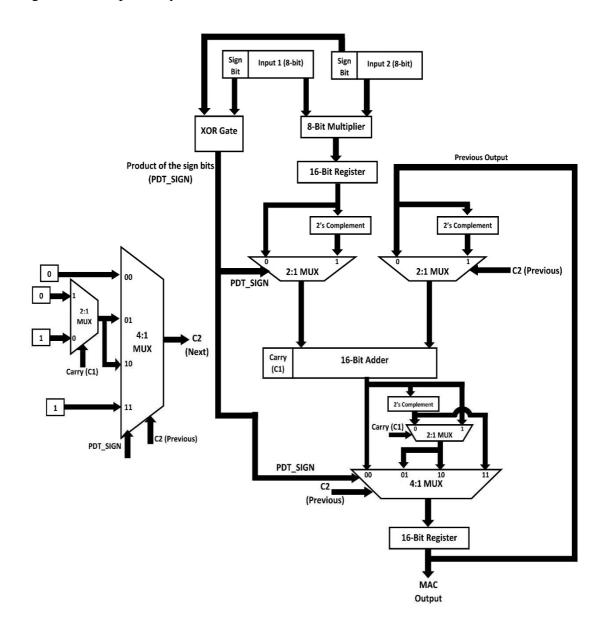

| 5.2 SFMAC ARCHITECTURE                                        | .67 |

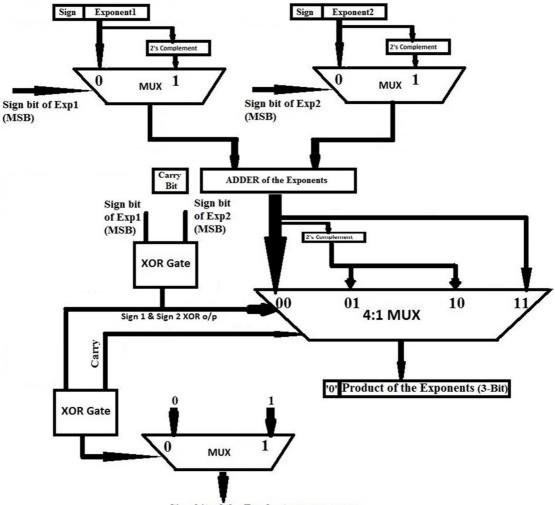

| 5.2.1 Exponential Adder (EA)                                  | .69 |

| 5.2.2 8-bit multiplier                                        | .71 |

| 5.2.3 16-bit register                                         | .71 |

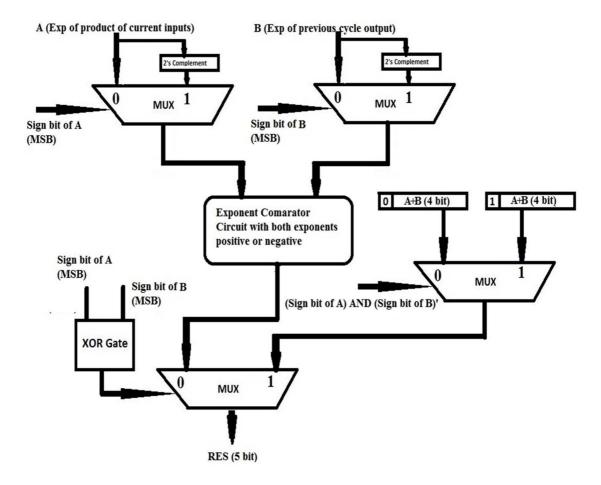

| 5.2.4 Exponent Comparator Circuit (ECC)                       | .71 |

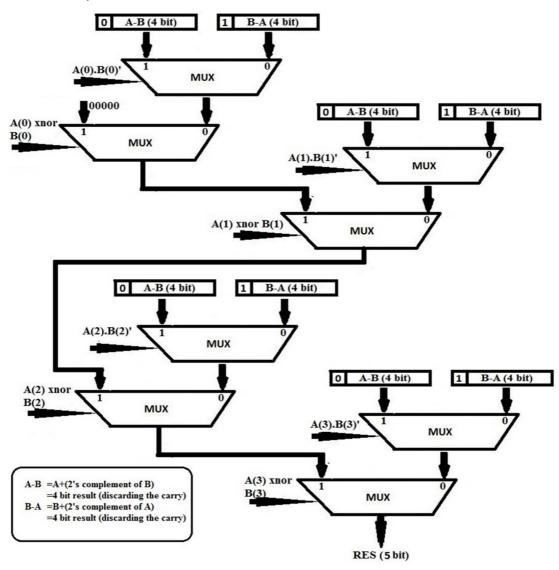

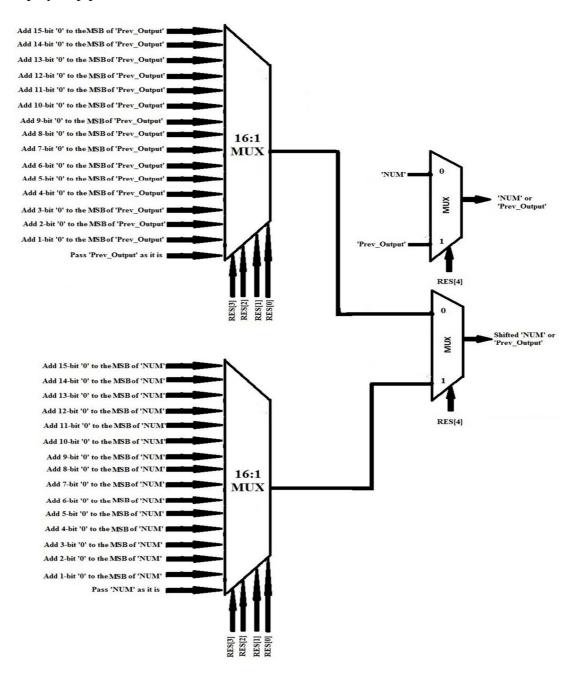

| 5.2.5 Exponent Shifter Circuit (ESC)74                                                 |

|----------------------------------------------------------------------------------------|

| 5.2.6 16-bit adder75                                                                   |

| 5.2.7 2:1/4:1 multiplexers of different sizes                                          |

| 5.2.8 Explanation of SFMAC using binary values75                                       |

| 5.3 CONCLUSIVE REMARKS                                                                 |

| CHAPTER 6: RESULTS & DISCUSSION81                                                      |

| 6.1 IMPLEMENTATION OF UCM ARCHITECTURE & FPGA<br>PROTOTYPING                           |

| 6.1.1 Power & delay analysis of novel UCM architecture82                               |

| 6.1.2 Nexys-4 Artix-7 based FPGA Implementation                                        |

| 6.1.3 PVT analysis of UCM architecture                                                 |

| 6.2 POWER, DELAY & AREA COMPARISON OF NOVEL UMAC,<br>USMAC, SMAC & SFMAC ARCHITECTURES |

| 6.2.1 Comparison with existing architectures                                           |

| CHAPTER 7: CONCLUSION & FUTURE WORK94                                                  |

| 7.1 CONCLUSION94                                                                       |

| 7.2 FUTURE WORK DIRECTIONS96                                                           |

| REFERENCES97                                                                           |

| LIST OF PUBLICATIONS108                                                                |

# **LIST OF FIGURES**

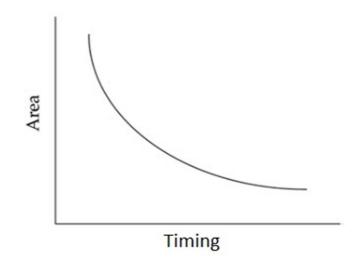

| Figure 1.1: Area versus Timing trade-off                                            | 2 |

|-------------------------------------------------------------------------------------|---|

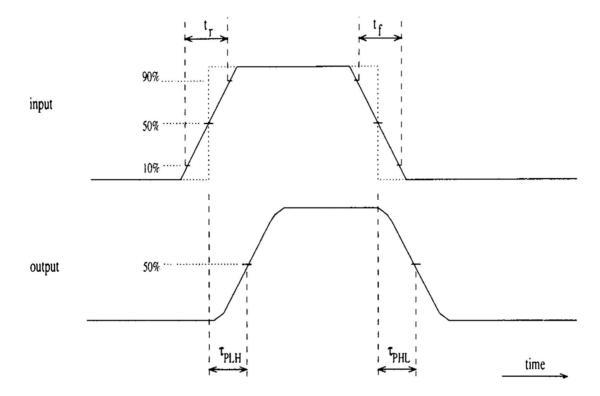

| Figure 1.2: Rise-fall time during input output transitions                          | б |

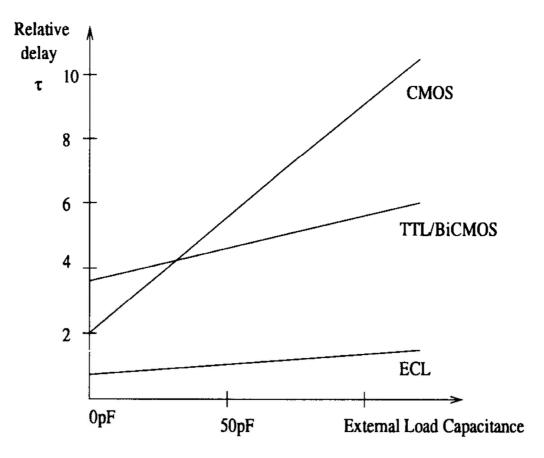

| Figure 1.3: Propagation delay versus load capacitance for different logic families? | 7 |

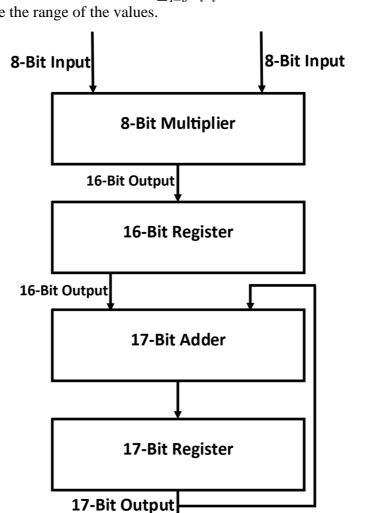

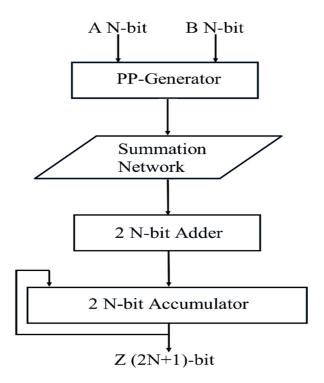

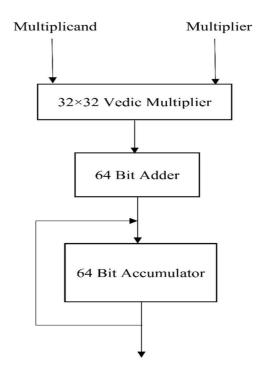

| Figure 1.4: Generalized block diagram of $8 \times 8$ bit MAC                       | 9 |

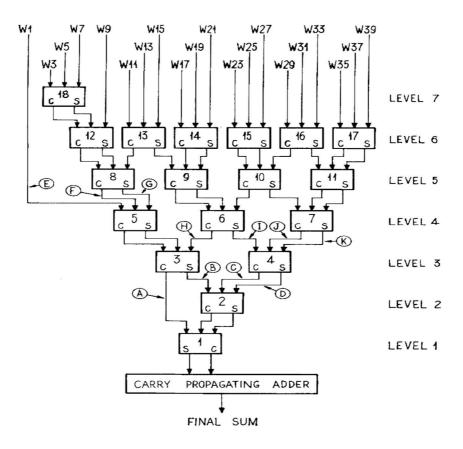

| Figure 1.5: 4-bit Wallace tree multiplier1                                          | 1 |

| Figure 1.6: Basic accumulator or register circuit12                                 | 2 |

| Figure 1.7: Pipelined and Block enabled Architecture                                | 4 |

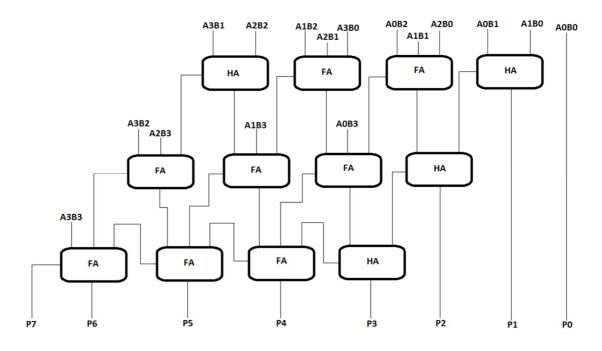

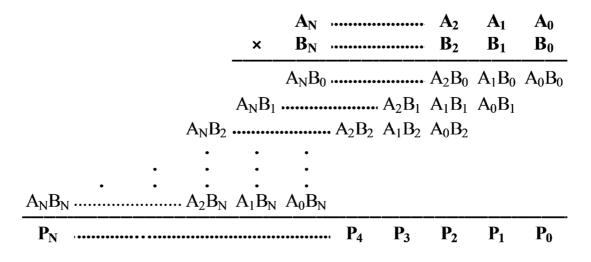

| Figure 3.1: Basic multiplication operation                                          | 8 |

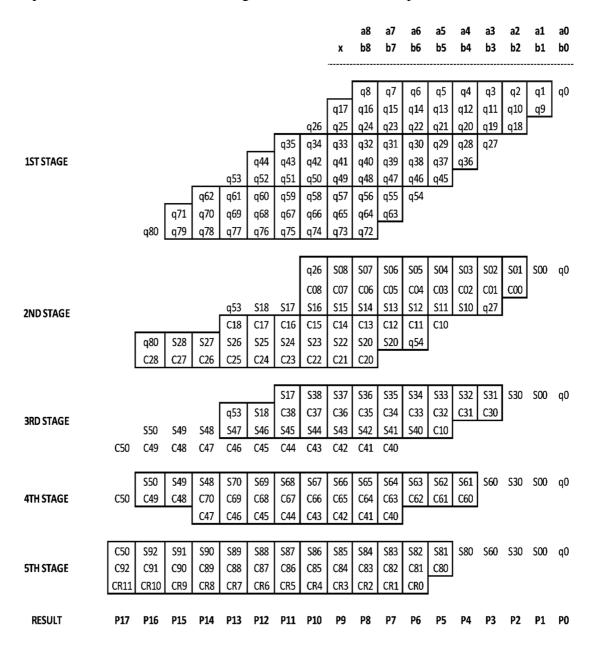

| Figure 3.2: Wallace tree multiplier for $9 \times 9$ bit multiplication             | 0 |

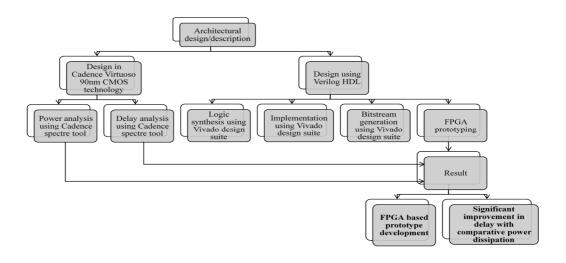

| Figure 3.3: UCM architecture design process flow                                    | 1 |

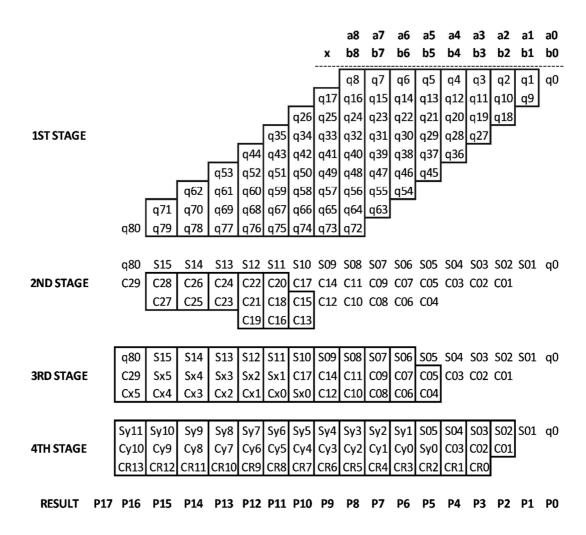

| Figure 3.4: UCM architecture for $9 \times 9$ bit multiplication                    | 2 |

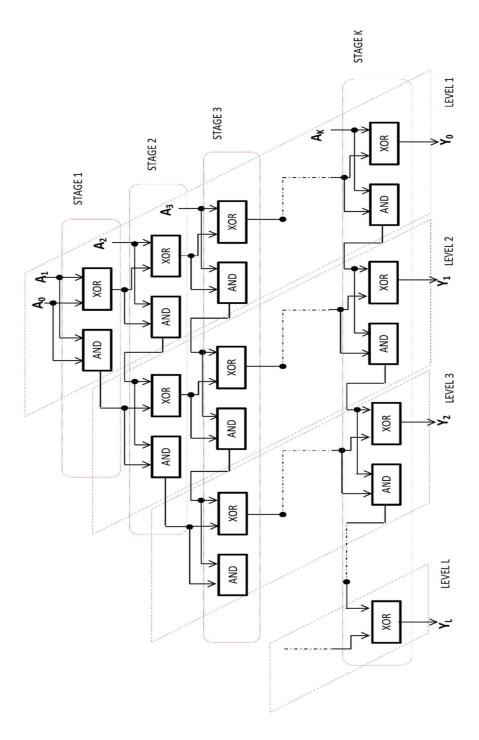

| Figure 3.5: AND-XOR gate arrangement with K stages and L levels44                   | 4 |

| Figure 4.1: Basic MAC Unit                                                          | 7 |

| Figure 4.2: Wallace tree multiplier (addition of partial products)                  | 9 |

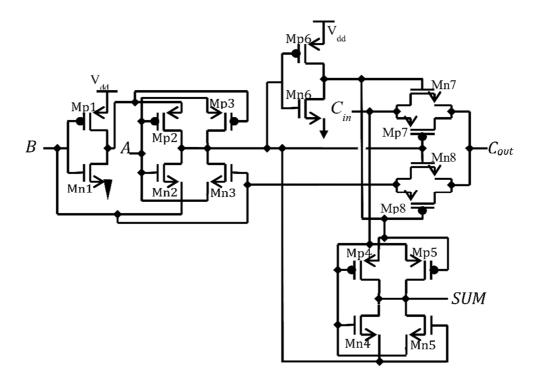

| Figure 4.3: Full adder design which uses both CMOS and TG logic styles50            | 0 |

| Figure 4.4: Partial product addition matrix                                         | 1 |

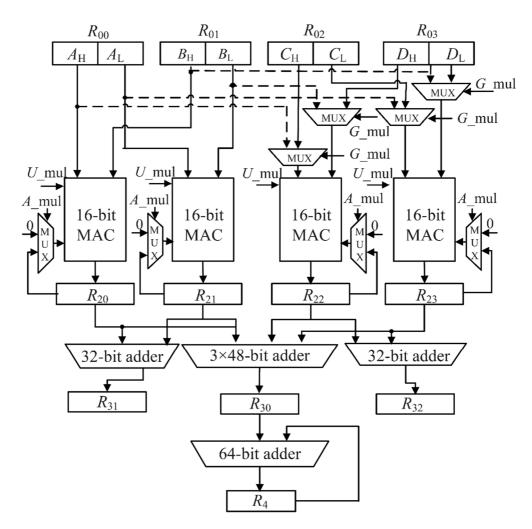

| Figure 4.5: 32-bit MAC architecture and its ASIC implementation                     | 1 |

| Figure 4.6: 32-bit MAC architecture                                                 | 2 |

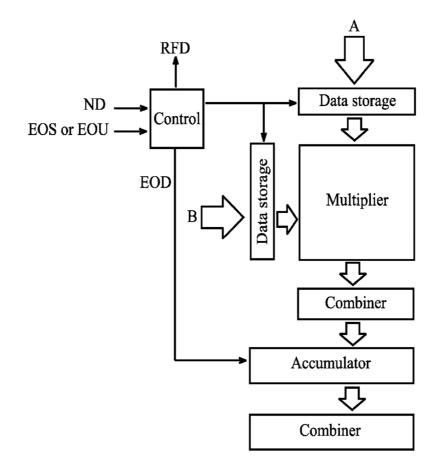

| Figure 4.7: Pipelined MAC architecture                                              | 3 |

| Figure 4.8: The RSFQ DS processor architecture                                      | 4 |

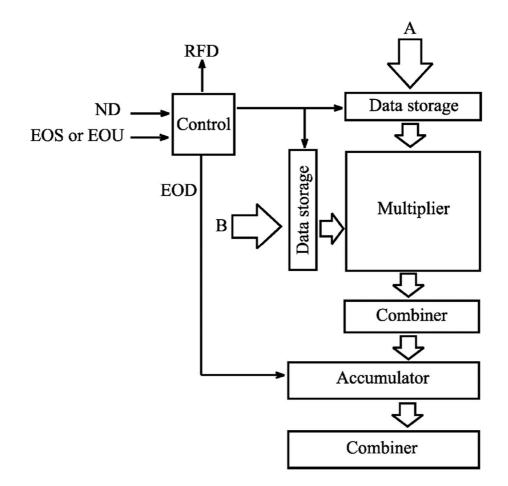

| Figure 4.9: Fixed-point vector MAC architecture                                     | 5 |

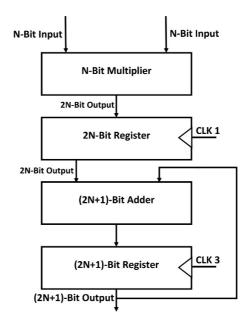

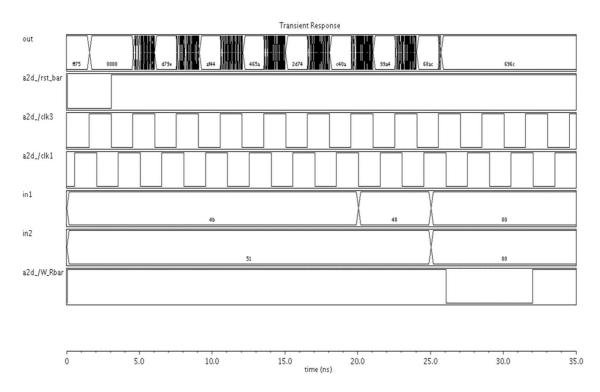

| Figure 4.10: Proposed architecture of UMAC57                                        | 7 |

| Figure 4.11: Output waveform of the proposed UMAC architecture                      | 7 |

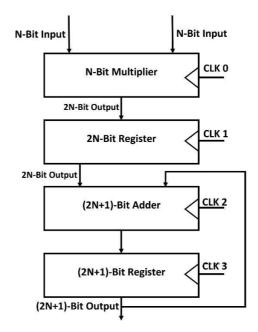

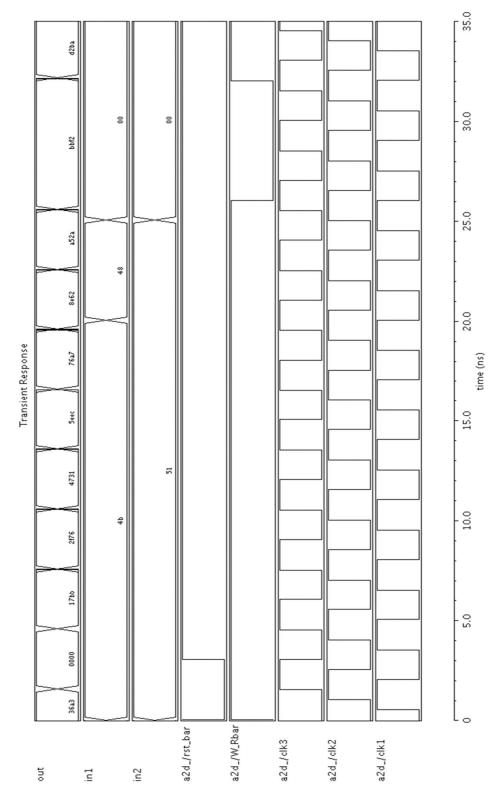

| Figure 4.12: Block diagram of USMAC architecture                                    | 8 |

| Figure 4.13: Output waveform of the USMAC architecture                              | 9 |

| Figure 4.14: Block diagram of SMAC architecture                                     | 0 |

| Figure 4.15: Output waveform of the SMAC architecture                               | 1 |

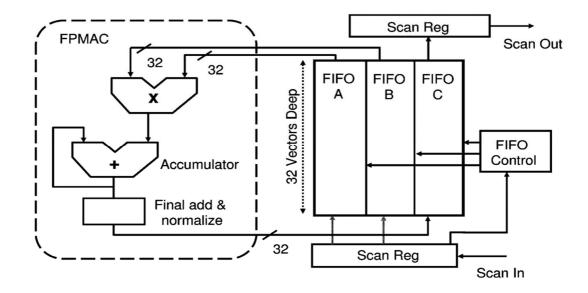

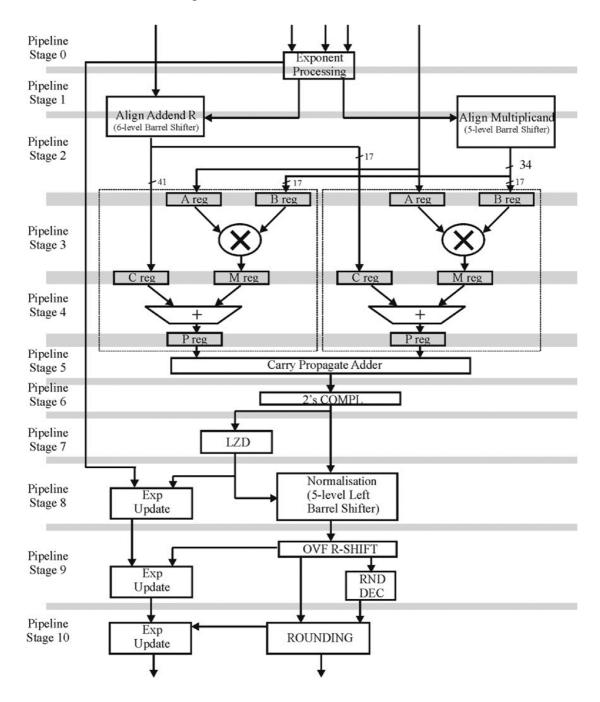

| Figure 5.1: Pipelined single-precision FPMAC                                        | 3 |

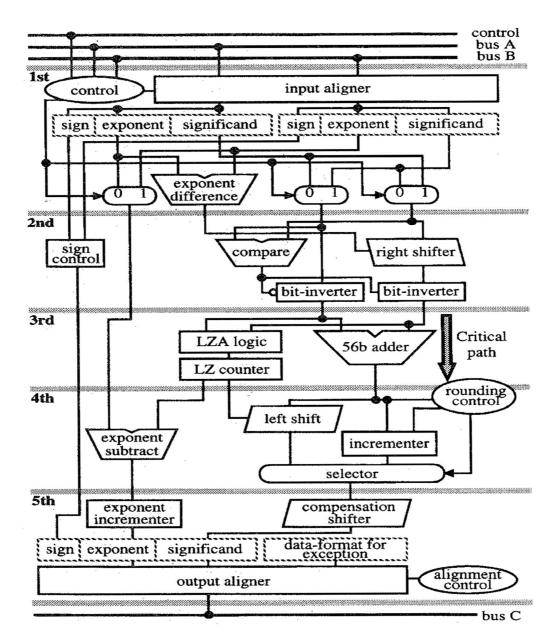

| Figure 5.2: An LZA logic for floating-point addition operation                      | 4 |

| Figure 5.3: Floating point multiply-add units for IEEE 16-bit or IEEE 32-bit65                    |

|---------------------------------------------------------------------------------------------------|

| Figure 5.4: RSFQ DS Processor                                                                     |

| Figure 5.5: Input format representation of SFMAC67                                                |

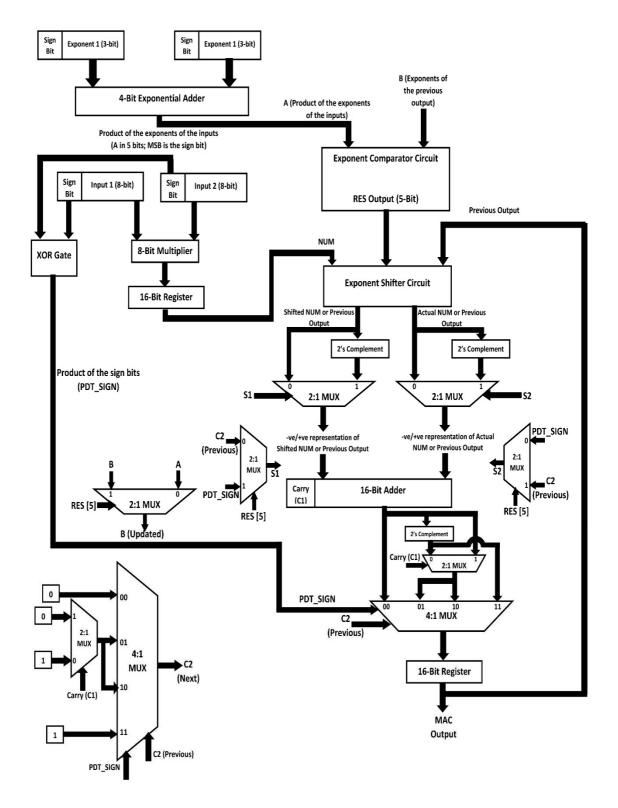

| Figure 5.6: The novel SFMAC architecture                                                          |

| Figure 5.7: Exponential Adder (EA) architecture70                                                 |

| Figure 5.8: The ECC architecture                                                                  |

| Figure 5.9: The ECC with same sign bit73                                                          |

| Figure 5.10: The ESC architecture74                                                               |

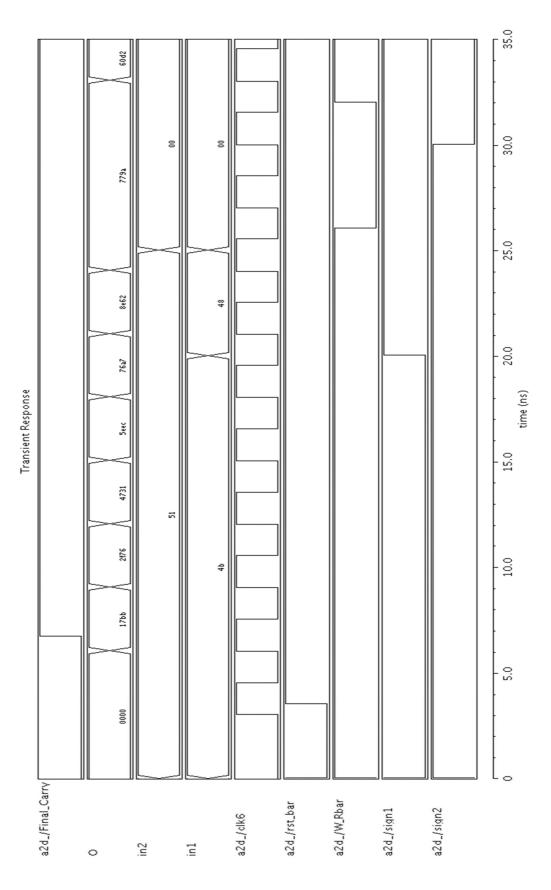

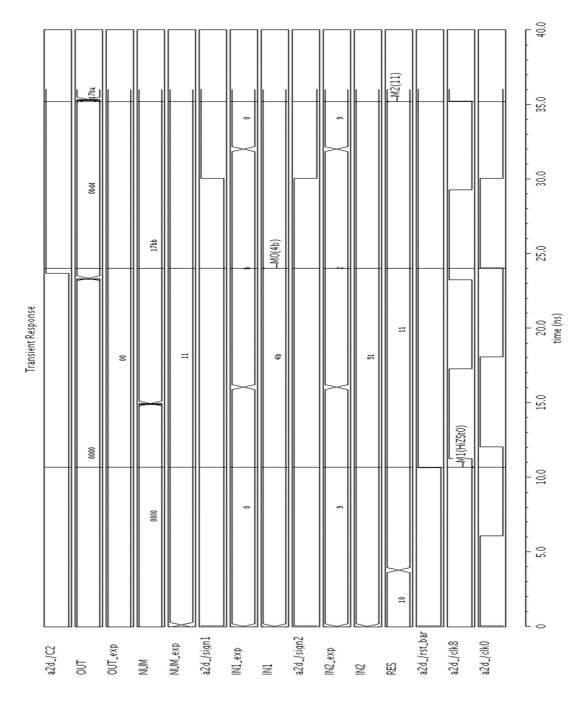

| Figure 5.11: The simulation waveform of the SFMAC architecture77                                  |

| Figure 6.1: UCM and Wallace tree for $5 \times 5$ -bit operations at voltages below $1V$ 83       |

| Figure 6.2: UCM and Wallace tree for $9 \times 9$ -bit operation at voltages below $1V$ 84        |

| Figure 6.3: FPGA realization of the $9 \times 9$ UCM                                              |

| Figure 6.4: PVT comparison of delay of UCM and Wallace tree for $5\times 5\text{-bit}$ operations |

| at 0.6V and 0.9V in different corners                                                             |

| Figure 6.5: PVT comparison of delay of UCM and Wallace tree for $9 \times 9$ -bit operations      |

| at 0.6V and 0.9V in different corners                                                             |

| Figure 6.6: Graphical comparison of UMAC, USMAC, SMAC and SFMAC                                   |

| architectures with 2V supply voltage and 20 ns simulation period                                  |

| Figure 6.7: Graphical analysis of the static power, average power and area of SFMAC               |

| in CMOS GPDK 90 nm and TSMC 130 nm technology90                                                   |

# LIST OF TABLES

| Table 1.1: Comparisons of performance parameters for different logic styles11              |

|--------------------------------------------------------------------------------------------|

| Table 5.1: Propagation delay of the internal blocks of SFMAC architecture78                |

| Table 5.2: The operation of the 16-bit 4:1 MUX based on the two select lines79             |

| Table 6.1: Delay comparison of UCM versus Wallace tree for $5 \times 5$ -bit operation82   |

| Table 6.2: Delay comparison of UCM versus Wallace tree for $9 \times 9$ -bit operation82   |

| Table 6.3: Delay comparison of UCM versus Wallace tree for $5 \times 5$ -bit operations in |

| different corners                                                                          |

| Table 6.4: Delay comparison of UCM versus Wallace tree for $9 \times 9$ -bit operations in |

| different corners                                                                          |

| Table 6.5: Comparison of UMAC, USMAC, SMAC and SFMAC architectures with 2V                 |

| supply voltage and 20 ns simulation period                                                 |

| Table 6.6: Comparison of SFMAC at supply voltage 2V and simulation period 40 ns in         |

| CMOS GPDK 90 nm and TSMC 130 nm technology90                                               |

| Table 6.7: Performance comparison of Proposed MAC architecture with existing               |

| architectures                                                                              |

# LIST OF ABBREVIATIONS

| MAC   | Multiply and Accumulate                             |  |  |  |  |

|-------|-----------------------------------------------------|--|--|--|--|

| FFT   | Fast Fourier Transform                              |  |  |  |  |

| UCM   | Universal Compressor-based Multiplier               |  |  |  |  |

| FPGA  | Field Programmable Gate Array                       |  |  |  |  |

| PVT   | Process, Voltage and Temperature                    |  |  |  |  |

| ADE   | Analog Design Environment                           |  |  |  |  |

| V     | Voltage                                             |  |  |  |  |

| UMAC  | Unsigned Multiply and Accumulate                    |  |  |  |  |

| USMAC | Unsigned Synchronous Multiply and Accumulate        |  |  |  |  |

| SMAC  | Signed Multiply and Accumulate                      |  |  |  |  |

| SFMAC | Signed Floating-point Multiply and Accumulate       |  |  |  |  |

| CMOS  | Complementary Metal Oxide Semiconductor             |  |  |  |  |

| MHz   | Mega Hertz                                          |  |  |  |  |

| GPDK  | Generic Process Design Kit                          |  |  |  |  |

| DSP   | Digital Signal Processing/Digital Signal Processor  |  |  |  |  |

| PDA   | Personal Digital Assistant                          |  |  |  |  |

| VLSI  | Very Large-Scale Integration                        |  |  |  |  |

| NCSim | Incisive Enterprise Simulator                       |  |  |  |  |

| RTL   | Register-Transfer Level                             |  |  |  |  |

| PPRT  | Partial Product Reduction Tree                      |  |  |  |  |

| VHDL  | VHSIC (Very High-Speed Integrated Circuit) Hardware |  |  |  |  |

|       | Description Language                                |  |  |  |  |

| HDL   | Hardware Description Language                       |  |  |  |  |

| PMOS  | P-channel Metal Oxide Semiconductor                 |  |  |  |  |

| NMOS  | N-channel Metal Oxide Semiconductor                 |  |  |  |  |

| IC    | Integrated Circuits                                 |  |  |  |  |

| μs    | Micro Seconds                                       |  |  |  |  |

| НА    | Half Adder                                          |  |  |  |  |

| FA                 | Full Adder                                                  |  |  |  |  |

|--------------------|-------------------------------------------------------------|--|--|--|--|

| CPL                | Complementary Pass Transistor Logic                         |  |  |  |  |

| DPL                | Double Pass Transistor Logic                                |  |  |  |  |

| BCD                | Binary Coded Decimal                                        |  |  |  |  |

| V <sub>DD</sub>    | Supply Voltage                                              |  |  |  |  |

| $\mathbf{f}_{clk}$ | Clock Frequency                                             |  |  |  |  |

| α                  | Switching Activities                                        |  |  |  |  |

| CL                 | Load Capacitance                                            |  |  |  |  |

| I/O                | Input-Output                                                |  |  |  |  |

| ULSI               | Ultra-Large-Scale Integration                               |  |  |  |  |

| PC                 | Personal Computer                                           |  |  |  |  |

| NiMH               | Nickel-Metal Hydride                                        |  |  |  |  |

| NiCd               | Nickel-Cadmium                                              |  |  |  |  |

| DEC                | Digital Equipment Corporation                               |  |  |  |  |

| W                  | Watt                                                        |  |  |  |  |

| V <sub>SS</sub>    | Source Supply or Ground                                     |  |  |  |  |

| MOSFET             | Metal Oxide Semiconductor Field Effect Transistor           |  |  |  |  |

| $	au_{ m P}$       | Propagation Delay                                           |  |  |  |  |

| $	au_{ m PLH}$     | Signal Switching from Logic Low to High                     |  |  |  |  |

| $	au_{ m PHL}$     | Signal Switching from Logic High to Low                     |  |  |  |  |

| ECL                | Emitter-Coupled Logic                                       |  |  |  |  |

| TTL                | Transistor-Transistor Logic                                 |  |  |  |  |

| PDP                | Power-Delay Product                                         |  |  |  |  |

| BiCMOS             | Bipolar Complementary Metal Oxide Semiconductor             |  |  |  |  |

| CSA                | Carry Select Adder                                          |  |  |  |  |

| MAVIP              | Multifunctional Architecture for Video and Image Processing |  |  |  |  |

| MIN                | Minimum                                                     |  |  |  |  |

| MAX                | Maximum                                                     |  |  |  |  |

| ASIC               | Application Specific Integrated Circuits                    |  |  |  |  |

| SAD                | Sum of Absolute Difference                                  |  |  |  |  |

| CSD                | Canonical Signed Digit                                      |  |  |  |  |

| TSMC     | Taiwan Semiconductor Manufacturing Company             |  |  |  |

|----------|--------------------------------------------------------|--|--|--|

| MOSIS    | Metal Oxide Semiconductor Implementation Service       |  |  |  |

| CSLA     | Carry Select Adder                                     |  |  |  |

| FAM      | Fused Add-Multiply                                     |  |  |  |

| BEC      | Binary to Excess 1 Converter                           |  |  |  |

| GDI      | Gate Diffusion Input                                   |  |  |  |

| DML      | Dual Mode Logic                                        |  |  |  |

| FADD     | Floating-point Addition                                |  |  |  |

| LZA      | Leading Zero Anticipatory                              |  |  |  |

| OBDD     | Ordered Binary Decision Diagrams                       |  |  |  |

| DMT      | Discrete Multitone                                     |  |  |  |

| SCM      | Single Carrier Modulation                              |  |  |  |

| VDSL     | Very high-speed Digital Subscriber Line                |  |  |  |

| RSFQ DS  | Rapid Single Flux Quantum Digital Signal               |  |  |  |

| GHz      | Giga Hertz                                             |  |  |  |

| FPMAC    | Floating-Point Multiply and Accumulate                 |  |  |  |

| FMA      | Fused Multiply-Accumulate                              |  |  |  |

| ISE      | Integrated Synthesis Environment                       |  |  |  |

| PMADD    | Parallel Multiply Add                                  |  |  |  |

| nm       | Nano Meter                                             |  |  |  |

| APC      | Adaptive Power Control                                 |  |  |  |

| UMC      | United Microelectronics Corporation                    |  |  |  |

| LNS      | Logarithmic Number System                              |  |  |  |

| LS-DCCFF | Low-Swing Differential Conditional Capturing Flip-Flop |  |  |  |

| ASIP     | Application-Specific Instruction-set Processor         |  |  |  |

| mW       | Milli Watt                                             |  |  |  |

| TG       | Transmission Gate                                      |  |  |  |

| IEEE     | Institute of Electrical and Electronics Engineers      |  |  |  |

| PWM      | Pulse Width Modulation                                 |  |  |  |

| 2D MAC   | Two Dimensional Multiply-Accumulate                    |  |  |  |

| IP       | Intellectual Property                                  |  |  |  |

| LUT                 | Look-Up Table                                              |  |  |

|---------------------|------------------------------------------------------------|--|--|

| SIMD                | Single Instruction Multiple Data                           |  |  |

| PID                 | Proportional Integral Derivative                           |  |  |

| SIM                 | Simulator                                                  |  |  |

| FIR                 | Finite Impulse Response                                    |  |  |

| IIR                 | Infinite Impulse Response                                  |  |  |

| DA                  | Distributed Arithmetic                                     |  |  |

| CNTFET              | Carbon Nanotube Field-Effect Transistor                    |  |  |

| HSPICE              | Hailey Simulation Program with Integrated Circuit Emphasis |  |  |

| HMC-MAC             | Hybrid Memory Cube Multiply-Accumulate                     |  |  |

| CMAC                | Complex Multiply Accumulate Cell                           |  |  |

| RPR-MAC             | Reduced Precision Redundancy Multiply And Accumulate       |  |  |

| FINFET              | Fin Shaped Field Effect Transistor                         |  |  |

| DWT                 | Discrete Wavelet Transform                                 |  |  |

| RAM                 | Random Access Memory                                       |  |  |

| ROM                 | Read Only Memory                                           |  |  |

| SOC                 | System on Chip                                             |  |  |

| RCA                 | Ripple Carry Adder                                         |  |  |

| М                   | Mantissa                                                   |  |  |

| В                   | Base                                                       |  |  |

| Е                   | Exponent                                                   |  |  |

| <b>PP-GENERATOR</b> | Partial Product Generator                                  |  |  |

| ND                  | New Data                                                   |  |  |

| EOS                 | End-Of-Symbol                                              |  |  |

| EOU                 | End-Of-User                                                |  |  |

| EOD                 | End-Of-Data                                                |  |  |

| RFD                 | Ready-For-Data                                             |  |  |

| CLK                 | Clock                                                      |  |  |

| PED                 | Pulse Edge Detector                                        |  |  |

| ps                  | Pico Seconds                                               |  |  |

| MUX                 | Multiplexer                                                |  |  |

|                     |                                                            |  |  |

| FIFO      | First in First out                                         |  |  |  |

|-----------|------------------------------------------------------------|--|--|--|

| ALU       | Arithmetic and Logic Unit                                  |  |  |  |

| MSB       | Most Significant Bit                                       |  |  |  |

| S BIT     | Sign Bit                                                   |  |  |  |

| Exp S BIT | Exponents' Sign Bit                                        |  |  |  |

| EA        | Exponential Adder                                          |  |  |  |

| ECC       | Exponent Comparator Circuit                                |  |  |  |

| ESC       | Exponent Shifter Circuit                                   |  |  |  |

| EXP       | Exponent                                                   |  |  |  |

| LSB       | Least Significant Bit                                      |  |  |  |

| NUM       | Number (Output)                                            |  |  |  |

| GDS-II    | Geometrical Data Base Standard for Information Interchange |  |  |  |

| FF        | Fast-Fast                                                  |  |  |  |

| FS        | Fast-Slow                                                  |  |  |  |

| NN        | Normal-Normal                                              |  |  |  |

| SF        | Slow-Fast                                                  |  |  |  |

| SS        | Slow-Slow                                                  |  |  |  |

| LED       | Light Emitting Diode                                       |  |  |  |

| IOB       | Input Output Buffer                                        |  |  |  |

### **CHAPTER 1: INTRODUCTION**

The invention of the TRANfer-reSISTOR (transistor) by William B. Shockley, Walter H. Brattain, and John Bardeen at AT & T Bell laboratories had changed the electronics industry dramatically and opened the way for the advancement of the Integrated Circuit technology. Jack Kilby designed the first IC at Texas Instruments in early 1960, and since then, there is an evolution of different generations of IC technology. The types of generation are based on the transistor count, such as SSI consisting of 10 to 1000 transistors, MSI consisting of 100 to 1000 transistors, LSI consisting of 1000 to 10000 transistors, and VLSI consisting of more than 10000 transistors. The fifth-generation, which has emerged recently as ULSI for which the range of transistor count on a single IC chip is not defined yet. Further miniaturization is yet to come, and there must inevitably be more revolutionary progress in applying the ULSI technology.

Silicon CMOS technology has become the dominant manufacturing process for relatively high performance and cost-effective VLSI/ULSI circuits over the past several years. This development's ground-breaking essence is demonstrated by the rapid growth in which the number of transistors on a single chip integrated into circuits. Though transistor count (i.e. the area) is the primary reason for such development, energy efficiency and high-speed designs are also the primary concerns for the designers. Therefore, the typical design constraints of VLSI/ULSI circuits are power, delay and area. Any digital system's performance is measured concerning the power, delay and area. Design constraints can be explained as follows:

- *Timing*: Any circuit has specific timing requirements. A circuit with optimized delay is the prime concern for VLSI designers.

- *Area*: A circuit's size can't exceed the threshold limit. Here, circuit size refers to the backend design or final layout.

• *Power*: A circuit must have the capability to save as much as the power it can. But the VLSI designers must be careful while minimizing the power of digital circuits because a decrease in power consumption can make the circuit slower.

There is an inverse relationship between the area and time constraints. The design has to be parallelized (which usually means that larger circuits have to be designed) to optimize timing (faster circuits) constraint for a specific technology. Designers typically have to compromise on circuit speed to create smaller circuits. Figure 1.1 shows the inverse relationship.

Figure 1.1: Area versus Timing trade-off

In addition to design constraints, the optimization of target technology is influenced by operating environment variables such as I/O delays, drive strengths and output loads. To ensure that the circuits are configured for the appropriate operating environment, operating environment factors must be input into the logic synthesis tool.

#### **1.1 NEED FOR LOW-POWER DESIGN**

The popularity of portable devices and the requirement to limit the power consumption (and therefore heat dissipation) in heavily-dense VLSI/ULSI chips have resulted in quick and revolutionary advances in low-power design over the past few years. Mobile applications necessitating low-power dissipation and high throughput, let's say notebook PCs, mobile communication devices, and PDAs, are the driving forces behind

these innovations. In most of these cases, low power consumption requirements need to be met along with equally challenging targets of high chip density and high speed. Therefore, the low-power IC design surfaced as a beneficial and fast-developing area of CMOS circuit design. Usually, the restricted battery life places very stringent demands on the portable system's overall power requirements. New types of rechargeable batteries say "Nickel-Metal Hydride (NiMH)" are being produced with better energy storage capacity than the traditional "Nickel-Cadmium (NiCd)" batteries. Still, there is no prospect of a significant increase in energy capacity in the foreseeable future. The energy density (which is the energy stored/unit weight) provided by new advancement in technologies (such as NiMH) is approximately 30 Watt-hour/pound, which is quite lesser considering the growing applications of portable systems. Scaling down the energy dissipation of ICs by improving functionality is, therefore, a significant task in the development of portable devices.

In high-performance digital systems, such as microprocessors-microcontrollers, DSPs, etcetera, the need for low-power circuit development is also becoming a significant concern. Targeting higher chip density and higher processing speed contributes to the development of high-clock rate in very complex circuits. If the chip's clock speed rises then the chip's energy dissipation, thereby increasing the temperature linearly. As the dissipated heat has to be efficiently removed to maintain the temperature of the chip at an optimum level, the packaging cost, cooling and heat extraction becomes an important aspect. A few elite microchips structured in the mid-1990s (such as, Intel Pentium, DEC Alpha, PowerPC) which operates in a frequency ranging from 100-300 MHz, and the total average power is ranging from 20-50 W. ULSI's reliability is one more critical factor to look after for the design engineers, as it emphases to the demand for energy-efficient design. There is a near connection between electronic circuit maximum power-dissipation and reliability concerns like electro-migration and system degradation caused by the carriers. Additionally, the thermal stress caused by chip heat dissipation is also a significant issue to look after in terms of reliability. As a consequence, increasing power-consumption is also critical for improving performance.

The procedures used in digital systems to achieve low-power consumption vary from device to device, technology to technology or algorithm to algorithm level. The standard system features (say threshold voltage), device dimension and interconnection properties are essential factors in reducing power consumption. Circuit level approaches such as a careful selection of circuit design logic family, decrement in the total number of voltage transitions and clocking approaches can be used to minimize transistor-level energy dissipation. Measures at the architecture level include intelligent power management of different system components, pipeline and concurrent usage, and bus layout design.

Lastly, a good set of data processing algorithms also reduces the power consumed by the device as it reduces the number of switching activity for a particular task.

#### **1.1.1 Causes for power dissipation**

The energy or power dissipation in CMOS based circuits is categorized into three main categories, namely,

- 1. Switching or Dynamic power consumption

- 2. Short circuit power consumption

- 3. Leakage power consumption

A fourth power element, namely static power, would also be considered if the device or chip contains circuits other than standard CMOS gates that have direct current paths between  $V_{DD}$  and  $V_{SS}$ .

#### Switching or Dynamic power consumption:

Dynamic power is the dissipation of energy during a switching activity which means that a CMOS logic gate's output node voltage makes a switch that consumes electricity. For digital CMOS circuits, as energy is collected from the  $V_{DD}$  to charge the capacitance at the output node, dynamic power is dissipated. The output node voltage usually transitions from 0 to  $V_{DD}$  during the charging cycle, and the power used for the conversion is relatively independent of the circuit's functionalities.

#### Short-Circuit Power Consumption:

The dissipation of the dynamic power described in the last sub-section is simply due to the power needed to charge the parasitic capacitance in the circuit, and the dynamic power is non-dependent on the input signal's rise/fall times. Now, in a situation where a CMOS logic gate is controlled with finite rise/fall time on the input waveforms, both the N-Channel MOSFETs and the P-Channel MOSFETs in the design may conduct momentarily and concurrently for a small duration of time during the transitions. This eventually forms a direct current path between the  $V_{DD}$  and the  $V_{SS}$ .

#### Leakage Power Consumption:

The N-Channel MOSFETs and the P-Channel MOSFETs used in digital designs using CMOS circuits usually have reverse leakage currents as well as sub-threshold currents with non-zero values practically. In a chip containing an enormous number of transistors, these flows of current can add to the total energy or power dissipation even when the transistors are not performing any transient activity. Primarily the processing parameters determine the scale of the leakage currents. The leakage current components found in N-Channel MOSFETs and P-Channel MOSFETs are:

- A. Reverse-diode leakage current

- B. Sub-threshold leakage current

#### **1.2 FACTORS AFFECTING HIGH-SPEED DESIGN**

The delay for a CMOS based circuit relies on the charge-discharge rate at the output of all capacitors. The capacitance of all capacitors connected to the circuit is due to two elements called the parasitic capacitance and the load capacitance. The propagation delay ( $\tau_p$ ) of a CMOS inverter is given by equation 1.1.

$$\tau_p = 2C_L / K V_{dd} \tag{1.1}$$

The delay in propagation (in general "propagation delay") is the time taken to transfer a signal to the output from the input. Typically, it is defined between the 50% points, as shown in figure 1.2. The propagation delay of the logic gate is the mean of the output signal switching from logic low to high ( $\tau_{PLH}$ ) and high to low ( $\tau_{PHL}$ ). As shown in figure 1.2, the dotted lines, i.e. the ideal input or output which has immediately changed from low to high and high to low. But practically, any system can't change abruptly from logic high to low or vice versa. Therefore, there is a requirement for rise and fall time. Rise time is the time taken by a signal to change from 10% to 90% of the final value; whereas the fall time is the time taken by a signal to change from 90% to 10% of the final value.

Figure 1.2: Rise-fall time during input output transitions

For CMOS inverter, as shown in equation 1.1, the propagation delay varies directly with the changes of load capacitance and varies inversely with the value of 'K'. The same relation can be obtained for the output transistor in bipolar technology. The relationship of propagation delay and load capacitance is shown in figure 1.3 in graphical representation for three logic families, i.e. ECL, CMOS and TTL. As the graph depicts, the delay is low at low capacitances in the CMOS logic family in comparison to TTL logic. The main reason for the same is the load capacitance is an external capacitance, and it doesn't include the internal capacitance of the logic gate. The internal capacitance for CMOS devices is smaller than bipolar devices because a CMOS device takes considerably smaller space in the layout than the bipolar device.

Hence the larger size of the device offers higher input capacitance. However, as the load capacitance is much bigger than internal load capacitance, its influence is not visible in the propagation delay.

Figure 1.3: Propagation delay versus load capacitance for different logic families

On the other hand, the practical value of K is more significant for bipolar devices than CMOS devices. Therefore, with larger load capacitance the propagation delay for CMOS devices are more than that of TTL devices. Thus, if a large capacitance to be driven, i.e. the system has large fan-in, then bipolar devices are preferred. On the other way around, if the system has low output capacitance to drive, (i.e. < 30 pF), then CMOS can be preferred. For ECL logic family, the delay versus capacitance shows that these devices are fastest among all three since ECL logic systems don't enter saturation. Therefore, a circuit with higher speed and lower power consumption is always desired. Moreover, as there is a trade-off between the power consumption and delay, the performance of a circuit is mostly evaluated in terms of Power-Delay Product (PDP).

### **1.3 INTRODUCTION TO MULTIPLY & ACCUMULATE (MAC) ARCHITECTURE**

Today's portable devices are capable of doing image filtering to face recognition, an audio signal enhancement to voice recognition and gesture-based control to biometric authentication. All those functionalities are the applications of Digital Signal Processing (DSP). A large number of mathematical operations are performed repeatedly and quickly on a series of data samples by DSP algorithms. Most operating systems and general-purpose microprocessors can successfully execute DSP algorithms. Still, because of power efficiency constraints, they are not suitable for use in portable devices such as PDAs and mobile phones. However, the rapid growth of portable electronics has introduced the significant challenges of low power and high throughput for VLSI/ULSI design engineers.

Among the other digital blocks, Multiply and Accumulate (MAC) unit plays a vital role while evaluating the performance of a DSP block. While performing convolution, filtering or any other DSP operations, it is always desired to use an efficient MAC unit. The efficiency of a MAC unit is measured in terms of two factors:

- 1) Speed of operation

- 2) Overall power consumption [1, 2]

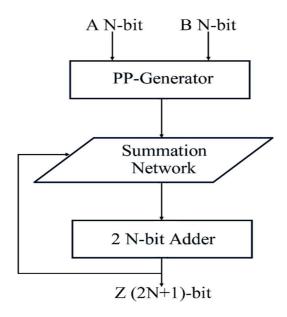

The essential operation of the MAC is to fetch the inputs from the input devices or memory and process it through the multiplier block and provide the result to an adder which sum-up the current multiplier output with the previously accumulated result and then again accumulate the result in an accumulator register. Generalized block diagram of  $8 \times 8$ -bit MAC is shown in figure 1.4. The MAC architecture contains the main functional blocks as multiplier, adder and register/accumulator. The multiplier performs the multiplication operation over the two input operands; the adder performs the addition of the result of the multiplier with the result of the previous cycle and the register or accumulator stores the sum for next cycle addition. Different approaches for multiplication as well as the addition for MAC operation is described in detail in the literature by [3, 4] etcetera. Mathematically, the operation of the MAC is to generate

the product of two operands X<sub>i</sub> and Y<sub>i</sub> and add the result with the previously stored result from the last multiplication in a single clock period [5]. The operation of MAC can be expressed, as mentioned in equation 1.2.

$$F = \sum_{i=0}^{n-1} X_i Y_i \tag{1.2}$$

Where 'i' denote the range of the values.

Figure 1.4: Generalized block diagram of  $8 \times 8$  bit MAC

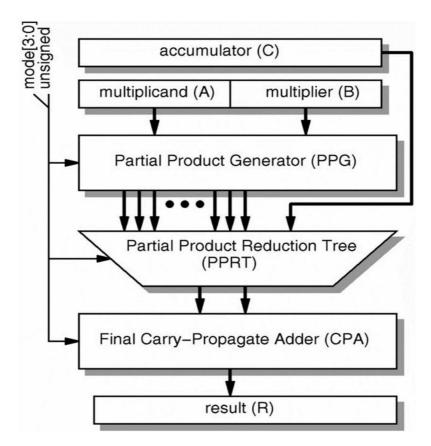

A high-speed MAC architecture which promises with an optimized area is proposed in [1]. It uses 4:2 compressor circuits to improve speed. In 2012, a novel architecture for the multiplier is proposed by [6]. In 2013, a novel architecture using modified Wallace tree multiplier is proposed by [7]. The implementation is done for 64 bits. Modified Braun multiplier is used to implement a basic MAC unit in [8]. The implementation is done on NCSim and RTL Compiler. A low power Baugh Wooley multiplier-based unit is proposed in the year 2014 by [9]. A pipelined based architecture has been proposed in this work. Split MAC architecture is explained by [10]. A technique to compress the partial product using "interleaved adders" and a "modified hybrid Partial-Product-Reduction-Tree (PPRT)" schemes are proposed in this work to enhance the speed of operation further. There are several architectures explained in the past by various designers. However, all these different architectures (90% of them in the literature) are designed with the help of Hardware Descriptive Languages (HDL) such as Verilog or VHDL. The main disadvantage of using HDL is that the basic blocks, those are to be used while designing any architecture, use the predefined system defined primitives (standard PMOS-NMOS implementation). Because of which, even after using smart and efficient structural designs, the architecture lags in certain aspects. The main reason for such a shortcoming is the non-optimization of basic building blocks viz. multiplier, accumulator and adder.

#### 1.3.1 Multiplier

In DSP architectures, multiplication is the fundamental operation. Multipliers require large area (because of partial product generation), long latency and consume relatively higher power than adder/subtractor circuits. Any multiplier-based system's performance is evaluated based on the optimization of the primary design constraints (explain later in this chapter). The reason for the same is that the multiplier is the slowest unit in the arithmetic system. Hence, maximizing the speed of operation of the multiplier along with optimization of power and area is the primary concern for any system design. However, the trade-off between area and speed & power and speed are unavoidable. Therefore, minimizing one of design constraint (power, delay or speed) may have the possibility to increase the other one. Moreover, as mentioned above, the hardware requirement in multiplier circuit is enormous. Hence, low power design is a challenge as it has become the authoritative measures for designing the power-efficient multiplier designs for high speed and compact devices. As mentioned earlier, the multiplier is one of the central units for designing a power-efficient circuit, where the multiplier block decides the efficiency of the DSP. Therefore, extensive research work has been performed on low power multiplier designs with different area-speed constraints.

Figure 1.5: 4-bit Wallace tree multiplier

| Multiplier | Logic | Delay | Power         | PDP           | No. of     |

|------------|-------|-------|---------------|---------------|------------|

| Туре       | Style | (ns)  | ( <b>µW</b> ) | ( <b>fJ</b> ) | Transistor |

|            | CMOS  | 8.300 | 10.73         | 89.06         | 384        |

| Array      | CPL   | 4.337 | 24.70         | 131.82        | 368        |

|            | DPL   | 4.667 | 19.72         | 92.03         | 448        |

|            | CMOS  | 4.247 | 10.68         | 45.35         | 384        |

| Tree       | CPL   | 4.105 | 23.61         | 125.25        | 368        |

|            | DPL   | 4.526 | 19.87         | 89.93         | 448        |

Table 1.1: Comparisons of performance parameters for different logic styles

Australian computer scientist Chris Wallace proposed a fast multiplication technique in the year 1964 [11]. The hardware requirement in this architecture is very high, but it reduces the delay substantially. The architecture promises to get the products and quotients within a time of 1  $\mu$ s and 3  $\mu$ s respectively if it is used in diode-transistor logic. The architecture proposed in [11] can be used where a high-speed design is a primary concern, not the regularity of the structure. Figure 1.5 shows the conventional Wallace tree architecture. As mentioned by [12] in 2012, "The Wallace tree multiplier is faster than an array multiplier because its height is logarithmic in word size, not linear". The only disadvantage of Wallace tree multiplier is that its irregular structure. In the recent past, many attempts are made to modify the Wallace tree structure, but a hand full of attempts are made to make the design regular. The performance comparison of array multiplier and Wallace tree in different logic style is given in table 1.1 [13].

#### **1.3.2 Accumulator**

An accumulator or register is a temporary storage where the internal as well as final arithmetical and/or logical results are stored. Without an accumulator or register it becomes very crucial to store the outcome of each and every operation (summation, multiplication, shift, etcetera) to the main memory. The main reason to use the accumulator or register is to read the stored data in the immediate previous cycle and to use it in the next operation because mathematical operations often take place in a stepwise manner, using the results from one operation as the input to the next. Moreover, the main memory access is slower than accessing an accumulator or register repetitively; which eventually decreases the speed of operation of the circuit. But it is to be noted that, though the technology used for accessing large main memory is slower but its design cost is cheaper than that of an accumulator or register as the memory.

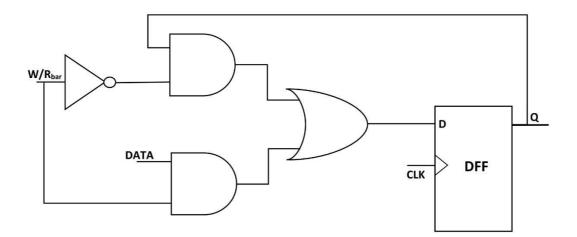

Figure 1.6: Basic accumulator or register circuit

The fundamental element constituting an accumulator or a register is a D-flip-flop which can store a 1-bit of data. Two AND gates with clock input are also used. Hence, the register cell has three inputs, namely "write or negation of read", "clock" and "D". The output of the block is Q. Figure 1.6 shows the single-bit register [5].

#### 1.3.3 Adder

An adder is also known as summer is a logic circuit which adds two numbers. Adders or summer circuit is used not only for addition but also for multiplication, updating the addresses, increment/decrement operations, table indices etcetera. The adder operation is performed in binary number systems, but the adder can also be applied on BCD, excess -3 etcetera. Adders are of two types:

- Half Adder: It adds two 1-bit binary numbers and the outputs are 'sum' and 'carry' values. For 'sum' output is the XOR of the two inputs whereas, the 'carry' output is the AND of the two inputs. Half adder is used rigorously in full adder circuit, multi-bit adder circuit, multiplier circuit etcetera.

- Full Adder: It performs addition operation on three 1-bit variables and produces the 'sum' and 'carry' outputs. It takes into account the carry input also. Most of the n-bit adder architectures utilize full adders. The multiplier, adder-cum-subtractor circuit etcetera use the full adder circuit rigorously.

#### 1.3.4 Block enabled technique & pipelined architecture

As the feature size is scaled down, low power is the most critical issue in today's VLSI design. Block Enabling is one of the most elegant and classic technique for reduction of dynamic power, a significant contributor in total power consumption of any VLSI circuit [13].

$$P_{dynamic} = P_{int \, ernal} + V_{DD}^2 f_{clk} \, \alpha . \, C_L \tag{1.3}$$

The mathematical expression for dynamic power is shown in equation 1.3, where ' $V_{DD}$ ' is the supply voltage, ' $f_{clk}$ ' is the clock frequency, ' $\alpha$ ' represents the switching activities at nodes and ' $C_L$ ' represents load capacitances. Block enabling technique facilitates saving of electrical power used by digital signal processors by reducing the switching activity ' $\alpha$ '. The power-saving is ensured in this technique by activating the design block as and when required. For this, initially, the delay for each building block of the architecture needs to be calculated. Every building block of the architecture gets enabled only after the desired delay required by that block to produce the output

correctly. The successive blocks are disabled until the inputs are available to the respective block and thus saving power [14].

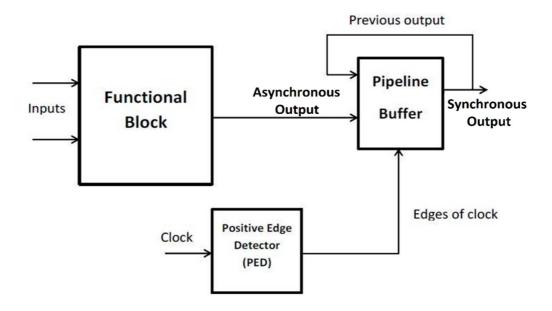

The basic idea of pipelining comes from everyday life. For example, water pipe continuously sends water without waiting for the water previously sent to be out, which leads to a reduction in critical paths. In DSP, pipelining either reduces the power consumption at the same speed or increases the clock speed. In the buffered and synchronous pipelined architectures, "pipeline registers" are introduced between the functional blocks, and are synchronized (using a clock pulse). The delay between each clock signal is set in such a way that when the registers are clocked, the data stored in it is passed to the next stage. The representation of pipelined architecture with block enabling technique is shown in figure 1.7.

Figure 1.7: Pipelined and Block enabled Architecture

The main objective of the research work is to investigate various pipelined MAC architectures which are efficient in terms of the implementation of the high-yielding signal processing architectures and also to have lesser power consumption. This is because, the power consumption, speed and high-yielding rates are always interlinked with the DSP systems. Initially, a  $1 \times 1$ -bit fixed point unsigned MAC unit is designed in full custom IC design platform (using Cadence Virtuoso) with appropriate geometries to produce optimized power, area, and delay. Similarly, using the same

concept, a  $1 \times 1$ -bit floating point signed/unsigned MAC unit is proposed and later the work is extended till  $8 \times 8$  bit fixed-point signed/unsigned number and  $8 \times 8$  bit floating-point signed/unsigned number. Full custom IC design platform is chosen for this research work to optimize the essential and fundamental building block.

#### **1.4 SIGNIFICANCE OF THIS RESEARCH**

As discussed earlier in this chapter, the multiplier and accumulator are the critical components of MAC architecture [1-9]. As the efficiency of the MAC is dependent upon the efficiency of the multiplier (mainly), an efficient multiplier (in terms of typical design constraints) design can further improvise the efficiency of a MAC unit. Moreover, the existing multipliers in the literature [11-13] are mostly based on the Wallace tree algorithm. It is claimed that the multipliers based on the Wallace tree reduce the steps involved to add the partial products. Still, it uses half adder or full adder for the addition of partial products which increases the complexity of the circuit. Further, any electronic circuit can be designed by two different approaches, namely the top-down approach and the bottom-up approach. In the top-down approach, the designs are implemented by focusing mainly on the output efficiency of the overall design. i.e. importance is given on the implementation of the process or algorithm, not on the optimization of primary cells. On the other hand, in the case of the bottom-up approach, the whole digital architecture is designed starting from its primary cell, i.e. importance is given on optimization of the primary cell as well as on the practical implementation of the algorithm. In the existing literature, full custom circuit design for the MAC unit has never been proposed [1-9]. Additionally, synchronization, clock gating techniques and pipelining can further enhance the speed of operation and minimize the power consumption.

Therefore, in this research work, a universal compressor (N:M of any size) based multiplier is proposed to use it as the core of the proposed MAC unit to improve the efficiency. Additionally, a full custom IC approach with synchronization, clock gating techniques and pipelining is adopted in the design of the proposed MAC to optimize the overall architecture which eventually provides much more efficiency in terms of power as well as delay.

#### **1.5 ROADMAP OF THE THESIS**

Chapter 2 offers a detailed review of literature based on adder, multiplier and MAC architectures. It has presented the recent developments in these areas in recent years. Based on the literature survey, the objectives of this research work are framed.

Chapter 3 shows the design and implementation of the novel UCM architecture, which promises higher speed at ultra-low supply voltages (less than 0.6V). A novel universal compressor (N:M of any size) is used for the addition of partial products while designing the multiplier. The multiplier is named as Universal Compressor-based Multiplier (UCM). The prototype of the proposed multiplier is implemented on FPGA. The UCM architecture is applied for developments of different architectures of MAC for fixed-point unsigned/signed, and floating-point unsigned/signed operations in chapter 4 and 5.

Chapter 4 discusses the UMAC, USMAC and SMAC architectures which are specialized in unsigned, synchronized-unsigned and synchronized-signed operations respectively for fixed-point inputs. The novel UCM architecture explained in chapter 3 is used for designing the MAC architectures. The graphical outputs of the UMAC, USMAC and SMAC architectures shows the accuracy of the designs and advantages of one over another.

Chapter 5 discusses the implementation of the SFMAC architecture, which is capable of performing signed/unsigned fixed-point or signed/unsigned floating-point MAC operation on given 8-bit inputs. The SFMAC architecture is the further extension of the MAC architectures proposed in chapter 4. The block enabling technique is deployed along with pipelining to optimize the power consumption of the proposed SFMAC architecture.

Chapter 6 consists of the detailed results and discussion of the proposed architectures. A comparative analysis is also shown in this chapter.

Finally, the conclusion of the thesis, its importance and its future works that can be adopted, are addressed in chapter 7.

# CHAPTER 2: REVIEW OF LITERATURE

As mentioned in the previous chapter, the essential component of a MAC unit is a multiplier; on the other hand, the integral component of a multiplier is an adder or summer. Therefore, this section is explained in two parts; namely i) Adder and Multiplier and ii) Multiply and Accumulate unit.

#### **2.1 ADDER AND MULTIPLIER**

(Wallace, 1964): A m  $\times$  n bit multiplier using combinational logic (in one gating step) is proposed. The proposed architecture promises to get the products and quotients within a time of 1  $\mu$ s and 3  $\mu$ s respectively if it is used in diode-transistor logic. Moreover, a rapid square-root process is also discussed [11].

(Itoh, et al., 2001): In this work, a rectangular styled Wallace-tree architecture is proposed. As stated, the partial products are segregated into two groups and summed up separately in top-down and bottom-up directions [15].

(**Onomi, et al., 2001**): A Wallace-tree multiplier architecture suitable for pipeline scheme is proposed in this research, where "carry-save adders are used for the addition of partial products". In this proposed work, the authors have claimed for removing the irregularity present in a conventional Wallace tree architecture [16].

(Liao, Su, et al., 2002): A CSA portioning algorithm is proposed in this paper, which is applied to the Booth-encoded Wallace-tree algorithm. As stated by the authors, "by taking into various data arrival times, a branch-and-bound algorithm is proposed and a heuristic to partition an n-bit carry-select adder into several adder blocks so that the overall delay of the design is minimized" [4].

(Guevorkian, et al., 2005): An architecture targeting mobile multimedia systems is proposed in this paper by introducing a "MAVIP", which is a "reconfigurable extension derived from a high-radix multiplier structure". A MAVIP may be configured "either to a processing unit with DSP-specific operations such as multiplication, multiply-accumulate, parallel addition, MIN/MAX, etcetera or one/another ASIC such as a matrix-vector multiplier, FIR filter or SAD accelerator" [17].

(**Kuo, et al., 2008**): Low power high-performance latch adder-based Wallace tree multiplier has been proposed. The proposed techniques-based tree multiplier provides 22.3-23.7% of lesser delay and 5.5-3.3% of lesser power consumption than the conventional traditional latch-adder technique-based tree multiplier [18].

(**Chen, et al., 2008**): Canonical Signed digit multiplier is proposed with the help of Wallace tree adder is proposed. CSD requires to the lookup table for fetching the data from memory. Hence the speed of operation has improved. Finally, the FPGA implementation is done [19].

(Yi, et al., 2009): In this research work, a modified booth algorithm is studied and proposed which yields a variable bit-length multiplier. The proposed multiplier can perform "a  $32 \times 32$ -bit or dual  $16 \times 16$ -bit or four  $8 \times 8$ -bit multiplications, which greatly enhance the parallelism of the multiplier". The overall implementation is performed in Verilog HDL [20].

(Nachtigal, et al., 2010): In this research work, reversible design of single-precision floating-point multiplier is proposed which uses a technique called "operand decomposition approach". To design a "reversible  $24 \times 24$ -bit multiplier", the operands are partitioned into three groups consisting of 8 bits each. Therefore, the " $24 \times 24$  bit reversible multiplication" is performed using nine "reversible  $8 \times 8$ -bit Wallace tree multipliers" and then the outputs are summed to get the final result [21].

(Singh, et al., 2012): Various logic style-based "1-bit full adders" and "AND2 function" are designed in this paper and used for designing  $4 \times 4$  unsigned arrays and tree multiplier. The full adders and AND2 function are designed in different logic

techniques such as CMOS logic, CPL logic and DPL logic style to improve the area, power, delay and PDP [13].

(**Rao, et al., 2012**): An improved version of tree-based Wallace tree multiplier architecture using Booth Recorder is proposed in this work. This proposed architecture reduces the latency and area of Wallace tree multiplier with the help of the Booth algorithm and compressor adders. The overall implementation is performed in Verilog HDL [12].

(Sousa, 2013): In this paper, an improved version of modulo  $(2^n + I)$  multipliers is proposed. The efficiency is achieved by "manipulating the Booth tables and by applying a simple correction term" in the existing modulo  $(2^n + I)$  multiplier algorithm. Moreover, the author states in the paper that "the proposed multiplier is almost as efficient as those for ordinary integer multiplication" [22].

(**Khan, et al., 2013**): The complexity of Wallace tree multiplier reduced in this research work without compromising with the delay. As full adder is used gregariously in Wallace tree multiplier (in partial product reduction as well as in the form of carry-propagation-adder), an "energy-efficient CMOS full adder" is used at the place of full adder standard cell to reduce power, area and delay [23].

(Kshirsagar, et al., 2013): For simultaneous arithmetic operation and therefore, to increase the speed of operations, a "four-stage pipelining at the intermediate nodes" is discussed in this proposed work. The architecture is designed in Verilog HDL and simulated using Cadence Spectre tool at TSMC 45nm technology. Cadence RTL Compiler is used for detailed analysis of the circuit [24].

(**Jayaprakash, et al., 2013**): This paper proposed a novel "low-power hybrid full adder" which consumes deficient power. The same is compared with its conventional counterpart (28T). The power consumption is found to be low in this design. The implementation is done on MOSIS 90 nm Technology [25].

(**Bhattacharyya, et al., 2014**): A hybrid full adder based on CMOS and transmission gate technique is proposed in this paper. The design is also extended till 32-bit full

adder operation. The implementation of the circuit is done in Cadence Spectre tool in 90 nm and 180 nm CMOS technology [3].

(**Paradhasaradhi, et al., 2014**): The "Modified CSLA (MCSLA)" is proposed in this paper, which is designed using "Common Boolean Logic" and implemented using the Wallace Tree Algorithm. The implemented MCSLA is compared with regular CSLA architectures. The proposed work requires lesser area in comparison to normal Wallace tree multiplier [26].

(Luu, et al., 2014): An unsigned 32-bit multiplier for best timing performance with the optimized area is proposed in this research paper. The architecture uses "a modified Radix-4 Booth encoder, a modified Wallace Tree adder, and a Carry Look Ahead adder" [27].

(**Reddy, et al., 2014**): In this paper, a Gate Diffusion Input technique based low-power multiplier for 8-bit operation is proposed. The reduction in power and area is achieved by using "Booth encoding and Wallace tree technique" as this algorithm generates the minimal number of partial products for signed number multiplication and provides an efficient way to add the partial products [28].

(**Srinitha, et al., 2015**): A VHDL based high performance Fused Add-Multiply (FAM) unit architecture is proposed in this research work. The proposed architecture uses 4:2 compressor block instead of full adder/half adder [29].

(**Jaiswal, et al., 2015**): A MUX based full adder is proposed in this research article and then, the work is further extended for designing a Wallace tree multiplier. Because of the optimization of the adder, the performance of the multiplier has got improved. The architectural design is done in Verilog, and the functionalities are confirmed using Quartus II [30].

(Shoba, et al., 2017): A "CslA and Binary to Excess 1 Converter (BEC)" based multiplier is proposed in this paper. Because of the use of the BEC, the total number of adders is reduced by n/4 than orthodox addition scheme (here 'n' is the width of the input). Moreover, a Vedic multiplier is used as a base multiplier which requires lesser

area and lesser delay. Additionally, Gate Diffusion Input (GDI) logic style is used for designing the proposed multiplier. The functionality of the proposed multiplier is analyzed and verified by Cadence Spectre Tool in 45 nm CMOS technology. From the comparative analysis, it is found that the proposed multiplier requires 17% lesser PDP than its close competitor. The Monte Carlo simulation is also performed to analyze the performance in extreme conditions [31].

(Ozcan, et al., 2018): A "Montgomery multiplier" which works iteratively is proposed in this work. A digit of the multiplier is multiplied by the digits of the multiplicand in every iteration. And the result is stored in an accumulator. Each time the total number of multiplier and multiplicand is reduced by the Montgomery method. As stated in the paper, the total number of iterations required to complete the multiplication process is eight cycles, and therefore it saves some hardware resources. The prototype of the architecture is implemented on the Virtex-7 FPGA board [32].

(Rose, et al., 2019): A DML multiplier which is capable of performing the mixed operation mode (i.e. a mixture of the static/dynamic mode) is proposed which promises to offer "better performance and energy trade-off" in comparison to the standard CMOS based designs. In fact, "the use of the dynamic mode for higher precision operations ensures higher performance as compared to the standard CMOS circuit (16% gain on average) at the cost of higher energy consumption". In comparison with standard CMOS implementation, the proposed DML's mixed-mode offers 15% of EDP improvement in a varied range supply voltage. A detailed PVT analysis is also carried out to ensure the performance at extreme conditions [33].

### 2.2 MULTIPLY AND ACCUMULATE UNIT

(Suzuki, et al., 1996): A FADD core is proposed in this design. The core has been fabricated in CMOS 0.5um technology. LZA technique is used for normalizing the numbers. HDL is used for the overall design [34].

(**Pillai, et al., 2000**): A floating-point low power multiply-accumulate unit is presented in this work. Transition activity and data path are simplified to reduce the power consumption. A 4 state FSM model is used to represent the switching activity. Due to data path simplification, the latency and delay are reduced [35].

(Natter, et al., 2000): A signed VHDL based MAC is proposed in this work. The design is also implemented on FPGA board. The proposed MAC algorithm uses "recursion formula in terms of new input-independent variables". The correctness of the proposed MAC is verified on MALAB and MAX plus II [36].

(William, et al., 2001): The technique proposed in the paper reduces the total number of partial product by a factor of two if applied to "signed-binay (SB) number". The work is also extended for FPGA hardware [37].

(**Plessis, et al., 2002**): Field Programmable Gate Arrays (FPGAs) are rapidly gaining popularity for signal processing applications. Multiplication, addition and Multiply-Accumulate (MAC) are the most important building blocks in signal processing. This paper will compare a number of structures to find the optimum configurations for minimum delay, size and cost in an FPGA [38].

(Huang, et al., 2002): A "novel limited resource scheduling (LRS) algorithm" based MAC for "DWT-processor" is proposed in this work. Given a set of architecture constraints and DWT parameters, the LRS algorithm can generate four scheduling matrices that drive the data path to perform the DWT computation, and the performance has also been investigated. Because the registers of FIR filtering are reused for the inter-octave storage, the MAClevel DWT architecture may require less extra inter-octave memory than the traditional architecture [39].

(**Premkumar, et al., 2002**): In this paper an alternative multiply accumulate units for the pulse shaping filters that use a new representation for their coefficients is proposed. Consequently, these new structures are fast, efficient and dissipate less power. The filters proposed take into account constraints, such as, inter symbol interference, response characteristics etc. in their design methodology [40].

(Tian, et al., 2002): In this paper, an algorithm of 32x32 multiply and MAC instructions' VLSI implementation with 32x8 multiplier-accumulator in DSP

applications is presented. The 32x32 multiplication is achieved by 4 times 32x8 multiplication. The result of 32x8 multiplication serves as a partial product of the next 32x8 operation, when the result' of such four multiplication is accumulated, we get the result of 32x32. The 32x8 multiplication is only implemented by the hardware Booth multiplier [21[31. The algorithm of multiply and MAC instructions' implementation is the better trade-off between serial multiplier and, parallel multiplier [41].

(Liao, et al., 2002): A high-performance and low-power 32-bit multiply–accumulate unit (MAC) is described in this paper. In the proposed architecture, one-cycle throughput for 16-bit 16-bit and 32-bit 16-bit MAC instructions was achieved at very high frequencies. To handle media streams more efficiently, the single-instruction-multiple-data (SIMD) and the multiply-with-implicit-accumulate (MIA) features were added [42].

(Kao, et al., 2002): This research develops a theoretical model to predict how dynamic power and subthreshold power must be balanced to give an optimal operating point that minimizes total active power consumption for different workload and operating conditions. A 175-mV multiply-accumulate test chip using a triple-well technology with tunable supply and body bias values is measured to experimentally verify the tradeoffs between the various sources of power [43].

(**Suvakovic, et al., 2003**): A mechanism to minimize non-adiabatic dissipation in adiabatic circuit is explained in this research work. As stated, "the non-adiabatic dissipation is minimized by architectural design involving a small number of complex logic gates". For designing complex adiabatic gates "Ordered Binary Decision Diagrams (OBDD)" is used. Finally, an optimized architecture "for adiabatic parallel multipliers" is explained and its power consumption is also estimated [44].

(Shim, et al., 2003): This paper shows the usage of MAC in Very High-Speed Digital Subscriber line. A detailed analysis is also performed for DMT (Discrete Multitone) and SCM (Single-Carrier Modulation) used in VDSL (Very high-speed Digital Subscriber Line). The work is further extended to estimate the memory requirement for the proposed design in addition to conventional complexity measures [45].