## DESIGN AND ANALYSIS OF CHALLENGE RESPONSE PAIR GENERATOR USING PUF AND DPA RESISTANT S-BOX

A Thesis

Submitted in partial fulfillment of the requirements for the award of the degree of

## **DOCTOR OF PHILOSOPHY**

in Electronics and Electrical Engineering

> By Abhishek Kumar

> > 41400729

Supervised By Dr. Suman Lata Tripathi

Transforming Education Transforming India

## LOVELY PROFESSIONAL UNIVERSITY PUNJAB 2020

## DECLARATION

I declare that the thesis entitled, "Design and Analysis of Challenge Response Pair Generator using PUF and DPA Resistant S-BOX" under the guidance of Dr. Suman Lata Tripathi, Professor, School of Electronics and Electrical Engineering, Lovely Professional University, Punjab, India. No part of this thesis has formed the basis for the award of a degree or fellowship previously.

Abhishek Kumar School of Electronics and Electrical Engineering Lovely Professional University Phagwara, Punjab Date

## CERTIFICATE

It is to certify that Abhishek Kumar (41400729) has completed the scientific formulation of the thesis entitled, "Design and Analysis of Challenge Response Pair Generator using PUF and DPA Resistant S-BOX" under my guidance and supervision. To the best of my knowledge, the present work results from their original investigation and study. No part of the thesis has ever been submitted for any other degree at any University.

Dr. Suman Lata Tripathi Professor School of Electronics and Electrical Engineering Lovely Professional University Phagwara, Punjab

## ABSTRACT

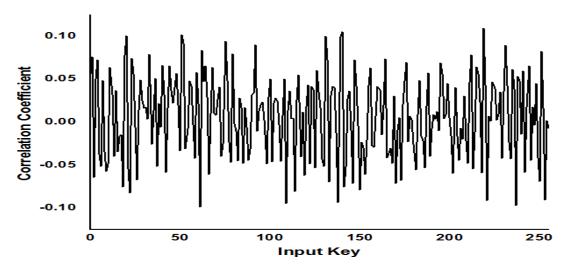

Traditionally, a large scale of integration (VLSI) implementation of a digital circuit is characterized as area power and delay; nowadays, additional parameter security is added as the 4<sup>th</sup> paradigm. Scaling offers an advantage as a reduction in dimension, but smaller devices exhibit high leakage. A complementary metal-oxidesemiconductor field-effect transistor (CMOS) -based low power VLSI design is a default standard for the electronic design automation (EDA) tool cell library. Implementation of a complex computation function like substitution-box (SBOX), a demanding block in terms of power, area, and security arises certain limitations, additionally leaks information along with unavoidable leakage current, known as sidechannel information. The side-channel analysis says leakage maintains relation with processed data, and attackers can access hidden secrets by analyzing it. The dynamic power of CMOS devices is dependent on data to be processed. Power trace varies depending on the number of high bit present and the number of bit position changes in the data. In this research work, we have implemented the SBOX with static CMOS and hybrid CMOS logic (Transmission gate (TG) and pass transistor logic (PTL)). Leakage cannot be avoided, but information leaks with leakage can minimize measure with Normalized energy deviation (NED) and normalized standard deviation (NSD). SBOX implementation with (TG+PTL) logic has achieved a reduction in NED by 48.64% and NSD by 21.8% compared to static CMOS. The cryptographic block's power consumption correlates with the intermediate result, allowing an attacker to predict the input data to be processed. Differential power analysis and correlation power analysis is the most critical side-channel attack, based on statistical analysis. Pearson correlation coefficient ( $\rho$ ) examines the dependencies between input data and power consumption patterns. A positive and higher value of 'p' justifies power pattern is highly correlated with processed data.

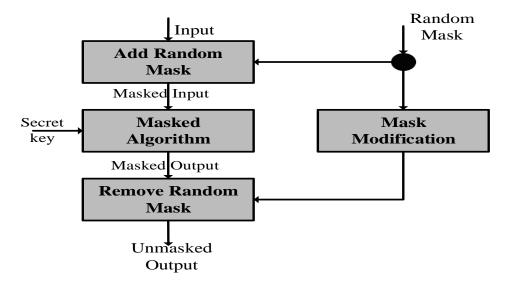

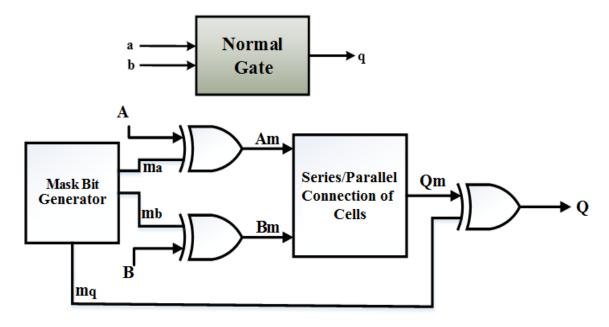

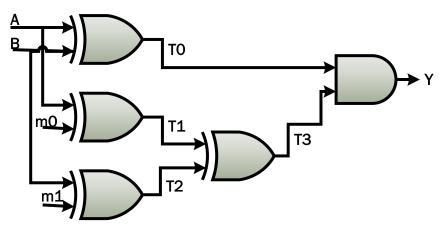

An attack resistant cell should not maintain relationships with processed data. Power attack countermeasure examines the strength of the CMOS cell to counter the power analysis attack. Hiding and masking are two widespread attacks resistant features to keep the device secure from a power attack. In this work, we have adopted a boolean

masking technique to randomized the intermediate information. The intermediate value of SBOX is masked with a random mask bit and additional cells; the output is unmasked with the same random bit or derived one. Masking at cell level modifies the cell design so that power consumption should be free from input data without disturbing functionality. Here mask XOR and mask AND cell (require for SBOX) presented whose actual power consumption does not depend on output node, it to be distributed on the internal node equally. The truth table approach is to verify the hamming weight of the internal node uniformly distributed; thus, power depends on all internal node attackers cannot predict the information by monitoring the output node only. SBOX implementation with mask cell improves the static power by 84.4%, dynamic power by 77.6%, delay by 164.8% compare to SBOX with unmask cell. The presented SBOX with Boolean masking at cell level requires 2173 gate counts, which is much lower than earlier reported work. Reduction in correlation coefficients between actual power and approximated power in the hamming weight power model is 32.17%, and 26.65% hamming distance power model implies independence between power consumption pattern and processed data. In Mask, cell input is mixed with the random number; the software mechanism to generate a random number is not truly random and repeats itself after definite sequence length. A physical unclonable function is one of the emerging hardware security modules whose response is a function of challenge input and device/specific feature. Due to manufacturing variation, a silicon-based device generates a unique response from the different circuits is preferred to design a physical unclonable function (PUF). Here we have presented Schmitt trigger PUF(STPUF), whose response is a function of circuit delay and hysteresis width. The presented STPUF validates the parameter with a uniqueness of 49.2% and reliability 99.7% under stringent operating conditions.

## ACKNOWLEDGMENT

First of all, I would like to express my gratitude to my supervisor, Dr. Suman Lata Tripathi, for her supervision, advice, and guidance, as well as extraordinary suggestions throughout the work. My special thanks to my previous supervisor Dr. Ravi Shankar Mishra, and Dr. KR Kashwan. I am very fortunate to have the opportunity to work with him. I found that their guidance is precious.

It is our pleasure to be indebted to various people, who directly or indirectly contributed to the development of this work and who influenced our thinking, behavior, and acts during the study. I am great full to my friend and colleague for their constructive suggestion.

I want to show gratitude to the School of Electronics and Electrical Engineering, Lovely Professional University, for providing me with a suitable research environment to carry out the research work.

I want to thank the almighty and our parents for their moral support.

# **TABLE OF CONTENTS**

| DECLARATION           | (ii)   |

|-----------------------|--------|

| CERTIFICATE           | (iii)  |

| ABSTRACT              | (iv)   |

| ACKNOWLEDGEMENT       | (vi)   |

| TABLE OF CONTENTS     | (vii)  |

| LIST OF TABLES        | (x)    |

| LIST OF FIGURES       | (xi)   |

| LIST OF ABBREVIATIONS | (xiii) |

### 1. Introduction

| 1.1 Introduction               | (1) |

|--------------------------------|-----|

| 1.2 Research's Contribution    | (4) |

| 1.3 Organization of the thesis | (4) |

### 2. Review of Literature

| 2.1 Hardware Security Module (HSM)                     | (6)  |

|--------------------------------------------------------|------|

| 2.2 PUF as HSM                                         | (7)  |

| 2.3 Power Attack on AES-SBOX                           | (7)  |

| 2.4 Side Channel Information                           | (8)  |

| 2.5 Categorization of Literature Review                | (9)  |

| 2.5.1 Literature Review of PUF                         | (9)  |

| 2.5.2 Literature Review of Power Attack Analysis       | (18) |

| 2.5.3 Literature Review of Power Attack Countermeasure | (22) |

| 2.5 Research Gap                                       | (31) |

| 2.6 Hypothesis                                         | (33) |

| 2.7 Objective                                          | (33) |

### 3. Physical Unclonable Function(PUF)

| 3.1 Introduction                       | (34) |

|----------------------------------------|------|

| 3.2 Application of PUF                 | (36) |

| 3.2.1 PUF based Authentication         | (36) |

| 3.2.2 Cryptographic Key generation     | (37) |

| 3.3 Classification of PUF              | (38) |

| 3.3.1 Delay based Arbiter PUF          | (39) |

| 3.3.2 Frequency variation based RO PUF | (40) |

| 3.3.3 Initial value-based SRAM PUF          | (41) |

|---------------------------------------------|------|

| 3.4 Schmit trigger PUF                      | (42) |

| 3.4.1 Different Topology of Schmitt Trigger | (47) |

| 3.4.2 Arbiter                               | (51) |

| 3.4.3 Schmitt trigger PUF (STPUF)           | (52) |

| 3.5 Result & Discussion                     | (56) |

| 3.5.1 Inter-PUF Variation                   | (57) |

| 3.5.2 Intra-PUF Variation                   | (57) |

| 3.5.3 Uniformity                            | (57) |

| 3.5.4 Bit Aliasing                          | (58) |

| 3.5.5 Uniqueness                            | (60) |

| 3.5.6 Reliability                           | (61) |

| 3.6 STPUF Evaluation                        | (63) |

| 3.6.1 Authentication                        | (63) |

| 3.6.2 Key Storage                           | (63) |

## 4. Substitution BOX (SBOX)

| 4.1 Introduction                                          | (65) |

|-----------------------------------------------------------|------|

| 4.2 Architecture of SBOX                                  | (67) |

| 4.2.1 Lookup Table SBOX                                   | (67) |

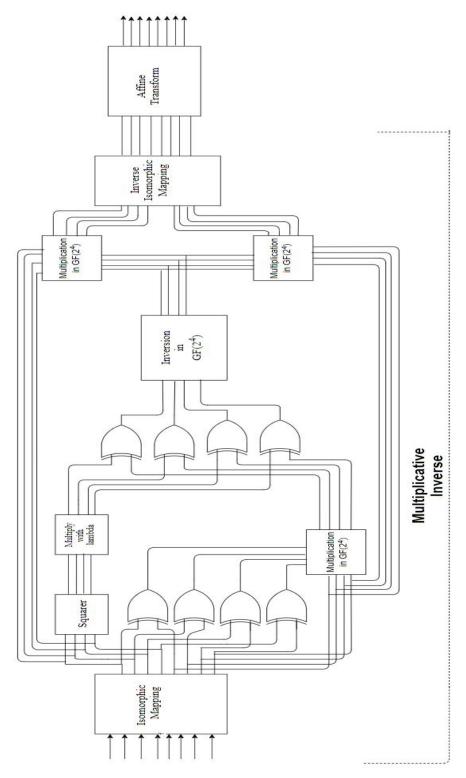

| 4.2.2 Computational Architecture of SBOX                  | (68) |

| 4.3 Internal Block of SBOX                                | (70) |

| 4.3.1 Isomorphic mapping                                  | (70) |

| 4.3.2 Addition in GF $(2^4)$                              | (72) |

| 4.3.3 Squaring in GF $(2^4)$                              | (72) |

| 4.3.4 Multiplication with constant ( $\lambda$ )          | (74) |

| 4.3.5 $GF(2^2)$ in Multiplication                         | (76) |

| 4.3.6 Multiplication with constant ( $\varphi$ )          | (77) |

| 4.3.7 $GF(2^{4})$ Multiplication                          | (77) |

| 4.3.8 Multiplicative Inversion in GF $(2^4)$              | (79) |

| 4.3.9 Inverse Isomorphic Mapping                          | (80) |

| 4.3.10 Affine Transform                                   | (81) |

| 4.4 SBOX implementation with static CMOS logic            | (82) |

| 4.5 SBOX implementation with Hybrid CMOS logic            | (85) |

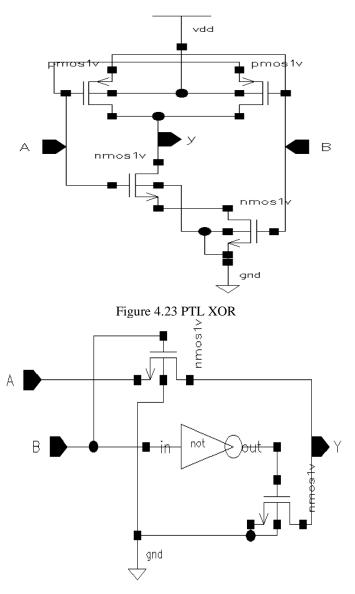

| 4.5.1.PTL XOR                                             | (85) |

| 4.5.2 PTL AND                                             | (86) |

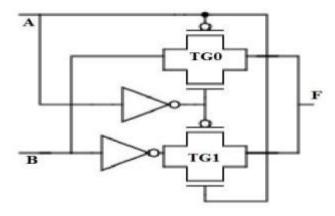

| 4.5.3 Transmission Gate XOR                               | (87) |

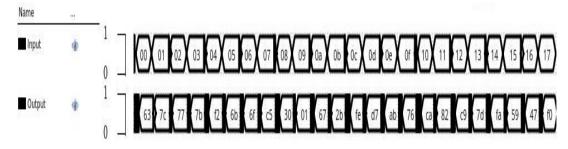

| 4.6 Result and Analysis                                   | (88) |

| 4.6.1 Dependency of Power Consumption with Processed Data | (89) |

|                                                           |      |

## 5. Power attack analysis

| (92) |

|------|

| (92) |

| (93) |

|      |

| 5.2.3 Dynamic Power                         | (93)  |

|---------------------------------------------|-------|

| 5.2.4 Power Delay Product                   | (95)  |

| 5.2.5 Energy Delay Product                  | (95)  |

| 5.3 Classification of Power Analysis Attack | (95)  |

| 5.3.1 Simple power analysis                 | (95)  |

| 5.3.2 Differential power analysis           | (96)  |

| 5.2.3 Correlation power Analysis            | (97)  |

| 5.4 Power Model                             | (99)  |

| 5.4.1 Hamming weight Power model (HWPM)     | (99)  |

| 5.4.2 Hamming distance power model (HDPM)   | (100) |

| 5.3 Experiment with DPA                     | (103) |

| 5.4 Experiment with CPA                     | (108) |

### 6. Power Attack Countermeasure

| (111) |

|-------|

| (113) |

| (114) |

| (116) |

|       |

|       |

|       |

| (120) |

| (123) |

| (125) |

| (128) |

|       |

### 7. Conclusion and Future Scope

| 7.1 Conclusion   | (132) |

|------------------|-------|

| 7.2 Future Scope | (133) |

|                  |       |

| Bibliography        | (134) |

|---------------------|-------|

| Index               | (151) |

| List of Publication | (152) |

# LIST OF TABLES

| Table 3.1 Strong vs Weak PUF                                                      | (38)  |

|-----------------------------------------------------------------------------------|-------|

| Table 3.2 Comparison of Schmitt Trigger                                           | (50)  |

| Table 3.3 Placements of Schmitt trigger circuit into PUF0                         | (53)  |

| Table 3.4 Placements of Schmitt trigger circuit into PUF1                         | (53)  |

| Table 3.5 Placements of Schmitt trigger circuit into PUF2                         | (53)  |

| Table 3.6 Placements of Schmitt trigger circuit into PUF3                         | (54)  |

| Table 3.7 Comparison of PUF's Parameter                                           | (63)  |

| Table 4.1 SBOX Values                                                             | (66)  |

| Table 4.2 Precomputed value of multiplicative inverse                             | (79)  |

| Table 4.3 power and delay report of an individual block of SBOX                   | (83)  |

| Table 4.4 Comparison of XOR-AND cell in different CMOS logic style                | (88)  |

| Table 4.5 Comparison of SBOX in different CMOS logic style                        | (89)  |

| Table 4.6 Comparison of energy parameters in SBOX topology                        | (90)  |

| Table 5.1 Power consumption pattern of CMOS Inverter with the respective bit      | (95)  |

| Table 6.1Transition energy for unmask XOR-AND cell                                | (115) |

| Table 6.2 Truth Table of Mask XOR-1 with Mask bit                                 | (117) |

| Table 6.3 Truth Table of Mask XOR-2 with Mask bit                                 | (118) |

| Table 6.4 Truth Table of Mask AND with Mask bit                                   | (119) |

| Table 6.5 Energy parameter and correlation of Mask gate                           | (122) |

| Table 6.6 Correlation coefficient ( $\rho$ ) between the actual power consumption |       |

| of SBOX and hypothesized power with HWPM for the correct key                      | (126) |

| Table 6.7 Correlation coefficient ( $\rho$ ) between the actual power consumption |       |

| of SBOX and hypothesized power with the HDPM for the correct key                  | (127) |

| Table 6.8 Comparison of different topology of SBOX                                | (130) |

| Table 6.9 Comparison of correlation co-efficient with hamming weight/             |       |

| distance power model                                                              | (130) |

| Table 6.10 Comparison of SBOX parameter with making method                        | (131) |

# LIST OF FIGURES

| Figure 2.1 Attack over SBOX Attack                                         | (8)          |  |

|----------------------------------------------------------------------------|--------------|--|

| Figure 3.1 PUF based Authentication                                        |              |  |

| Figure 3.2 PUF based key generation                                        |              |  |

| Figure 3.3 Arbiter PUF                                                     | (37)<br>(39) |  |

| Figure 3.4 RO PUF                                                          | (41)         |  |

| Figure 3.5 SRAM PUF                                                        | (42)         |  |

| Figure 3.6 (a) STPUF circuit                                               | (43)         |  |

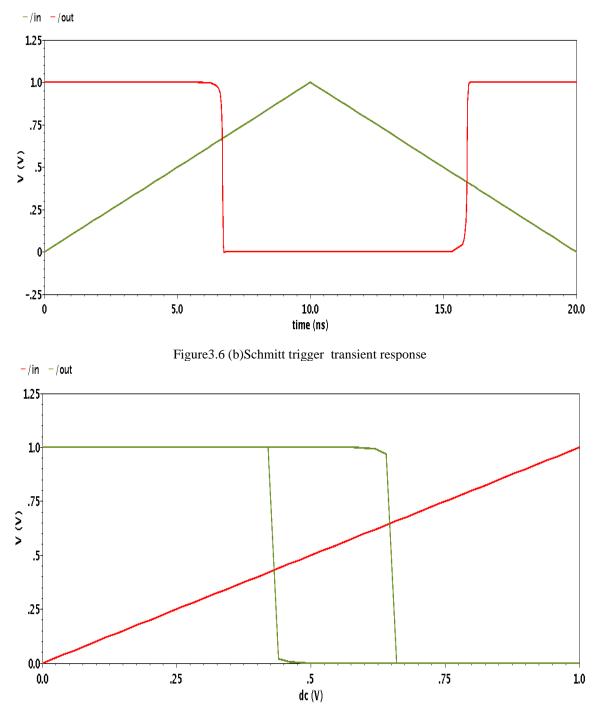

| Figure 3.6 (b)Schmitt trigger transient response                           | (44)         |  |

| Figure 3.6 (c) Schmitt trigger DC response                                 | (44)         |  |

| Figure 3.7 STPUF module                                                    | (46)         |  |

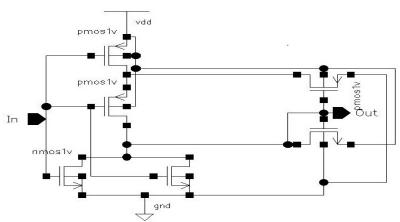

| Figure 3.8 (a) NORST                                                       | (47)         |  |

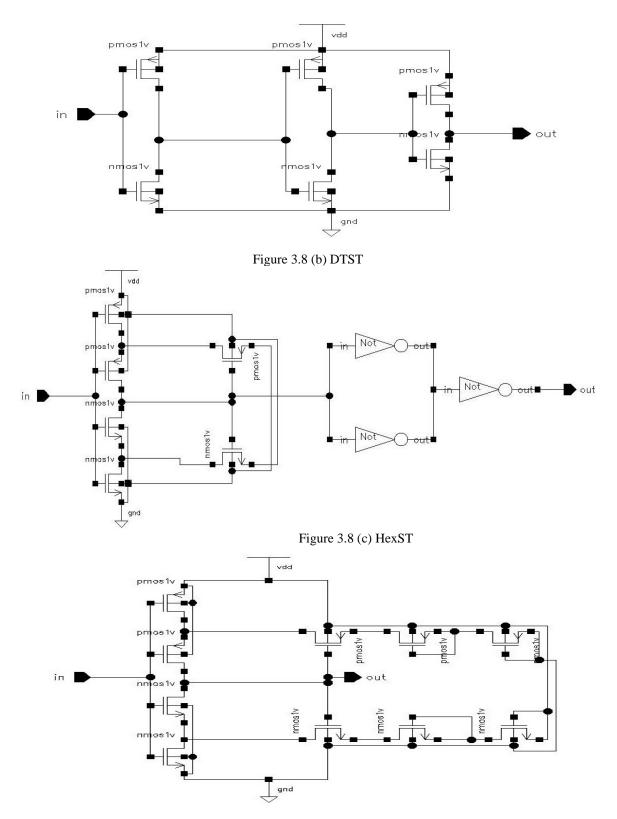

| Figure 3.8 (b) DTST                                                        | (48)         |  |

| Figure 3.8 (c) HexST                                                       | (48)         |  |

| Figure 3.8 (d) SAHST                                                       | (48)         |  |

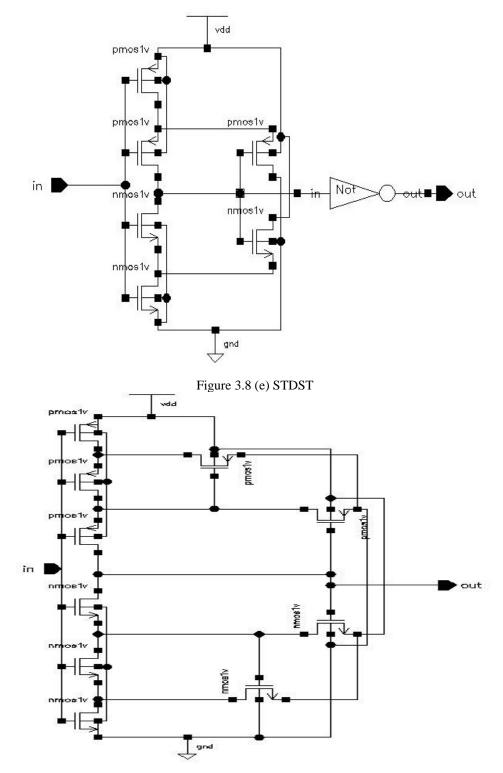

| Figure 3.8 (e) STDST                                                       | (49)         |  |

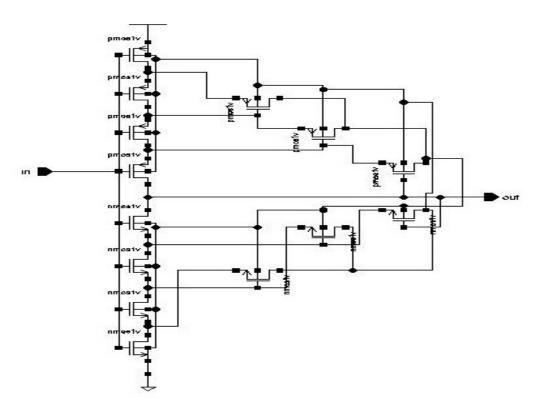

| Figure 3.8 (f) Ladder ST                                                   | (49)         |  |

| Figure 3.8 (g) SOIST                                                       | (50)         |  |

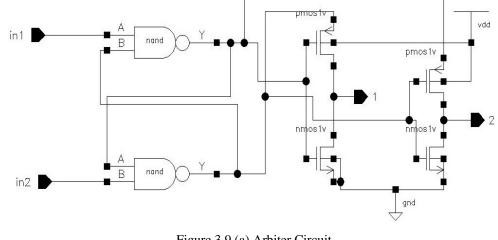

| Figure 3.9 (a) Arbiter Circuit                                             | (52)         |  |

| Figure 3.9(b) Arbiter response                                             | (52)         |  |

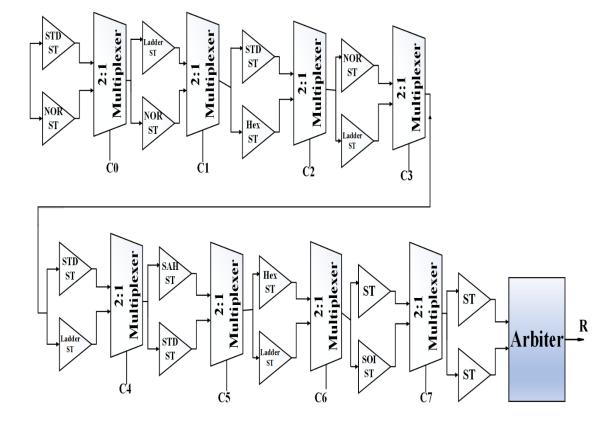

| Figure 3.10 PUF0 first row schematic                                       | (54)         |  |

| Figure 3.11 Simulation setup for PUF                                       | (55)         |  |

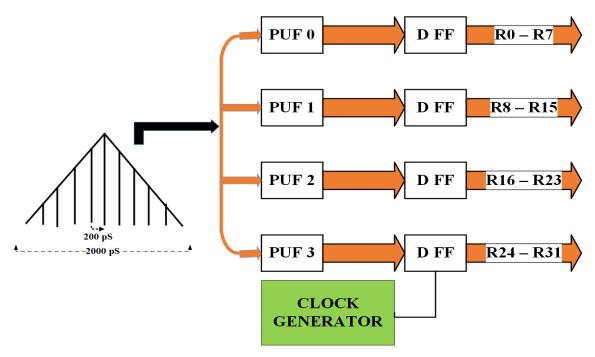

| Figure 3.12 Transient simulation result of PUF                             | (56)         |  |

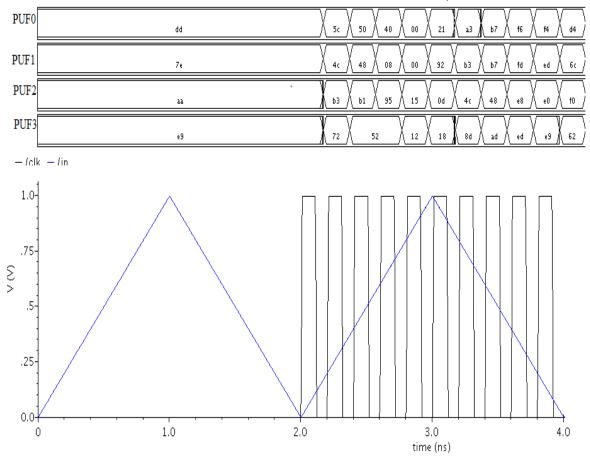

| Figure 3.13 Uniformity of STPUF                                            | (58)         |  |

| Figure 3.14 Bit aliasing of STPUF                                          | (59)         |  |

| Figure 3.15 Uniqueness of STPUF                                            | (60)         |  |

| Figure 3.16 Reliability of STPUF with temperature variation                | (61)         |  |

| Figure 3.17 Reliability of STPUF with supply voltage variation             | (62)         |  |

| Figure 3.18 STPUF authentication evaluation                                | (64)         |  |

| Figure 4.1AddRoundKey and SubByte Stage                                    | (66)         |  |

| Figure 4.2 Lookup table SBOX                                               | (68)         |  |

| Figure 4.3 Multiplicative inverse and Affine transform in SBOX             | (69)         |  |

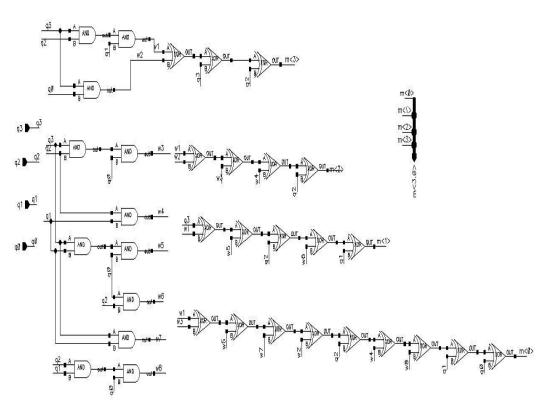

| Figure 4.4 Schematic of Isomorphic Mapping                                 | (71)         |  |

| Figure 4.5 Simulation result of Isomorphic Mapping                         | (71)         |  |

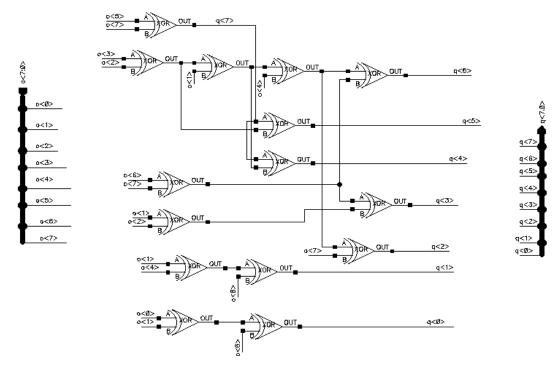

| Figure 4.6 Schematic of Squarer                                            | (73)         |  |

| Figure 4.7 Simulation Result of Squarer                                    | (73)         |  |

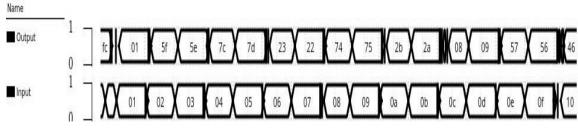

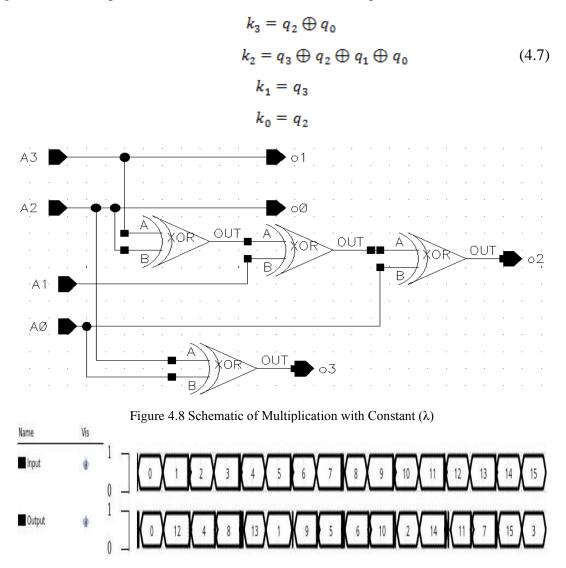

| Figure 4.8 Schematic of Multiplication with Constant ( $\lambda$ )         | (75)         |  |

| Figure 4.9 Simulation Result of Multiplication with Constant ( $\lambda$ ) | (75)         |  |

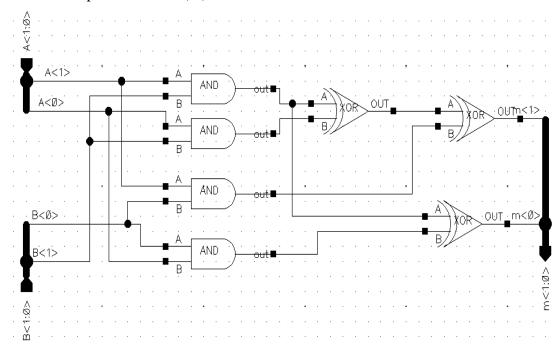

| Figure 4.10 Schematic of Multiplication in $GF(2^2)$                       | (76)         |  |

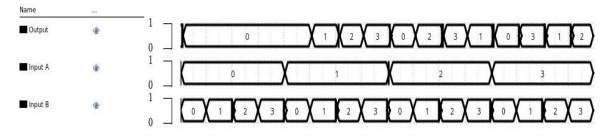

| Figure 4.11 Simulation Result of Multiplication in $GF(2^2)$               | (78)         |  |

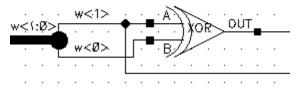

| Figure 4.12 Schematic of Multiplication with $\phi$                        | (77)         |  |

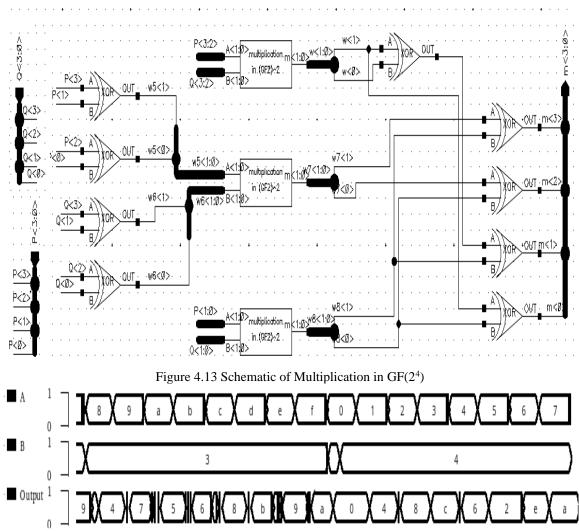

| Figure 4.12 Schematic of Multiplication in $GF(2^4)$                       | (77)         |  |

| Figure 4.14 Simulation Result of Multiplication in $GF(2^4)$               | (78)         |  |

| Figure 4.15 Schematic of Multiplicative Inverse in $GF(2^4)$               | (70)         |  |

| Figure 4.16 Simulation Result of Multiplicative Inverse in $GF(2^4)$       | (80)         |  |

| righter 4.10 Simulation Result of Manipheative inverse in Of (2)           | (00)         |  |

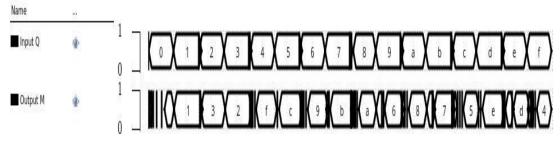

| Figure 4.17 Schematic of Inverse Isomorphic Mapping                       | (80)  |

|---------------------------------------------------------------------------|-------|

| Figure 4.18 Simulation Result of Inverse Isomorphic Mapping               | (80)  |

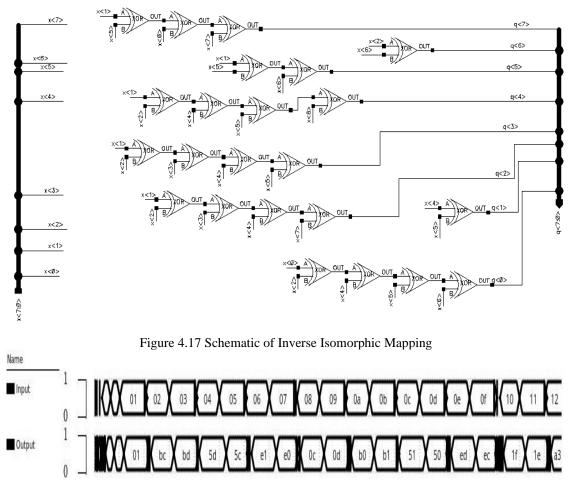

| Figure 4.19 Schematic of Affine Transform                                 | (82)  |

| Figure 4.20 Simulation Result of Affine Transform                         | (82)  |

| Figure 4.21 Interfacing diagram of SBOX                                   | (84)  |

| Figure 4.22 Simulation result of SBOX                                     | (85)  |

| Figure 4.23 PTL XOR                                                       | (86)  |

| Figure 4.24 PTL AND                                                       | (86)  |

| Figure 4.25 TG XOR                                                        | (87)  |

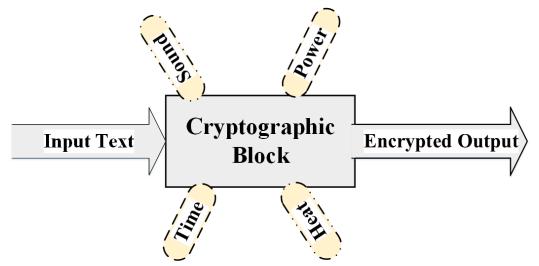

| Figure 5.1 Source of side-channel information                             | (91)  |

| Figure 5.2 Power trace in SPA                                             | (96)  |

| Figure 5.3 Flow chart of DPA                                              | (97)  |

| Figure 5.4 Flow chart of CPA                                              | (98)  |

| Figure 5.5 Power approximation with hamming weight                        | (100) |

| Figure 5.6 Power approximation with hamming distance                      | (101) |

| Figure 5.7 Current vs Hamming weight (HW)                                 | (102) |

| Figure 5.8 Current vs Hamming distance (HD)                               | (102) |

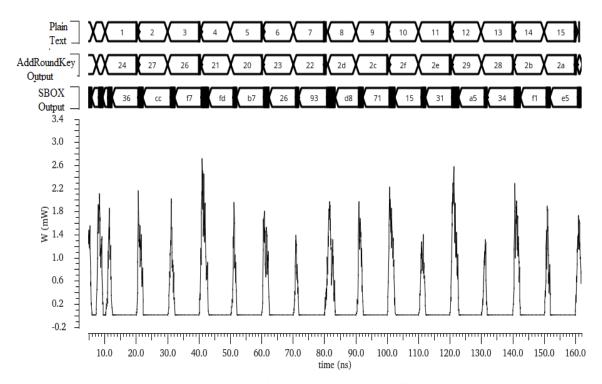

| Figure 5.9 Power trace of SBOX during DPA                                 | (104) |

| Figure 5.10 Power trace of SBOX during DPA for first 16 input             | (105) |

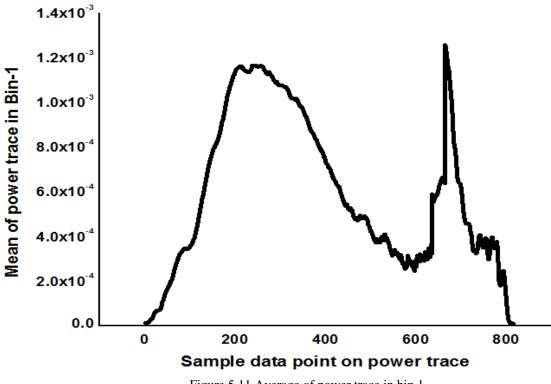

| Figure 5.11 Average of power trace in bin 1                               | (105) |

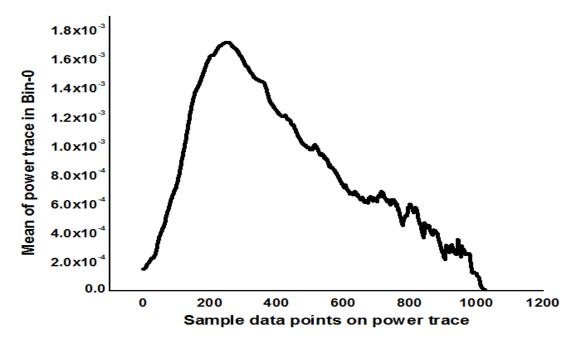

| Figure 5.12 Average of power trace in bin 0                               | (106) |

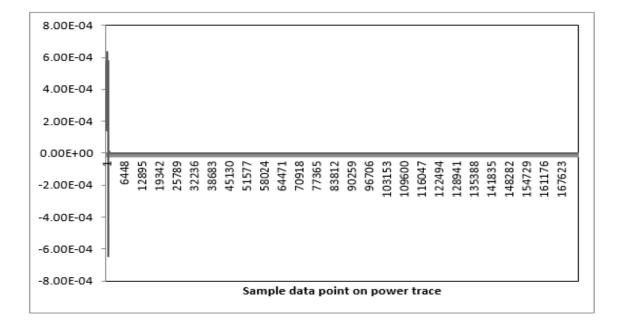

| Figure 5.13 Differential curve of average power trace for LSB1 and LSB0   | (106) |

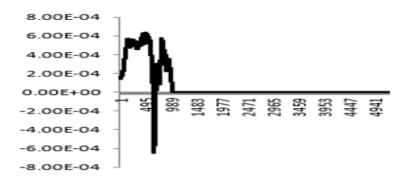

| Figure 5.14 Zoomed view of the differential curve for lower sampled value | (107) |

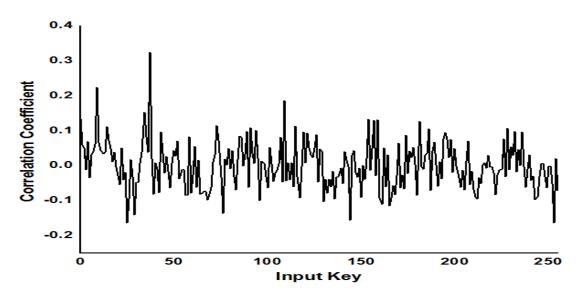

| Figure 5.15 Correlation coefficient vs guess key of SBOX with HWPM to     |       |

| guessed correct key 25H                                                   | (108) |

| Figure 5.16 Correlation coefficient vs guess key SBOX with HDPM to        |       |

| guessed correct key 25H                                                   | (109) |

| Figure 5.17 Correlation coefficient vs guess key of SBOX with HWPM to     |       |

| guessed incorrect key                                                     | (110) |

| Figure 5.18 Correlation coefficient vs guess key of SBOX with HDPM to     |       |

| guessed incorrect key                                                     | (110) |

| Figure 6.1 Boolean masking process                                        | (112) |

| Figure 6.2 Input-output of normal (unmask) and mask gate                  | (113) |

| Figure 6.3 Proposed mask XOR-1 cell                                       | (117) |

| Figure 6.4 Proposed mask XOR-2 cell                                       | (118) |

| Figure 6.5 Proposed mask AND cell                                         | (119) |

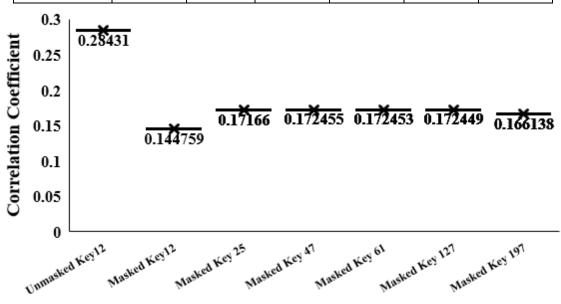

| Figure 6.6 Pearson correlation coefficient of normal and mask cell        | (123) |

| Figure 6.7 ILA vs probability of occurrence of mask bit                   | (124) |

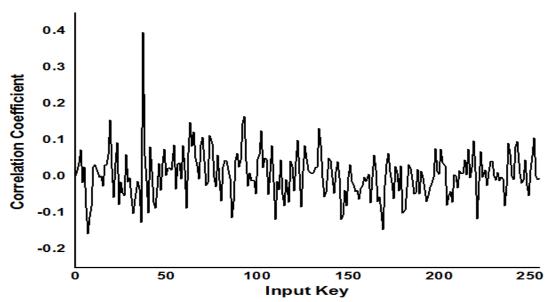

| Figure 6.8 Correlation coefficient vs guess key of mask SBOX with HWPM    |       |

| to guessed correct key                                                    | (125) |

| Figure 6.9 Correlation coefficient vs guess key of mask SBOX with HDPM    |       |

| to guessed correct key                                                    | (126) |

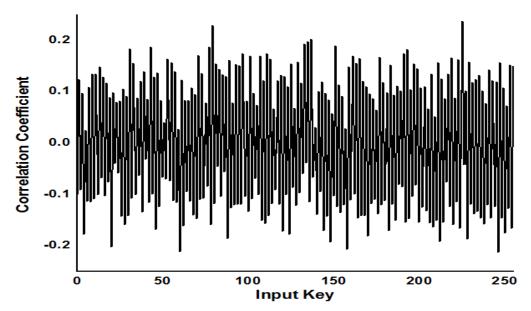

| Figure 6.10 Comparison of Correlation Coefficient of SBOX under           |       |

| CPA attack with HWPM for incorrect key                                    | (127) |

| Figure 6.11 Comparison of Correlation Coefficient of SBOX under           |       |

| CPA attack with HDPM for incorrect key                                    | (127) |

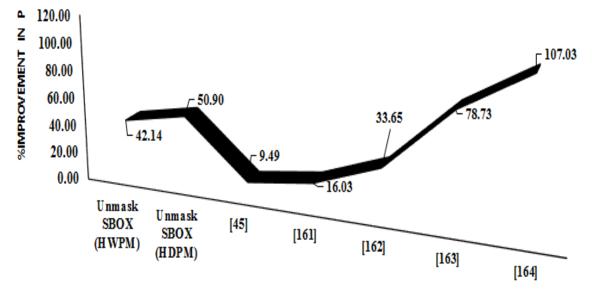

| Figure 6.12 Improvement in $\rho$ of SBOX with mask cell                  | (131) |

# LIST OF ABBREVIATION

### Abbreviations

### Description

| CMOS   | Complementary Metal Oxide Field Effect Transistor |

|--------|---------------------------------------------------|

| CPA    | Correlation Power Analysis                        |

| DPA    | Differential Power Analysis                       |

| EDP    | Energy Delay Product                              |

| HDPM   | Hamming Distance Power Model                      |

| HSM    | Hardware Security Module                          |

| HWPM   | Hamming Weight Power model                        |

| SCA    | Side-Channel Attack                               |

| LUT    | Lookup Table                                      |

| MuxPUF | Multiplexer based Physically Unclonable Function  |

| PDP    | Power Delay Product                               |

| PTL    | Pass Transistor Logic                             |

| PUF    | Physical Unclonable Function                      |

| RNG    | Random Number Generation                          |

| RO-PUF | Ring Oscillator Physically Unclonable Function    |

| SPA    | Simple Power Analysis                             |

| ST     | Schmitt Trigger                                   |

| ST_PUF | Schmitt trigger PUF                               |

| SBOX   | Substitution Box                                  |

| SVM    | Support Vector Machine                            |

| TG     | Transmission Gate                                 |

### **1.1 Introduction**

Hardware security is a protection methodology that comes with physical devices rather than a software algorithm. While accessing the equipment, we put a lot of trusts, are we interacting authorized devices? Whether our sensitive data is preserved? The cryptographic protocol restricts access from unauthorized users. Cryptographic algorithms like Advance encryption standard (AES), Data encryption standard (DES), etc. require the secret key. During encryption user, input data is mixed up with a secret key, generates ciphertext, which would decrypt with the same key. The security level of the algorithm aligns with the secret key. The contender tries to predict or clone the intermediate round key, elaborated in [1]. Hardware limitation of very-large-scale integration (VLSI) implementation of the cryptographic module highlights the weakening of the security algorithm. Traditionally VLSI circuit's attribute is characterized by area, power, and delay, now a day's 4<sup>th</sup> parameter identified as security. Security into the system must arise from the root of trust. The hardware security module is a function whose output (response)is a nonlinear function of challenge input and unpredictable for unauthorized users.

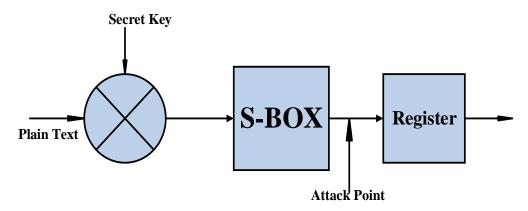

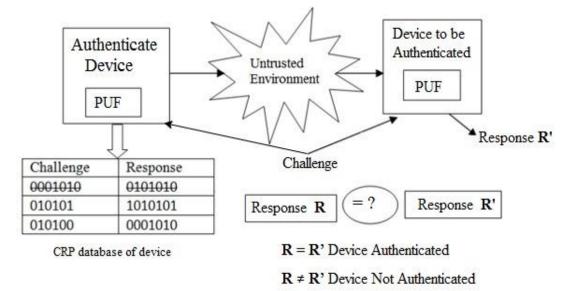

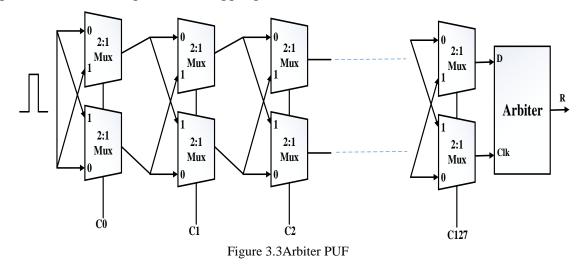

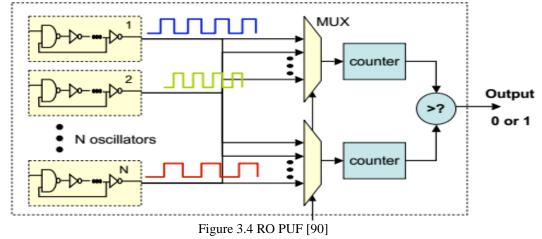

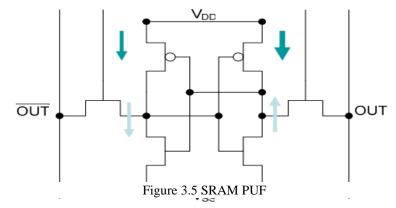

Physical unclonable function (PUF) is a simplified structure of the hardware security module (HSM) [2] [3] that, for a part of the given information, provides a physically defined response. Semiconductor-based PUF utilizes unique physical equipment or circuit variation, which occurs naturally during manufacturing [4]. According to NXP semiconductor, electronics properties which are variable into nature and last with the stable state can use to have a PUF system. Selected unique features of electronic devices are included in computation to generate a response; output response is a function of input and device-specific properties. The expectation from PUF is (a) for the same challenge multiple PUF should have different response (b) response of PUF are uniformly distributed (c) PUF's responses should stable even in the unsecured operating environment. If secret keys and structures are known to 3<sup>rd</sup> parties, they will not have access to unauthorized access. PUF found two significant applications as secured authentication and key generation in a cryptographic key generation [5] [6]. 2 accessible structure of PUF is delay based arbiter-PUF and frequency variation-based ring oscillator PUF(RO-PUF).

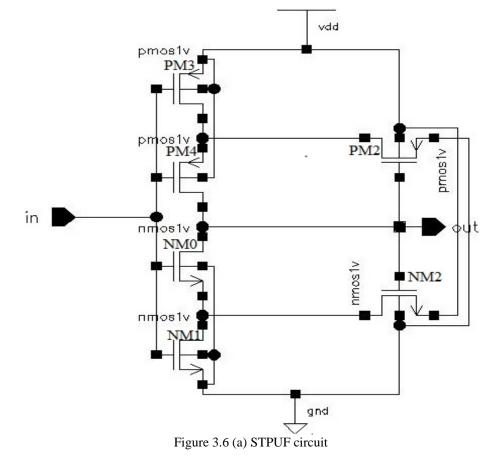

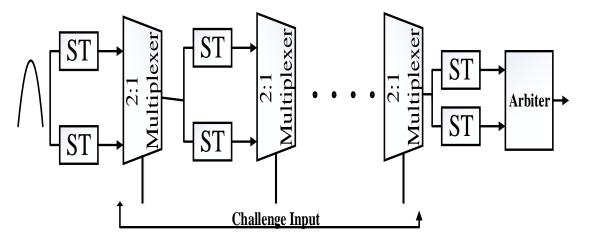

In this work, Schmitt trigger based PUF structure presented; whose output responses are a function of challenge two device-specific feature threshold voltage and hysteresis width. Schmitt trigger acts as a wave shaping circuit to variable signal consists of 2 trigger voltage. Here eight different architecture of trigger circuit has been utilized to generate multiple trigger points. The cascaded connection of Schmitt triggers the circuit to sample the input signal numerous times. Hysteresis width or delay associated with circuit put their effect in the computation of responses for a given input challenge. The first time in the literature that PUF response is a function of more than one device signature. A Schmitt trigger PUF (STPUF) enhances the response bit generation.

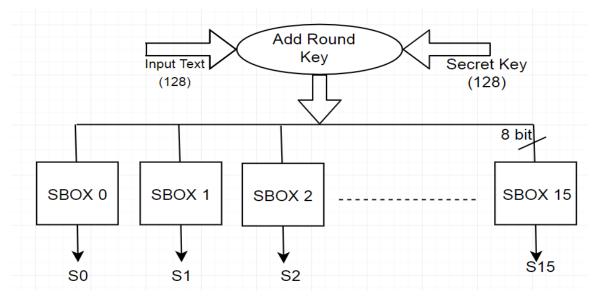

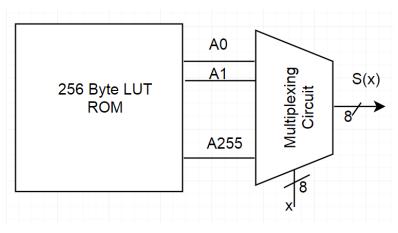

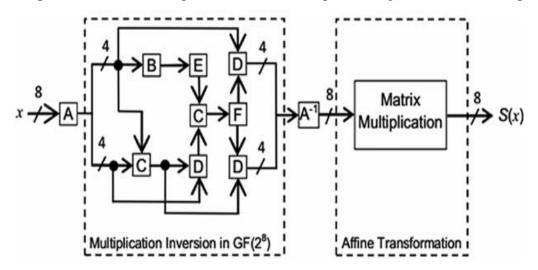

AES is adopted as the standard for the specification of electronics data by the national institute of a standard technology (NIST) in 2001. AES algorithm is based on complex mathematical computation. AES-128 bit required 128-bit size of plain text and secret key, repeat internal module AddRoundKey, ShiftRow, SubByte, and MixColumn by the ten rounds. Out of which, SubByte is the most complicated block; it includes the non-linearity into the computation. In this step, 256 single-byte arranges as 16\*16 matrix, known as substitution box (SBOX). Two famous architecture of SBOX presented in [7] is a lookup table (LUT) based and computational architecture using the Galois field (GF). LUT based SBOX require the large size of memory and efficient fetching device to substitute by a single nonlinear byte.

The limitation of LUT-SBOX is an unavoidable delay and leakage of the memory element. VLSI implementation of GF-SBOX shown in [8] requires substantial resources. Consumes maximum power in the encryption takes 75% of total power alone. CMOS transistors-based logic gate is the default standard for design lower power circuits, but the power requirement of CMOS devices depends on the input data. In addition to primary

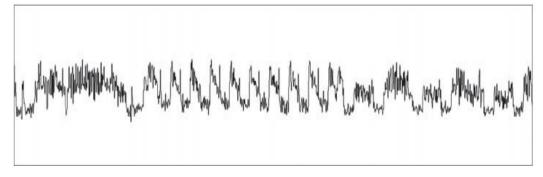

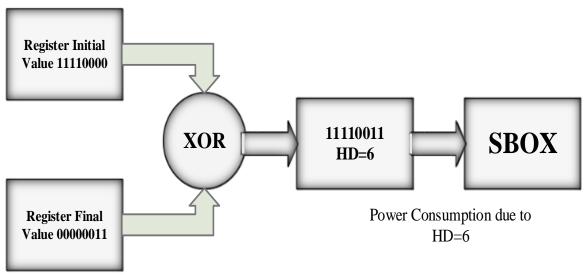

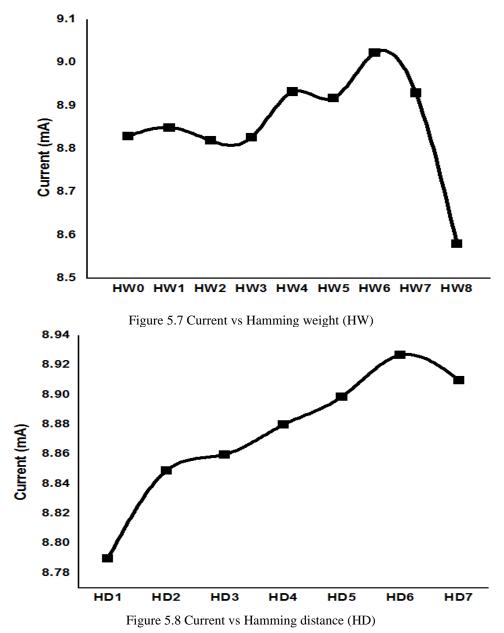

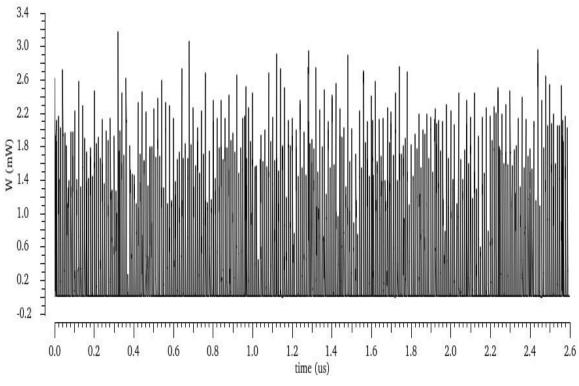

output, SBOX leaks secondary information in terms of power, simulation time, electromagnetic radiation, and sound, known as side-channel information. Dynamic power consists of significant chunk information about hidden data at the internal terminal, which can be revealed. Attackers target the point where maximum information can be extracted from, a power trace discussed in [9]. The power trace of SBOX depends on the number of high bits (hamming weight) of input data and the number of bits changing at the input (hamming distance). Information can reveal from a power trace; like how many highs in the data, time to application of data, change of bit position on MSB or LSB. The attacker performs statistical analysis from the stored power trace, available information, and tries to guess the correct secret key.

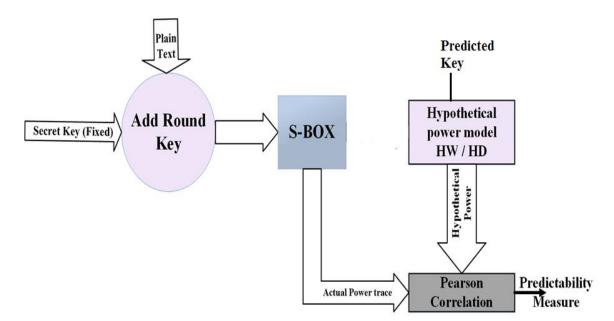

Power analysis attack is based on a hypothetical model of power traces obtained with hamming weight or hamming distance of input. Specific statistical parameters, like mean for differential power attack (DPA) and person correlation coefficient for correlation power attack (CPA), are utilized to develop a relationship between actual power trace and mathematically calculated power value. Since the power consumption of CMOS devices is data-dependent, to include power attack resistant features, power consumption must be independent of the input data. Hiding and masking are two popular algorithms of power countermeasures. Hiding countermeasures shown in [10] hides the power consumption of key-dependent cryptographic computations by increasing the signal-to-noise ratio (SNR), randomize the power, and equally balance the power at each moment. Masking countermeasures randomize the intermediate value of cryptographic computation to avoid dependencies. Masking applies at (a) algorithm level where some part of the algorithm needs to rewrite and (b) cell level where each cell of design is resistant to power attack explain in [11]. Boolean secret sharing of mask schema employs new cells into a model with a mask bit. Here input bits mixed-up with random mask bit using XOR gate and final output are unmasked with external mask bit or internally generate signals. A mask gate does not change the functionality but reduce the dependencies of power consumption with input data. Masking countermeasures decreases the correlation between actual power consumption and power value computed by the mathematical model. These

countermeasures enhance the security level at the cost of area and high power consumption.

#### **1.2 Researcher's Contribution**

In this work, we have presented the Schmitt trigger (ST) based physical unclonable function, whose response is a function of challenge input and two device-specific features. It is the first time in literature, where PUF responses are a function of multiple hardware-specific features. Another part of the thesis is power attack countermeasure with mask cell. Power attack analysis enables the adversary to extract the hidden information by statically analyzing the leakage with a hypothetical model. The proposed mask XOR and mask AND cell include the power attack resistant feature into the design. SBOX implement with mask cell shows achieve the lower value of the correlation coefficient, Implies the power consumption pattern does not maintain linear relation with processed data.

#### **1.3 Organization of the thesis**

The thesis is organized into seven chapters. A brief outline of the chapters is given below. Chapter 1 introduces the requirement of hardware security. It highlights the key point to design physical unclonable function, and brief about limitation arises due to side-channel information. The author's contribution included in this chapter.

Chapter 2 presents the research work done by a different researcher, according to the author's objective. The literature review is segregated into three categories physical unclonable function creation, power and attack, and power attack countermeasure.

Chapter 3 proposes a novel design of a Schmitt trigger-based physical unclonable function novel. The simulation result of STPUF is thoroughly analyzed, and their achievement has been explained in the chapter.

Chapter 4 proposes an optimized design of SBOX. A detailed description of the Internal block of SBOX covered in this chapter. Implementation of SBOX with static and hybrid CMOS logic is described in the section. The results of the simulation are also analyzed in the chapter.

Chapter 5 includes the power analysis attack onto SBOX with hamming weight and hamming distance power model. The dependency of actual power and predicted power is analyzed in the chapter.

Chapter 6 highlights the attack resistant feature of the logic cell involved in the design. This chapter analyzed the masking technique to mask the sensitive information of the circuit.

Chapter 7 concludes the thesis and highlights the prime outcomes of the author's current research and the significant contribution of the thesis and notifies the scope for future research in this area.

## Chapter 2 Review of literature

Historically three-parameter power, area, and delay used to optimize semiconductor design. The area is related to cost; larger areas reduce the number of dies onto a wafer led to an increase in processing and material cost. The performance of the VLSI circuit measured in terms of circuit speed. Lower propagation delay leads to higher performance of the digital circuit. Power dissipation has a profound impact on both cost and performance. High power dissipation requires additional heat removal and advanced packaging technology, increase the cost and system size. Power and delay are contradicting factors as a function of the supply voltage. Delay of circuit reduces with higher supply voltage, but higher supply voltage results in high power consumption. For the given circuit these factor trade-offs according to the application [15]

CMOS is dominant in the VLSI era since 1970. The progress of VLSI technology makes an instructive trade-off in the I.C. design process. In 1970, yield or die area was the primary concern. With advances in technology in 1980, circuit speed is the principal limit. With the progress of scaling era of 1990 was focused on optimizing speed and power. Integrating a higher number of components onto a wafer leads to noise, in 2000, is known for optimizing the power and speed with noise. 2010 is known for the inclusion of security at the design level. It is an additional block in the circuits introduced to make the leakage information independent of the data to be processed, leading to an increase and die area, power consumption. However, the delay can optimize by a directed critical path.

### 2.1 Hardware Security Module (HSM)

Hardware security is an emerging field of engineering to enhance the security level of the cryptographic algorithm by including the unpredictable features form semiconductor devices.

#### 2.2 PUF as HSM

A physical unclonable function is an innovative circuit extract unique intrinsic feature of the integrated circuits. Gassend and Blaise et al. in 2002 introduced delay PUF [16] based on the silicon IC-based PUF circuit. Two silicon devices cannot have the same properties in all aspects, even manufacturing with similar material and corresponding instruments. G. Suh and S. Devdas in 2007 [17] introduced the application of PUF into authenticating and random numbers of generation. PUF response should be unique for each challenge and not able to predict by other users. The feature of the PUF circuit is validated by Horie et al. [18] in 2013 with uniformity, uniqueness, and reliability.

#### 2.3 Power Attack on AES -SBOX

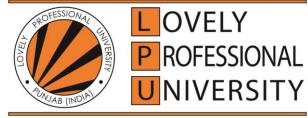

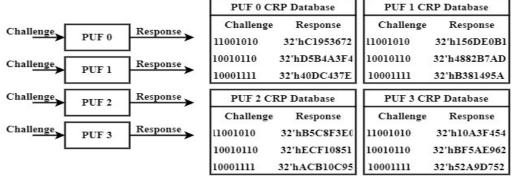

Traditionally, a circuit's performance depends on area, power, and delay; time demands to add 4<sup>th</sup> parameter security. Security should emerge from the hardware, preferably only with a cryptographic algorithm. A circuit response must be secured; the adversary must not predict the circuit detail like internal block function, hidden secret, etc. During computation, the VLSI circuit must leak secondary information in terms of power, delay, electromagnetic radiation. According to [64], power analysis is the most efficient sidechannel attack. The power attack starts with identifying high-power consumption points in the crypto circuit so that maximum information can be collected. Identifying sensitive location in a power attack is necessary, where the relation between power trace and data can be analyzed. Substitution box in AES is the hungriest power consumption block, 75% of encryption/decryption power consumed by SBOX alone. SBOX is the most demanding block in terms of area, power, delay, and security measure. Figure 2.1 shows that a typical target point is the output of SBOX. AddRoundKey mixes the 128-bit input byte with the same sized secret key followed by SBOX. An SBOX operated on a single byte; thus, 16 SBOX needed in parallel to performs substitution. The output of each SBOX provides an exciting point to collect power traces. Since the algorithm is available for public, input, or output, it may also be available, only unknown is the secret key byte. An attacker stores the power information [127] for each possible input and tries to predict the processed data at SBOX. The data can reveal time to application of data, number of high bits in the data of SBOX, number of bits switching at the input. SBOX consumes minimum power for the lowest of hamming weights of input data, and power consumes maximum for the highest of hamming weights.

Figure 2.1 Attack over SBOX

#### 2.4 Side-Channel Information

A side-channel attack is a methodology to obtain a circuit secret based on information gained rather than the security algorithm's weakness. Security algorithms like DES, AES is mathematically secured require primary input by a user, and secret key computes primary output. [61, 71] described VLSI implementation of such an algorithm suffers from hardware limitations. CMOS device suffers from leakage issues, and this issue arises more for scaled MOS transistors. CMOS implementation of the cryptographic algorithm does compute primary output, in addition to that leak's secondary information. This information contains information related to circuit internals terminal; the attacker uses this information to gain access over the device by reverse engineering known as a side-channel attack. Sources for side-channel attacks are power, heat, sound, timing, fault, etc., out of which power attack is considered the most productive offence. Side-channel attacks presented in [69, 82] classified as (a) passive side-channel attack utilizes leakage information external to a device with the interface. (b) An active side-channel

attacker manipulates the device, injecting probes, and injecting fault to learn secret information discussed in [126].

### 2.5 Categorization of Literature Review 2.5.1 Literature Review of PUF

In paper [19] by Maiti, A., Kim, I., & Schaumont, P. (2011), challenge-response pair (CRP) is the essential requirement of device authentication explained, for each challenge generated response must be unique. A reliable PUF must create a different response from multiple responses for the same input challenge; A reliable PUF must make a large number of random numbers to derive the secret key. In this paper, the author suggested an R.O. based scheme to enhanced CRP set. The entropy of a PUF is controlled by circuit parameters to build it. Large size key and a broad set of challenge-response pairs enhance the circuit hardware area and hardware cost. Here the author has implemented ROPUF to generate the same size of CRP pairs with reduced resources. CRP generator using ROPUF map to FPGA platform capable of creating new functions using statistical hypothesis test; reduce the area by two times. PUF quality is measure using uniqueness, reliability, and unbiased. The average value inter-chip H.D. of presented PUF is 50.07% achieve high uniqueness and reliability of PUF output with the slow area. A PUF circuit should able to generate individual responses even in a secured environment. Memorybased response bit generation at high temperature and threshold voltage variation. Study of the effect of environmental and diversification into supply voltage in terms of mean, standard deviation, and its limitation explored.

In paper [20] by Eiroa, Susana et al. (2010), different structures of PUF, like Arbiter PUF, Ring oscillator PUF, Butterfly PUF, and NOR-based PUF architecture designed and their performance compared in term of inter hamming distance, intra hamming distance. PUP map the set of challenges bit/byte to a set of responses bit/byte driven by physical properties that are difficult to predict and reproduces. 2 significant applications of PUF have secured authentication and hardware-based random number generation [21]. Exact random generation scheme based on silicon I.C. discussed, and their statical analysis of

randomness, uniqueness reliability explored. Implementation difficulty and their sensitivity to the environment investigated. The selection of PUF could be difficult since several parameters to control to generate the response. Here the author has presented a report to various PUF architecture; reconfigurable PUF dynamically modifies the inherited properties. Controlled PUF uses a general processing element to access through a specific application. Leakage current PUF based on leakage current of a cell, leakage current to be converted to a digital one, and codified to obtains the I.D.

In paper [22] by Kumar et al. (2008) presents one of the most challenging tasks for I.P. vendors, FPGA manufacturers are I.P. protection use bitstream encryption. PUF is a different physical system extract response from the intrinsic physical properties of the integrated circuit. Describes PUF provides un-clonability means of a highly secure method of generating a volatile secret key of the cryptographic operation. In this paper, the author has utilized D-latch's unpredictable behaviour to settle on a stable state after metastability due to setup and hold time violation. A cross-coupled D latch structure acts as butterfly PUF implemented using I.P. available in every FPGA, i.e., CLB, BRM. Inter and Intra hamming distance variation at temperature variation from -20 to 80 C is analyzed. Validation of PUF with a difference of hamming distance measured on the FPGA and between the difference in H.D. of multiple FPGA. Butterfly PUF uses the internal matric of available resources on FPGA to generate the response using the integrated circuit's intrinsic physical properties. Butterfly PUF is a promising module that generates stable response and FPGA operating environment.

In paper [23] by Katzenbeisser et al. (2012), the contribution is ASIC implementation of delay arbiter and ring oscillator (RO-PUF), SRAM memory-based PUF based on SRAM, latch and flip flop is designed using CMOS 65nm technology. The author has analyzed the properties of PUF at temperature, supply voltage, and noise. ROPUF achieve all desired properties [24], SRAM PUF instance is independent. Evaluation result based on 96 ASICs based on TSMC 65nm CMOS technology. PUF is analyzed based on the following properties (a) robustness- quantified by bit error rate, the number of bits in a response1 is different from response2. (b) Unpredictability contenders not efficiently

compute the response of PUF to a known input challenge. The author has experimented with ring oscillator and SRAM PUF and analyzed it with 96 ASICs. Arbiter PUF sows very low entropy; a change influences the entropy of flip-flop and latches in temperature. Suitability and selection of PUF are essential for critical application for authentication and key generation.

In paper [25] by Majzoobi et al. (2012), slender PUF protocol presented a secure method to authenticate and respond generated from strong PUF using arbiter. Linear arbiter and two independent parallel arbiter path response mixed (XORed) to put into effect PUF with better statically properties. Slender PUF used the right random number and found that arbiter PUF of length 64 modelled as 95% accuracy. Presented slender PUF does not follow the classical paradigm of exposing the complete responses, a random subset of responses sent for authentication. The response pattern is lightweight and possesses resilient against machine learning attack, additional error correction logic, and fuzzy extractor for robust authentication. The critical length of slender PUF of 128, 256, and 512 achieve hamming threshold 33,76 and 154, respectively.

In paper [26] by Handschuh et al. (2010), PUF is used to extract the key and be considered an electronic fingerprint or feature of a device. PUF involves a physical device's feature challenging to clone due to the unique micro and nanoscale properties driven by manufacturing variation. Cloning of PUF requires lots of time, complex mathematical models, and software programs to compute the precited response of a challenge within the expected amount of time. Here author used variation among threshold voltage in the transistor of SRAM as a biometric feature. Fast and slow transistor chooses logical preference to settle both logic 1 to 0. The secret key stored in non-volatile memory; in this paper, the author introduced a reliable key storage technique on SRAM, ROM. A threshold voltage of different transistors achieved by carrying a length of individual transistor and provide a unique start-up value from each cell. Quality of PUF evaluated with operation consultation variation into temperature, voltage variation, and radiation. Reported PUF of different PUF are; SRAM PUF 950/1000 bits Delay PUF 130/1000 bits and Butterfly PUF 600/1000 bits.

In paper [27] by Barak et al. (2014) true random number generation scheme is explained. The random number should not be computable. PRNG based random number is not entirely non-deterministic, and the upcoming number can guess statically based on the previous history. The random number found applications in multiple critical applications in a lottery, Monte-Carlo simulation, cryptographic key generation, etc. The software mechanism to generate random is not entirely random and repeats itself after a particular set and can compute if the initial seed or previous number pattern is known. A true random number generator mix selected propertied from the hardware. Generated random number is a non-linear function of this feature. In this paper, the author has discussed the noise-based entropy generation, which is further processed to create a random number. R.O. based glitch is the source of entropy for generation scheme. The author has discussed the open problem and outlook in random number generation. The noise mechanism generates small voltage strongly amplified and converts to digital form. Since the I.C. designer reduces noise to any level design of the amplifier is cumbersome. Chaos RNG conceptually mixing the randomness, set of free-running oscillator generates multiple frequency, randomly chosen rate applied to digital block to have a random bit.

In paper [28], Bhargava et al. (2010) Attack resistant sense amplifier based PUFs based on the sensed voltage. The amplifier acts as a reading path in static memory. This circuit able to detect small voltage variation in the cell. In this work, the author has designed a large number of SRAM cells with a different threshold voltage. Forlag input, each cell carries a different voltage. For each column sense amplifier, enables, Generated response depends on offset voltage and mapping scheme. Sense amplifier resolves 0 or 1 bit with equal probability, with minimum voltage microvolts. A post-processing block corrects the error onto the response to have a stable and reliable bit. The cost-effective technique of error-correcting code (ECC) block presented in the paper sensed amplifier PUF is resistant to environmental change. SA PUF architecture accesses the S.A. array challenge bit select the address the response passed through scrambler. CMOS 65nm technologybased simulation result present that average Hamming distance 16.000937 and reduce the area by 2.5-time. In paper [29] by NXP semiconductor (2013), Processor-Based Strong PUF verified with an ageing analysis of response reliability. Process variation based inherent randomness in silicon I.C. affect threshold voltage, effective gate length, and various side effects. Two different ALU core response arbitrated to have final response bit. in between circuit xor gate additionally intended to have data obstruction. Hamming distance variation on applying various challenge and PUF behaviours are studied. A smaller circuit added into the processor known as on the fly extraction of response bits to have a unique timing signature. The presented PUF achieves average Hamming distance 16.1% for a 32-bit response; the ageing parameter measures the deterioration of logic level with time—this difference used as a stimulus to an amplifier and digital conversion block. CMOS 45nm technologic node implementation shows the average intra chip hamming distance by 98.1%.

In paper [30], Hossain (2015) promising security module based ROPUF random function of I.C.'s specific functions that are unique for every instance of the die. I.C. manufacturing variation used to generate a different kind of PUD. RO is the best candidate for the PUF circuit; it always gives properties as expected. In this work, the author proposed 13 sets of RO PUF generating independent frequency, each stage of inverter in R.O. designed in CMOS and FTL inverter. A comparative study of normal and FTL inverter presented; FTL more inverse comprises additional NMOS in parallel gate terminal controlled by the independent clock. FTL inverter provides a high operating frequency. Randomly one of the frequencies selected to respond a bit. Achieved result show that uniqueness is 45.24% (ideal 50%) reliability 91.14%(ideal 100%) and uniformity 41.45 %(ideal 50%). PUF quality measure uniqueness, reliability, and uniformity with PVT variation reported with low threshold voltage 46.85%, 95.54%, and 40.799% for high threshold 41.71%,90.12%, and 42.34% respectively.

In paper [31], Maiti et al. (2009) application of PUF presented as True Random Number Generator (TRNG). PUF and TRNG are two successful components in secrete system design. PUF extracts a random chip signature to generate a volatile secret key and TRNG use for making random padding bits and initialization vector. Here the author has explored R.O. based TRNG; their original contribution is area reduction, scalability, portability to different platforms, and bridge between circuit and system. Quality of bitstream from TRNG is passing on the NIST test suit and DIEHARD test suite. RO PUF implemented with Xilinx's Spartan 3S500E series FPGA with 32 and 64-bit rising oscillators. RO PUF response is 42.8 % unique and 80.6 % reliable; it observed that with the high number of R.O. stages, uniqueness and reliability start to decreases. An XOR gate controls the circuitry giving 3.2 MBPS truly random bits and 32-bit unique device signature.

In paper [32], Kong et al. (2013), low power and smaller circuits for device authentication, which size PUF compact. The threshold voltage variation of nmos and pmos is, and the temperature co-efficient of threshold voltage significantly improves the stability of silicon PUF. The different architecture of inverter with different width size enhance the reliability of PUF. Technology dependent PUF with CMOS 90nm and 45nm response tested with NIST test suit. Leakage current based PUF used leakage sensor; the output of each sensor is identical, but process variation includes a slight change into the PUF response. CMOS 90nm SPICE with Monte Carlo simulation analyses with 2000 chip instance, leakage PUF score 60% reduction and power, and 84% reduction in area, 35% improvement in temperature stability compare to RO PUF.

In paper [33] by Maiti et al. (2013), transient effect based ROPUF has proposed. The design, evaluation, and optimization of the ROPUF transient effect. The temporary impact of the ring oscillator during start-up adds more randomness and generates response more reliable than ROPUF. Response generation scheme with TERO PUF tested on 30 chips with CMOS 350nm process technology in a nominal corner and voltage temperature condition. TERO PUF is focused on optimize performance and reduce area without noticeable loss in output. An additional balancing block extract high-level entropy. TERO PUF can generate several response bits from the same circuit; TERO PUF causes a unique response by extracting oscillation from TERO. Uniqueness involved in producing responses is 49%, steadiness 5%, and Randomness 99%.

In paper [34] by Shaza et al. (2015), PUF design is presented with the unique feature if remanence decay. Non-volatile memory used to store the binary value for a long time; remanence is the property that measures the channel in the stored information with time due to decay or leakage or environmental conditions. Here 8KB SRAM array PUF proposed as lightweight security primatial at CMOS 65nm technology. SRAM PUF has a countermeasure against side-channel attack used remanence decay to improve cloning resistance o SRAM PUF. To generate stable high response voltage remanence 44.82% and time remanence 43.455. Similarly, log logic response voltage remanence 45.14% and time remanence 41.86%.

In paper [35], Herder et al. (2014), PUF broadly classified as weak and robust PUF; strong PUF can generate secret key while weak PUF response process through errorcorrecting code. Author have Implemented arbiter, ring oscillator, and SRAM based PUF in CMOS 180nm technology. According to the application, it Classifies PUF as a string and weak PUF. A strong PUF suitable for secured authentication and weak PUF uses for cryptographic key generation. A weak PUF requires a small number of CRP and exploits the manufacturing variation while strong PUF requires a large number of CRP.

Additionally, error correction schemes on the PUF response used to produce stable and reliable answers. The author has tested the different topology of PUF like optical PUF, Arbiter PUF, and RO PUF. Obtained PUF response inter and intra variation is 6% and 5% respectively at temperature range -25 to 85C. PUF is resistant to training attacks since it is challenging to measure the internal hardware parameter, testing to clone, challenging to predict the past CRPS.

In paper [36] by Meguerdichian (2011), A new design of dynamic physically unclonable functions (DPUFs) proposed whose physical properties are subject to unpredictable changes between uses. Here device ageing adapted because it provides rapid and lowenergy customization and exhibits fast reversibility since. Here the author has proposed numerical algebra technique for reverse engineering. Cad tool ages model based on negative bias temperature instability (NBTI) and hot carrier injection (HCI) where selected hardware features for PUF non-linear function decay with time. Pair of a module under ageing effect show variation, based on a variation arbiter decode to generate a response of logic one or logic 0. To include attack countermeasures, a series of buffer to be added. Dynamic PUF has high unpredictability and can quickly stabilize.

In paper [37], Zouha et al. (2012) method that allows evaluating a silicon PUF, based on delay elements, at the design stage without the need to have the circuit. The essence of the way based on a Monte Carlo (MC) simulation of the netlist that considers the process variation and the environment. Evaluation of PUF is an open problem different parameter is analyzed. Randomness derived from maximum entropy. Uniqueness says two PUF must have a different response of the same challenge and reliability say response bit not be affected by the environmental and operating condition—arbiter PUF designed with HDL and simulation results based on Cyclone II FPGA. To be validated, this method compares the simulation results and measurements on silicon, showing that arbiter PUF has a uniqueness of 97% and seediness of 99%. Loop PUF utilizes the delay chain, the odd number of cascaded structures like ring oscillator follow by frequency measurement device achieves uniqueness 95% and steadiness 98.7%.

In paper [38], Pegu et al. (2015) multiplexer PUF based non-linear and unique response for each challenge input by taking advantage of an uncontrollable intrinsic random feature of the integrated circuit during manufacturing variation. This paper presents the well-experimented analysis of the different MUX-based PUFs based on layout-based simulation performed in CMOS 50nm.rul—using Microwind and DSC2.7 tools. A comparison of the various topology of MUX based arbiter PUF presented. The feedforward structure of mux PUF enhances the nonlinearity in mux. MUX PUF gives the reliability 88% uniqueness 79% and randomness 86%. Inter and intra chip variation with the different condition is 11% and 9%. A feedforward structure increases nonlinearity and decreases errors caused by environmental conditions. MuxDmux PUF selects the direction of the propagation signal and implements reconfigurable PUF.

In paper [39] by Ozturk et al. (2008), delay-based PUF based on intrinsic process variation and random switching by input challenge that implements the pseudo-random

function. In addition to logic 1 and 0 tristate have 3rd stage as high impedance (Z). IF the gate is not enabled output is tri-states, A tristate delay unit implement with BUF0 and BUF1 stage when letting the same input pass since the delay of BUF0 and BUF1 is the different response time of tristate buffer is different. The tristate barrier is similar to arbiter PUF, where the inverter substituted with tristate buffer Delay of BUF0 is higher than BUF1 due to addition invert gate. A mathematical model can compute the response time for output. Synthesized result-based ion TSMC 130nm technology library shows at 100MHz mux PUF require 193.67 $\mu$ W and tristate PUG require 152.93 $\mu$ W with 49 units of reduction in getting counts.

In paper [40] by et al. Hussain(2014), an online test evaluation for testing quality metrics, i.e., NIST test, Diehard test, Dapra Shield test. BIST-PUF enables the on-the-fly assessment of the desired PUF properties, all in hardware predictability and stability. BIST PUF has its response generator integrated with a test suite. An online assessment tool developed to report quantitatively and to evaluate PUF stability and unpredictability. BIST PUF assesses by three different methods sensor-based, parametric interrogation, and multiple interrogations. A high entropy TRNG includes BIST PUF to exclude the biases in challenge generation. Stability tool removes the requirement of error correction logic, Xilinx Vertex-5 based FPGA implement power requirement of BIST PUF are 18.92mW.

In paper [41] by Yao et al. (2013), new PUF techniques can extract secret from pairwise skews between sinks of a clock network. These techniques acquire the stability of the clock network to acquire unique chip signatures from process variations. The clock network implemented in CMOS 45nm technology node. On-chip clock network builds resilient to attack; tunable delay enhances the entropy of clock PUF. Algorithmic selection of pairwise comparison performed by multiplexors, the inclusion of return oath minimizing the routing congestion. SPICE simulation measure as Inter and Intra hamming distance verify on performing Monte Carlo analysis with 1000 key. PUF arrangement shows inter-Hamming distances ~50% as desired. Reproducibility is

responses ensure the response is independent to  $\pm 10\%$  in voltage and  $-20^{\circ}$ C to  $120^{\circ}$ C temperature. Compare to the ROPUF clock, PUF has a 2-time higher reproducibility.

### 2.5.2 Literature Review of Power Attack Analysis

In paper [42] by Mestiri et al. (2013) number of power traces necessary to guess the key of AES SBOX with the SASEBO-GII board has experimented. This board comprises cryptographic FPGA and control FPGA supports HDL programming language. Power trace to compute output plotted on to CRO. Here the relation between actual power and predicted with hamming weight power model or hamming distance power model and switching distance exploits to implement CPA attack. Here the author has focused on how many power traces are required to ascertain each byte of the correct key. Based on 4000 traces correlation coefficient between actual and estimated model 10th key can distinguish. The switching distance model requires less power to guess the correct key successfully compared to the Hamming distance model. H.D. and S.D. model shows a high degree of approximation at corresponding key; 1<sup>st</sup> pivotal HD 5.7 SD 5.6, 4<sup>th</sup> key HD 6.1 SD 6.5, 8<sup>th</sup> key SD 8.5 HD 11, 12<sup>th</sup> key SD 4.4 HD 5 and 16<sup>th</sup> key SD 9.3 HD 9.3. In the paper by [43] by Takeshi Fujino et al. (2017) power consumption pattern linearly depends on the number of switching bits at the input of the cryptomodule. Authors have reviewed various countermeasures against side-channel attacks. A countermeasure cell does not reveal hidden circuit information under a power attack; it provides the random or constant power for inputs. Attack resistant cell shows a notable increase in circuit area and power dissipation. SBOX implementation with Threshold implementation and HMDR-ROM shows excellent resistance to side-channel attack, but area increase by five times and power 15 times in case of T.I. and 6% and 20% for HMDR-ROM. MDR ROM based SBOX implementation shows the constant ability to fetch substituted byte from memory.

In the paper by [44] by Massimo Alioto et al. (2014) have explained the effectiveness of power attack countermeasures to leakage power described by Leakage power in the CMOS circuit is unavoidable. The effectiveness of leakage power analysis to implement

differential power attack (DPA) and their countermeasures. Leakage power is smaller but unique for each input, here the author tries to recover key of the crypto module by analyzing the leakage power consumption. Total leakage current is a combination of two distinct currents; the first part of the current depends on the hamming weight of both text input and round key applied on add round key. The first part of the current linearly increases the number of high bits, and another part of the current is a constant leakage current. The coefficient of correlation shows the probability of successfully guessing the correct kay. CMOS architecture of innate cells such as WDD, SABL, MDPL can achieve a smaller value of relationship but increase the area.

In the paper by [45] by Junrong Liu et al. (2010)have shown correlation power analysis is a useful technique to predict secret from cipher by analyzing H.W. and H.D. is the two most preferred models to apply correlation power analysis (CPA) with steam cipher MICKEY v2. H.W. model map the presence of the number of high bits at the output and H.D. model map the number of transitions occurring at the input with power consumption in the actual model. Assumption follows to model the estimate; the model is the power consumption for load capacitor charging when output changes 0-1 and discharging for production 1-0. No power consumption occurs for 0-0 and 1-1 transitions. The limitation of the Hamming weight model is it can recover the key more effectively. For k=0 and 1 correlation effect in -0.43 and 0.4 respectively, the power consumption follows inverse relation to the hamming distance. Here authors describe that only ten power trace requires the difference between k=0 and k=1.

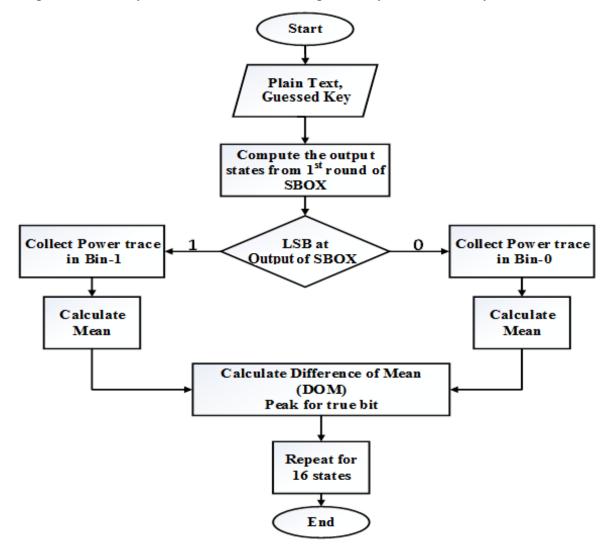

In paper [46] by Eiric Brier (2004) have a mathematical model of DPA and CPA. CPA and DPA are two commonly used power attack analyses to evaluate the crypto module's side-channel analysis. DPA attack relies on the difference between the mean value of power trace at input LSB 0 and LSB 1. At the same time, the CPA utilizes the correlation coefficient to measure the relation between estimated power and actual power. Here the author exposed the defect in the former approach of differential power attack and presented a mathematical model of correlation power attack. The CPA model finds a correlation between a power consumption pattern and the number of high bits to an input of SBOX. Limitation of DPA attack is a DPA attack that shows a ghost peak, whereas the CPA attack presented as the higher value of the correlation coefficient. CPA attack applied in the first round of 8 SBOX with only 40 power traces. The maximum amount of correlation achieves for the first SBOX is 92% and a minimum of 65%. Compare to CPA, DPA requires more sample power traces. Even partial correlation still provides an exploitable indication of attack analysis. CPA must require reverse engineering (leakage rate) on known data.

In paper [47], Satok et al. (2001) present a methodology to retrieve a key from cache memory between processor and memory system. Cache memory uses in the novel process sharing scheme in a cryptographic algorithm. Lookup table-based SBOX exhibits the cache resistant feature; since each time slice provided b victim is tiny gives a limited number of table access while accessing the table if available byte cache hit else cache miss. After cache miss flush and loading new byte required. This information used to exploit the side-channel attack. The author in [47] has demonstrated the side-channel attack (SCA) base on the recent data available in cache memory as hit or miss. Requirements of large-sized cache memory highlighted if the victim has up to 60 cache access open can develop an analytic model to develop leakage model. Cache attack can recover a full 128-bit AES key using 5-7 encryption or decryption.

In paper [48] by Cecile Canovas and Jessy Clediere(2005) have classified power attack as DPA, DEMA, and CPA. DPA and CPA use the leakage power information at the SBOX, while DEMA is based on electromagnetic radiation while a module performs computation. A capture probe requires the collection and process of the E.M. radiation for each input to the SBOX. DPA and DEMA exhibit the wrong key with ghost peak, but in CPA correct key and the false key is identified as the various weighting of the correlation coefficient. CPA attack based on the hamming distance model applies to multi-bit and single-bit output of SBOX. Hypothetical model of hamming weight and hamming distance normalized with the factor of 32. Correlation value replaces the ghost peak problem and gives better classification in terms of the correlation coefficient.

Imbalance increases the wellness of the approach. These types of tests improve the rectify and relevance of SBOX architecture before the actual test.

In paper [49] by Davide Bellizia et al. (2016) exploited the dependency of the static current of the submicron CMOS device with internally processed data. Power attack can recover the secret key by the univariant attack, by statistically quantifying the relation between actual leakage current and leakage model. Countermeasures of power attack are WDDL, MDPL, SABL shows hiding the information into power trace or randomized the power such that equal power paternal for different input. A new type of power resistant logic is time-closed logic (TEL) into dynamic CMOS logic implementation. The security level s measured as a function of the data path and CMOS technology, and it is independent of the clock signal. The evaluation person s set to 10ps, which is lower than predicted settling time of transient time. Thus, the attacker does not get sufficient time to collect the power trace.

In paper [50] by Y.J. and Noh, M.J. (2005) presents a survey report on differential power attack and their countermeasures as masking. Leakage power is the source of power attack analysis since power value is related to input data. The power trace of the masked cell does not follow the linear relation with input. Masking based on a regular Boolean logic gate such that power consumption value does not depend on the primary data rather than distributed in the internal stage of the circuit. Information is masked with random bit and output bit in again unmasked i<sup>th</sup> another set of the random bit. A combination of logic gate arranged such that final output unaffected; Here, the author has tested 4-bit ripple carry adder and AES, SEED, and SHA function with mask gate. Masking increases the gate count and critical path delay. AES with masked SBOX increases gate count from 17.4K to 25.9K.

In paper [51], Owen Lo et al. (2017) implemented a DPA and CPA attack on SBOX output. DPA attack presents the difference between the mean value of power trace for LSB1 and LSB0. A peak in the differential curve is identifying the correct key while the wrong key presented ad ghost peak. CPA attack utilizes a Pearson correlation value easy to interpret, Power trace storage setup developed with Arduino uni, key-sight

oscilloscope, probe, and data analyzing machine. Limitations of DPA are the availability of open-source code of cryptographic libraries that capture the power trace in real-life devices during operation. By selecting the exact attack point for DPA and CPA, one can predict the output of the AddRroundKey for the given plain text. For correct guess, one can have the original secret key.

In paper [52] by Saravanan P and Kalpana P.(2015), the XOR gate's importance is presented in the encryption process. CMOS based XOR gate is vulnerable to power attack. The security level of XOR gate measures as non-leakage on information along with power trace shown by Here, the author has proposed a new architecture of the XOR gate with charge sharing option in adiabatic logic. NED and NSD are two energy-based parameters present power attack resistant features. NED measured as a percentage of the difference between the minimum energy and maximum energy, and NSD is deviation into energy for input plain text. NED-NSD value of different existing architecture of XOR like CPL, DCSVL, Adiabatic, SABL, SyAL, CSSAL shows that reduction into NED and NSD but in increases the gate count and power consumption. The proposed XOR gates saves energy 79.6% and 82.5% concerning SyAL and CSSAL XOR gates, respectively, and shows a reduction in NED by 20.8% and 1.6% and NSD by 26.1% and 91.1% compared to SyAL and CSSAL. Limitation exhibits in area requirement show 409.1% and 463.6% concerning the SyAL XOR gate and CSSAL XOR gate, respectively.

### 2.5.3 Literature Review of Power Attack Countermeasure

In paper [53] by Lu Zhang, Luis Vega, and Michael Taylor (2016) have implemented a Power model to verify DPA and CPA attacks over the crypto module and their countermeasures. CPA attack performed with a hamming distance using a power consumption pattern with the change of high bits in the input. At the input data of CMOS circuit change of bit 0-0 and 1-1 does not consume power (assumption), power trace of XOR and AND gate gave the visible appearance of input bit. DPA and CPA successfully recover the secret key with a high correlation factor. Masking is a pronounced technique to have a secure crypto module. Usage of the masked gate to implement masking at algorithm level capable of reducing correlation factor compare to without mask gate. Mask gate considered better countermeasure compare to masking logic like WDDL, RSL, SABL.

In paper [54] by Stefan Mangard et al. in 2005, it was observed that the mask gate's performance decreases with glitch; the presence of glitch introduces susceptibility to DPA attack. DPA countermeasure tries to remove to reduce correlation ultimately between actual power and the hypothetical power model. The objective of countermeasure by keeping power consumption of the CMOS circuit independent of the input pattern. A mathematical model to study the energy requirement E0-0, E0-1, E1-0, and E1-1 for output 0-0,0-1,1-01 and 1-1, respectively. The energy required to produces one is more significant, and energy needed to switch output 0 provides an opportunity for DPA attack. Attack implementation of a mask gate requires a 45\*16 power trace compare to 25\*16 on a standard gate. Mask gate not only makes the computation difficult to modifies the shape of the differential curve of mean in DPA analysis.

In paper [55] by Maneesha Jayakumar (2018), the efficient architecture of mask AES engine are resistant to DPA attack. A Boolean asking approach is applied to implement masking of the AES algorithm. The boolean equation of each component of AES given as a present logic gate-based schematic. SBOX is considered the most sensitive point on the encryption process, masking applied at the input and output of SBOX. Masking a methodology to change the input of SBOX by XORing with the random bit, the output of SBOX masked must be unmasked with another set of the random bit. The random bit at input and output of SBOX used for masking must be related such that the final production of SBOX should be as expected to unmasked data. Power trace of masked SBOX and unmasked SBOX must be different from each other. FPGA implementation of unmasked and masked AES shows the delay is 36.886 nS, and the memory requirement is 342.532 Mb.

In paper [56] by Tiri, Kris et al. (2005) have analyzed power resistant logic styles to prevent DPA attacks are SABL; WDDL and TDL are focused on random charging-

discharging of load capacitor. Minimized energy technique SBOX based on adiabatic charging proposed in this work. The energy required to charge low to high transition is  $2(R/_{tp})C_LVDD^2$ , adiabatic pre-charging, and evaluation change the power trace. The technique to make output power independent of input bits are; charge sharing symmetric adiabatic logic SBOX provides balanced output power for each transition. eCSSAL SBOX achieve Emin 4.85pJ Emax 5.87pJ at 50MHz. DPA resistant adiabatic charging discharging achieve NED NSD are 3.7 and 0.65% at 50MHz.

In paper [57] by M. Masoumi(2019) have implemented an efficient architecture of AES based on a modified Boolean masking scheme without adding area overhead. A classical randomized table included breaking the correlation between actual power and mathematical power model—the difference between the ability to compute outputs 0 and 1, identified as Welch's t-test. The XORed output of the add-around key stage is applied to SBOX to find a substitutable byte and mask table. The mask table is 16\*16 matrix contains a unique mask value for each XORed output. At output SBOX output and mask, value is again XORed together to find unmasked output. The outcome of the paper found as; affine transform shows a 300% increase in area 60% decrease in speed.

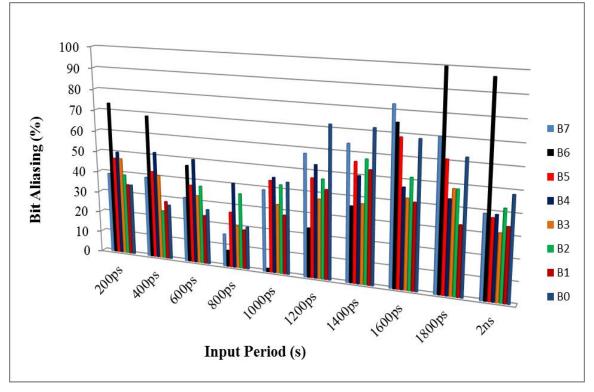

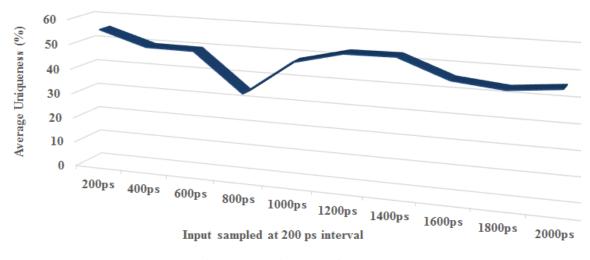

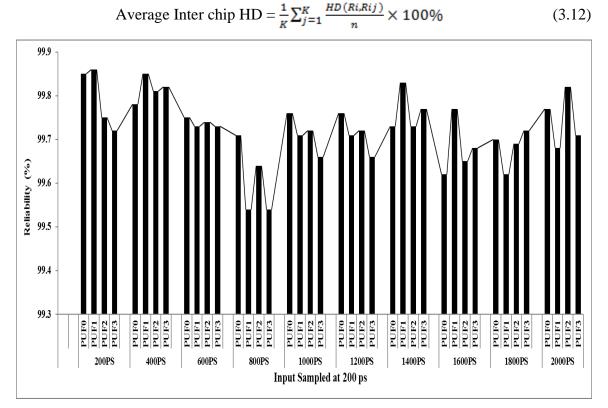

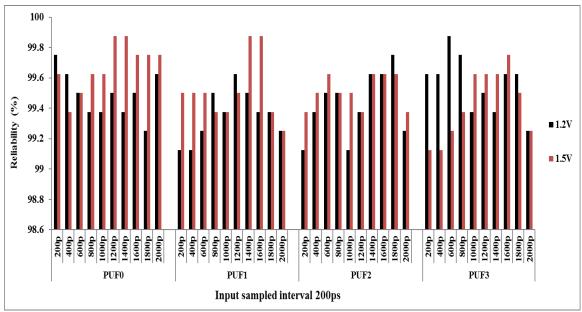

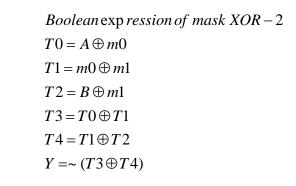

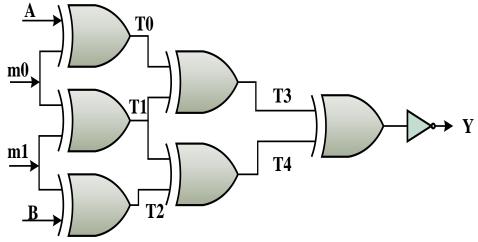

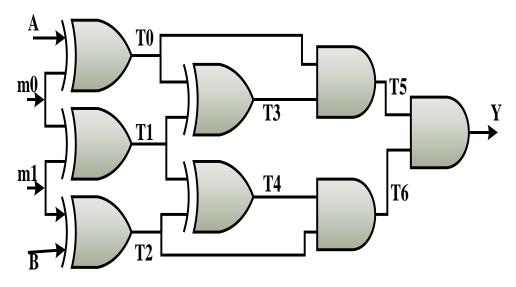

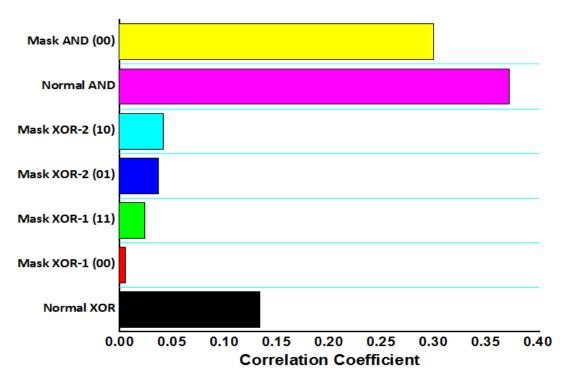

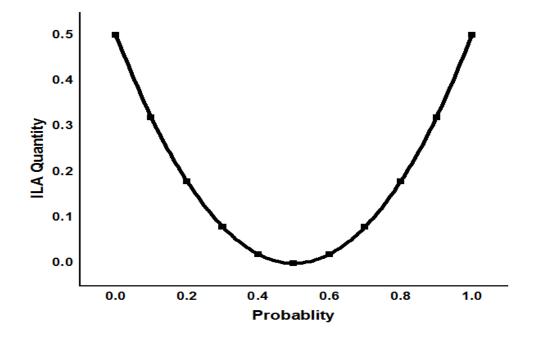

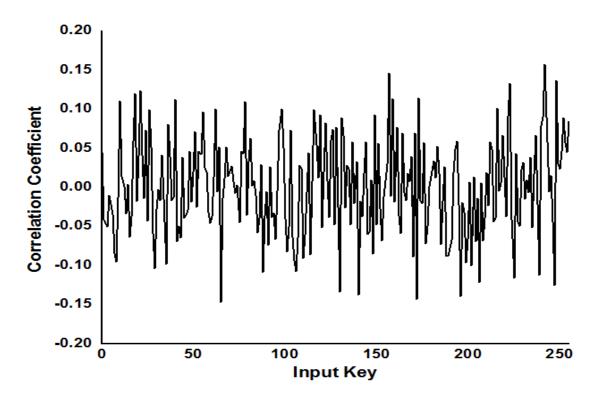

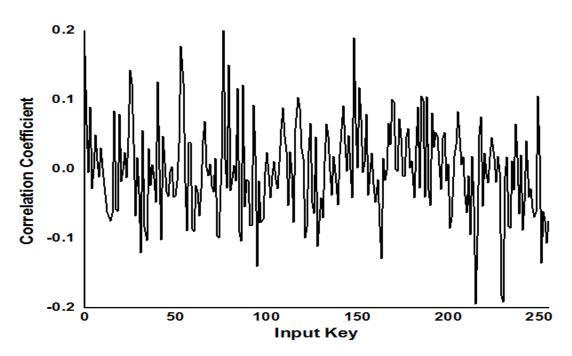

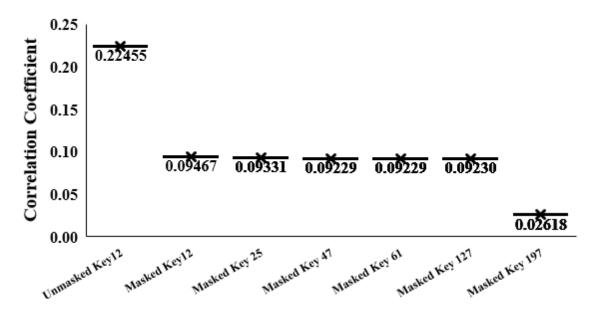

In paper [58] by Tena-Sanchez et al. (2014), cryptanalysis is a technique that explained to find hidden secrets by a third-party power attack with the correlation between power and input such that resistance to DPA attack. Limitation of mask logic style presented, such as; SABL sensible to unbalanced output, SyCML shows reduced swing, TDPL generates an additional control signal, DDPL needs an additional inverter. Here, the author has modified ht pull-down criteria during the precharge and evaluation phases with single and double switch implementation. It reported that for AND gate improvement in NED value during precharge 0.17% with a single switch 35.15% with double switch, in NSD 10.9% with a single switch and 27% double witch switch. Improvement in NSD value during evaluation 32.95% with single switch 157.17% with double switch, in NSD 35.08% with a single switch and 53.05% double witch switch. During the evaluation phase, XOR / XNOR architecture requires the energy of 1.28 times and 1.02 delay 1.14time and 102times for double and single switch pull-down compared to classical implementation.