# VLSI ARCHITECTURE FOR HIGH LEVEL TRANSFORMATION ON HARDWARE SECURITY WITH AUTHENTICATION AND OBFUSCATION

Thesis Submitted for the Award of the Degree of

# **DOCTOR OF PHILOSOPHY**

in Electronics and communication engineering

> By Jyotirmoy Pathak 41500072

## Supervised by Dr. Suman Lata Tripathi (21067)

School of Electronics and Electrical Engineering (Professor)

Lovely Professional University

Transforming Education Transforming India

LOVELY PROFESSIONAL UNIVERSITY PUNJAB 2022

#### **DECLARATION**

I, hereby declared that the presented work in the thesis entitled "VLSI Architecture for high Level Transformation on Hardware Security with Authentication and Obfuscation" in fulfilment of degree of **Doctor of Philosophy (Ph. D.)** is outcome of research work carried out by me under the supervision of Dr. Suman Lata Tripathi, working as Professor, in the School of Electronics and Electrical Engineering of Lovely Professional University, Punjab, India. In keeping with general practice of reporting scientific observations, due acknowledgements have been made whenever work described here has been based on findings of other investigator. This work has not been submitted in part or full to any other University or Institute for the award of any degree.

Jyotirmoy Pathak 41500072 School of Electronics and Electrical Engineering Lovely Professional University Punjab, India

### **CERTIFICATE**

This is to certify that the work reported in the Ph. D. thesis entitled "VLSI Architecture for high Level Transformation on Hardware Security with Authentication and Obfuscation" submitted in fulfillment of the requirement for the reward of degree of **Doctor of Philosophy (Ph.D.)** in the Electronics and Communication Engineering, is a research work carried out by Jyotirmoy Pathak, 41500072, is bonafide record of his/her original work carried out under my supervision and that no part of thesis has been submitted for any other degree, diploma or equivalent course.

### (Signature of Supervisor)

Dr. Suman Lata Tripathi Professor School of Electronics and Electrical Engineering Lovely Professional University

### Abstract

In addition to miniaturizing, today's technologies are also getting more and more linked to one another. The aggregate name for these connected, smart devices is "Internet of Things" (IoT). High-speed wireless sensor nodes, consumer electronics, and life-saving systems like implantable and medical devices are just some of the IoT applications already in use. Low-cost, high-efficiency, and high-security algorithms must be implemented on the most resourceefficient platforms for the devices used in these applications. The ever-changing nature of the application landscape necessitates fresh architectural mappings and design methodologies that go beyond conventional optimization. This thesis focuses on developing hardware architectures that can deliver robust end-to-end security and low-cost, low-energy solutions through the use of Application-Specific Integrated Circuit (ASIC) designs and Field Programmable Gate Array (FPGA) implementations. The proposed layouts are meant to provide safe semiconductor circuit production.

There are limitations on power, space, and safety that must be met in order to perform complex compute functions. Leakage current also exposes sensitive information through unavoidable side channels. The side-channel analysis suggests that attackers can uncover secret information by monitoring leakage, which remains linked to processed data. Data has a role in determining how much dynamic power CMOS devices have. Variations in high bits and bit position shifts cause power traces to sway.

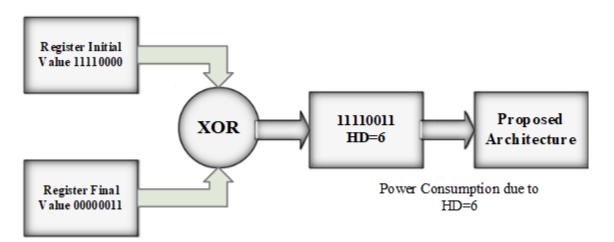

For secure production, hardware obfuscation layouts are proposed. Hardware security has become more important over the past decade in response to reports of counterfeit gadgets detected in life-or-death military systems. In the next phase of the Internet of Things, when more devices are built and connected to a common network, the demand for security will increase. The goal of hardware obfuscation is to make circuits more secure by hiding their intended purpose and protecting them with secret keys before sending them off to be manufactured. Those without the correct secret key will be unable to decipher or use the circuit thanks to this technology. After acquiring the chips from questionable manufacturing facilities, they are encrypted and sent to end customers for verification of reliability. The development of novel structures and obfuscation techniques is the major focus of my research. The suggested design uses both traditional CMOS components and a newer type of CMOS logic known as a "hybrid" (Transmission gate (TG) and pass transistor (PTL) logic). While there is no way to completely stop information from leaking out, tools like normalized energy deviation (NED) and normalized standard deviation (NSD) can help keep leaks to a minimum. The use of (TG+PTL) logic in design implementation has resulted in a 48.64% reduction in NED and a 21.8% reduction in NSD compared to static CMOS. By seeing the relationship between the amount of power used by the cryptographic block and the intermediate result, an adversary might speculate on the data that will be processed in the subsequent step. Based on statistical analysis, the most important side-channel assaults are differential power analysis and correlation power analysis. Examining input data and power usage trends using the Pearson correlation coefficient ( $\rho$ ). If " $\rho$ " is large and positive, then the power pattern and the processed data are highly correlated.

A cell that is impenetrable to assault would forget its prior connections to the data it processes. The resilience of the CMOS cell is investigated as part of the power attack countermeasure in order to provide protection against power analysis assaults. Hiding and masking are two common types of attack-resistant qualities, and they work together to shield the device from a power attack. During the course of our investigation, we made use of a boolean masking approach to produce the intermediate data in a random fashion. An intermediate value is masked in the architecture that has been proposed by making use of a random mask bit and extra cells. The output is then unmasked by making use of either the same random bit or a new random bit that has been derived from the first random bit. Cell-level masking can be used to make the cell's design more power-efficient and less sensitive to the data being fed into it. Here we see mask XOR and mask AND cells, whose true power consumption is demonstrated to be the same regardless of which internal node serves as the output. Since power is dependent on each internal node, and attackers cannot surmise information by seeing only the output node, the truth table approach ensures that the hammering weight of each internal node is dispersed evenly. Static power is increased by 84.4%, dynamic power by 77.8%, and latency is reduced by 164.8% when compared to a design without a mask cell. When compared to previously published work, the present design's use of Boolean masking at the cell level reduces the necessary gate count to 2173. There is an implication of independence between power consumption pattern and processed data when using the hammering weight power model, which

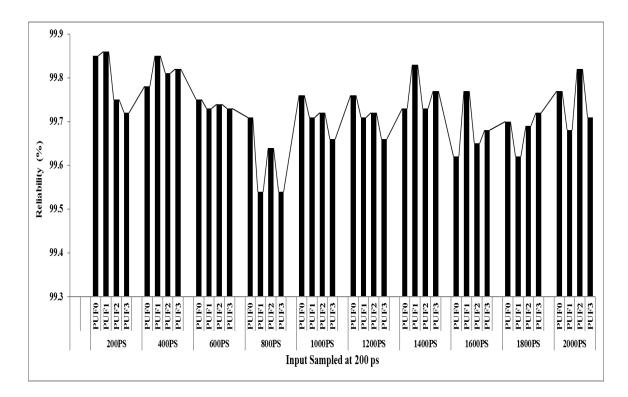

decreases the correlation coefficient between real and estimated power by 32.17 percent, and when using the hammering distance power model, which reduces the correlation coefficient by 26.65 percent. In Mask, the random number is merged with the input from the cells; however, the software used to produce the random number is not truly random and will cycle back after a fixed amount of iterations. One of the forthcoming hardware security modules is the response of a physically unclonable function to a challenge input and device/specific feature. For the purposes of constructing a physically unclonable function (PUF), a silicon-based device in which each of the circuit generates a distinct response is desirable. The delay and hysteresis bandwidth of the circuit determine the response of the Schmitt trigger PUF (STPUF). The given STPUF validates the parameter, with a uniqueness of 49.2%, and a reliability of 99.7% under severe operating conditions.

## Acknowledgement

I am really obliged and appreciative to the several persons that assisted me with my research and thesis preparation.

I express particular appreciation and credit to the Almighty God for granting me the intelligence and health to finish this quest.

I would like to thank my adviser, **Dr. Suman Lata Tripathi**, professor in the School of Electronics and Electrical Engineering, for her guidance, support, and counsel throughout my Ph.D. programme. Her patience in providing me with comments over the years and her support for my work have helped me become a better researcher and complete my thesis effectively.

It is a joy to be obliged to the numerous individuals who directly or indirectly contributed to the production of this work and who inspired my thinking, conduct, and actions over the course of this research. I am quite grateful to my colleague and friend for their insightful advice.

I would like to express my appreciation to the School of Electronics and Electrical Engineering at Lovely Professional University for providing me with a conducive atmosphere for doing research.

Nobody has been more significant to me in my pursuit of this topic than my family members. I owe my parents, my siblings, and my in-laws profound gratitude for their love, drive, support, and wisdom when it was most needed. Importantly, I owe a great deal to my ever-supportive and caring wife, **Dwaraka Niranjana Pathak**, who has supplied me with continuous emotional and mental motivation. Always at a loss for words, I found it hard to articulate her support in words.

**Jyotirmoy Pathak**

# **Table of Content**

| DECLARATION          | (ii)   |

|----------------------|--------|

| CERTIFICATE          | (iii)  |

| ABSTRACT             | (iv)   |

| ACKNOWLEDGEMENT      | (vii)  |

| TABLE OF CONTENTS    | (viii) |

| LIST OF TABLES       | (xi)   |

| LIST OF FIGURES      | (xii)  |

| LIST OF ABBREVIATION | (xv)   |

## 1. Introduction

| 1.1 Overview                | (1) |

|-----------------------------|-----|

| 1.2 Research's Contribution | (7) |

| 1.3 Outline of Thesis       | (8) |

## 2. Literature Review

| 2.1 Hardware Security Module (HSM)                                         | (9)  |

|----------------------------------------------------------------------------|------|

| 2.2 Physically Unclonable Function (PUF) as Hardware Security Module (HSM) | (10) |

| 2.3 Obfuscating DSP Circuits via High Level Transformation                 | (10) |

| 2.4 Side Channel Information                                               | (11) |

| 2.5 Literature Review: Categorization                                      | (12) |

| 2.5.1 PUF Literature Review                                                | (12) |

| 2.5.2 Literature Review of Obfuscation Technique                           | (20) |

| 2.5.3 Review of Literature on Power Attack Analysis and Countermeasure     | (45) |

| 2.6 Research Gap                                                           | (58) |

| 2.7 Objective                                                              | (59) |

## 3. Secret Key Generation

| 3.1 Introduction                             | (60) |

|----------------------------------------------|------|

| 3.2 Classification of PUF                    | (61) |

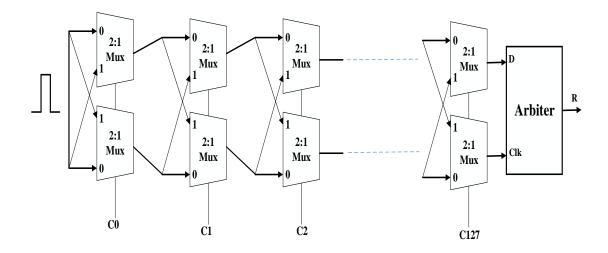

| 3.2.1 Arbiter PUF based on Delay             | (62) |

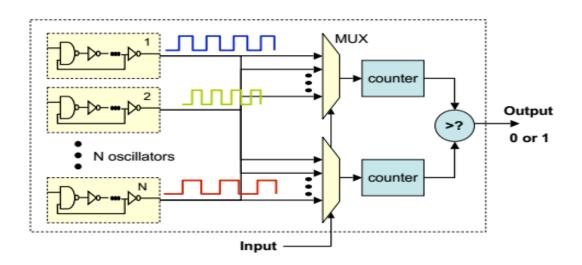

| 3.2.2 Ring Odcillator PUF based on Frequency | (64) |

| 3.2.3 SRAM PUF based on Initial Value        | (65) |

| 3.3 Schmit Trigger PUF                       | (66) |

| 3.3.1 Different Topology of Schmitt Trigger  | (71) |

| 3.3.2 Arbiter                                | (76) |

| 3.3.3 Schmitt trigger PUF                    | (77) |

| 3.4 Result & Discussion            | (80) |

|------------------------------------|------|

| 3.4.1 Inter-PUF Variation          | (81) |

| 3.4.2 Intra-PUF Variation          | (82) |

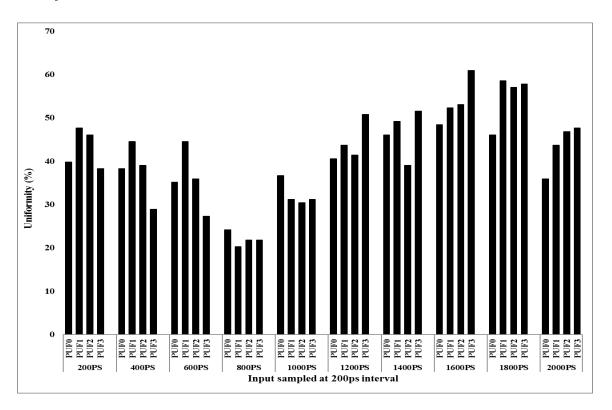

| 3.4.3 Uniformity                   | (82) |

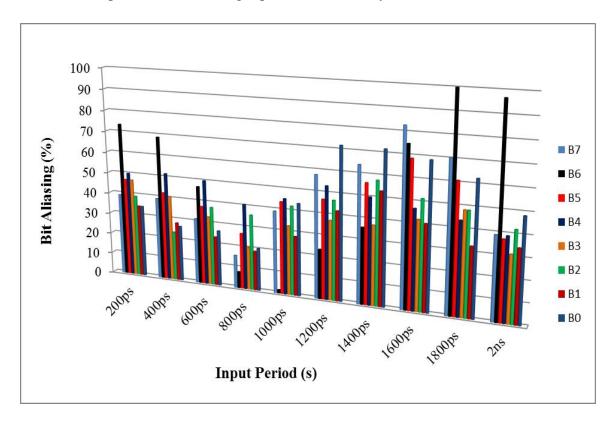

| 3.4.4 Bit Aliasing                 | (83) |

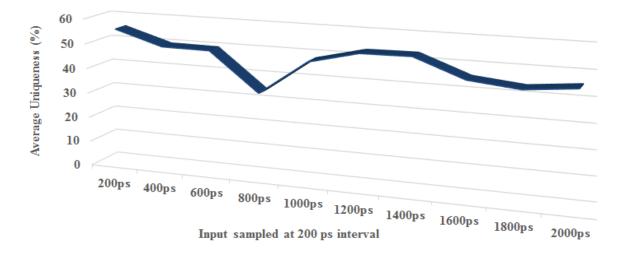

| 3.4.5 Uniqueness                   | (85) |

| 3.4.6 Reliability                  | (85) |

| 3.5 Proposed PUF Evaluation        | (88) |

| 3.5.1 Authentication               | (88) |

| 3.5.2 Secret Key Generation        | (89) |

| 3.6 Applications of PUF            | (90) |

| 3.6.1 PUF based Authentication     | (90) |

| 3.6.2 Cryptographic Key Generation | (91) |

## 4. Mode Based Obfuscation

| 4.1 Introduction                                           | (93)  |

|------------------------------------------------------------|-------|

| 4.2 Iteration Bound                                        | (96)  |

| 4.2.1 Longest Path Matrix Technique                        | (96)  |

| 4.2.2 Proposed Algorithm                                   | (99)  |

| 4.2.3 Comparison with LPM Technique                        | (105) |

| 4.3 Obfuscation Methodology                                | (106) |

| 4.3.1 Folding Transformation                               | (106) |

| 4.3.2 Modification to control flow for Obfuscation         | (107) |

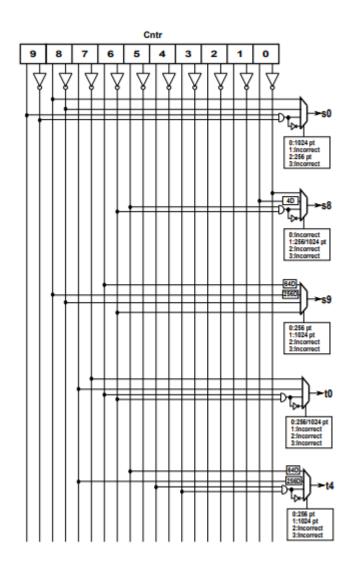

| 4.3.3 Time Varying and Dynamic Sequentally Triggered Modes | (110) |

| 4.4 Complete Design                                        | (112) |

| 4.4.1 Meaningful and Non-Meaningful Modes                  | (112) |

| 4.4.2 Trigger Circuits                                     | (115) |

| 4.5 Anaysis of Obfuscated Modes                            | (118) |

| 4.5.1.Attack Model                                         | (118) |

| 4.5.2 Obfuscation of Control Flow                          | (119) |

| 4.6 Result and Discussion                                  | (120) |

| 4.6.1 Area and Power Overhead                              | (120) |

|                                                            |       |

## 5. Power Attack

| (123) |

|-------|

| (124) |

| (124) |

| (125) |

| (125) |

| (127) |

| (127) |

| (127) |

| (127) |

|       |

| 5.3.2 Differential power analysis           | (128) |

|---------------------------------------------|-------|

| 5.2.3 Correlation power Analysis            | (130) |

| 5.4 Power Model                             | (131) |

| 5.4.1 Power Model for Hamming weight        | (132) |

| 5.4.2 Modelling Power at a Hamming distance | (132) |

| 5.5 Experimental Setup                      | (135) |

| 5.5.1 Differential Power Analysis           | (135) |

| 5.5.2 Correlation Power Analysis            | (140) |

## 6. Defence Against Side Channel Attack

| 6.1 Introduction                       | (144) |

|----------------------------------------|-------|

| 6.2 Mask Cell                          | (146) |

| 6.2.1 Security Analysis of Unmask Cell | (147) |

| 6.2.2 Power Analysis of Mask Cell      | (149) |

| 6.2.3 Security Measures of Mask Gate   | (153) |

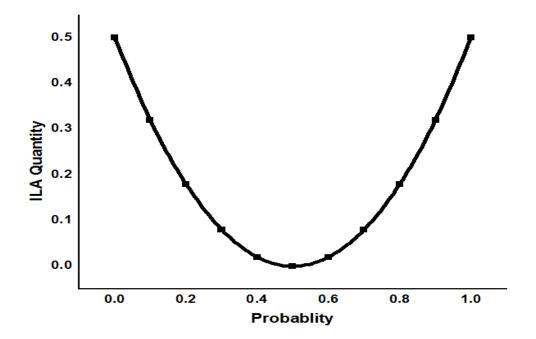

| 6.2.4 Mask cell with bias bits         | (156) |

| 6.3 Attack Model on Masked Cell Design | (158) |

| 6.4 Result and Analysis                | (161) |

|                                        |       |

## 7. Conclusion and Future Work

| 7.1 Conclusion  | (165) |

|-----------------|-------|

| 7.2 Future Work | (166) |

| Bibliography | (167) |

|--------------|-------|

|              |       |

| List of Publication | (192) |

|---------------------|-------|

|                     | (1)_) |

## List of Table

| Table 3.1 Comparison between Weak and Strong PUF                        | (62)  |

|-------------------------------------------------------------------------|-------|

| Table 3.2 Comparison of Schmitt Trigger                                 | (75)  |

| Table 3.3 Placements of Schmitt trigger circuit into row0 of PUF0       |       |

| Table 3.4 Placements of Schmitt trigger circuit into row0 of PUF1       |       |

| Table 3.5 Placements of Schmitt trigger circuit into row0 of PUF2       |       |

| Table 3.6 Placements of Schmitt trigger circuit into row0 of PUF3       |       |

| Table 3.7 Comparison of PUF's Parameter                                 | (88)  |

| Table 4.1 Comparison of Computed numbers of elements using LPM and      |       |

| Proposed Column Shifting Method                                         | (104) |

| Table 4.2 Overhead due to Meaningful Modes                              | (120) |

| Table 4.3 Overhead due to MUX in Control Path                           | (121) |

| Table 4.4 Overhead due to key size                                      | (121) |

| Table 5.1 CMOS Inverter's Power consumption pattern with respective bit | (127) |

| Table 6.1Transition energy for unmask XOR-AND cell                      | (148) |

| Table 6.2 Mask XOR-1 Cell Truth Table with Mask bit                     | (150) |

| Table 6.3 Truth Table of Mask XOR-2 with Mask bit                       | (151) |

| Table 6.4 Truth Table of Mask AND with Mask bit                         | (153) |

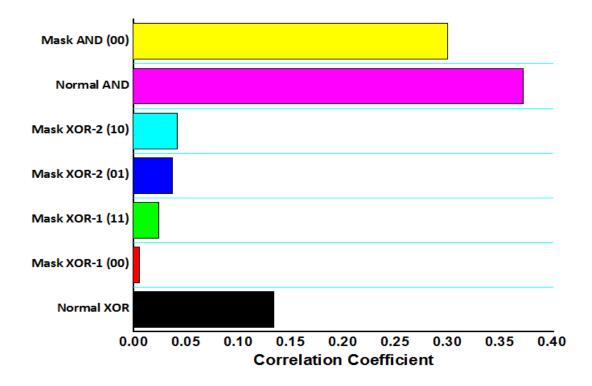

| Table 6.5 Mask gate energy correlation and energy parameter             | (155) |

| Table 6.6 Evaluating the suggested designs' topologies                  | (162) |

| Table 6.7 Evaluation of the hammering weight/distance power model's     |       |

| correlation coefficient                                                 | (163) |

| Table 6.8 Parameters of the suggested design are compared to the        |       |

| fabrication process.                                                    | (164) |

# List of Figures

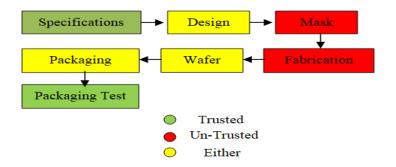

| Figure 1.1 Level of IC Design and Security at each stage       | (3)  |

|----------------------------------------------------------------|------|

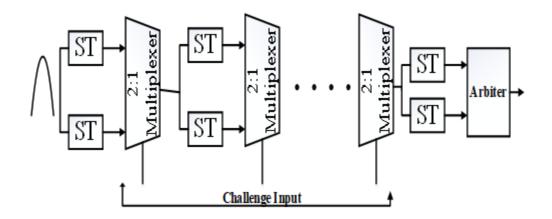

| Figure 3.1 Delay based Arbiter PUF                             | (63) |

| Figure 3.2 Frequency based Ring Oscillator PUF                 | (65) |

| Figure 3.3 SRAM PUF                                            | (66) |

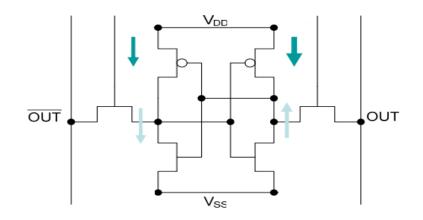

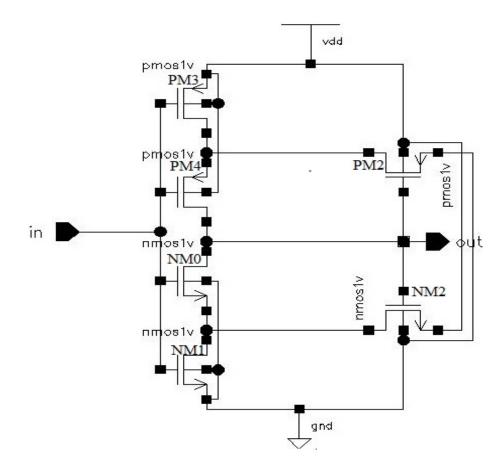

| Figure 3.4 (a) Schmitt Trigger PUF                             | (67) |

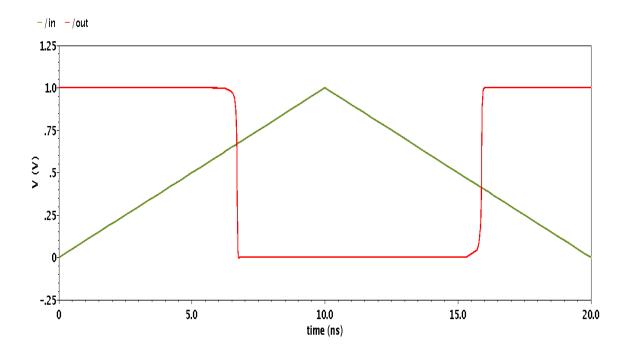

| Figure 3.4 (b) Transient response of Schmitt Trigger PUF       | (68) |

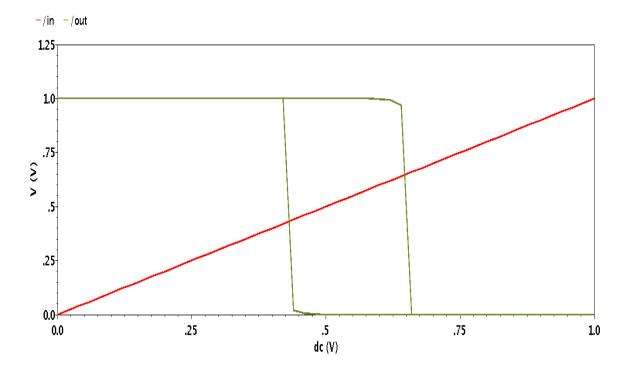

| Figure 3.4 (c) DC response of Schmitt Trigger PUF              | (68) |

| Figure 3.5 Module of Schmitt Trigger PUF                       | (71) |

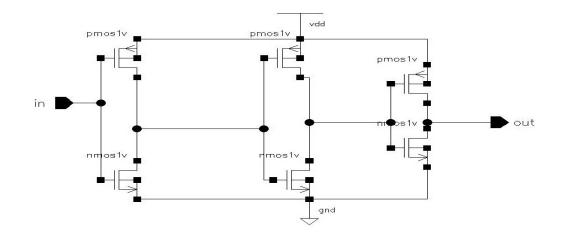

| Figure 3.6 (a) NOR based Schmitt Trigger                       | (72) |

| Figure 3.6 (b) Dual Threshold based Schmitt Trigger            | (72) |

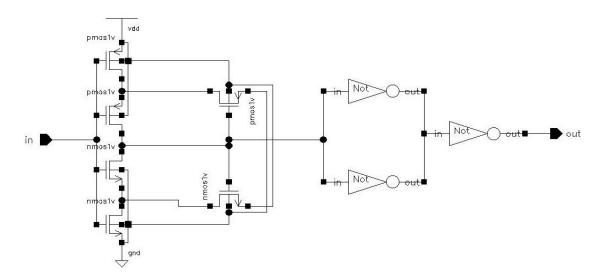

| Figure 3.6 (c) Hexadecagonal Schmitt Trigger                   | (72) |

| Figure 3.6 (d) Self Adjusting Hysteresis Schmitt Trigger       | (73) |

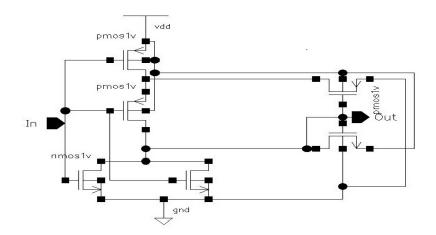

| Figure 3.6 (e) Standard CMOS Schmitt Trigger                   | (73) |

| Figure 3.6 (f) Ladder Schmitt Trigger                          | (74) |

| Figure 3.6 (g) Silicon on Insulator Schmitt Trigger            | (74) |

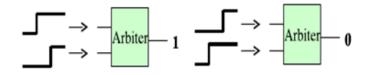

| Figure 3.7 (a) Internal architecture of Arbiter                | (76) |

| Figure 3.7(b) Response of an Arbiter                           | (77) |

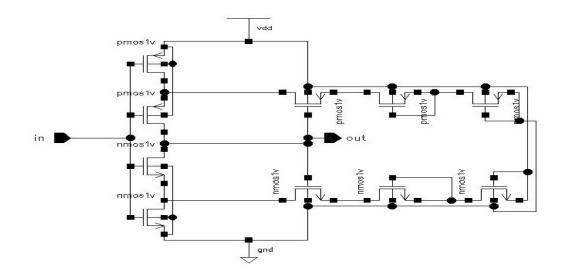

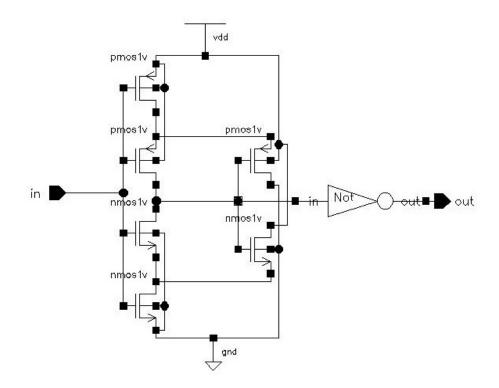

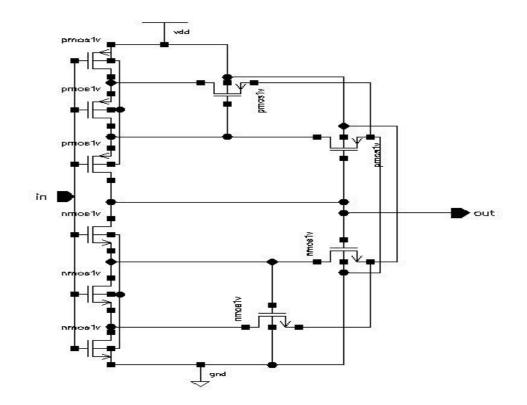

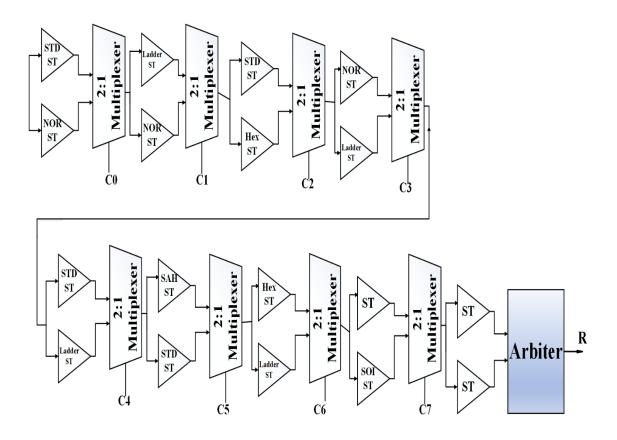

| Figure 3.8 PUF0 first row schematic                            | (79) |

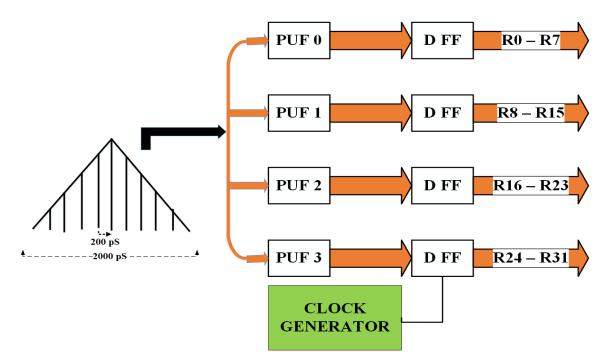

| Figure 3.9 Simulation setup for PUF                            | (80) |

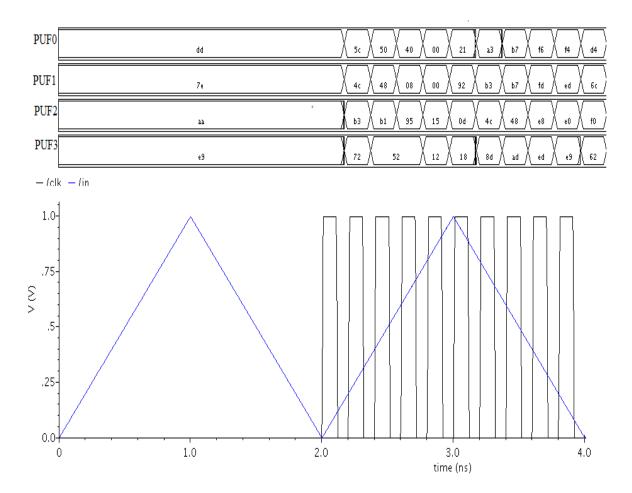

| Figure 3.10 Transient simulation result of PUF                 | (81) |

| Figure 3.11 Uniformity of STPUF                                | (83) |

| Figure 3.12 Bit aliasing of STPUF                              | (84) |

| Figure 3.13 Uniqueness of STPUF                                | (85) |

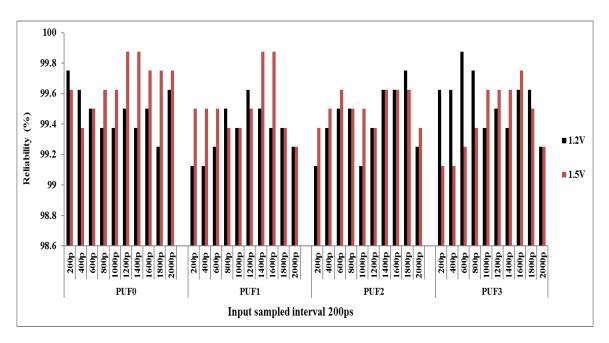

| Figure 3.14 Reliability of STPUF with temperature variation    | (87) |

| Figure 3.15 Reliability of STPUF with supply voltage variation | (87) |

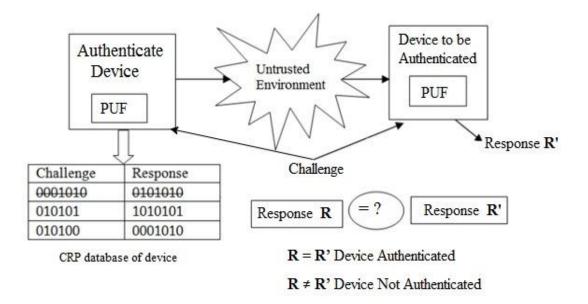

| Figure 3.16 ST-PUF authentication evaluation                   | (90) |

| Figure 3.17 PUF based Authentication                           | (91) |

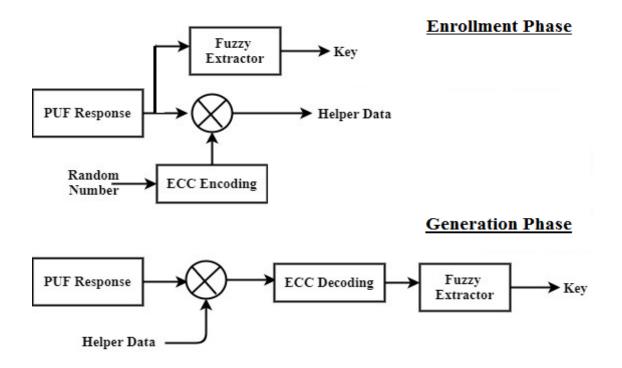

| Figure 3.18 PUF based key generation                           | (92) |

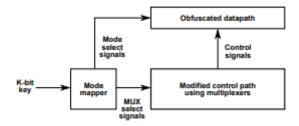

| Figure 4.1 Design Flow of Mode based Obfuscation               | (95) |

| Figure 4.2 Comparison of Encryption Scheme                                   | (96)  |

|------------------------------------------------------------------------------|-------|

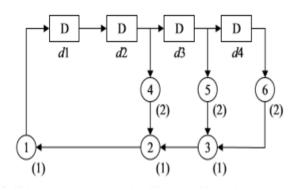

| Figure 4.3 Data Flow Graph of Finite Response System                         | (97)  |

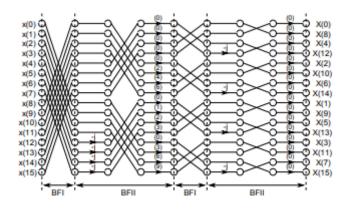

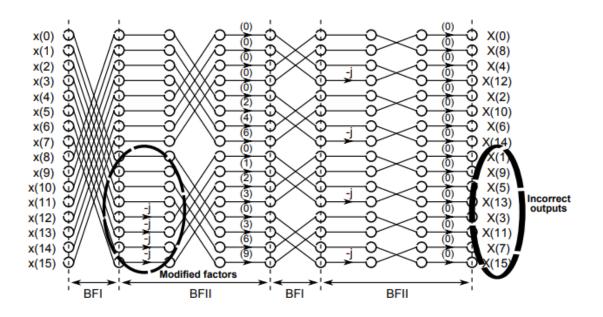

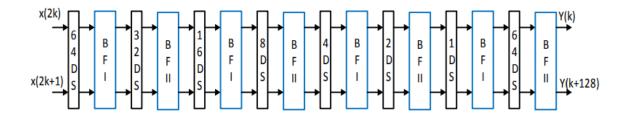

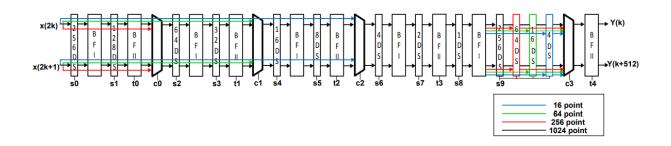

| Figure 4.4 Flow graph of radix 2 <sup>2</sup> 16 point DIF FFT               | (106) |

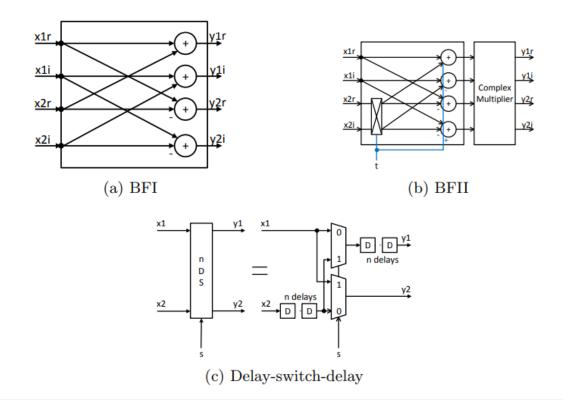

| Figure 4.5 Folded Fast Fourier Transformation (FFT) structure with 16 points | (107) |

| Figure 4.6 Blocks of Folded Architecture                                     | (108) |

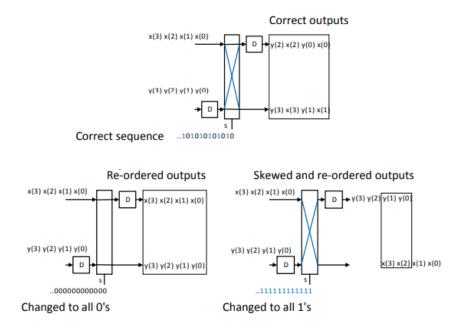

| Figure 4.7 Modified Control Logic of Delay Switch Structure                  | (108) |

| Figure 4.8 Effect of modification of –j factor                               | (109) |

| Figure 4.9 Modification of Control Logic                                     | (110) |

| Figure 4.10 Mode Based Obfuscation                                           | (111) |

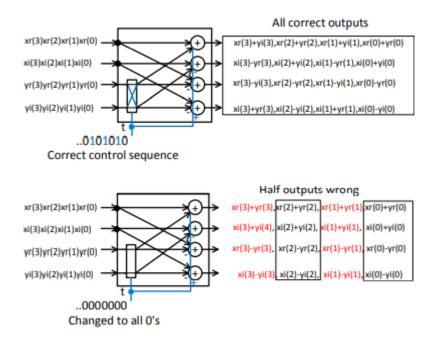

| Figure 4.11 2 Parallel Folded FFT                                            | (112) |

| Figure 4.12 Obfuscated Architecture with Meaningful Mode                     | (113) |

| Figure 4.13 Obfuscated Architecture of Control Path                          | (114) |

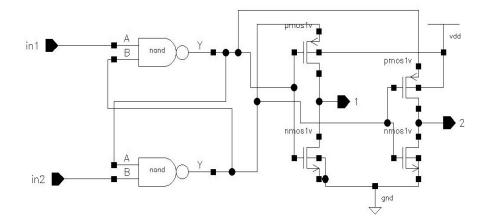

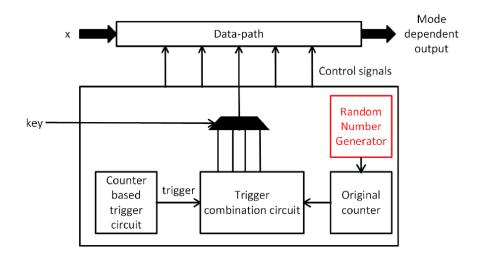

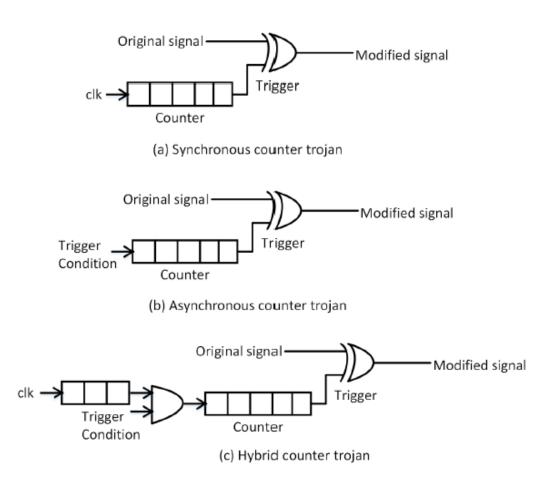

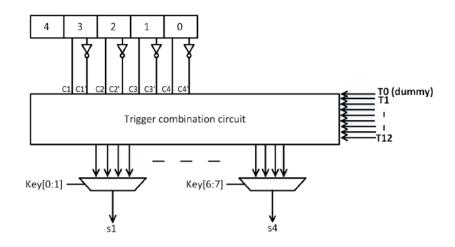

| Figure 4.14 Hardware Trojan Circuit                                          | (116) |

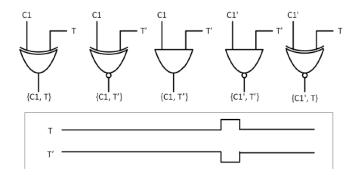

| Figure 4.15 Logic gates of Combination Trigger Circuit                       | (117) |

| Figure 4.16 Circuit for triggering multiplexer's key bits using the          |       |

| generated control signal                                                     | (118) |

| Figure 5.1 Source of side-channel information                                | (123) |

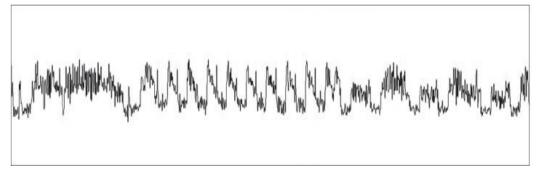

| Figure 5.2 Power trace in SPA                                                | (128) |

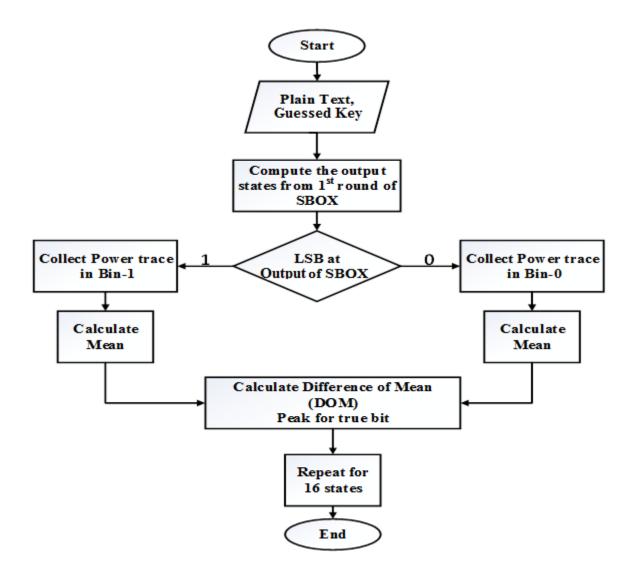

| Figure 5.3 Flow chart of DPA                                                 | (129) |

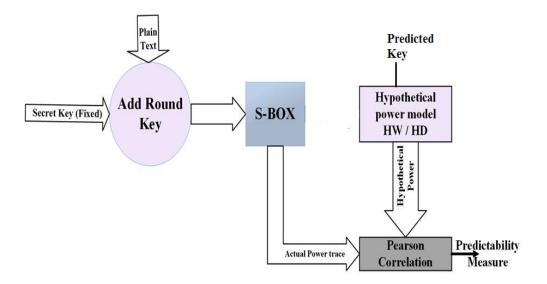

| Figure 5.4 Flow chart of CPA                                                 | (131) |

| Figure 5.5 Estimating Power using Hamming Weight                             | (132) |

| Figure 5.6 The Hamming distance Power Approximation                          | (133) |

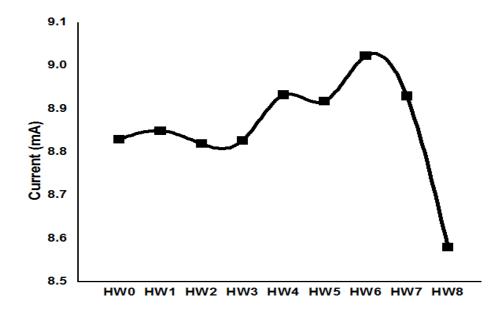

| Figure 5.7 Current vs Hamming weight (HW)                                    | (134) |

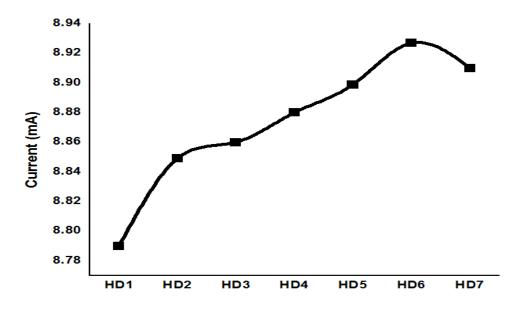

| Figure 5.8 Current vs Hamming distance (HD)                                  | (135) |

| Figure 5.9 DPA Power Flow Diagram for Proposed Design                        | (136) |

| Figure 5.10 DPA power trace for the first 16 inputs of the proposed design   | (137) |

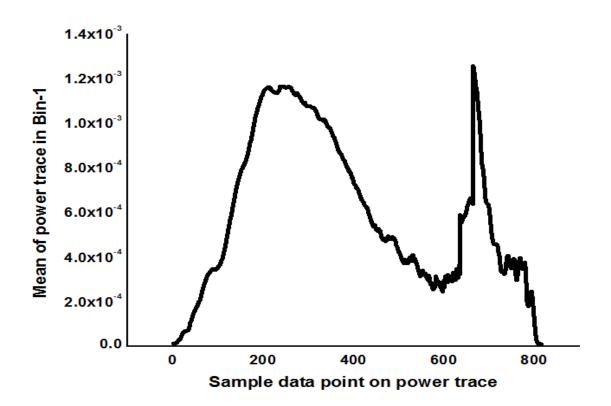

| Figure 5.11 Sum of bin1's power traces                                       | (138) |

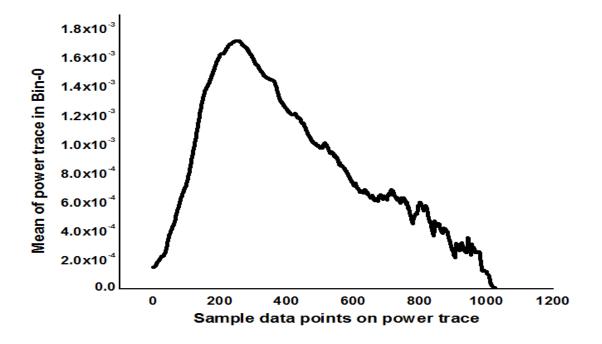

| Figure 5.12 Power curve average in bin0                                      | (138) |

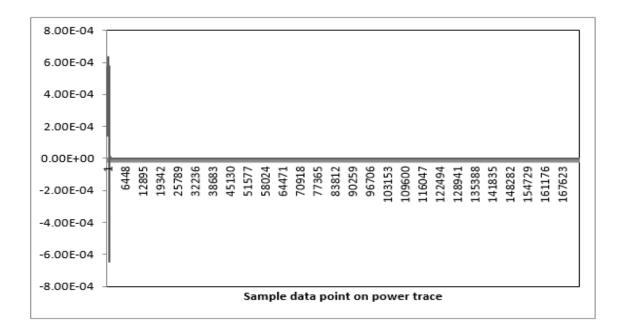

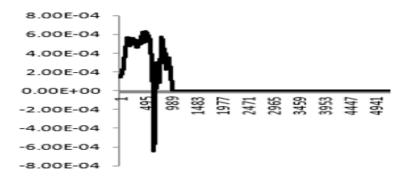

| Figure 5.13 LSB1 and LSB0 average Power Differential Curve and trace         | (139) |

| Figure 5.14 The differential curve, magnified for lower sampling value       | (139) |

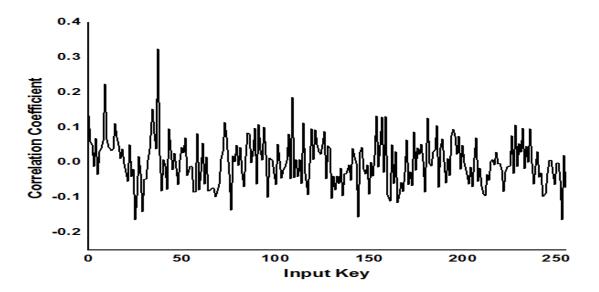

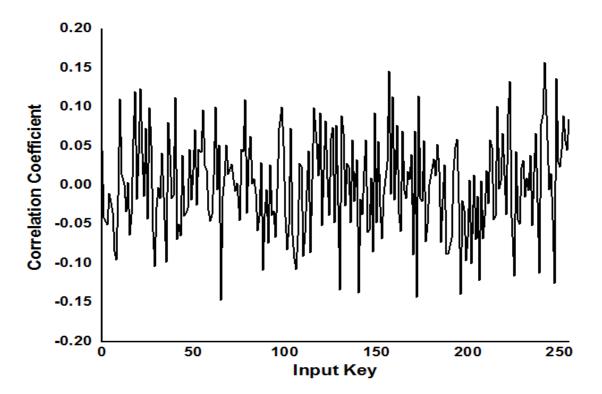

| Figure 5.15 The suggested mask design's correlation to the right guess key   |       |

| at 25HWPM                                                                      | (141) |

|--------------------------------------------------------------------------------|-------|

| Figure 5.16 The proposed design's correlation with HDPM ability to correctly   |       |

| estimate 25H keys                                                              | (141) |

| Figure 5.17 Proposed architecture with HWPM's correlation to wrong             |       |

| guess of the key                                                               | (142) |

| Figure 5.18 Proposed mask design based on a correlation coefficient with       |       |

| HDPM's ability to incorrect guess keys                                         | (143) |

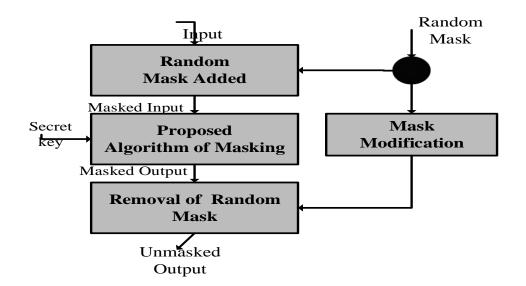

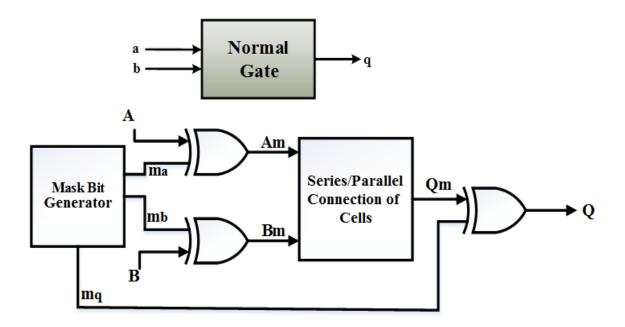

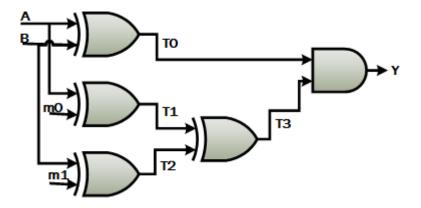

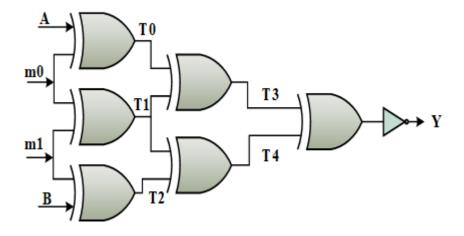

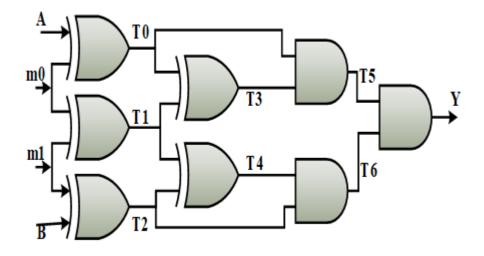

| Figure 6.1 Process of Boolean mask                                             | (145) |

| Figure 6.2 Unmask and mask gate                                                |       |

| Figure 6.3 Mask XOR-1 proposed cell                                            | (150) |

| Figure 6.4 Proposed mask XOR-2 cell                                            | (151) |

| Figure 6.5 Proposed mask AND cell                                              | (152) |

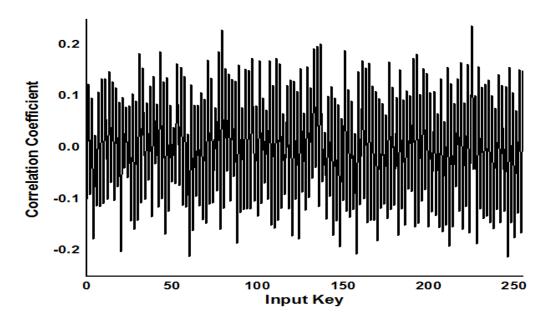

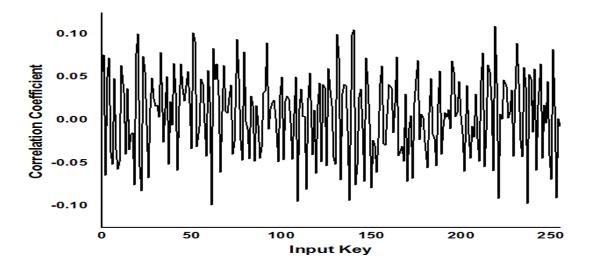

| Figure 6.6 Normal and Mask cell Pearson correlation coefficient                | (156) |

| Figure 6.7 ILA vs probability of occurrence likelihood                         | (157) |

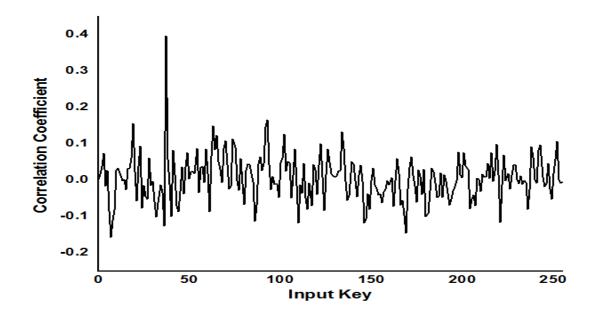

| Figure 6.8 Pearson's Correlation between the accurate guess and the actual     |       |

| key for the SBOX mask and HWPM                                                 | (158) |

| Figure 6.9 Proposed mask design with HDPM correlation with correct             |       |

| key guesses                                                                    | (159) |

| Figure 6.10 The right key's HWPM correlation coefficient is compared to        |       |

| that of an SBOX under a CPA attack                                             | (160) |

| Figure 6.11 SBOX under CPA attack comparing correlation coefficient ( $\rho$ ) |       |

| to HDPM's right key                                                            | (160) |

| Figure 6.12 Improvement in $\rho$ of proposed design with mask cell            | (164) |

## LIST OF ABBREVIATION

| Abbreviations | Description                                       |

|---------------|---------------------------------------------------|

| CMOS          | Complementary Metal Oxide Field Effect Transistor |

| CPA           | Correlation Power Analysis                        |

| DPA           | Differential Power Analysis                       |

| EDP           | Energy Delay Product                              |

| HDPM          | Hamming Distance Power Model                      |

| HSM           | Hardware Security Module                          |

| HWPM          | Hamming Weight Power model                        |

| SCA           | Side-Channel Attack                               |

| LUT           | Lookup Table                                      |

| MuxPUF        | Multiplexer based Physically Unclonable Function  |

| PDP           | Power Delay Product                               |

| PTL           | Pass Transistor Logic                             |

| PUF           | Physical Unclonable Function                      |

| RNG           | Random Number Generation                          |

| RO-PUF        | Ring Oscillator Physically Unclonable Function    |

| SPA           | Simple Power Analysis                             |

| ST            | Schmitt Trigger                                   |

| ST_PUF        | Schmitt trigger PUF                               |

| SBOX          | Substitution Box                                  |

| SVM           | Support Vector Machine                            |

| TG            | Transmission Gate                                 |

## **Chapter 1**

## Introduction

### **1.1 Overview**

The Internet-of-Things (IoT), a global network that will connect billions of devices. The trend of computing moving away from the cloud and toward the network edge is being driven by the proliferation of interconnected devices. Edge-centric computing is the term for this approach. More and more businesses are moving their computing operations to the "edge" because of concerns about security and privacy, better data accessibility, and improved computing resources [1, 2]. However, there will be a number of issues that need to be addressed as a result.

- Manufacturing small integrated circuits and embedded chips is expected to rise as the number of devices being produced and connected grows.

- In-house foundries will see a decline in use as more companies opt to outsource their fabrication.

- The IoT framework thrives on both device-to-device and cloud-to-device communication in its network. These communications necessitate high levels of security and privacy.

- Smart cards and chips, as well as laptops and cell phones, can all be used at the edge of the network. A lack of high-quality random number generators, which is critical for a number of cryptographic algorithms, could result in low device resources in many applications.

- Cryptographic algorithm tasks like secret key distribution and management can be difficult due to the large number of devices connected to the network.

- Machine learning algorithms, such as Support Vector Machines, Neural Networks, etc., will become increasingly necessary to run on the device itself. Training algorithms can also be run on the hardware in many cases. This necessitates a lot of processing power and memory.

IoT devices must consume as little energy as possible because they are typically powered by small portable batteries or wireless power transfer.

Because of the current craze, hardware security is becoming an increasingly important area of study. While software threats can be traced, physical tampering of hardware can go undetected, making hardware threads difficult to detect. It is extremely dangerous to distribute this hardware in an unsupervised and uncontrolled manner, as the user may be fooled by the tampered device. IC chips, which are becoming increasingly common in consumer electronics, are a result of the current smart era's emphasis on making every device as user-friendly and intelligent as possible. In the military, precise and efficient results are achieved through the use of these Hardwares. Scientific and space research organisations also use them, and the security risks they pose are frightening. IP theft, piracy, Trojan insertion, and information leaks are just a few of the many attack models. The device's security may be jeopardised as a result of this. Trojans, which are difficult to learn about. Since the hardware implementation provides more information than specific algorithms, these approaches are extremely risky.

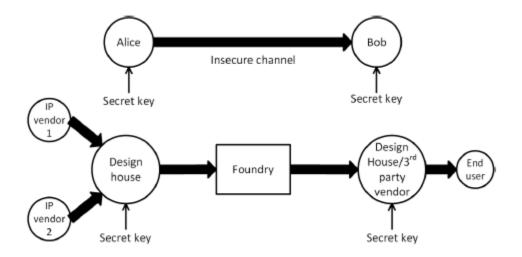

Demand for semiconductor devices has skyrocketed as a result of the invention of semiconductor material. For the most part, other consumer electronics have utilised semiconductor integrated circuits (ICs). As a result, there was a demand for a more advanced device with additional features, and scaling technology was used to meet that demand and increase functionality. The threshold value and the supply voltage are both reduced in this method. Moore's Law predicts that this scaling of the device will occur [3]. As technology shrinks in size, new issues in the circuit arise, such as the difficulty of fabricating 10nm technology and problems with IC testing. In response to the fact that IC production had become a time-consuming and difficult process, several foundries emerged to address these issues. Some companies offer software tools to assist in the circuit's verification and design. Soft intellectual property (IP) provided by designers can also significantly reduce design time. The next step is to have the ICs fabricated in an outsourced fabrication facility, which aids in both precision and speed. This has also prompted questions about the ICs' safety. No one can guarantee 100 percent safety; the best we can do is design a chip that makes reverse engineering much more expensive and time consuming. Figure 1.1 depicts the various stages of IC production and the security issues that arise at each stage.

Figure 1.1. Level of IC design and security at each stage

Another security concern arises from the use of outside foundries in the fabrication process. Allegations of hardware theft have skyrocketed in recent years [4]. As a result, it is even more critical than before to focus on hardware security. The designer's ability to maintain creative control has been severely weakened as a result of the outsourcing industry. Since this design was stolen, some security measures have been put into place. The IC's threat can be categorised as:

- ▶ Hardware Trojan Insertion is used to steal sensitive data from a target device.

- Reverse engineering is a method for discovering the design's structure and functionality.

- Stolen design and manufacturing of the same IC under another name results in significant revenue loss; this practise is referred to as "IC theft".

- Illegal use of intellectual property to produce the design is known as IP threat.

Many techniques are procured at various stages of IC manufacturing in order to ensure the design's security. Authentication-based and obfuscation-based approaches are the two broad categories of hardware security technique.

The standard set of characteristics used to characterise very large scale integration (VLSI) circuits now includes security. The safety of the system must be built on a bedrock of trust. The response (output) of the hardware security module is a nonlinear function of the challenge input [5, 6], making it impossible for unauthorised users to foresee. A piece of information is given a physically specified answer by the Physical Unclonable Function (PUF). Semiconductor devices that exploit PUF take use of a physical device or circuit variance that occurs spontaneously during manufacturing [7]. According to NXP Semiconductors, a PUF system may be employed for electronic qualities that are inherently unstable but whose stable state varies. The reaction of

the electrical gadget depends on both the input and its own properties. If a third party has knowledge of the feedback and the equipment, unauthorised access is impossible. PUF should offer (a)a wide range of responses to the same challenge, (b)a consistent distribution of responses, and (c)a steady response even in a hostile operating environment. PUF's two most important uses are in secure authentication and key creation for use in cryptography. [8, 9]. Both a ring oscillator PUF and a delay-based arbiter-PUF are available as PUF parts.

PUFs, or physically unclonable functions, are innovative, promising circuits that are primitive in design but hold great promise because they can be used for authentication, as well as for generating and storing the secret key, without the need for the previously mentioned expensive, power-guzzling large circuitry. PUF generates the secret key, rather than keeping the secret key in nonvolatile memory, so that we can accomplish this goal.. It is impossible to control all aspects of integrated circuits during manufacturing. Due to manufacturing variations, PUF realises these controllable parameters and converts them into a readable form. It is possible to use PUF's uncontrollable parameters as a secret key. Depending on our application, this secret key can now be used for authentication or cryptographic methods.

A few of PUF's advantages over other standard protocols are listed below.

- Because SRAM/EPROM memory sources are expensive and difficult to manufacture, PUF hardware uses simple digital circuits that are easier to manufacture, require less space and consume fewer kilowatts of power. To replace PUFs, we can use the secure hash algorithm (SHA) and replace encryption algorithms that use public and private keys with cryptographic hardware techniques.

- We generate our secret key in PUF using the physical parameters of an integrated circuit. When the device is powered on, any information about the secret key must be extracted. As a result, the chip can only be attacked physically when it is powered on.

- Attacks on PUF are more difficult because the physical parameters of PUF must not be altered to extract the secret key. As a result, invasive attacks against PUF are more difficult to carry out. Due to the lack of invasive attacks on PUF, we don't need expensive and power-consuming anti-tamper mechanisms.

Non-volatile memory manufacturing is a costly endeavour. EPROMs and RAMs, which require external power, always require additional mask layers. These are not necessary in the case of PUF.

Watermarking and IP signatures were the most widely used authentication methods in the beginning, but they were eventually supplanted by more sound and effective security methods that protect against both copyright violations and unauthorised copying. This strategy helped to reduce the illegal distribution of ICs, protect intellectual property rights, and reduce the use of counterfeit IC chips by consumers. To protect their products from unauthorised reselling, manufacturers use watermarking and signature techniques. However, this does not prevent counterfeiters from learning about the design's internal structure and fabricating their own chip. The basis for a watermark or digital signature is that the IC displays a logo that identifies the original designer or manufacturer of the product. Because it does not provide security at all levels, this technique is ineffective in preventing overbuilding and IP piracy by protecting against illegal use of the IC. It is still possible for the hacker to study the schematics and gain an understanding of the IC's operation and structure, and then produce his own version of the IC from scratch. In the IC industry, reverse engineering has become a major threat to theft and espionage. An IC's structure, functionality, and design can all be described using Reverse Engineering. It is very easy to tamper with or illegally use a circuit once you have a good understanding of its inner workings. The number of incidents involving the theft of computer hardware has skyrocketed. Additionally, various techniques like watermarking [10, 11] and cryptography [12, 13] can be used to prevent the illegal and unauthorised use of IC. The use of a key or fingerprint as a form of authentication is also common. Keys used to encrypt designs previously resided inside of the IC chips, but new techniques for reverse engineering have made it much easier to extract the key from the fuses, which are located on the surface of the chips. As a result, a method for creating a key that can't be duplicated was devised. PUFs and FSMs are both viable options for providing a user's key. To operate normally, the circuit needed to be entered correctly. To operate incorrectly, the circuit needed to be entered incorrectly.

Physical Unclonable Functions (PUFs) exist in several forms, with each variant possessing distinct attributes. Various types of Physical Unclonable Functions (PUFs) include the Ring Oscillator PUF, SRAM PUF, Arbiter PUF, Delay PUF, Optical PUF, MEMS PUF, and

Analogue PUF. The selection of a physically unclonable function (PUF) type is contingent upon the particular demands of the application, the desired level of security, the resources at hand, and the vulnerability to environmental and manufacturing fluctuations. Scholars persist in their investigation of novel forms of Physical Unclonable Functions (PUFs) and the enhancement of pre-existing ones in order to tackle diverse issues and boost the overall security and dependability of PUF-based systems. A Delay Physical Unclonable Function (Delay PUF) is a variant of a Physical Unclonable Function (PUF) that leverages the inherent changes in signal propagation delays present in a circuit. One of the advantages of Delay Physical Unclonable Functions (PUFs) is the technique employed involves the utilization of variances in signal propagation delays. The utilization of common digital components can facilitate the implementation process. Exhibiting resistance to certain environmental fluctuations. Prone to fluctuations in temperature. The Delay Physical Unclonable Function (PUF) has been selected for our research because to its ability to operate independently of environmental fluctuations and its utilization of timing variations in the signal.

Once the chip has been manufactured, we must ensure that the adversary has a difficult time understanding the chip's structure and function. This sparked further research into the secure technique, which resulted in the development of a number of similar methods in the years to come. Obfuscation is one of the most widely used strategies. Obfuscation is the primary focus of this paper. The process of making an IC structurally and functionally safe is referred to as obfuscation. The IC's structure and function are hidden from the adversary, making it much more difficult for them to reverse-engineer the IC itself. Due to the increased difficulty and expense of reverse engineering, the design is a success in protecting against various malicious attacks.

When obfuscation is employed, there are two primary approaches: structurally and functionally.

Structure Obfuscation is when we make it more difficult to figure out the design's function by making it more complex structurally [14]. In [15], we saw how by employing HLT techniques, we were able to alter circuit structures to look similar but perform a different function. Although they appear to be structurally identical, the two circuits are functionally distinct.

A key is used in Functional Obfuscation. The design will not produce the desired result unless the key is entered correctly. It is possible to store this key in the form of fuses within the circuit. Fusing the key into non-volatile memory of circuits makes it insecure because the adversaries can get their hands on it and use it to attack the system. The key to the circuitry was thus developed using a technique known as PUF [16]. Using dynamic obfuscation in [17], the author devised a technique that uses the circuit going into obfuscated mode, but does not always produce the wrong output, in order to make it much more difficult to reverse engineer. To make the design more difficult and more secure, a random number generates output that is sometimes correct and other times incorrect.

#### **1.2 Researcher's Contribution**

This work presents a Physical Unclonable Function (PUF) based on a Schmitt trigger whose response depends on challenge input and two device-specific characteristics. Until now, PUF responses have never been linked to multiple hardware-specific characteristics.

To reduce the number of in-line delay elements, a shifting algorithm has been proposed. Advanced sign preparation calculations are represented by iterative information flow diagrams, in which hubs and edges speak to calculations and correspondences separately because of the redundant concept of these calculations.

It has been suggested that hardware obfuscation, which involves making modifications to integrated circuits and locking them with keys, be used to ease the burden of secure manufacturing. In my research, I present a novel approach to hardware obfuscation by modifying control signals of the architecture and extending it for use in a hierarchical manner to an integrated circuit.

Attacks on obfuscated circuits have become more effective due to the availability of low-cost resources and equipment, and current obfuscation methods are insufficiently secure and easy to break. As a response to this issue, an obfuscation method that uses modes that are unpredictable and random was developed to increase the design's security by orders of magnitude.

By analysing the power supply, the attacker can decrypt the secret data. In this study, we suggest a design for mask XOR and mask AND cells that is resistant to power attacks. Due to the reduced correlation coefficient, it is clear that the pattern of power consumption does not retain a linear relationship with the processed data when using a mask cell implementation.

### **1.3 Outline of Thesis**

There are seven parts to the thesis. Here is a rundown of what each chapter covers.

The necessity of hardware security is presented in Chapter 1. It stresses the need of constructing a physical unclonable function and gives a brief summary of the limitations imposed by sidechannel information. This chapter incorporates the author's work.

Chapter 2 details the research of a third party in accordance with the goals of the author. There are three main categories that we'll be looking at: the formation of physical unclonable functions, power and assault, and defences against power attacks.

In Chapter 3, we see an original idea for an unclonable physical function that relies on Schmitt triggers. The chapter delves further into the STPUF simulation findings and details their successes.

In Chapter 4, we see how to determine the iteration bound using the column-shifting method. In this chapter, you will learn how to use the Folding Transformation to create both meaningful and meaningless blocks for use in mode-based obfuscation.

In Chapter 5, we see an attack against SBOX based on power analysis, specifically a combination of pounding weight and distance power models. The connection between actual strength and anticipated strength is investigated here.

The chapter 6 content is dedicated to the attack-resistant feature of the logic cell design. In this section, we looked at masking, a technique used to hide sensitive data from circuits.

Chapter 7 concludes the thesis by discussing the most important findings of the author's current research, the contribution of the thesis, and the scope for further study in this area.

# Chapter 2 Literature Review

Concerns about the security, authenticity, and reliability of electronic components (ICs) have risen as a result of their widespread use in smart phones and other devices. Security measures have been developed to protect the design not just against algorithmic attacks but also from physical ones. There have been a number of attempts to design an authentication system that secures the owner's entitlement to the IC, but does not shield it from physical attack. Thereby, various methods were investigated and the secret key-locking method was developed. Incorrectly inputted keys do not operate the IC and it displays unknown value. Previous versions of reverse engineering techniques utilised RAMs inside IC chips to store the key required to lock designs, but newer techniques like side channel attacks and power estimates made it possible to extract the key from fuses with relative ease. It made it simple to make a copy of the key and use it to unlock the design by making power differences in the design. To ensure the IC's security, a more trustworthy method was required. PUF and FSM techniques advanced as a result of this. Because of its inherent inability to be replicated, these tactics quickly became popular. It demonstrates a wide range of inter-chip and intra-chip features.

Since 1970, CMOS has been the dominating technology in the VLSI industry. VLSI technology has made an important trade-off in the design of integrated circuits (I.C.s). yield or die area was of paramount importance in 1970. In 1980, circuit speed became the primary constraint due to advancements in technology. The 1990s scaling era was characterised by an emphasis on improving both speed and power. In 2000, it was discovered that adding more components to a wafer increases cacophony. and that noise may be used to improve both power and speed. It's no secret that security was a major focus in product development in 2010. To make, leakage information independent, of the data to be processed, additional circuitry has been added, resulting in an increase in die size and power consumption. A directed critical path, on the other hand, can reduce the time.

#### 2.1 Hardware Security Module (HSM)

By incorporating the unpredictable characteristics of semiconductor devices, hardware security aims to raise the algorithm's security bar.

#### 2.2 Physically Unclonable Function (PUF) as Hardware Security Module (HSM)

It's an inventive circuit that extracts a unique feature from integrated circuits. PUF circuits based on the silicon IC-based were introduced in 2002 by Gassend, Blaise, and others [18]. Even when using the same material and tools, no two silicon devices will have the exact same properties. 2007 [19] saw the introduction of PUF's use in authenticating and generating random numbers by G. Suh and S. Devdas. For each challenge, the unique PUF response should be impossible to guess by users. Horie et al. [20] in 2013 confirmed the PUF circuit's uniqueness, homogeneity, and reliability.

### 2.3 Obfuscating DSP circuits via High Level Transformation

It's become apparent that software isn't the only item that requires safeguarding with the unexpected explosion of smart devices in our homes, workplaces, and military forces. Moore's Law predicted in [3] that the number of transistors on a semiconductor would increase exponentially due to the pervasive use of integrated circuits (ICs) in electronic devices and the optimal utilisation of those devices' functionality. When the density of chips increases, the size of chips shrinks. Because of the difficulty and length of time involved in designing and fabricating IC devices with a shrinkage in the 6nm-7nm region, this technology has become obsolete. A number of outsourcing organisations have emerged to handle fabrication, masking, and IP production tasks as a result. The rise in outsourcing of chips has resulted in a loss of control for the designer in the design process. There are numerous ways to compromise the IC chip's security. The number of incidents involving the theft of hardware has skyrocketed [21]. Protection from Hardware Theft and Reverse Engineering threats is a must in light of these requests. A technique known as Obfuscation is discussed in this work. Obfuscation is a technique for making the design difficult to reverse engineer in both its functional and structural aspects. The more secure a device is, the more time and work it takes to reverse engineer it. This section discusses structural obfuscation via HLT, such as folding and pipelining.

Since electronic gadgets are becoming more and more interconnected, it's become apparent that software isn't the only thing that needs safeguarding. Devices need hardware security in order to function properly. Military and other sensitive areas are concerned that electronic devices could leak sensitive information. Authentication or obfuscation-based approaches can be used to accomplish this. This study takes an obfuscation technique, in which a design's structure and function are altered in such a way that understanding it and deciphering it are both tough tasks. In contrast to previous work on obfuscation DSP filters, a combinational DSP multiplier is employed in this paper. Folding Technique has been used to perform Structural Obfuscation on the Wallace Tree and Baugh Walley multipliers. Folding and retiming techniques have also been shown to significantly lower the power consumption of the original design. By altering the timing of switch connectivity, Structural Obfuscation by Folding not only made the design difficult to understand, but it also provided protection against the design's functional identification as well. The DSP circuits, with switches for timing control are difficult to comprehend at a glance, and the same structure serves multiple purposes. In order to accomplish this goal, the switches in the circuit might be programmed to act in a different manner. The behaviour of the circuit is dependent on the configuration of the switches. The output is accurate if the switches are synced with one another in the suitable manner; otherwise, it is inaccurate.

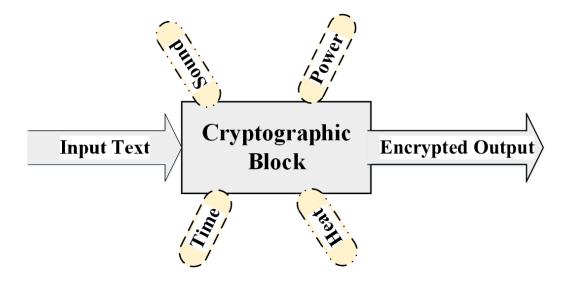

### 2.4 Side Channel Information

Instead of exploiting a flaw in the security algorithm, a circuit secret can be obtained by a side-channel attack. Mathematically secure security algorithms like DES and AES rely on the user providing the primary input and the secret key being used to calculate the primary output. A VLSI implementation of such an algorithm has hardware restrictions, as explained in [22, 23]. Leakage is a problem for CMOS devices, and it becomes more noticeable with scaled MOS transistors. The cryptographic algorithm's principal output is computed by a CMOS implementation, in addition to the secondary information that was leaked. By using a technique called side-channel analysis, the attacker can obtain control of the device and examine its internals. Although a power assault is the most efficient type of side-channel attack, there are others, like heat, sound, time, faults, etc., that are all viable options. Attacks that use passive side-channels take use of information that is released from the outside of a device through its interface. These attacks are discussed in [24, 25]. An active side-channel attacker actively manipulates, a device by introducing probes and defect data in order to get the sensitive information discussed in [26], which describes how this type of attack is carried out.

### 2.5 Literature Review: Categorization

#### **2.5.1 PUF Literature Review**

In [27], Maiti, A., Kim, I., and Schaumont, P. explain that a unique response to each challenge is a necessary condition for device authentication. A reliable PUF must generate a unique response from a pool of possible responses to the same input bit challenge, as well as a large numbers, of random numbers from which the secret key can be extracted. To improve the CRP set, the author of this study proposes a new method that relies on a recursive operator (R.O). A PUF's entropy can be adjusted during construction by adjusting various circuit characteristics. When a large key and a large numbers, of challenge-response pairs are employed in a circuit, both the hardware area and cost are increased. The author uses ROPUF to produce CRP pairs of the same size while using fewer resources. The area required for this CRP generator has been cut in half, and it is now able to generate additional functions via statistical hypothesis testing on an FPGA platform. Uniqueness, reliability, and impartiality are the metrics by which PUF quality is evaluated. High output uniqueness and dependability may be attained with the presented PUF, which has an inter-chip H.D. of an average of 50.07 percent. Even in a protected setting, a PUF circuit should be able to produce unique replies. High-temperature, threshold-voltage-variable, response-bit creation using memory. The limitations of supply voltage and the means by which it can be distributed and diversified were studied.

Different PUF structures, are constructed and their performance, is compared in paper [28] by Susana Eiroa et al. (2010) in terms of, inter and intra hamming distance. In PUF, a collection of challenges is transferred to a set of responses, both of which are bit/byte in size and are driven by physical characteristics that are difficult to predict and recreate. Two of PUF's most important uses are in secure authentication and random number generation in hardware [29]. Discussed and analysed is a silicon I.C.-based exact random generating technique for its randomness, uniqueness, and dependability in static analysis. Investigated were the challenges of implementation and how they were affected by their surroundings. Since there are many variables to tweak before getting a usable result, PUF selection can be tricky. This research covers many PUF architectures, and discusses how reconfigurable PUF can be used to dynamically alter the inherited attributes. A controlled PUF system will typically allow access to a generic processing unit via a dedicated programme. Cell leakage current is used to calculate the PUF, and the PUF is then digitalized and encoded to produce the cell's unique identifier.

Bitstream encryption is used by many FPGA manufacturers as a means of protecting intellectual property, as discussed in paper [30] by Kumar et al. (2008). PUF is an alternative physical system that extracts response from the integrated circuit's inherent physical features. PUF, as explained below, is a very secure approach to creating a temporary secret key for use in a cryptographic operation that cannot be duplicated. In this study, the author uses the unpredictability of the D-latch to achieve stability following metastability caused by the violation of the setup and hold times. A butterfly PUF is implemented with common I.P. found in any FPGA (cross-coupled D-latch structure, CLB, BRM). The effects of temperature changes, from - 20 degrees Celsius to 80 degrees Celsius, on the inter- and intra-hamming distances are investigated. Measured H.D. and FPGA-based H.D. discrepancies validate PUF. In order to generate the response, Butterfly PUF makes use of the integrated circuit's inherent physical qualities, specifically the matrix of available internal resources on the FPGA. An encouraging component, Butterfly PUF creates a steady response and FPGA-friendly environment to run in. Katzenbeisser et al. (2012) of the paper [31] implement a delay arbiter and ring oscillator (RO-PUF) using CMOS 65nm technology.

The temperature, supply voltage, and noise properties of PUF have been investigated. When compared to SRAM PUF, ROPUF has complete independence in all desirable qualities [32]. Data from testing performed on 96 TSMC 65nm CMOS ASICs. The following PUF characteristics are taken into consideration during an evaluation: (a) robustness, as measured by bit error rate; (b) the number of bits in response1 differs from response2. Unpredictability challengers (b) are incapable of computing PUF's response to a known input challenge efficiently. The entropy of flip-flops and latches is temperature-dependent, whereas the Arbiter PUF exhibits minimal entropy. Authentication and key generation are two of the most important uses of PUF, hence their suitability and selection are crucial.

Majzoobi et al. (2012) offered a safe way to authenticate and reply utilising arbiter and strong PUF in article [33]. With the XORing together of the path responses from a linear arbiter and two separate parallel arbiters, we may implement PUF with improved static characteristics. Thin PUF correctly guessed a random number and discovered that a 64-bit arbiter PUF model achieved 95% accuracy. The presented slim PUF deviates from the traditional model in that just a fraction of the responses received for authentication are revealed. Lightweight error correction logic, a fuzzy extractor, and resistance to machine learning attacks all contribute to the response

pattern's strength as a method of strong authentication. Short PUFs with a critical length of 128, 256, or 512 reach the hamming threshold of 33,76 or 154 bits, respectively.

According to Handschuh et al. (2010), the PUF is a feature of a device in paper that may be used to extract the key. It is also called an electronic fingerprint [34]. Physically Unclonable Function (PUF) refers to the physical characteristic of a device that is difficult to replicate due to its distinct micro and nanoscale features, which are the result of manufacturing variation. The cloning of PUF is a lengthy process that necessitates the use of sophisticated mathematical models and computational algorithms in order to predict the correct answer to a problem in a timely manner. Here, the author implemented a biometric based on differences in threshold voltage between SRAM transistors. A fast transistor and a slow transistor each make a choice based on logic to determine if a situation is 1 or 0. The author of the paper proposed a secure key storage method for SRAM and ROM, where the secret key is stored. With each transistor's length in mind, a separate threshold voltage can be attained, and a different initialization value can be provided by each cell. Operational consultation temperature, voltage variation, and radiation evaluation of PUF quality. The various PUFs that have been reported are as follows: SRAM PUF 950/1000 bits The delay PUF is 130 bits per 1000 bits, while the butterfly PUF is 600 bits per 1000 bits.

True random number generation is described in paper [35] by Barak et al. (2014). It's important that the random number be uncalculable. Although PRNG-based random numbers are typically thought to be non-deterministic, it is possible to predict the next number by looking at its past behaviour. Multiple extremely important applications, such as lotteries, Monte-Carlo simulations, cryptographic key generation, etc., made use of random numbers. The software process used to produce random numbers is not truly random; it cycles back over the same numbers after a fixed number of iterations, and it can be computed if the original seed or the pattern of numbers generated before it is known. Mixed hardware properties are used in a real random number generator. This parameter is a nonlinear function of the derived random number. The author explains how to generate random numbers using noise as the source of entropy in this study. A generating scheme's entropy comes from a random operation, or R.O., malfunction. There is still work to be done, but the author has laid out the challenges and opportunities in random number generation. To create digital data, the noise mechanism amplifies and digitises a low-voltage signal. Given that the I.C. designer can bring down the noise to any acceptable level,

designing an amplifier is a tedious process. A random number generator (RNG) based on the concept of chaos combines a collection of free-running oscillators to generate numerous frequencies at a randomly selected rate, and then applies that rate to a digital block to produce a random bit.

Bhargava et al (2010) [36] Personal Uninterruptible Power Supplies that use a sensing amplifier to withstand attacks on the measured voltage. In static memory, the amplifier serves as the reading path. This circuit can detect very low voltage changes. The author of this work has produced a sizable number of SRAM cells, each of which has a threshold voltage that is distinct from the others. The input delay is determined by the unique voltage that is present in each cell. Allows, for every column sense amplifier It is the offset voltage and the mapping strategy that determine the resulting response. The minimal voltage required to resolve a 0 or 1 bit is only a few microvolts, and the sense amplifier can do this reliably. The error is fixed on the answer in a post-processing unit so that the bit is consistent and trustworthy. The research presents a low-cost error-correcting code (ECC) block method for protecting power-under-full-load (PUF) amplifiers against the effects of environmental variation. Through a scrambler, the SA PUF design obtains the required address from the S.A. array based on the inputted challenge bit. The median of the simulation results based on CMOS 65nm technology Area reduced by a factor of 2.5 and the hamming distance down to 16.000937.

NXP Semiconductor (2013) [37] published a paper titled "Processor-Based Consistently high PUF over time confirmed by studying response consistency across many years. Threshold voltage, effective gate length, and other factors are all influenced by the intrinsic randomness of the manufacturing process in silicon I.C. The final response bit is decided by combining the results of two ALU cores, with a xor gate inserted in the middle of the circuit to prevent any information from escaping. The effect of changing challenge and PUF behaviours on Hamming distance is investigated. A minuscule circuit embedded within the processor extracts response bits with a distinct temporal signature on the fly. Using an ageing parameter to evaluate the decay of logic level over time, the given PUF is able to produce an average Hamming distance of 16.1% for a 32-bit response. After that, this difference is sent into an amplifier and a digital converter block as their respective input. Following the deployment of CMOS 45nm technology, an increase of 98.1% in the typical intra-chip hamming distance is seen.

Hossain (2015) in article [38] presents a promising security module based on the ROPUF random function of the I.C.'s special functions that are distinct for each die. Producing a new variety of PUD through I.C. manufacturing variations. If you want a reliable component in your PUF circuit, RO is your best bet because it consistently delivers the desired results. All of the inverter stages in the R.O. were constructed using CMOS and FTL technology, and the author recommended using 13 sets of RO PUF to generate independently-operating frequencies. An analysis of the differences between a standard inverter and an FTL inverter is provided; the FTL inverter is more inverse since it uses a larger number of NMOS in a parallel configuration, each of which is operated by its own clock. Using an FTL inverter allows for a high frequency of operation. To some extent, each of the frequencies was chosen at random. The results suggest that we are 45.24 percent unique (the target is 50 percent), 91.14% reliable (100 percent), and 41.45 percent uniform. Low threshold voltage PUF quality reports of 46.85% uniqueness, 95.54% reliability, and 40.799% uniformity, and high threshold voltage PUF quality reports of 41.71% uniqueness, 90.12% reliability, and 42.34% uniformity.

Maiti et al. (2009) publish a study [39] where PUF is used as a (TRNG) True Random Number Generator. Both PUF and TRNG have proven to be useful for developing a secrete system. The TRNG is used to produce random padding bits and the initialization vector, while the PUF is responsible for extracting a random chip signature to use as a volatile secret key. In this work, the author investigates R.O.-based TRNG, bringing novel contributions in terms of reduced area requirement, scalability, portability between platforms, and bridge between circuit and system. The TRNG bitstream quality has been validated by both the NIST and DIEHARD test suites. Xilinx's Spartan 3S500E series FPGA was used to create a rising-edge 32-bit and 64-bit RO PUF. The originality and reliability of the RO PUF answer are, respectively, 42.8% and 80%. However, when the number of R.O. stages increases, these values begin to decline. The circuit is controlled by an XOR gate, which generates 32 bits of randomness at 3.2 MBPS and a unique device signature.

According to the findings that Kong et al. (2013) report in their study [40], device authentication requires very little power and smaller circuits than traditional methods, which makes PUF's modest dimensions suitable. Stability of silicon PUF may be improved by lowering the temperature coefficient of threshold voltage and lowering the nmos and pmos threshold voltage fluctuation. The use of inverters with a variety of widths and architectural layouts contributes to an improvement in the dependability of PUF. PUF, depending on the technology, was evaluated using a NIST test suit for CMOS responsiveness at both 90nm and 45nm. PUFs that measure leakage current make use of a leakage sensor whose output remains the same from measurement to measurement. Despite this, PUF responses can fluctuate to some degree owing to manufacturing tolerances and other variables. When compared to RO PUF, leakage PUF achieves a score of 60% reduction in power consumption while also achieving an 84% reduction in area and a 35% improvement in temperature stability utilising Monte Carlo simulation experiments with 2000 chip instances.

Using transitory effects, Maiti et al. (2013) [41] suggest a ROPUF. The planning, testing, and fine-tuning of the ROPUF impulse response. The ring oscillator's brief effect at startup increases randomness and produces a more consistent response than ROPUF. The TERO PUF response generating system was evaluated on 30 chips fabricated using a CMOS 350nm manufacturing technology at room temperature with standard corner and voltage settings. The design goals of TERO PUF are to maximise efficiency and minimise footprint without sacrificing output quality. To further ensure stability, a second balancing block is used to draw out maximum entropy. By isolating TERO's oscillation, TERO PUF generates multiple response bits from a single circuit. There is 49% originality, 5% consistency, and 99% chance in the production of responses.

PUF design with remanence decay is reported in paper [42] by Shaza et al. (2015). Remanence is the property used in conjunction with non-volatile memory to retain the binary value for an extended period of time. In this paper, we propose a CMOS 65nm PUF array with 8KB of SRAM as a lightweight security primary. In order to increase cloning resistance in SRAM PUF, remanence decay is utilised as a countermeasure against side-channel attacks. The goal is to achieve a time remanence of 43.455% and a voltage remanence of 44.82%.

According to study [43] by Herder et al. (2014), PUF can be broken down into two categories: those that are weak and those that are strong. The author has developed a PUF based on a ring oscillator, SRAM, and arbiter using 180nm CMOS technology. According to the application, PUF is classified as a string and feeble PUF. The strong PUF can be used for secure authentication, while the weak PUF can generate cryptographic keys. While a powerful PUF requires a large number of CRP, a weak PUF can get by with a smaller number by taking advantage of the manufacturing variation. In addition, results obtained by PUFs were previously

steady and dependable thanks to error correcting algorithms. Various PUF topologies, including optical PUF, Arbiter PUF, and RO PUF, have been tried and tested by the author. The 6% interand 5% intra-variation in PUF responsiveness obtained across a -25 to 85C temperature range is impressive. Since it is difficult to test to clone PUF and predict its past CRPS, it is also difficult to teach it to be vulnerable to attacks.

Meguerdichian (2011) introduced in article [44] a new design of Dynamic PUF (DPUFs), whose properties fluctuate randomly between applications. Since device ageing allows for fast reversibility and low-energy customisation, it was a natural fit in this scenario. For this purpose, the author suggests using a technique from numerical algebra to perform reverse engineering. As predicted by the ageing model for CAD tools based on negative bias temperature instability (NBTI) and hot carrier injection (HCI), particular hardware properties for the PUF non-linear function degrade over time. When a module pair ages, there is a difference in their state, which can be decoded as a logic one or zero by a variation arbiter. A buffer chain must be included to the design in order to provide protection from attacks. High unpredictability and rapid stabilisation are hallmarks of dynamic PUF.

In their article [45], Zouha et al. (2012) present a method for assessing a silicon PUF based on delay elements during the design phase without the circuit. The method is predicated on a Monte Carlo (MC) simulation of the netlist that accounts for process variation and the surrounding environment. When endeavouring to evaluate PUF, numerous parameters are utilised. Maximum entropy randomness. PUF constructed with HDL and simulation results based on Cyclone II FPGA to guarantee uniqueness and dependability (response bit unaffected by environmental and operational conditions). This method verifies the simulation results by comparing them to silicon measurements, which indicate that the arbiter PUF is 97% unique and 98% corrupt. Loop PUF is able to accomplish a 95% rate of uniqueness and a 98% rate of stability by utilising a delay chain, an odd number of cascaded structures such as a ring oscillator, and a frequency measurement device.

Pegu et al. (2015) of article [46] make use of an uncontrolled intrinsic random characteristic of the integrated circuit during manufacturing variation in order to develop a nonlinear and unique response for each challenge input based on a multiplexer PUF. This is accomplished by using the inherent randomness of the integrated circuit. In this study, an analysis of the different MUX-based PUFs is provided, and it is based on layout-based simulation in CMOS 50nm.rul utilising tools like as Microwind and DSC2.7. The analysis has been tested extensively. Different MUX-based arbiter PUF topologies are compared. Mux PUF's feedforward topology boosts the mux's nonlinearity. With MUX PUF, you get a randomness of 86%, a combination of rarity (79%) and reliability (88%). There is 11% variation between chips under one scenario and 9% variation under another. Nonlinearity is enhanced and mistakes due to the environment are reduced in a feedforward architecture. Mux-Demux PUF is a reconfigurable PUF that allows you to choose the propagation direction.

In paper [47] by Ozturk et al. (2008), the pseudo-random function is implemented with a delay-based pseudo-uniform generator (PUF) based on intrinsic process variation and random switching via input challenge. One- and zero-based logic tristates also feature a third stage, which acts as a high impedance (Z). Output tri-states IF gate is disabled. Since the delay of BUF0 and BUF1 stage is the different reaction time of tristate buffer, a delay unit is implemented with BUF0 and BUF1 stage while allowing the same input to pass. Tristate buffer acts as a barrier between two states, much like an arbiter PUF does except the inverter is removed. BUF0 has more delay than BUF1 because of an extra invert gate. Input lag can be calculated using a mathematical model. The simulated results based on the TSMC 130nm technology library reveal that at 100MHz, mux PUF require 193.67W and tristate PUG require 152.93W, with a reduction in power consumption of 49.

On-line evaluations of the NIST test, the Diehard test, and the Dapra Shield test, among others, are presented in article [48] by Hussain et al. (2014). In terms of hardware predictability and stability, BIST-PUF offers real-time measurement of the desired PUF features. The response generator for BIST PUF is incorporated into a test suite. Quantitative reporting and evaluation of PUF stability and predictability via a web-based assessment tool.

Sensor-based analysis, parametric probing, and multiple probing are the three methodologies used in BIST PUF evaluations. High entropy TRNGs use BIST PUF to eliminate challenge generation bias. The 18.92mW of power that is needed to run the BIST PUF on a Xilinx Vertex-5 based FPGA is eliminated by the stability tool.

A new research by Yao et al. (2013) [49] demonstrates how to use pairwise skews between clock network sinks to recover a secret using PUF techniques. These methods improve the reliability of the clock network in order to isolate individual chip signatures caused by manufacturing flaws. The CMOS clock network was built at the 45nm node. To make the chip more secure, an on-chip clock network is constructed; a delay that may be adjusted increases the entropy of the clock PUF. Multiplexors execute pairwise comparison using an algorithm, and the addition of a return oath helps keep traffic on the network's roads to a minimum. When running a Monte Carlo analysis with 1000 keys, SPICE uses the Inter and Intra hamming distances as a verification metric. Inter-Hamming distances in the PUF configuration are as desired (50%). The ability to reliably reproduce a result depends on the response being invariant throughout a voltage range of 10% and a temperature range of -20°C to 120°C. PUF clocks are twice as reliable than ROPUF ones.

### 2.5.2 Literature Review of Obfuscation Technique

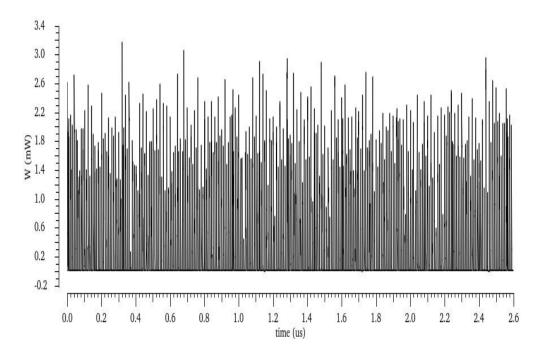

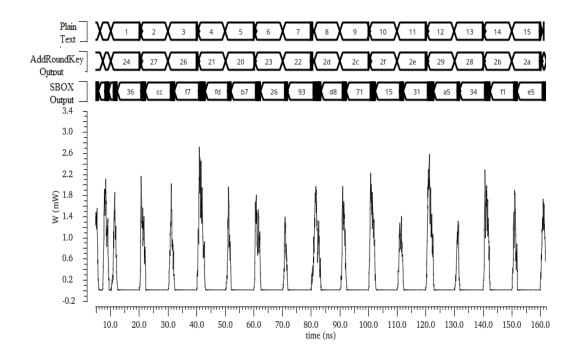

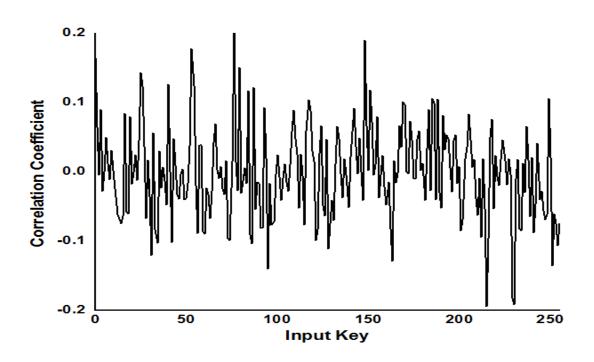

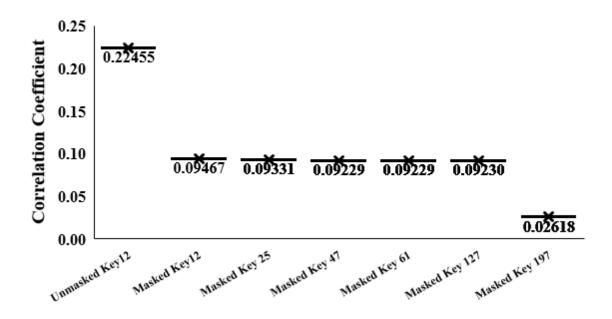

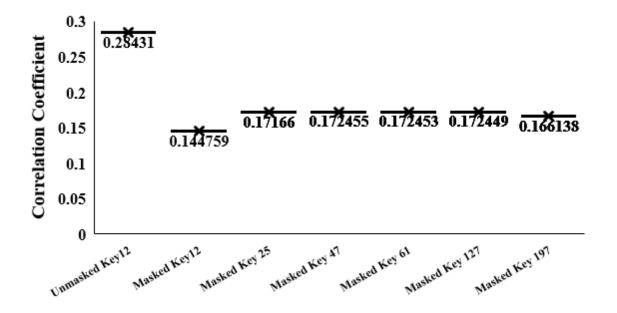

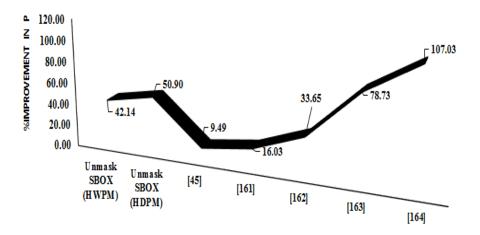

With so many ICs on the market, it's getting harder to keep their secrets safe while keeping their functioning intact (2012) [50]. Overbuilding and hardware Trojan infection are both options for attackers. Therefore, measures are taken to secure the ICs, such as the use of logical obfuscation, PUFs, and IC camouflage. This paper compares and contrasts the efficacy of several methods of logical obfuscation from the perspective of security. By inserting special gates called key gates into the circuits, this method hides the ICs' true performance. Only the right key will unlock the IC's capabilities; using the wrong one will result in the IC's false functionality being shown. These writers also include attacks on logic obfuscation circuits in their article. Having the secret key allows the attacker to deduce the properties of the logic obfuscation. Once the attacker has the secret key, they will be able to decipher the obfuscated gate netlist and replicate the ICs. This paper proposes an approach wherein the adversary applies several input patterns and, by observing the resulting output patterns, learns the secret key. This attack requires both a working IC and the netlist of the obfuscated version. Therefore, logic obfuscation is used to safeguard the key, where key sensitization is accomplished by introducing a gate within the ICs. The key gates are placed in the network in such a way that key value propagation is only allowed under certain forced input conditions. For this reason, brute force is required for an attacker to determine the correct key values. The study detailed a wide variety of assault methods for a variety of setups. Cascade connections between configuration key gates make up the run of key gates. Therefore, the keyspace is diminished and the attack probability is raised thanks to these run-key gates. Once the attacker has reduced the number of key bits, they need to replay the run key gate using single hatred. An attacker can deduce the entire key