# DESIGN AND OPTIMIZATION OF LOW POWER HIGH PERFORMANCE TRIPLE GATE FINFET FOR SUB 22nm TECHNOLOGY

Thesis Submitted for the Award of the Degree of

## **DOCTOR OF PHILOSOPHY**

in

## **Electronics and Communication Engineering**

By

Kalasapati Bindu Madhavi

**Registration Number: 41900188**

**Supervised By**

Dr. Suman Lata Tripathi (21067)

School of Electronics and Electrical Engineering

(Professor)

Lovely Professional University

Transforming Education Transforming India

LOVELY PROFESSIONAL UNIVERSITY, PUNJAB 2023

#### **DECLARATION**

I, hereby declared that the presented work in the thesis entitled "DESIGN AND OPTIMIZATION OF LOW POWER HIGH PERFORMANCE TRIPLE GATE FINFET FOR SUB 22nm TECHNOLOGY" in fulfilment of degree of Doctor of Philosophy (Ph. D.) is outcome of research work carried out by me under the supervision Dr Suman Lata Tripathi, working as Professor in the School of Electronics and Electrical Engineering of Lovely Professional University, Punjab, India. In keeping with general practice of reporting scientific observations, due acknowledgements have been made whenever work described here has been based on findings of other investigator. This work has not been submitted in part or full to any other University or Institute for the award of any degree.

#### (Signature of Scholar)

Name of the scholar: Kalasapati Bindu Madhavi Registration No.: 41900188 Department/school: Electronics and Communication Engineering Lovely Professional University, Punjab, India

ii

### **CERTIFICATE**

This is to certify that the work reported in the Ph.D. thesis entitled "DESIGN AND OPTIMIZATION OF LOW POWER HIGH PERFORMANCE TRIPLE GATE FINFET FOR SUB 22nm TECHNOLOGY" submitted in fulfillment of the requirement for the reward of degree of Doctor of Philosophy (Ph.D.) in the Electronics and Communication Engineering, is a research work carried out by Kalasapati Bindu Madhavi, 41900188 is bonafide record of her original work carried out under my supervision and that no part of thesis has been submitted for any other degree, diploma or equivalent course.

(Signature of Supervisor) Dr. Suman Lata Tripathi Professor School of Electronics and Electrical Engineering Lovely Professional University

#### ABSTRACT

The substantial short channel effects of the typical MOSFET transistor have made scaling progressively challenging. Reduced performance and greater average power consumption result from scaling down the width and length of MOS devices is observed. Therefore, a viable alternative to bulk MOS at the nanoscale is fin-type field effect transistors (FinFET). This device is chosen as the fabrication process followed for a FinFET design is essentially as same as for a traditional MOS transistor.

A double gate or triple gate structure is formed by the gate being positioned on either two or three sides of a channel that is constructed on a substrate. Integrated Circuits are benefitted significantly from the FinFET transistor innovation. Higher current drive capability and Low Power Consumption are the major advantages of multi gate MOSFETs. FinFETs can readily replace MOSFETs in near future due to the similar designing method. The quasi-planar structure of FinFETs is also the part of the double gate (DG) transistor family. As the channel is constructed perpendicular to the wafer and the current trajectory is parallel to it, they are termed as quasi-planar. FinFET through its multi gate terminals tends to provide a variety of design options for the users, including the ability to individually for regulating or shorting them. The thin silicon body and two electrically connected gates of the FinFET are widely recognized for lowering the short channel effects that has proved in the literature.

My work mainly focused on the three technologies, namely 10nm, 18nm and 22nm. By using Cogenda Visual TCAD, the device all the trees technologies of triple-gate FinFET are designed, examined and simulated and evaluated the electrical characteristics. The device performance optimization is done by analyzing drain current characteristics at different channel lengths, oxides, different doping levels and different temperatures for the proposed 10nm and 22nm Triple gate FinFET . The electrostatic behavior is also evaluated which include electrical behavior, surface potential, electron as well as hole density characteristics from device framework that are displayed. A tri gate 18nm FinFET has been implemented for bio sensing techniques. Also in this work, the performance of the 18nm triple gate FinFET device is analyzed with different cavity lengths such as 5nm, 7nm and 10nm. The observation shows that the OFF current becomes small when cavity length decreases. Thus a high sensitive 18nm triple gate FinFET is designed with highly threshold voltage and I<sub>ON</sub>/I<sub>OFF</sub> current ratio with several dielectric constants of both neutral and charged molecules

#### ACKNOWLEDGEMENT

An endeavor of a long period of my Thesis work can be successfully completed only with the advices and continuous support of my well-wishers.

I would like to express my deep and sincere gratitude to my supervisor Dr. Suman Lata Tripathi, Professor, School of Electronics & Electrical Engineering, Lovely Professional University (Phagwara, Punjab) for her constant support, encouragements, constructive discussions and critical analysis of the research topics. Her positive attitude and belief have always motivated me to carry forward my research even during the days of pandemic. I am truly very fortunate to have the opportunity to work with her.

I am indebted to Honorable Chancellor, Pro-Chancellor, the Vice Chancellor, and the successive Deans, LPU, for facilitating the administrative issues involved and encouraging me throughout. I express my heartfelt gratefulness to Head of School, of the School of Electronics and Electrical Engineering, and the staff of Electronics and Electrical Engineering School for their cooperation and support.

I am grateful to the members of Centre for Research Degree Programmes (CRDP) for being in my entire research progress review panel, providing useful suggestions during the period. I am indeed thankful to all anonymous reviewers of my research papers submitted to various High indexed Journals and International conferences, due to which I was indeed able to improve upon the work containing herein.

I extend my deepest gratitude to my husband Mr. T Lakshman Kumar, my in-laws and my children for their love, affection, encouragement and support during this whole journey. Finally, I thank God for blessing me with sound health and strength to carry out my work.

Kalasapati Bindu Madhavi

# TABLE OF CONTENTS

| ABSTRACT            |                                       | iv   |

|---------------------|---------------------------------------|------|

| ACKNOWLEDGEMENT     | ¬                                     | V    |

| TABLE OF CONTENTS   |                                       | vi   |

| LIST OF TABLES      |                                       | ix   |

| LIST OF FIGURES     |                                       | X    |

| LIST OF SYMBOLS     |                                       | xiii |

| LIST OF ABBREVIATIO | DNS                                   | XV   |

| CHAPTER 1: INTRODU  | CTION                                 | 1    |

| 1.1 About Con       | ventional MOSFETs                     | 1    |

| 1.2 Scaling of      | CMOS Technology                       | 4    |

| 1.3 Advanced        | FET devices                           | 5    |

| 1.4 Fin shaped      | I Field Effect Transistors (FinFET)   | 6    |

| 1.5 Short Char      | nnel Effects in MOSFET                | 7    |

| 1.5.1               | Drain Induced Barrier Lowering Effect | 8    |

| 1.5.2               | Effect of quantum tunneling           | 9    |

| 1.5.3               | Surface scattering                    | 10   |

| 1.5.4               | Velocity saturation                   | 10   |

| 1.5.5               | Impact ionization                     | 10   |

| 1.5.6               | Hot electron effect                   | 11   |

| 1.6 FinFET des      | sign and Analysis                     | 12   |

| 1.7 Application     | ns of FinFET                          | 15   |

| 1.8 Physical M      | odels                                 | 16   |

| 1.9 Scaling lim     | its of TG FinFET structure            | 17   |

| 1.10 Chapter Co     | nclusion                              | 19   |

| CHAPTER 2: LITERATU | JRE REVIEW AND METHODOLOGY            | 20   |

| 2.1 Introductio     | n                                     | 20   |

| 2.2 Future Finl     | FETs                                  | 21   |

| 2.3 Existing Fi     | nFETs                                 | 22   |

| 2.4 Biosensor       | FinFETs                               | 29   |

| 2.5 Junctionles     | s FinFETs                             |      |

| 2.6 Research g      | aps identified                        |      |

| 2.7 Objectives      | framed                                | 35   |

| 2.8 Metho                                     | bology followed                                                        | .36 |

|-----------------------------------------------|------------------------------------------------------------------------|-----|

| 2.9 Sequence of steps followed in Visual TCAD |                                                                        |     |

| 2.10 Chap                                     | ter Conclusion                                                         | .40 |

| CHAPTER 3: PERF                               | ORMANCE EVALUATION OF LOW POWER TRIPLE GATE FINFET                     |     |

| FOR SUB 22nm TEC                              | CHNOLOGY NODE                                                          | .41 |

| 3.1 Introd                                    | uction to Sub 22nm Technology                                          | .41 |

| 3.2 Imple                                     | mentation using Visual TCAD tool                                       | .41 |

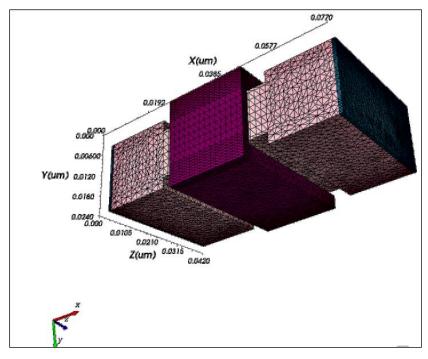

|                                               | 3.2.1 The FinFET Structure                                             | .42 |

|                                               | 3.2.2 Results and Discussions                                          | .45 |

|                                               | 3.2.3 Short channel effects                                            | .49 |

| 3.3 Chapt                                     | er Conclusion                                                          | 50  |

| CHAPTER 4: ANAL                               | YSIS OF PROCESS PARAMETERS VARIATION FOR HIGH STABILI                  | ΤY  |

| 10nm FINFET                                   |                                                                        | 51  |

| 4.1 Introd                                    | uction                                                                 | 51  |

| 4.2 Imple                                     | mentation of 10nm FinFET using Visual TCAD tool                        | 53  |

| 2                                             | 4.2.1 FinFET Device structure with SiO <sub>2</sub>                    | .54 |

| 2                                             | 4.2.2 10nm FinFET Device structure with HfO <sub>2</sub>               | .54 |

| 4.3 Simul                                     | ation Results and Discussions                                          | .55 |

| 4.3.1                                         | Electrostatic behavior of 10nm FinFET                                  | .55 |

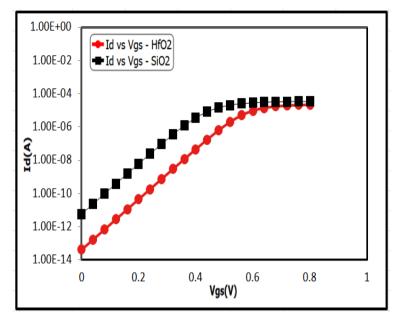

| 4.3.2                                         | V-I Characteristics for 10nm FinFET                                    | .56 |

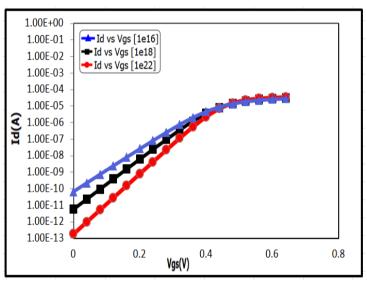

| 4.3.3                                         | Analysis of process parameters of 10nm FinFET                          | .57 |

| 4.4 Chapt                                     | er conclusion                                                          | .63 |

| CHAPTER 5: ELEC                               | TRICAL CHARACTERIZATION OF 10nm FINFET FOR DIFFERENT                   |     |

| CONTACTS AND D                                | DI-ELECTRIC CONSTANTS                                                  | .64 |

| 5.1 Introd                                    | uction                                                                 | .64 |

| 5.2 Perfor                                    | mance evaluation of 10nm FinFET using Visual TCAD tool                 | .64 |

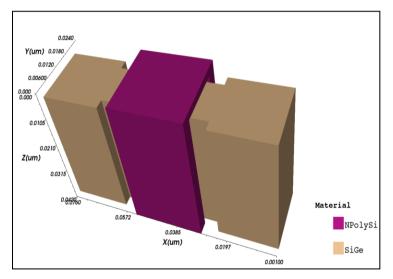

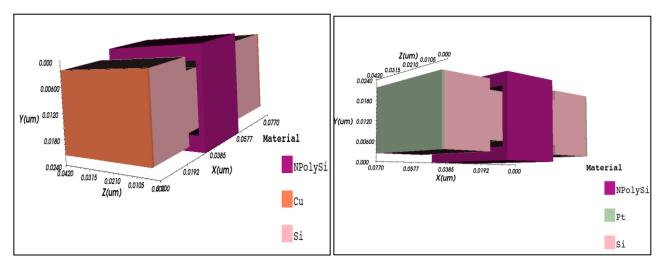

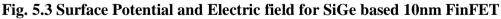

| 5.2.1                                         | SiGe based 10nm FinFET architecture                                    | .65 |

| 5.2.2                                         | 10nm FinFET 3D Structures with different contacts for source and drain |     |

|                                               | Materials                                                              | .65 |

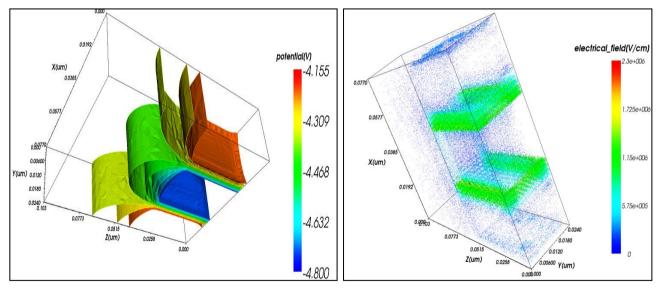

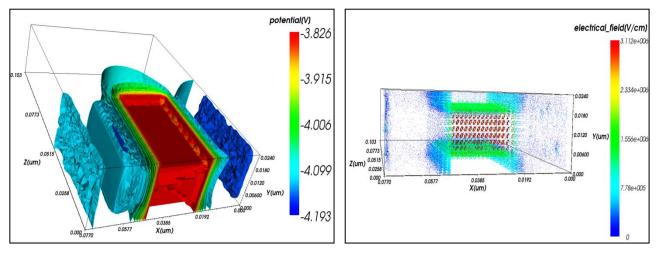

| 5.2.3                                         | Surface Potential and Electric field of 10nm FinFET                    | .66 |

| 5.2.4                                         | Analysis of performance characteristics of 10nm FinFET with different  |     |

|                                               | contacts for source and drain materials                                | 67  |

| 5.2.5                                         | Analysis of Performance characteristics of 10nm FinFET with different  |     |

| (                                                                           | di-elect | ric values                                                 | 68         |

|-----------------------------------------------------------------------------|----------|------------------------------------------------------------|------------|

| 5.2.6 Analysis of Performance characteristics of 10nm FinFET with different |          |                                                            | erent      |

| n                                                                           | nateria  | s for Channel                                              | 70         |

| 5.2.7                                                                       | Analy    | sis of Performance characteristics of 10nm FinFET with     |            |

|                                                                             | differe  | nt materials for Gate                                      | 71         |

| 5.3 Chapter C                                                               | Conclus  | ion                                                        | 72         |

| CHAPTER 6: 18nm T                                                           | RIPLE    | GATE FINFETAS BIOSENSOR                                    | 73         |

| 6.1 Introdu                                                                 | ction .  |                                                            | 73         |

| 6.2 Method                                                                  | dology   |                                                            | 75         |

| 6.3 Perform                                                                 | nance e  | evaluation of 18nm FinFET using Visual TCAD                | 77         |

|                                                                             | 6.3.1    | Proposed 18nm FinFET 3D architecture                       | 78         |

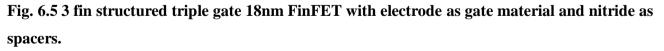

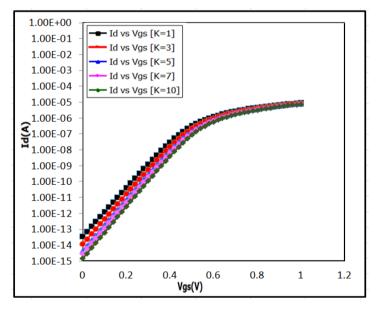

|                                                                             | 6.3.2    | 3D structure of Cylindrical Nano wire                      | 78         |

|                                                                             | 6.3.3    | Performance parameters of proposed cylindrical Nano wire   | 79         |

|                                                                             | 6.3.4    | Proposed 18nm FinFET Bio Sensor architecture               | 80         |

|                                                                             | 6.3.5    | Performance parameters of proposed 18nm                    | triplegate |

|                                                                             |          | FinFET biosensor                                           | 80         |

|                                                                             | 6.3.6    | Electrostatic behavior of 18nm Triple gate FinFET as Biose | ensor85    |

| 6.4 Chapte                                                                  | r Conc   | lusion                                                     |            |

| CHAPTER 7: CONCI                                                            | LUSIO    | N AND FUTURE SCOPE                                         | 90         |

| 7.1 Conclu                                                                  | sion     |                                                            | 90         |

| 7.2 Future                                                                  | Scope    |                                                            | 91         |

| REFERENC                                                                    | ES       |                                                            | 92         |

| LIST OF PU                                                                  | BLICA    | TIONS                                                      | 105        |

# LIST OF TABLES

| Table 1.1 Comparative study of MOSFET and FinFET    14                                          |

|-------------------------------------------------------------------------------------------------|

| Table 3.1 Device model parameters for 22nm FinFET44                                             |

| Table 3.2 Performance Characteristics of 22nm FinFET46                                          |

| Table 4.1 Device model parameters for 10nm FinFET53                                             |

| Table 4.2 Performance characteristics of 10nm FinFET at two different channels                  |

| Table 4.3 Performance characteristics of 10nm FinFET with temperature effect60                  |

| Table 4.4 Performance characteristics of 10nm FinFET with different oxide materials61           |

| Table 4.5 Performance characteristics of 10nm FinFET with different doping levels               |

| Table 5.1 Performance characteristics of 10nm FinFET with different contact materials used for  |

| Source and Drain                                                                                |

| Table 5.2 Performance characteristics of 10nm FinFET with different dielectric values           |

| Table 5.3 Performance characteristics for SiGe and Si based 10nm FinFET71                       |

| Table 5.4 Performance characteristics of 10nm FinFET with different Gate materials72            |

| Table 6.1 Physical parameters of triple gate 18nm FinFET as Biosensor                           |

| Table 6.2 Thickness and permittivity of Biomolecules    78                                      |

| Table 6.3 Application of different bio molecules on Nano wire for cylindrical gate              |

| Table 6.4 Application of different neutral bio molecules on 3 Fin triple gate 18nm FinFET       |

| with respect to di-electric constant                                                            |

| Table 6.5 Application of different neutral bio molecules on 3 Fin triple gate 18nm FinFET       |

| with respect to positive and negative charges                                                   |

| Table 6.6 Application of different neutral bio molecules on 3 Fin triple gate 18nm FinFET       |

| with respect to di-electric constant                                                            |

| Table 6.7 Application of different neutral bio molecules on 3 Fin triple gate 18nm FinFET       |

| with respect to positive and negative charges                                                   |

| Table 6.8 Threshold voltage and $I_{ON}/I_{OFF}$ Ratio at various cavity lengths of 18nm Triple |

| Gate FinFET                                                                                     |

| Table 6.9 Comparison of performance characteristics of Nano wire for Cylindrical gate,          |

| 3 Fin 18nm triple gate FinFET and Bulk CMOS device                                              |

## **LIST OF FIGURES**

| Figure 1.1. MOSFETs (a) n-channel (b) p-channel01                                      |

|----------------------------------------------------------------------------------------|

| Figure 1.2 Double gate MOSFET03                                                        |

| Figure 1.3 Planar Double gate MOSFET03                                                 |

| Figure 1.4 Illustration of Moore's law05                                               |

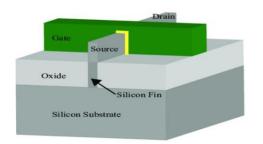

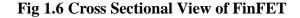

| Figure 1.5 3D Structure of FinFET07                                                    |

| Figure 1.6 Cross Sectional View of FinFET07                                            |

| Figure 1.7 DIBL effect in MOSFET08                                                     |

| Figure 1.8 A typical NMOS switch characteristics and a comparison to an ideal switch09 |

| Figure 1.9 Poly depletion improvement over metal gate09                                |

| Figure 1.10 Surface Scattering Phenomenon in FINFET10                                  |

| Figure 1.11 Hot Electron Effect in FINFET12                                            |

| Figure 1.12 (a) IG FinFET Symbol (b) Short Gate                                        |

| Figure 1.13 Physical Models17                                                          |

| Figure 1.14 Fabrication Process                                                        |

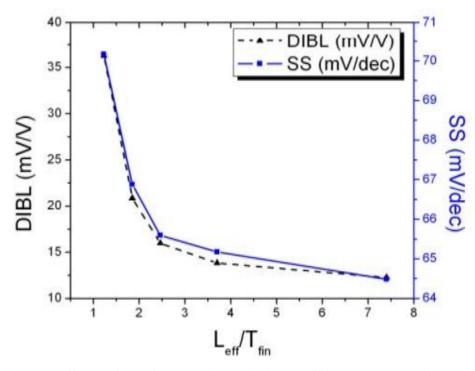

| Figure 1.15 Effects of (Leff/Tfin) ratio variation on SCEs at 22nm of Hfin18           |

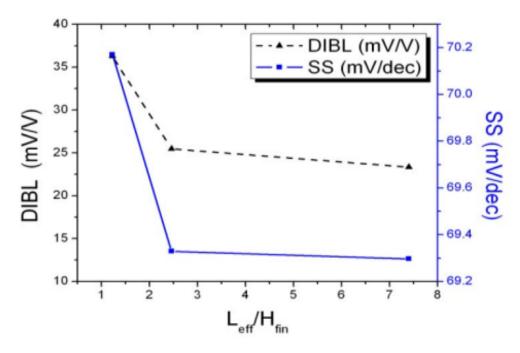

| Figure 1.16 Effects of (Leff/Tfin) ratio variation on SCEs at 22nm of Hfin18           |

| Figure 2.1 Different FinFET Structures                                                 |

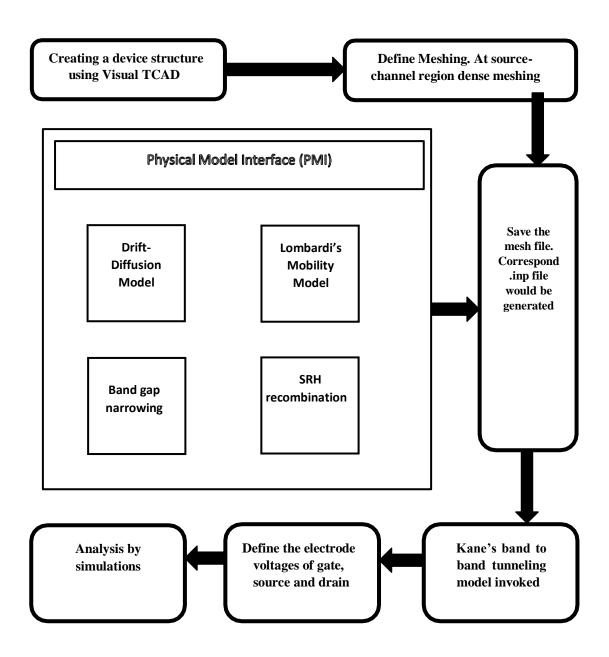

| Figure 2.2 Methodology                                                                 |

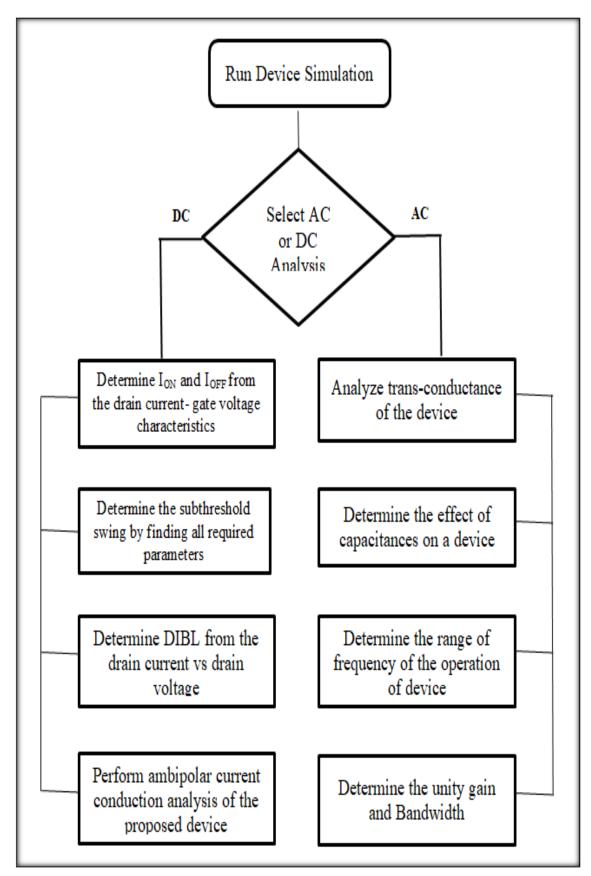

| Figure 2.3 Flow chart for Simulation                                                   |

| Figure 3.1 22nm FINFET fabricated structure                                            |

| Figure 3.2 3D structure of 22nm FinFET                                                 |

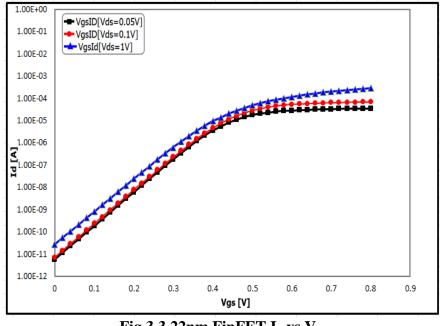

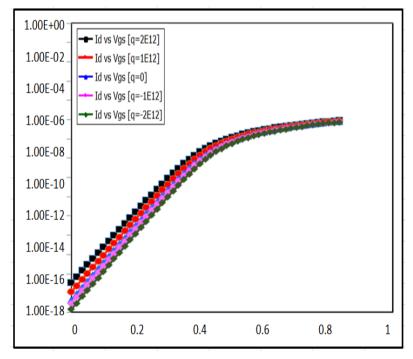

| Figure 3.3 22nm FinFET I <sub>d VS</sub> V <sub>gs</sub>                               |

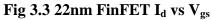

| Figure 3.4 22nm FinFET Id vs Vgs at different temperatures                             |

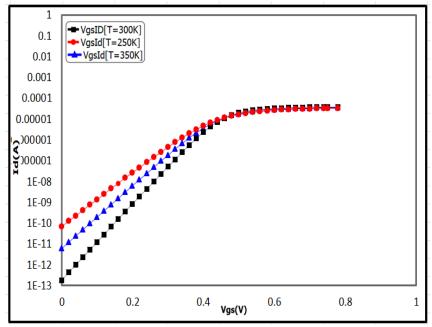

| Figure 3.5 22nm FinFET I <sub>d</sub> vs $V_{ds}$ ( $V_{gs}$ = Const)47                |

| Figure 3.6 22nm FinFET Electric Field(V/cm)                                            |

| Figure 3.7 Surface Potential of 22nm FinFET                                            |

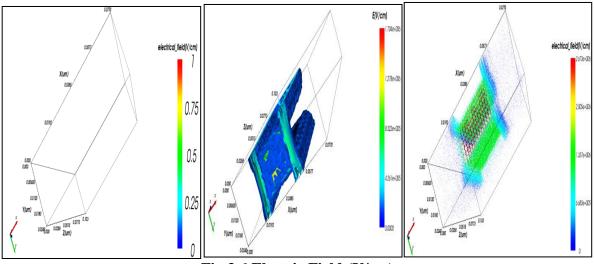

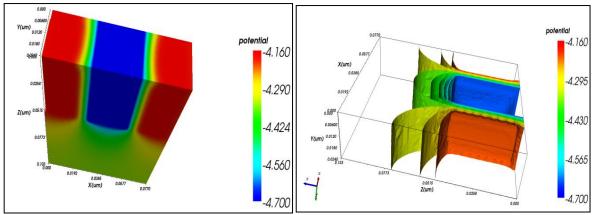

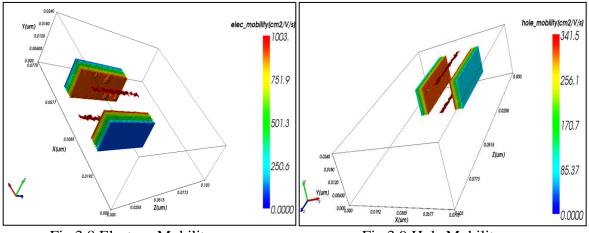

| Figure 3.8 Electron Mobility                                                           |

| Figure 3.9 Hole Mobility                                                               |

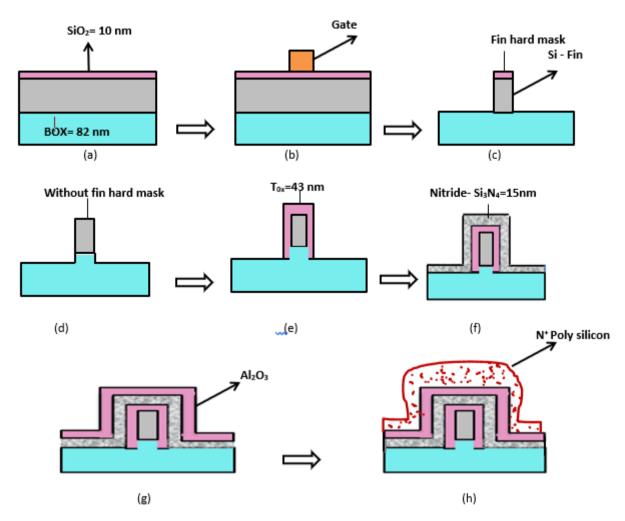

| Figure 4.1 Schematic device fabrication process flow for triple gate 10nm FinFET       |

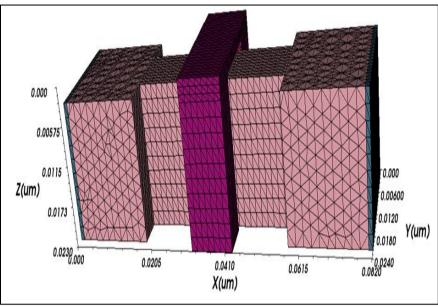

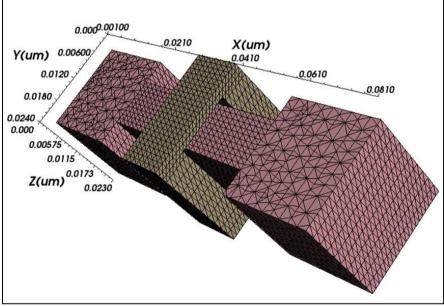

| Figure 4.2 10nm FinFET Device with polysilicon and SiO <sub>2</sub>                    |

| Figure 4.3 10nm FinFET Device with Electrode and HfO <sub>2</sub>                      |

| Figure 4.4 Surface potential of 10nmFinFET55                                           |

|                                                                                        |

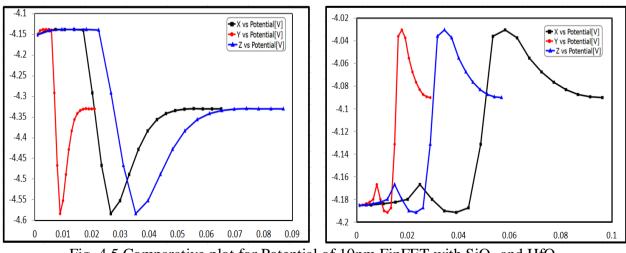

| Figure 4.5 Comparative analysis of Potential for 10nm FinFET with SiO <sub>2</sub> and HfO <sub>2</sub> 55      |

|-----------------------------------------------------------------------------------------------------------------|

| Figure 4.6 Comparative analysis of Electric Field for 10nm FinFET with SiO <sub>2</sub> and HfO <sub>2</sub> 56 |

| Figure 4.7 10nm FinFET I <sub>d</sub> vs V <sub>gs</sub>                                                        |

| Figure 4.8 I <sub>d</sub> vs V <sub>ds</sub> (V <sub>gs</sub> = Const) for 10nm FinFET                          |

| Figure 4.9 $I_d$ vs $V_{gs}$ curve for 10nm FinFET at different channel lengths                                 |

| Figure 4.10 Performance characteristics of 10nm FinFET at different temperatures                                |

| Figure 4.11 Performance characteristics of 10nm FinFET with different oxide materials61                         |

| Figure 4.12 Id vs Vgs Characteristics with different Doping levels                                              |

| Figure 5.1 SiGe Based 10nm FinFET 3D structure65                                                                |

| Figure 5.2 10nm FinFET with Copper and Platinum as source and drain contacts 3D structure66                     |

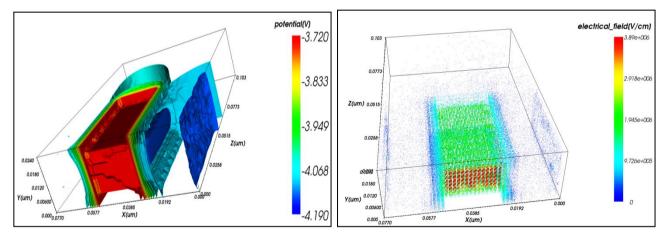

| Figure 5.3 Figure 5.4 Surface Potential and Electric field for SiGe based 10nm FinFET66                         |

| Figure 5.4 Surface Potential and Electric field for 10nm FinFET with Copper as source and drain                 |

| contacts                                                                                                        |

| Figure 5.5 Surface Potential and Electric field for 10nm FinFET with Platinum as source and drain               |

| contacts                                                                                                        |

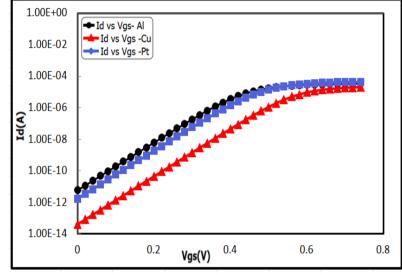

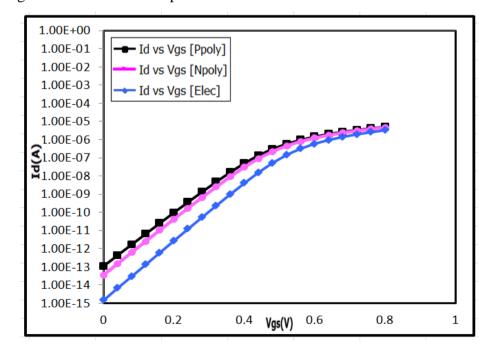

| Figure 5.6 $I_d$ vs $V_{gs}$ characteristics with different contact materials used for Source and Drain68       |

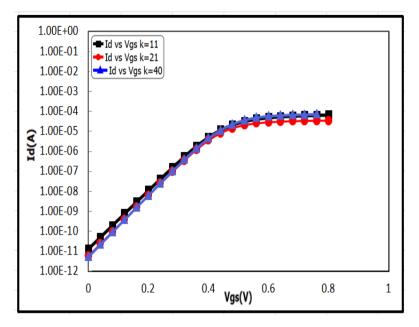

| Figure 5.7 I <sub>d</sub> vs V <sub>gs</sub> characteristics with different dielectric values                   |

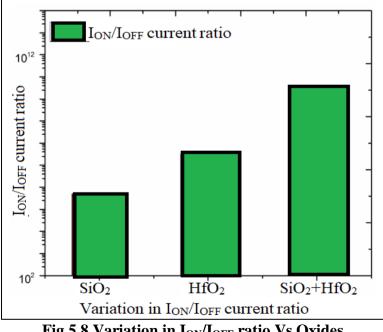

| Figure 5.8 Variation in I <sub>ON</sub> /I <sub>OFF</sub> ratio vs Oxides69                                     |

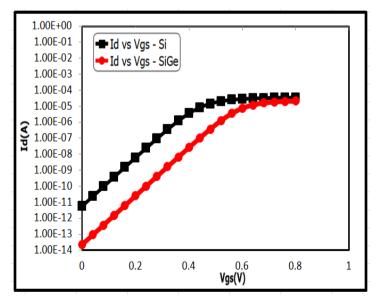

| Figure 5.9 $I_d$ vs $V_{gs}$ characteristics for SiGe and Si based 10nm FinFET                                  |

| Figure 5.10 $I_d$ vs $V_{gs}$ characteristics of 10nm FinFET with different Gate materials71                    |

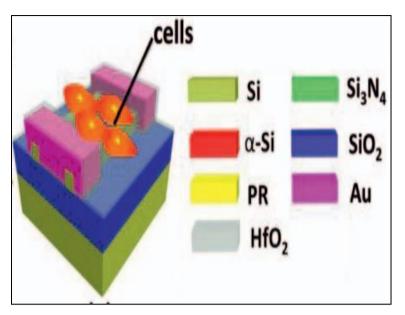

| Figure 6.1 Introduction of cells adherence to the HfO <sub>2</sub> dielectric surface75                         |

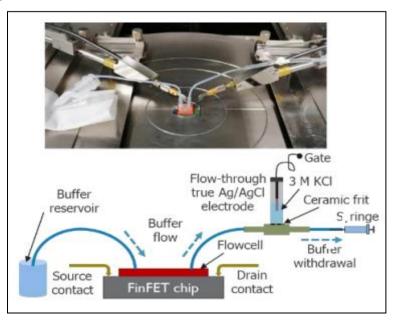

| Figure 6.2 Electrical setup illustrating the fluidic flow path and Ag/AgCl electrolyte gate contact75           |

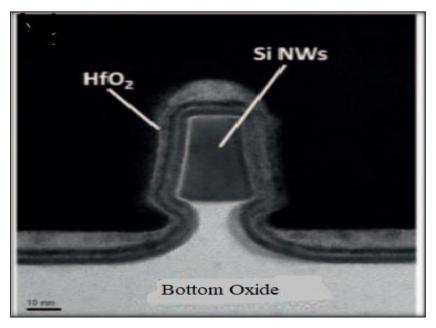

| Figure 6.3 Cross Sectional TEM Image of Si Nanowires Sensors, Conformal and Uniform HfO <sub>2</sub>            |

| Layer                                                                                                           |

| Figure 6.4 Schematic of the Cross Section of the FinFET Sensor used for the simulation of the                   |

| Single-Molecule Signal - 2D76                                                                                   |

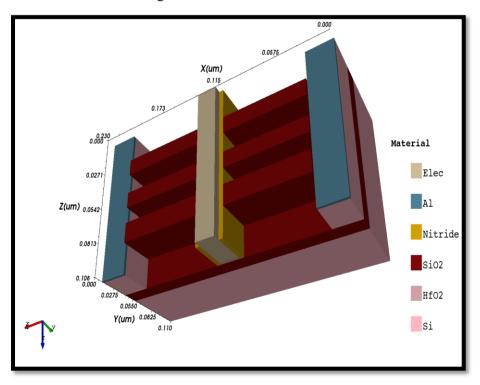

| Figure 6.5 3 Fins structured triple gate 18nm FinFET with electrode as Gate material, nitride as                |

| spacers                                                                                                         |

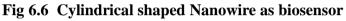

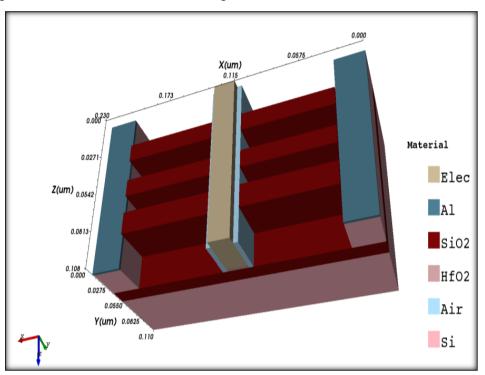

| Figure 6.6 Cylindrical shaped Nanowire as biosensor79                                                           |

| Figure 6.7 Triple gate 18nm FinFET as biosensor                                                                 |

| Figure 6.8 $I_d$ - $V_{gs}$ characteristics with different biomolecules of 18nm triple gate FinFET-based        |

| biosensor For different neutral biomolecules80                                                                  |

| Figure 6.9 $I_d$ - $V_{gs}$ characteristics with different biomolecules of 18nm triple gate FinFET-based        |

| biosensor for both positive and negative charged biomolecules                                                   |

| Figure 6.10 3 fin structured triple gate 18nm FinFET as bio sensor                                        | 83 |

|-----------------------------------------------------------------------------------------------------------|----|

| Figure 6.11 $I_d$ - $V_{gs}$ characteristics with different biomolecules of 18nmtriple gate FinFET- based |    |

| biosensor with Air cavity for different neural biomolecules                                               | 33 |

| Figure 6.12 $I_d$ - $V_{gs}$ characteristics with different biomolecules of 18nm triple gate FinFET-based |    |

| biosensor with air cavity for both charged and neutral biomolecules                                       | 84 |

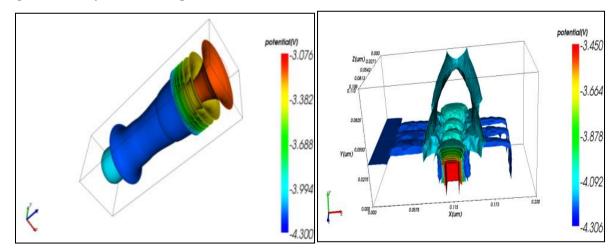

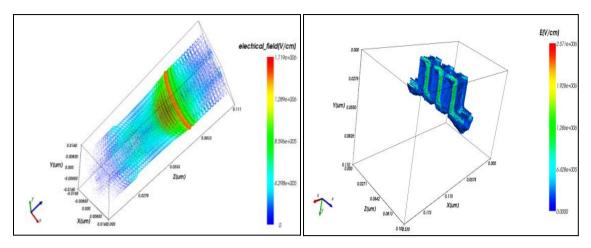

| Figure 6.13 3D view of potential for Nano wire and triple gate FinFET                                     | 85 |

| Figure 6.14 3d view of electric field(v/cm) for cylindrical shaped gate nano wire and 18nm triple         |    |

| gate FinFET                                                                                               | 86 |

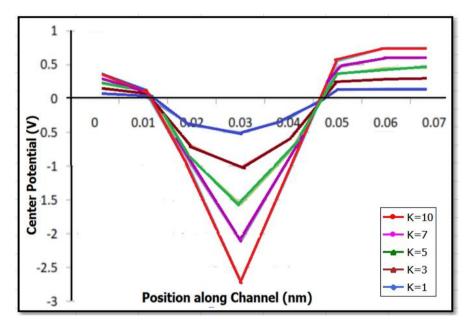

| Figure 6.15 Central Potential varying along with channel for Neutral bio-molecules                        | 36 |

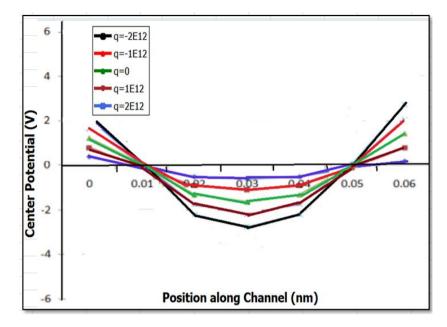

| Figure 6.16 Central Potential varying along with channel for charged bio molecules                        | 87 |

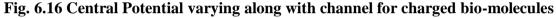

| Figure 6.17 ION/IOFF current ratio vs. Dielectric Constant (K) for different cavity Lengths               | 88 |

# LIST OF SYMBOLS

| I <sub>ON</sub>  | On current                                    |

|------------------|-----------------------------------------------|

| I <sub>OFF</sub> | Off current                                   |

| V <sub>Th</sub>  | Threshold Voltage                             |

| V <sub>GS</sub>  | Gate to source voltage                        |

| V <sub>DS</sub>  | Drain to source voltage                       |

| $L_g$            | Gate length                                   |

| Cox              | Oxide capacitance                             |

| Ps               | Static power dissipation                      |

| P <sub>D</sub>   | Dynamic power dissipation                     |

| V <sub>DD</sub>  | Supply voltage                                |

| C <sub>L</sub>   | Load capacitance                              |

| α                | Switching probability                         |

| f                | Device operational frequency                  |

| e                | Electronic charge                             |

| h                | Planck's constant                             |

| t <sub>ox</sub>  | Oxide thickness                               |

| $t_{Si}$         | Silicon body thickness                        |

| ID               | Drain current                                 |

| Т                | Temperature                                   |

| k                | Boltzmann constant                            |

| SS               | Subthreshold swing                            |

| μ                | Mobility                                      |

| $E_{\perp}$      | Transverse component of the electrical field. |

| Ns               | Doping at the source region                   |

| N <sub>D</sub>   | Doping at the drain region                    |

| N <sub>ch</sub>  | Doping at the channel region                  |

| L <sub>ch</sub>              | Channel Length                           |

|------------------------------|------------------------------------------|

| E                            | Electrical field                         |

| CD                           | Depletion capacitance                    |

| V <sub>DSAT</sub>            | Supply voltage during saturation mode    |

| $V_{D_{LIN}}$                | Supply voltage during linear mode        |

| V <sub>T<sub>LIN</sub></sub> | Threshold voltage during linear mode     |

| V <sub>TSAT</sub>            | Threshold voltage during saturation mode |

| φ                            | Gate work function                       |

| $C_{GS}$                     | Gate-source capacitance                  |

| $C_{GD}$                     | Gate-drain capacitance                   |

| $C_{GG}$                     | Total gate capacitance                   |

| fr                           | Cut-off frequency                        |

| $g_m$                        | Transconductance                         |

| $g_m I_{DS}$                 | Device efficiency                        |

| V <sub>T</sub>               | Thermal voltage                          |

# LIST OF ABBREVIATIONS

| BOX       | Buried oxide layer                                |

|-----------|---------------------------------------------------|

| CMOS      | complementary metal oxide semiconductor           |

| DD        | Drift-diffusion                                   |

| DG FinFET | Double gated Fin Field Effect Transistor          |

| TG FinFET | Triple Gated Fin Field Effect Transistor          |

| DIBL      | drain induced barrier lowering                    |

| GBP       | Gain-bandwidth product                            |

| IC        | Integrated Circuit                                |

| VLSI      | Very Large Scale Integrated Circuit               |

| FinFET    | Fin Field Effect Transistor                       |

| JL FinFET | Junction less Fin Field Effect Transistor         |

| IG FinFET | Insulated Gate Field Effect Transistor            |

| MOSFET    | metal oxide semiconductor field effect transistor |

| NMOS      | N channel metal oxide semiconductor               |

| PDA       | Personal Digital Assistant                        |

| PMI       | Physical Model Interface                          |

| PMOS      | P channel metal oxide semiconductor               |

| QC        | Quantum confinement                               |

| RF        | Radio frequency                                   |

| SCE       | Short channel effects                             |

| SOI       | Silicon on Insulator                              |

| SS        | Subthreshold swing                                |

| TCAD      | Technology computer-aided design                  |

#### **CHAPTER 1: INTRODUCTION**

The familiarity and expansion of MOSFET technology for digital and power approaches are operated by two main benefits over bipolar junction transistors. Among those advantages is the effort to utilize the Metal-oxide semiconductor Field-Effect Transistor (MOSFET) devices in high-frequency switching implementations. Metal-oxide semiconductor Field-Effect Transistors are easy to operate due to their regulated electrode being isolated from current conducting silicon; hence, constant ON current is inessential. After metal-oxide semiconductor Field-Effect Transistors are switched on, their drive current is almost zero. Therefore, regulating the power and corresponding storage period in metal-oxide semiconductor Field-Effect Transistor is highly decreased. This firstly removes the model trade-off in between on-state voltage drop that is inversely proportional to overflow control charge and switch-off period. As an output, MOSFET technology assures the utilization of simpler and highly beneficial drive circuits with important economic advantages compared to bipolar devices. [1]

**1.1 About Conventional MOSFETs:** A MOSFET is the structure consisting of the base material as silicon called as body or substrate. It is the foundation over which whole device would be constructed. Over the substrate, a thin silicon dioxide layer is deposited over the material. The drain and the source are being doped with the same type of the material. The source and the drain terminals are attached through the metallic contacts. The gate terminal is made up of polysilicon and remains insulated from the channel due to the SiO2 layer.[2]

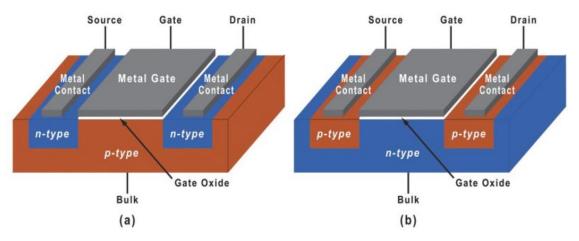

Fig 1.1 MOSFET (a) n-channel (b) p-channel

MOSFETs can be of two categories: n-channel and p-channel Metal-Oxide Semiconductor Field-Effect Transistor. The drain and source regions of an n-channel Metal-Oxide Semiconductor Field-Effect Transistor are greatly doped with n+ type dopants, as a result the current conduction would be due to the electrons as charge carriers. While, in the p- channel MOSFET, the drain and source are both heavily doped with p+ style dopants, as a result the current conduction would be due to the holes as charge carriers [3]. The cross sectional diagram provided in figure 1.1 represents both N-channel and P-channel MOSFETs.

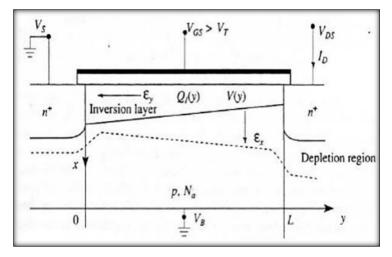

The current conduction from source terminal to drain is controlled by the application of the gatesource voltage. The p-type substrate is used in NMOS transistors and is usually connected to the ground. The voltage at drain side would be greater as compared to the source. Due to the absence of the channel, no current would flow from source to drain if the gate-source voltage was zero. Therefore, we assume the transistors do not operate. If the gate to source voltage is gradually increased, an electric field is developed across the channel; as a result free electrons are attracted at Si-SiO<sub>2</sub> interface. When a gate voltage becomes sufficiently high, a situation is created where the number of free electrons available in the channel is greater than the number of holes in the psubstrate. This phenomenon is referred as an inversion. Now that, the channel has become N-type electrons can move from the source side to the drain terminal, and there would be rise in the drain current.

Similarly the n-type substrate of a PMOS transistor is normally connected to the drain voltage. The voltage at drain side would be lesser than that of the source. If the gate-source voltage is zero or even at the positive voltage, then no current would travel from source todrain, due to absence of the channel. Thus, we assume that the transistor has turned off. When the voltage applied at gate is in negative, an electric field is developed across the channel; as a result free holes are attracted at Si-SiO<sub>2</sub> interface. When a gate voltage becomes sufficiently negative in magnitude, a situation is created where the amount of free holes at the channel outnumbers the electron numbers available in the n-substrate. Again, the channel has become inverted (p-type), it would be feasible for holes to move from the source to the drain terminal, and drain current starts to rise. Thus, whenever the gate voltage applied is higher than the MOSFET's threshold voltage, astrong channel inversion occurs below the gate. The material used to build the MOS structure determines the threshold voltage. There occurs a deposition of holes in PMOS and electrons in NMOS below the gate. Then, the drain voltage sweeps the charge carriers, and hence the current flows in the MOSFET. [4, 5]

Figures 1.2 and 1.3 presents a standard form of ultra thin type of MOSFET and a double-gate MOSFET. The framework of double gate is reversed by continuing the gate leakage current in its inexpensive form.

All gate electrodes in the transistor are self-aligned using standard lithography techniques. Dynamic Metal Oxide Semiconductor logic circuits are utilized in faster Very Large Scale Integrated chips to reach the greatest device implementation. Noise is the main problem in the structure of dynamic logic circuits. In the deep sub-micron region, the noise margin of dynamic logic circuits is inexpensive and highly expected to leads to logical failure. Dynamic logic circuits have various noise sources such as charge sharing noise, leakage noise, crosstalk noise, power and ground noise, substrate noise, etc. [6].

#### Fig 1.2 Double gate MOSFETFig 1.3 Planar Double Gate MOSFET

One of the applications of the MOSFET is that, they act as a switch when operated under cut-off and saturation regions. As an ideal switch, it is expected that when a transistor is turned off, it does not dissipate any power, and when turned on, it would deliver a large amount of current. However, the MOSFET used in practical applications exhibit a small leakage current as well, thus even when turned OFF, some power would get consumed. It is referred as static power dissipation ( $P_s$ ), and is represented by:

In the above equation,  $V_{DD}$  represents the supply voltage and  $I_{OFF}$  represents the leakage current. Besides, When a MOSFET transitions from ON to OFF state or vice versa, a significant power gets consumed as well. This type of power consumption is called as dynamic power dissipation (PD) and is given by the following relation:

$$P_D = V_{DD}^2 C_L \alpha f....(1.2)$$

In the above equation,  $V_{DD}$  represents the supply voltage, *f* denotes operational frequency,  $C_L$  is the load capacitance and  $\alpha$  is the switching probability.  $C_L$  represents the combination of the input capacitances and interconnects capacitances [7].

**1.2 Scaling of CMOS Technology:** Scaling of the standard MOSFET transistor becomes very tough due to its high short-channel impacts. Reducing the width and length of MOS device measurements causes lower implementation and higher average power utilization. Dynamic MOS logic circuits are utilized in faster executed Very Large Scale Integrated chips to reach the greatest device execution.

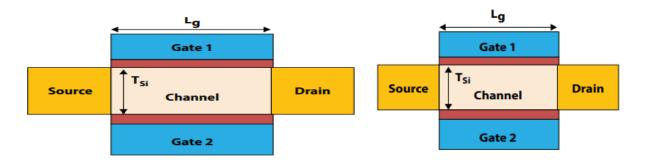

Noise is the main problem in structure of dynamic logic circuits. [8] At present the main goal of the researchers in the MOSFET technology has been to miniaturize the size of the transistors, so that more and more components can be accommodated on a given area. This would also increase the functionality of the given chip, as the number of operations it can perform would increase as represented in figure 1.4.

This exponential trend in miniaturization was predicted by G. Moore, which states: "After every 18 months, the number of components in an integrated circuit doubles". From the past five decades, Moore's law has stood true and this law is being seen as a benchmarkof industry progress [8]. Moreover, the advantages of the CMOS scaling are that the input capacitance of the MOSFET decreases and the current driving capability of MOSFET increase. However, the constraint remains as it is, instead of the fact that the driven current of MOSFETs increases, but because of its limitation due to the short channel effects, the I<sub>OFF</sub> also rises due to the shorter gate length [9].

As a result of the increase in  $I_{OFF}$ , an increase in the power dissipation occurs statistically. The aggressive pace at which the CMOS scaling is done, it is predicted by the researchers that the range of dissipation observed in static power in conventional MOSFETs will soon overcome the range of dynamic power dissipation. The other major limitation of static power dissipation is that it would drain large power from the battery even when the device is turned OFF. This would result in the draining of the battery although the device is not in use.

For a hand held devices like PDA, smart phones, etc., it would be detrimental in terms of their battery performance. Furthermore, the static power dissipation would also result in the heat getting produced in the IC resulting in the temperature rise, although the gadget might have been optimized for the best performance with respect to the ambient room temperature.

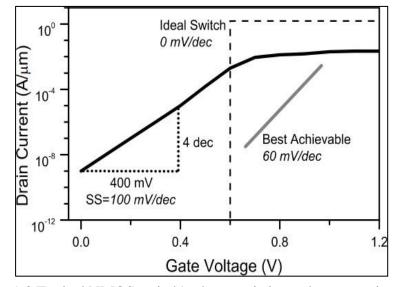

Equations (1.1) and (1.2) provide us some parameters with which the power dissipation could be reduced. However, the fundamental limitation of MOSFET is that: to increase current by tenfold, around 60 mV of voltage is required (ideally). This constraint occurs due to the Maxwell-Boltzmann distribution, and is more popularly referred as "Boltzmann tyranny". It is important in the MOSFET to achieve the current in the range of around ( $\sim 10^4$  to  $10^6$ ) so that OFF state can be distinguished from ON state. Thus, accordingly we can say, that the minimum amount of supply voltage required would be  $60 \times \log (10^6) = 360$  mV. This result also indicates that if the supply voltage is scaled aggressively to a smaller value, it would be extremely difficult to distinguish between the OFF-ON switching. This would prevent the MOSFET to act as a switch. Therefore, we can conclude that due to the "Boltzmann tyranny" the conventional MOSFETs cannot be used as a switch at ultra-low supply voltages. [11]

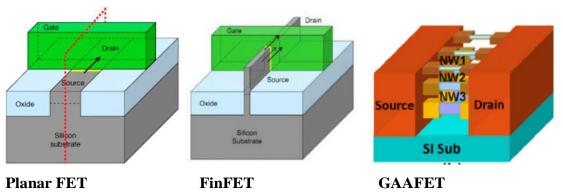

**1.3 Advanced FET Devices:** Advanced mobile and computing systems are innovating at a considerable value of delivering high implementation in lower form factors with great power capabilities. Hence, at the beginning of the integrated circuit industry, model metrics like execution, power, area, value, and time to market stayed the same. [12] Actually, with every recent technology generation, there is Moore's Law about optimizing those aspects to construct the portable feasible transistor size. If Gordon Moore had laid out his law back in 1965, he would have realized about 50 parts of the design. Recent chips contain billions of transistors and model teams' efforts for better, faster, cheaper products. Fin Field Effect Transistor (FIN FET) is a transistor structure initially implemented by Chenming Hu and his colleagues at the University of California at Berkeley that effort to get rid of least kinds of SCE (Short Channel Effect).

At the beginning, Fin Field Effect Transistor was informed to utilize Silicon-On-Insulator (SOI).SOI FIN Field Effect Transistor with thick oxide on top of fin is known as "Double-Gate" and on sides is known as "Triple-Gate" Fin Field Effect Transistors.

**1.4 Fin shaped Field Effect Transistors (FinFET):** A viable alternative to bulk MOS at the nanoscale is fin-type field effect transistors (FinFET). This is so because the fabrication process for a FinFET is essentially the same as for a traditional MOS transistor. A multigate gadget is a fin-shaped field-effect transistor (FinFET). A double gate or triple gate architecture is formed by the gate being positioned on two or three of the channel's sides, in this type of MOSFET it is constructed on a substrate. FinFET transistor approaches in Integrated Circuits have more substantial advantages than the more common planar approach. The main benefits of multi gate MOSFETs are their increased current drive capabilities and reduced power usage. [13]

FinFETs could readily replace MOSFETs in the further future due to the identical fabrication method. The quasi-planar structure of FinFETs makes them members of the double gate (DG) transistor family [6]. They are referred to as quasi-planar because the channel is constructed perpendicular to the wafer and the current trajectory is parallel to it. FinFETs' gate terminals provide a variety of design options, including the ability to individually regulate or short them. The thin silicon body and two electrically connected gates of the FinFET are widely known for suppressing the short channel consequences in the literature. [14]

FinFETs' wide range of design possibilities and improved channel management provide low power solutions with increased noise tolerance. A multi-gate device known as a FinFET is a form of MOSFET (metal-oxide-semiconductor field-effect transistor) which is constructed upon a substrate with gates positioned on two, three, or four of the channel's sides to create a double gate structure[10,15]. When it comes to designing integrated circuits, FinFET transistor architecture has many more important advantages than the more common planar approach. It has been noted that every two years, a particular silicon region doubles in transistor count. Design choices for FinFETs comprise 3D designs that just resemble fins and 2D and 3D architectures that extend over the substrate. FinFET produces superior efficiency with less power loss and lower threshold voltages.

FinFET technology plays a pivotal role in advancing health monitoring and biomedical applications by offering improved power efficiency, miniaturization, high performance, sensitivity, biocompatibility, multi-functionality, flexibility, and signal integrity [16]. These characteristics make FinFETs well-suited for the development of innovative and efficient solutions in the field of healthcare technology.

6

Due to reduced leakage power consumption, additional FinFET may be integrated into an identical chip zone. Therefore, it can be inferred from the development of FinFET technology which will proceed in a specific way. A comparison of triple-gate (TG-FinFET) and planner DG having vertical (DG-FinFET) Fin shaped double-gate architectures is shown in Figures 1.5 and 1.6 In this planar substrate, the channel would perform a small amount of leakage current when the device is in the OFF state. The gate's length in FinFETs is equidistant from the channel's thickness. [17, 18]

#### Fig 1.5 3D Structure of FinFET

FinFETs become more prioritised with the advancement of MOSFETs, as the channel length of the devices has always steadily decreased to allow for the production of small, quick devices. The requirement of FinFETs is for more compact, smaller devices and is highlighted by the MOSFET-related metrics, which also gives the reason that why the MOSFET is an unsuitable option for those applications. The gate electrode's length is its shorter portion, and its breadth is its longer portion. The short-channel impacts become more pronounced when a MOSFET's channel length decreases.

**1.5 Short Channel Effects in MOSFET:** The reasons for the occurrence of short channel effects in the MOSFET are as follows:

(1) Hectron drift characteristics limitations

(2) When the length of the channel is shortened, the threshold voltage changes.

By definition, a short channel device is one in which the channel length **a**nd the depletion region thickness is almost off the same order in magnitude [19 20]. As the channel length decreases, the lateral electrical field increases. For lower field values, the drift velocity is directly proportional to the electrical field, but as the electrical field increases, it begins to saturate. It is known as velocity saturation, and has a major impact on short channel MOSFETs' current voltage characteristics. [21]

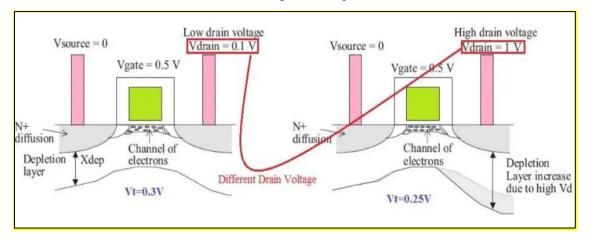

**1.5.1 Drain Induced Barrier Lowering Effect:** In the long channel MOSFET, the source to drain channel is exclusively controlled by the gate voltage. Barrier height at source to channel modulates the gate voltage, causing the electrons to drift from the source to the drain. But, due to CMOS scaling, the channel length is shortened aggressively, thus the drain-channel and the source-channel interface interact with each other. So the gate voltage regulates the height of the obstacle between the source and the channel. The electron energy levels would be reduced, as well as the source to channel barrier height as shown in figure 1.7. This leads to the phenomena called as drain induced barrier lowering (DIBL) effect. The result would be an increase in the leakage current [22-24]. This effect is not so prominent in long channel devices simply because there is no interaction between the two depletion regions.

Fig 1.7 DIBL effect in MOSFET [24]

Because of the heavy doping at drain and source regions of MOSFET, there is an overlap with the p-channel substrate. Since the gate length has already been shortened due to the scaling, so the width of the depletion junctions becomes significant. As a result, the channel is not any longer solely controlled by the applied gate voltage. Besides, the control over the charge on the channel by the gate voltage also reduces. In comparison to a non-depleted MOS capacitor, the voltage required to invert the channel is significantly lower.

The "threshold voltage roll-off" is a well-known short channel effect that exhibits the decrease in threshold voltage as gate length decreases [25]. The potential barrier is decreased although gate-source voltage is lesser than the threshold voltage V<sub>th</sub>, allowing current to flow across source and drain. The subthreshold current (V<sub>gs</sub><V<sub>th</sub>) is the current that flows in the channel under such conditions. A steep transition is required from ON to OFF state in the current, and vice - versa, for any device to act as a switch. However, as discussed at the beginning of the chapter, a fundamental limit for the rate at which current changes in accordance to the applied gate voltage is characterized by thermal current transport across the source-channel barrier height in case of a MOSFET.

An ideal MOSFET switch should do a smooth and abrupt transition from ON position to OFF position, when voltage at gate terminal is lesser to the threshold voltage and should go from OFF state to ON state, when the voltage at gate side is higher than the threshold voltage asshown in Figure 1.8. Subthreshold swing is important feature which measures the degree of abruptness of the transition from ON position of the transistor to the OFF position, and vice versa. It represents the minimum quantity of gate voltage needed to ten-fold the draincurrent [26].

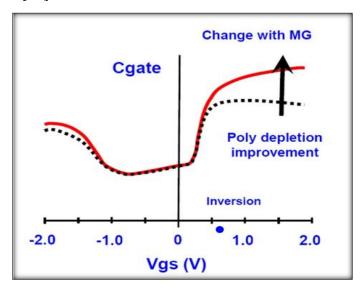

Figure 1.8 Typical NMOS switch's characteristics and a comparison to an ideal switch **1.5.2 Effect of quantum tunneling:** Tunnel effect of the quantum is a quantum desire that arises, if those particles travel along the barrier that, according to assumptions of conventional physics,

would be hard to travel [27].

Fig. 1.9 Poly depletion improvement over metal gate. [27]

A quantum tunneling process has a n source and p drain. The band to band tunneling effect gives the FinFET design a new scaling component. This serves as the method through which this FinFET architecture operates. By overlapping the area of the gate as well as drain and contributing to the high channel doping, the e-h pair produced by a quantum to quantum tunnel effect. [37]

**1.5.3 Surface scattering:** Surface mobility changes from being independent of the electric field to being more longitudinally dependent as the channel length is reduced. Within the restricted inversion layer of a MOSFET, the carrier transport is contained.

Fig. 1.10 Surface Scattering Phenomenon in FINFET [28]

Reduced mobility is a result of surface scattering. Moving parallel to the contact is challenging for the electrons. This is necessary to ensure mean surface mobility is almost equal to average bulk mobility. Electrons that are propelled toward the interface collide with objects, causing surface scattering. [28]

**1.5.4 Velocity saturation:** Trans conductance in saturation state is decreased by velocity saturation. The maximum carrier velocity, or saturation velocity, is reached in the existence of a high electric field.

The transistor enters a state referred to as velocity saturation when this happens. The increasing rate of extremely energetic electron scattering, mostly brought on by optical phonon emission, results in velocity saturation, which lengthens the time that carriers must travel along the channel. [29]

**1.5.5 Impact ionization:** This typically happens as a result of the high electron velocities present in strong longitudinal fields, which can cause impact ionization to produce electron hole pairs. The impact upon silicon and also the ionization of a electron hole pairs results in impact ionization. As a rule, the drain attracts the majority of the electrons; the parasitic substrate power

is created whenever the holes enter the substrate. An N-P-N transistor's base can also function in the space among the source and drain. [30] The source is as same as the emitter, while the drain is as same as the collector.

The usual reverse biasing substrate to the source of P-N junction could conduct if the source collects the holes and the resulting hole current results in a voltage drop of around.6V in a substrate material. Then, in a manner similar to how electrons are injected from an emitter to a base, the substrate can receive electrons from emitter. They can gather adequate energy as they go in the direction of drain to form novel electron hole pairs. If a few of the electrons generated by powerful fields transverse, the situation might deteriorate further, the drain field and enter the substrate, damaging other chipset components. [31]

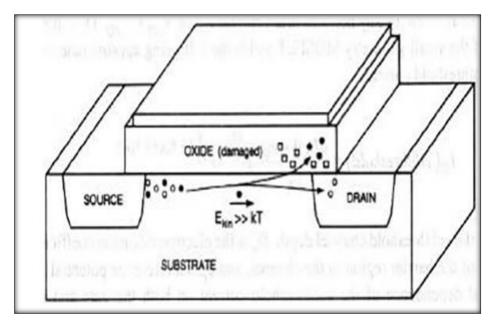

**1.5.6 Hot electron effect:** This phenomenon happens whenever electrons or holes inside a semiconductor device acquire a lot of kinetic energy as a result of a strong electric field. Due to their higher initial mobility, hot electrons are more likely than hot holes. Hot carrier Effects are caused by hot carriers that are introduced or trapped in specific regions and lead to unfavorable device behavior and degradation. [32] The electric field of a channel gets stronger as the gadgets' sizes get smaller. As a result, a significant portion of the channel length is taken up by the high field zone close to the drain terminal.

The hot electron effect results from this, which over time causes the device parameters to degrade. While the device is being scaled down, this impact produces impediments. Peak currents are greater in FinFETs due to higher drive current and device densities. Because of this, the voltage drop on a big SoC depends on the package resonance and the resistance of the power grid. (L), described as identical to IR + L (di/dt), becomes extremely important. Hot electrons play a crucial role in the operation circumstances of hot electron effect premised over FinFET. The creation of hot electrons cannot be stopped because they are constantly available during regular functioning.

The primary cause of the hot electron phenomenon is the intensity of a strong electric field present in channel sector as a result of the systems enlarging size. The gate oxide may degrade as a result.A 100 mV decrease represents about 10% of the supply for planar transistors running at a 1V supply. When a FinFET working voltage is lower, the same 100mV drop represents a considerably larger portion of the supply voltage.

Fig. 1.11 Hot Electron Effect in FINFET [33]

As a result, the chip's operational headroom and noise tolerance are reduced, and for power noise evaluation, higher accuracy standards are required. These requirements include more reliability in power grid extraction, modeling switching currents while taking package/PCB impedance into consideration.

In addition to advantages FinFET provide, Elevated temperatures and issues with electro migration (EM) are caused by the smaller connection sizes, smaller connections, and higher power densities and voltage. Due to EM limitations, designers are that are introduced or trapped in specific region, s substantially more constrained in terms of device dimensions and via/wire routing.

Thermal effects such as self-heating are caused by the elevated FinFET temperatures. The predicted lifetime of electronics and metal layers typically degrades 3X to 5X for every 25°C raise in temperature. It is crucial to consider the outcomes of a precise thermal analysis in order to find real EM weaknesses in a design. The mean time to failure decreases as temperature increases. This necessitates tight coordination along a foundry as well as satisfying its "sign-off" credential criteria having complicated regulations of EM for enhanced process nodes.[33]

#### **1.6 FinFET Design and Analysis:**

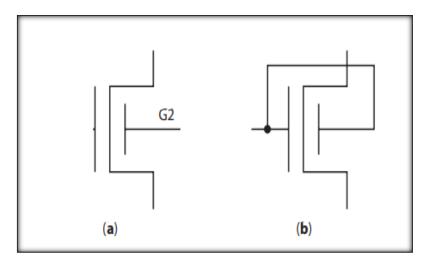

The FinFET device's construction includes a silicon fin. Both of the substrate's edges of a silicon insulator are located of this silicon fin. This gadget typically has two gates that can be activated individually. The FinFET can be configured in a variety of ways, as illustrated in Figure 1.12

Fig. 1.12 (a) IG FinFET Symbol (b) Shorted Gate

This characteristic would change  $V_{gs}$  in an n-type FinFET device. Therefore, swing deterioration as well as drain-induced barrier was reduced in single-gate state in FinFET devices compared to double-gate state. The device's effective electrical width is determined by the height of the fins. Variations in device width are directly related to variations in fin height. The proportion of deviation in device width will be the same for all fin-based devices.

To meet or excel the efficient width of the FinFET device, fins must be extremely tall in size. Fin width control is poor whereas if the chosen fin's diameter is minimal then the range of flexible optical lithography also decreases. Additionally, the process's line edge roughness (LER) causes a significant amount of local fin width variation (LWR).[34] With more fin-thickness, the threshold voltage decreases.

Along with the capacitive coupling among gate as well as channel area, the surface potential for shorter channel lengths is also influenced by the resistance at the drain/fin and source/fin junctions. With enhanced fin thickness, the drain/fin and source/fin junction impedances decrease as breadth of drain/fin and source/fin depletion zones enhances. Whenever a finding, as the film thickness grows, the threshold voltage getting low as a result of an enhancement in gate to surface prospective coupling.

Threshold voltage's impact is minimized with greater fin thickness. The origin and drain resistivity at the junction across the lowering the length of the channel, the capacitive coupling between the gate and channel area, and the surface potential all have an impact. As the breadth of a source and drain/depletion area expands with an increment in fin thickness, the capacitance at a source and drain junction drop. Therefore, it is noted that an increase in fin thickness corresponds to a rise in voltage drop, leading to an augmented coupling between the gate and surface potential.

In the comparison of FinFET and Bulk CMOS at lower supply voltages, the  $I_{ON}/I_{OFF}$  ratio favors the former, whereas at higher supply voltages, the latter exhibits a larger  $I_{ON}/I_{OFF}$  ratio. As a result, the  $I_{OFF}$  of the bulk CMOS is lower than that of the FinFET, and the  $I_{ON}$  of the FinFET is higher than that of the bulk CMOS. To undertake device optimization and help engineers who integrate devices and processes, a TCAD tool is required. In order to evaluate the transistor's random variation efficiency employing noise-like resistivity domain approach using 3-D gadget TCAD simulations, FinFET or Tri-gate transistors below the 20nm technology node must make heavy use of 3D TCAD simulations.[35]

SCE is principally caused by the drain induced barrier lowering (DIBL) consequence, that decreases the edge voltage because channel length decreases. The SOI gadget, however, SCE is affected by thin film thickness, thin film doping thickness, and substrate biasing, as well as covering oxide thickness. SCE is brought on by parasitic electric forces out from source and drain areas, that finally have an impact on the drain current.

It is anticipated that with a MOSFET, the gate will ultimately have control over the channel, hence regulating the drain current. SCE, in which the length of channel is within the sequence of a source and drains sections, originates from gate not having total management over the channel. In a FinFET, the gate completely controls the channel because it surrounds it like a fin In terms of performance metrics; FinFET and bulk MOSFET are compared in Table 1.1. [36]

| Parameter Name | Bulk MOSFET                     | FinFET                                |

|----------------|---------------------------------|---------------------------------------|

|                |                                 |                                       |

| SCE            | In this case, gate has complete | A gate surrounds the channel on all   |

|                | control over the channel.       | sides.                                |

|                |                                 |                                       |

| Quantum        | More power is used, while less  | Low power consumption and high        |

| Tunneling      | channel doping                  | channel doping                        |

|                |                                 |                                       |

|                |                                 |                                       |

| Hot Electron   | Electrons won't get             | The operational circumstances include |

| Effect         | accelerated in this channel     | electrons as a fundamental component. |

|                |                                 |                                       |

|                |                                 |                                       |

## **1.7 Applications of FinFET:**

### **Low-Power Applications:**

In CMOS-based electronic circuit architecture for reduced implementations, the inclusion of FinFET as a possible replacement for conventional MOSFET. With nFinFET and pFinFET in place of traditional MOSFETs, a variety of digital uses could be achieved. TCAD is also useful for the design and evaluation of CMOS-based implementations that use more sophisticated FETs, such as FinFET.[37]

## **FinFET-Based Digital Circuit Design:**

In CMOS VLSI circuit design, the FinFET can take the place of conventional n-MOSFET and p-MOSFET.

It makes it simple to construct a variety of mixtures and sequential circuit implementations for reduced and fast processes. [38]

### **FinFET-Based Memory Design:**

To extend battery life, smart gadgets require huge memories containing SRAM and DRAM cells which employ minimal power. For a smart device such as a laptop, a phone, and various portables and wearables, the layout of SRAM cell featuring 7nm innovation node created is practical. [39]

### **FinFET-Based Biosensors:**

Similar to existing DGMSFET-based biosensors, FinFET may be employed for bio-medical purposes by incorporating a nano gap cavity sector behind sided gate. The newly inserted cavity region exhibits a significant shift in the device's electrical properties due to the dielectric modulation caused by variations in the presence of bio-species. To find out if a biomolecule is present, these alterations can be quantified and observed.

A biosensor built on a GaAs FinFET was suggested, with a cavity region between the source drain and gate regions. It was demonstrated that an enhancement in the cavity region's dielectric constant enhances the surface current in the ON state. Changes in the bio-species existing in the cavity [40] zone affect the dielectric constant's value.

The FinFET transistor architecture has the potential to revitalize the chip market. It would do this by lessening the impact of short channels. About 25 years ago, in the late 1980s, multi-gate MOSFET research began. Hieda et al. suggested the first multi-gate transistor in 1987. Designers learned from it that a silicon-based transistor's entirely depleted body helps enhance switching since the body bias effect is reduced. In the following two years, Hisamoto et al. successfully demonstrated DELTA, a prototype FinFET in bulk silicon. A team from the University of

California, Berkeley, lead by Dr. Chenming Hu, suggested a novel transistor construction in 2004[15] that would lessen leakage current. The Berkeley investigators suggested that by maintaining the gate impedance nearer to the entire channel, a thin-body MOSFET construction would manage SCE and minimize leakage.[4] Some studies have evaluated how the sources of variability affect the device's I<sub>OFF</sub> and I<sub>ON</sub> currents as well as how they affect the threshold voltage.

Random distribution of dopants (RDD) is a primary reason for flexibility in bulk CMOS technology, according to Gold Standard Simulations (GSS) Limited [13]. However, RDD's contribution to FinFET innovation has been drastically decreased as a result of the minimal channel doping. Additionally, FinFETs need to take into account the effects of flaws such as LER and GER.

Metal Gate Granularity (MGG) has been identified using greater metal gates as the primary driver of statistical variability in node 45nm innovation. Due to the metal's polycrystalline form, the surface voltage has experienced working function fluctuations (WFF) due to disturbances that are locally created. WFF is formed in the form its granules are arranged, in accordance with the relying of the metal gate [14]. The gates produced during the optimal manufacturing period for metal entrance hardware feature new metal which is equally distributed and has little variance in functional capacity.

However, in actual production, metal gate devices are typically supplied via metals with a variety of hastily fitted blades, indicating greater  $W_{FIN}$  variability. It is determined that variations in restricted voltage caused by the granularity of the metal entrance are closer to Gaussian distribution and that standard deviation directly correlates to the diameter of the metal grains.

Despite the edge voltage, the strong WFIN influence is seen in the recent investigations, particularly in the fluxes of  $I_{ON}$  and  $I_{OFF}$  [41]

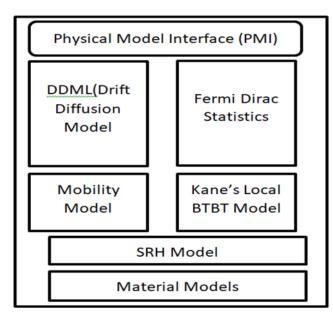

#### **1.8 Physical Models:**

The actual methods of every substance are stacked together in Genius' actual model interface next to the replica structure (PMI). The approaches may be considered using PMI order. Additionally established here are model borders.

#### Fig. 1.13 Physical Models

With the Physical Model Interface (PMI), Genius' main program will be able to access the numerous material-explicit models. In Genius, every supported file contains corresponding dynamic loadable library (DLL) entry located within \$(GENIUS DIR)/lib/index directory. Every DLL record includes every model relevant to that data.

A default model lacking a PMI order will be laid for each type of model. In the event that the customer submits at least one PMI order, Genius would sequentially stack specified illustrated and assign it to the predefined region. An alternative is for the customer to give the PMI model a list of their own unique mathematical and string boundaries. As an illustration, the bounds of the snare design will be organized and stacked in the future commands for the Silicon location. The PMI order may be employed to modify each model's unique bunch bounds. In "Versatility Models," each portability model's representation and the limits of comparison are clear.

**1.9 Scaling limits of TG FinFET structure:** Figure 1.15 depicts the impact of the effectiveness of the gate-length to the fin thickness ratio ( $L_{eff}/T_{fin}$ ). With a falling ratio ( $L_{eff}/T_{fin}$ )., DIBL and subthreshold swing (SS) rise. For the same SCEs, this ratio can be decreased to less than 1.5, unlike DG FinFET.

The SCEs may exceed allowable limits when this ratio gets closer to 1. The TG FinFET architecture has greater scaling possibilities than DG FinFET structure, for this reason.

Fig 1.15 Effects of  $(L_{\text{eff}}/T_{\text{fin}})$  ratio variation on SCEs at 30nm of  $H_{\text{fin}}[42]$

Fig 1.16 Effects of (L<sub>eff</sub>/H<sub>fin</sub>) ratio variation on SCEs at 30nm of T<sub>fin</sub> [42]

Fig.2.7 displays the impact of the effective gate length to fin height ratio upon SCEs. While DIBL and subthreshold swing (SS) rise as the ratio ( $L_{eff}/T_{fin}$ ). falls, the increase is less than it is for the ratio ( $H_{eff}/T_{fin}$ ).). This is because fin thickness, as opposed to fin-height, is highly susceptible to SCEs. It is possible to raise fin height while maintaining an acceptable SCE value to obtain more on-current than fin thickness.[43]

**1.10 Chapter Conclusion:** This chapter concludes that the field-effect transistor technology is the major contribution in developing the modern electronics industry. This technology reduces the short channel effects that promote the continuous upgradation in the FinFET technology. Also this chapter deals about the different types of FinFETs depending on the applications. It focuses on the emerging history of FinFETs and current technology of fin structure, also briefed about the challenges and issues in the technology. Physical models and fabrication process to develop FinFET are clearly explained. And finally applications and the scaling limits of triple gate FinFET structure. The collated understanding of the FinFET device with respect the bulk and SOI MOSFET has been carried out by exploring the various FinFETs, literature survey has done in the next chapter.

#### **CHAPTER 2: LITERATURE REVIEW AND METHODOLOGY**

**2.1 Introduction:** Fin engineering is crucial for balancing the altitude of fin, fin and oxide thickness, and various channel lengths are in need to reduce  $I_{OFF}$  leakage current and increase  $I_{ON}$  current in electronic systems. The source and drain regions are linked to the ends of the vertical silicon fins which make up the channel region in FinFET structures. This vertical fin is surrounded by the gate area. MOS channels have been constructed along the circuit's two sides and on the peak surface of the fin. By building the MOS channel on the surface of a fin wafer rather than in a wafer beneath the gate, the effects of a short channel in the FinFET are avoided.

Additional electrostatic control over the charge carriers exists since the gate is positioned along the channel region. In compared to planar devices, the height of the fin shows a higher current drive per each unit area for the FinFETs. The number of fins in a FinFET transistor is inversely correlated with the current density. Since substantial doping is not necessary in these FinFET, their susceptibility to RDD variations is reduced. [44]

A silicon oxide film's equivalent oxide thickness, which is often expressed in nano meters (nm), is the thickness at which it offers the identical electrical efficiency as the currently being utilized high-performance material. The phrase is frequently used to refer to field effect a transistor that depends on a material pad that acts as an electrical insulator among a gate and a doped semiconducting area. It has been common practice to increase device performance through insulating pad thickness reduction in silicon oxide. Leakage current remained a concern as the insulating pad's thickness neared 5–10 nm, necessitating the use of alternative materials. These novel materials had a reduced equivalent oxide thickness, which allowed them to maintain the required gate oxide thickness to reduce leakage current all while accelerating switching. For instance, a material ten times thicker than silicon oxide with a dielectric constant of 39 (as opposed to 3.9 for silicon oxide) might achieve the same capacitance and good performance while reducing the amount of electron leakage across the dielectric pad[45]. To put it another way, to get equivalent performance while taking into consideration leakage current, a SiO<sub>2</sub> film with a texture one-tenth that of the greater might be required. For gate-all- around devices, hafnium oxide and, more recently, Aluminium oxide are two commonly utilized high-gate dielectrics.[45]

**2.2 Future FinFETs**: RFID (radio frequency identification) as well as IoT (internet of things) systems are among the applications for which the FinFET-based adders are built. If they could be integrated at the server and device ends, artificial intelligence (AI) and the Internet of Things (IoT) can offer advantages and possible prospects. IoT is now integrated with growing AI technology, which aids businesses in making intelligent judgments and avoiding any human interaction. In order to address manufacturing-related challenges, the field of semiconductor devices has recently focused on ML (machine learning) applications. [46]

As an illustration, ML is used to forecast the variability process, estimate the error rate of software, and anticipate the place of the damaged bridge in FinFET. The overall ionizing dosage of this trap refers to its effect on dielectric areas. However, even though the majority of current work concentrates on the impact of displacement damage, this does not necessarily imply that displacement destruction is more substantial than the overall ionizing dose.

Additionally, the impact of the overall ionizing dosage is equally essential, and ML approaches can be used to estimate the impact of a single trap. In line with this development, machine learning (ML) was used for research because this can be used to faithfully reproduce point defect FinFET TCAD information.  $V_{dd}$  is lowered while employing a reduced innovation node, which can reduce dissipation and boost circuit speed. It may be inferred from the simulated findings using the 7nm FinFET innovation node which FinFET-relied adders of 7nm provide adders employing alternative innovation nodes better speed and reduced consumption of power. In portable gadgets where there is a limited budget for power and speed usage, this given adder circuit was employed.

As a result, it is crucial for researching the circuits that use FinFET devices in ultralow power applications. DRAM (dynamic random access memory) specifications are becoming more and more in demand due to block chain, AI & ML, and automotive generations.[46]

## **2.3 Existing FinFETs:**

Kumar H., Jethwa M.K., Porwal A., Dhavse R., Devre H.M., Parekh R [47]: This paper focused on the impact of channel composition on different performance characteristics of FinFET. Channel materials such as semiconductors like Germanium (Ge), Indium Nitride (GaN), and Silicon (Si) have utilized by them in designing process. The impact of the multiple channel materials on different indicators, such as temperature, drain-induced barrier lowering (DIBL), trans conductance ( $g_m$ ), threshold voltage ( $V_{th}$ ), and Subthreshold swing (SS) are analyzed.

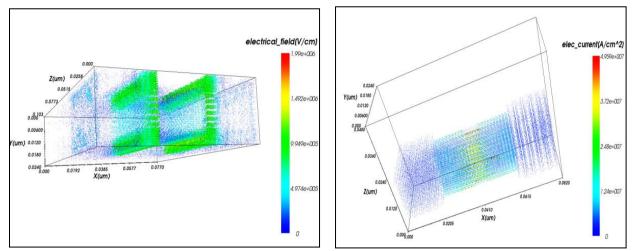

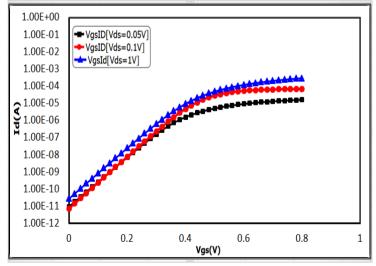

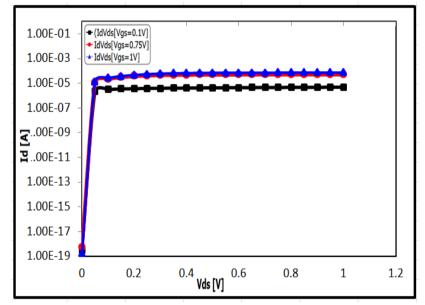

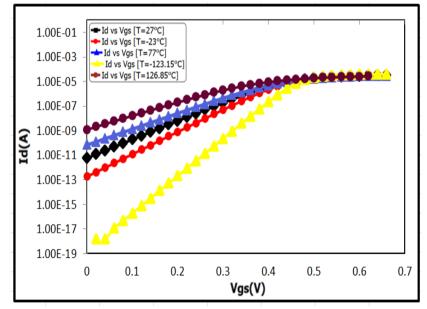

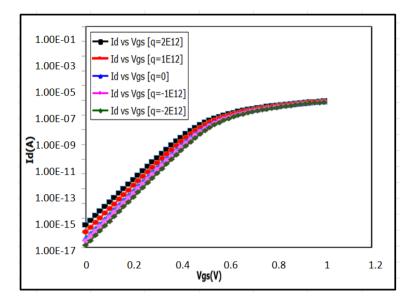

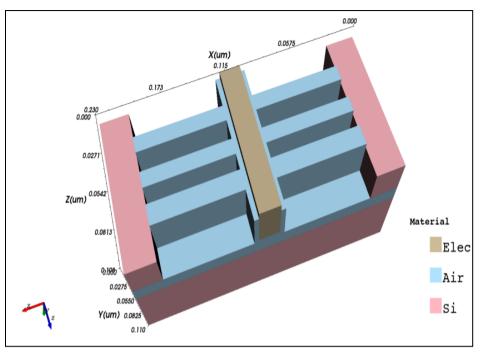

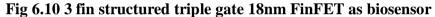

Anuj Chhabraa, Ajay Kumarb, Rishu Chaujara [48]: This study introduces a novel FinFET structure based on GaAs that performs better than existing FinFET structures. Here, for the first time, a thorough examination of device features is investigated along with a stress evaluation of the suggested device structure. In addition, the relationship between linearity and stress effect is examined. Observations indicate that adding stress to FinFET enhanced device efficiency (TGF) to 49.36%, intrinsic gain (Av) to 17.23%, and  $I_{ON}$  to 159.2%, all of which are particularly advantageous for reduced power applications.