# DESIGN AND ANALYSIS OF AN OPTIMIZED ASYMMETRIC MULTILEVEL INVERTER FOR GRID CONNECTED PV SYSTEM

Thesis Submitted For the Award of the Degree of

## **DOCTOR OF PHILOSOPHY**

in

**Electrical Engineering**

By

Devineni Gireesh Kumar

Registration No: 41800726

Supervised By Dr. Aman Ganesh Co-Supervised By Dr. Neerudi Bhoopal

Transforming Education Transforming India

LOVELY PROFESSIONAL UNIVERSITY PUNJAB, INDIA 2022

### DECLARATION

I declare that the thesis entitled "DESIGN AND ANALYSIS OF AN OPTIMIZED ASYMMETRIC MULTILEVEL INVERTER FOR GRID CONNECTED PV SYSTEM" has been prepared by me under the supervision of Dr. Aman Ganesh, Professor, School of Electronics and Electrical Engineering, Lovely Professional University, Punjab, India, and co-supervision of Dr. Neerudi Bhoopal, Professor & Dean Administration, Department of Electrical and Electronics Engineering, B V Raju Institute of Technology, UGC-Autonomous, Narsapur, Telangana, India. No part of this thesis has formed the basis for the award of any degree or fellowship previously.

#### Devineni Gireesh Kumar

**Reg. No: 41800726** School of Electronics and Electrical Engineering Lovely Professional University, Phagwara – 144002 Punjab, India.

Place: Phagwara Date: 19/03/2022

### CERTIFICATE

This is to certify that the thesis entitled "DESIGN AND ANALYSIS OF AN OPTIMIZED ASYMMETRIC MULTILEVEL INVERTER FOR GRID CONNECTED PV SYSTEM" submitted by Devineni Gireesh Kumar to the Lovely Professional University, Phagwara, Punjab, India for the award of the degree of Doctor of Philosophy in Electrical Engineering is a bonafide record of research work carried out by him under our guidance. The contents of this thesis, in full or in parts, have not been submitted to any other Institute or University for the award of any degree or diploma.

#### Dr. Aman Ganesh

Professor, School of Electronics and Electrical Engineering, Lovely Professional University, Phagwara –144002, Punjab, India.

### Dr. Neerudi Bhoopal

Professor & Dean Administration,Department of Electrical & Electronics Engineering,B V Raju Institute of Technology (UGC-Autonomous), Narsapur–502313,Telangana, India.

Place: Phagwara Date: 19/03/2022

### ABSTRACT

Due to the increase in energy demand and growing awareness of the environmental impact, renewable energy harnessing has attracted increased interest. The solar photovoltaic system (SPV) is the most enabling technology for power generation among various available renewable energy sources. The inverter in a grid-connected solar photovoltaic (GCSPV) system is a significant component to convert PV power into AC power since it costs 59% of the total cost. Generally, two and three-level inverters are used in the GCSPV system to reduce the cost of the inverter. However, these inverters suffer from a lack of galvanic isolation between the grid and the PV source and provide constant dv/dt output, which requires a bulky filter to convert the constant dv/dt to a nearly sinusoidal output. As a result, multilevel power converter technology has emerged as a potential solution for medium and high-power applications.

Traditional multilevel inverters (MLIs) such as neutral point clamped (NPC), flying capacitor (FC), and cascaded H-bridge inverter (CHB), are not commercially significant for solar photovoltaic (SPV) systems, where the potential for conversion of energy is already limited (performance in commercial applications is generally less than 20%). Such multilevel inverters are more costly as they require more semiconductor switches, capacitors, dc sources, and clamping diodes. Due to its modular design and simple operation, the CHB-MLI has gained more importance in grid interconnecting applications. However, it necessitates many power electronic switches and separate dc sources in its design, which leads to a significant problem in the control circuit and switching modulation. The researchers have developed various solutions to address the CHB-MLI control complexities. The number of switches and isolated dc sources often increases with the output voltage levels, making CHB-MLI even more complicated. Furthermore, when employing the CHB-MLI for PV applications, it is challenging to handle asymmetric PV sources produced by varying temperature and irradiance.

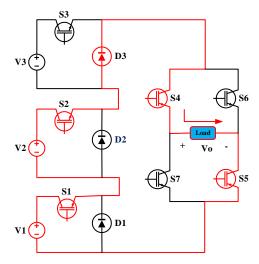

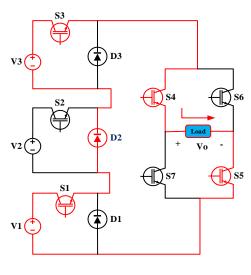

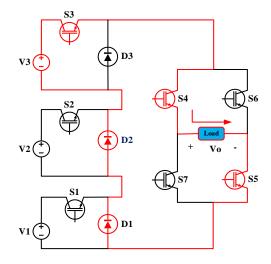

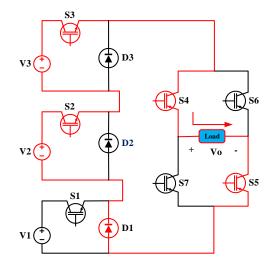

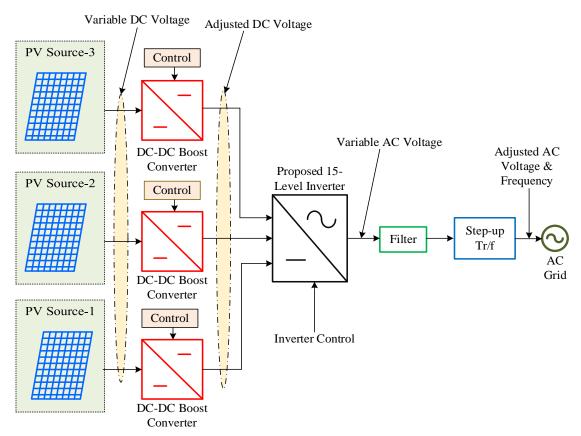

This research aims to develop an optimized asymmetric multilevel inverter for interconnecting the PV sources under the different operating conditions of the grid. The performance of the inverter majorly depends on design topology, switching modulation techniques, and control methodology. The first part of the thesis focuses on the inverter topology. This dissertation presents the design and analysis of a single-phase asymmetric inverter for a grid-connected solar photovoltaic (SPV) system with reduced components. The proposed inverter topology comprises two circuits, namely the primary circuit and the auxiliary circuit. The primary circuit is connected to the asymmetric PV sources and can generate several levels. The auxiliary circuit is an H-bridge circuit that reverses the polarity of output voltage. The proposed MLI utilizes seven power switches, three diodes, and three dc sources for 15-level output. The required number of switches, diodes, and input dc sources of the proposed inverter is compared with existing 15-level topologies. The proposed inverter utilizes a minimum number of switches to generate a more significant number of output voltage levels. It is also free from clamping capacitors, where voltage balancing is a major issue and utilizes very few switching diodes. Hence, the effect of reverse recovery times of the diode on inverter performance is minimal. The metrics considered for the proposed inverter's performance assessment are reduced switches, power losses, THD, and grid integration.

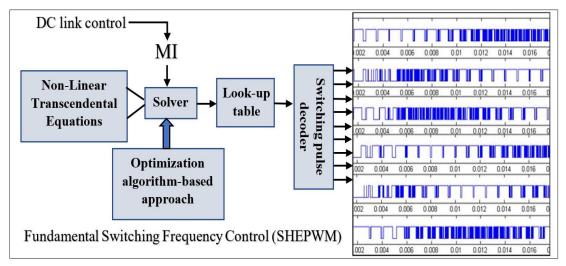

The second part of the thesis focuses on improving the designed inverter performance by switching modulation. This includes both high-frequency (carrier-based) modulation and low-frequency modulations. It is intended to reduce the power losses by reducing the switching losses and conduction losses to improve the efficiency of the inverter. This study explores selective harmonic elimination pulse width modulation (SHEPWM) as low-frequency switching modulation to lower the system power losses while minimizing the selected lower order harmonics at the inverter's output.

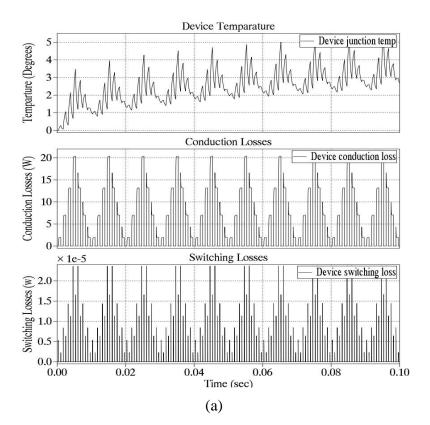

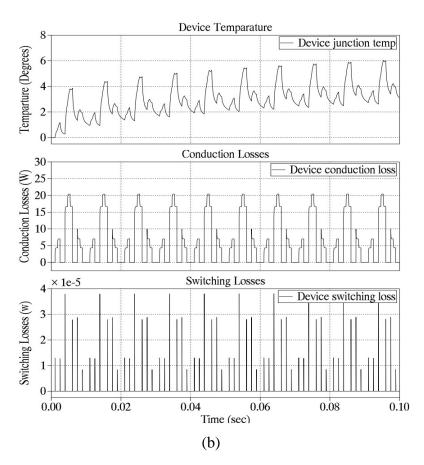

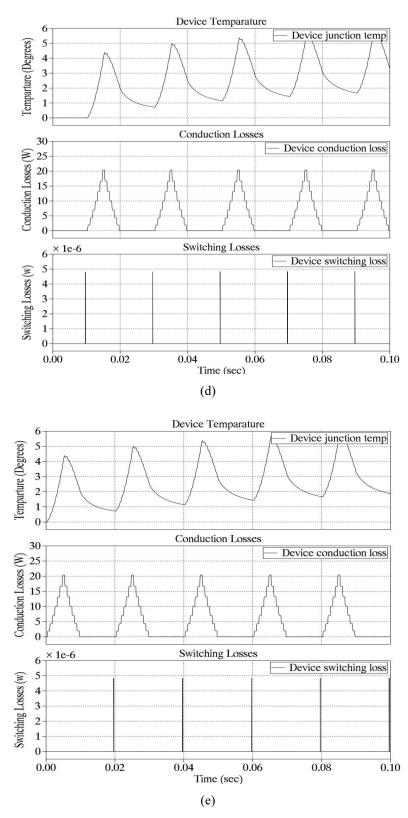

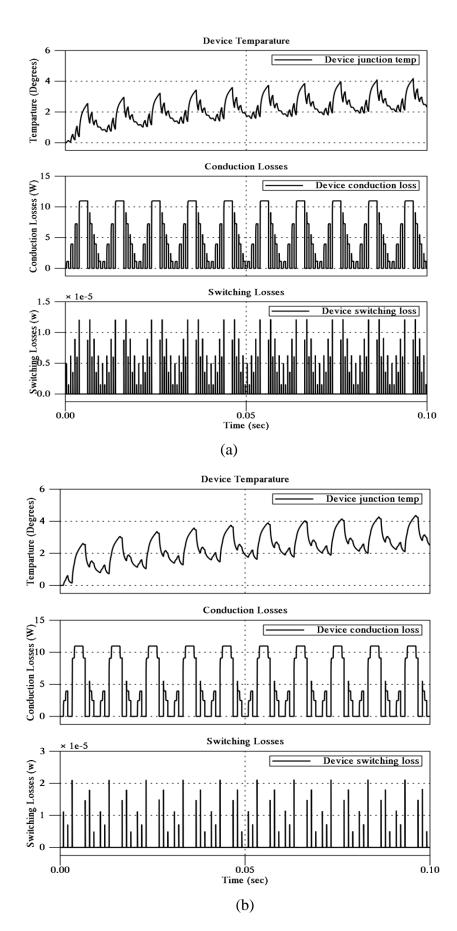

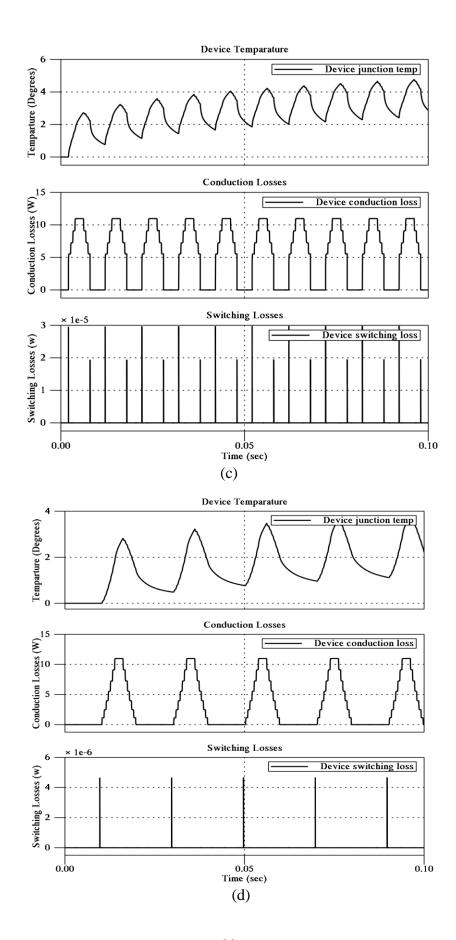

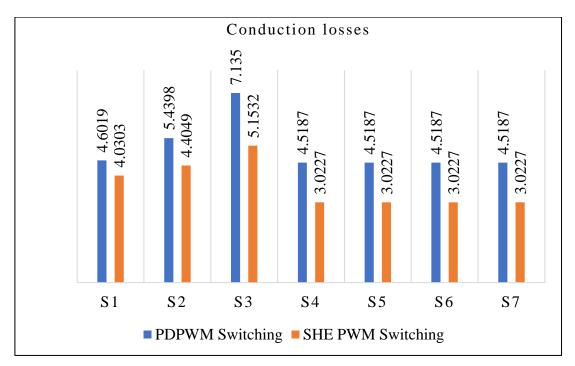

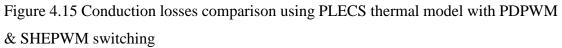

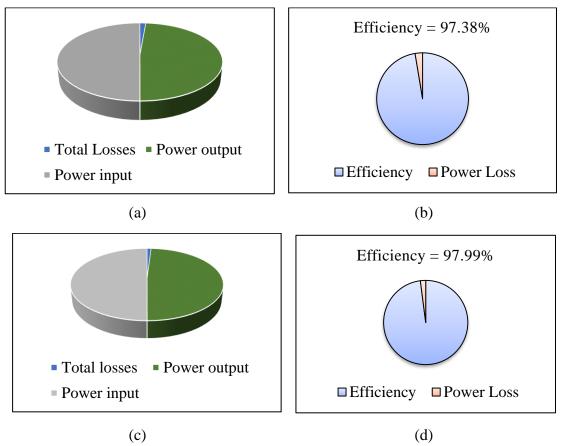

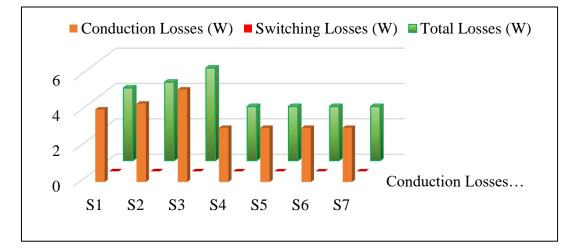

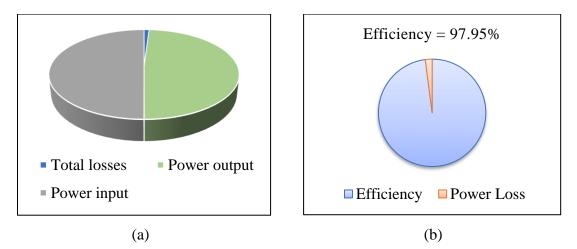

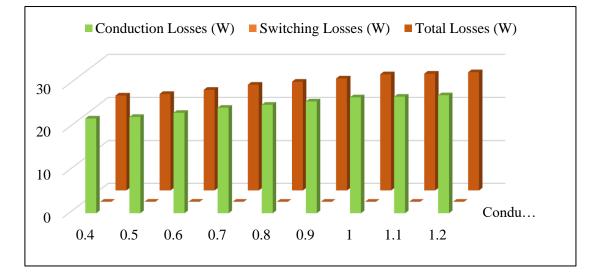

The inverter is simulated using the PLECS thermal model for analyzing the power losses in the proposed 15-level inverter using low switching frequency modulation (SHEPWM) and high switching frequency modulation (phase disposition pulse width modulation - PDPWM). The power losses obtained from the PLECS thermal model with SHEPWM are compared with the PDPWM. The inverter's efficiency is determined in both cases. It is observed that the efficiency of the inverter with SHEPWM (97.99%) is greater than PDPWM (97.38%) switching. Further, the power losses and inverter efficiency are validated with precise models simulated on Simulink using SHEPWM control.

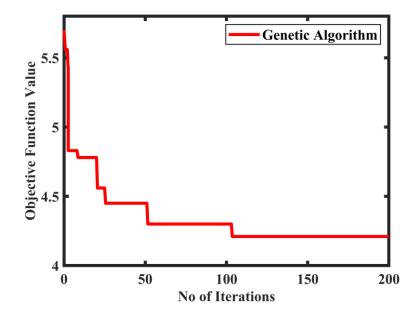

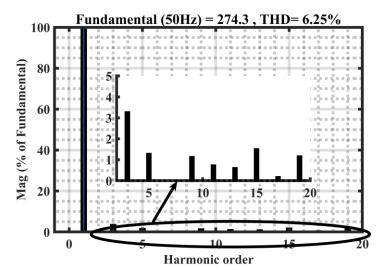

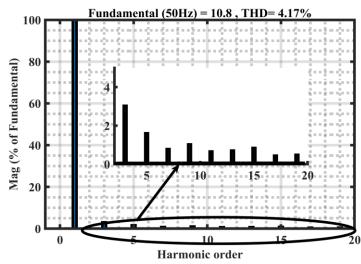

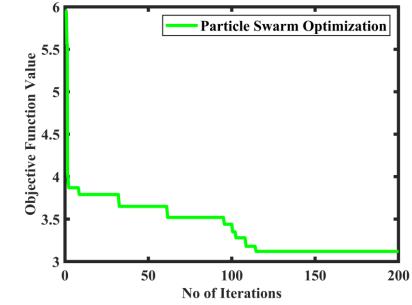

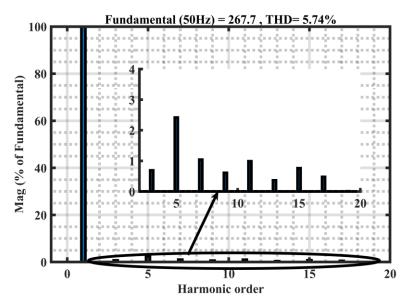

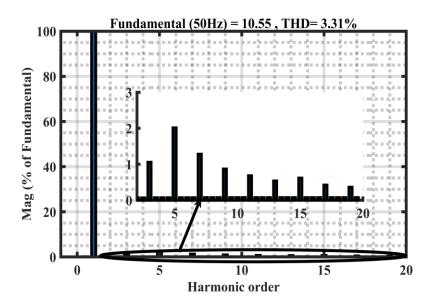

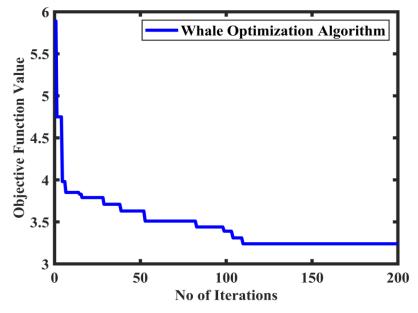

To solve the nonlinear transcendental equations established by SHEPWM, optimization techniques such as Genetic Algorithm (GA), Particle Swarm Optimization (PSO), Whale Optimization Algorithm (WOA), and Harris Hawk Optimization algorithm

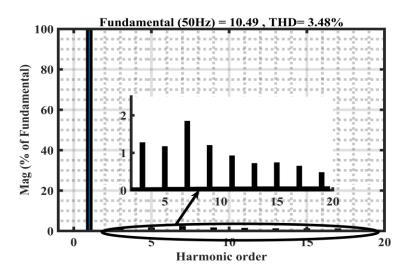

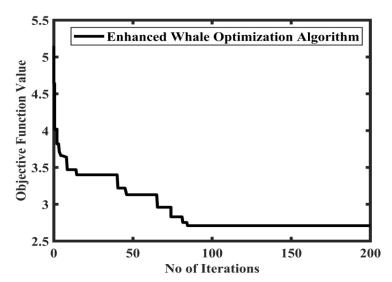

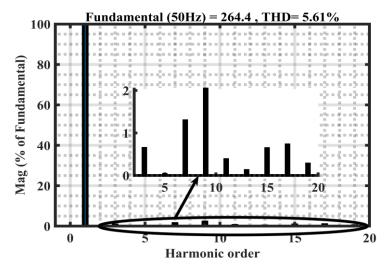

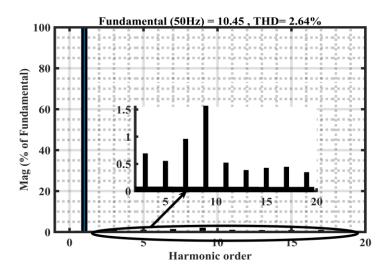

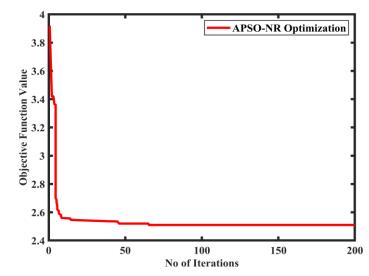

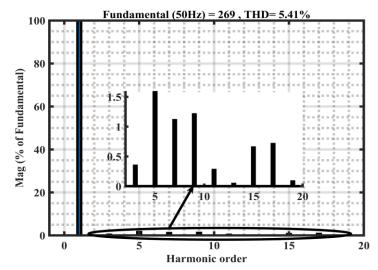

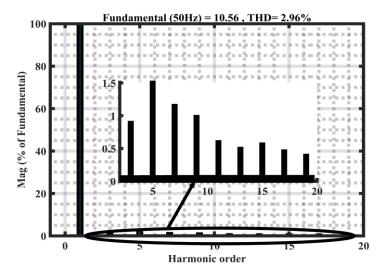

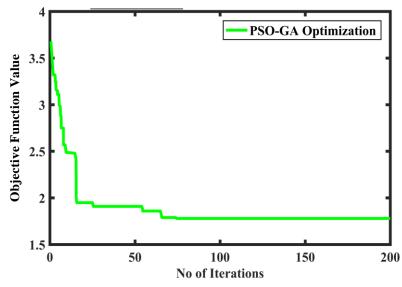

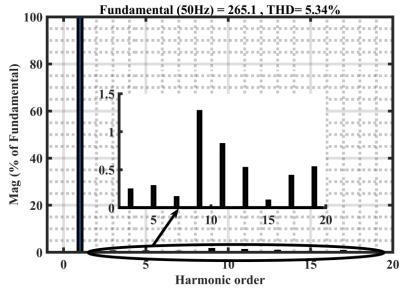

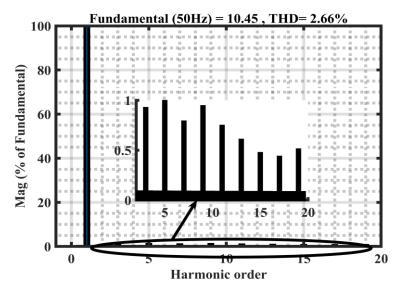

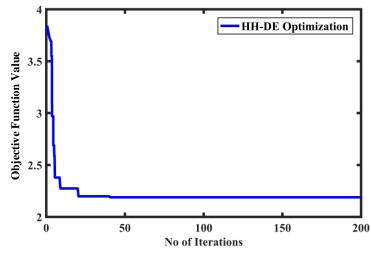

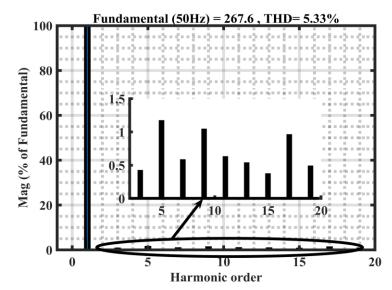

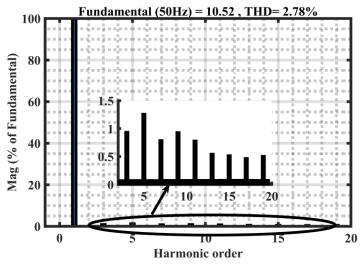

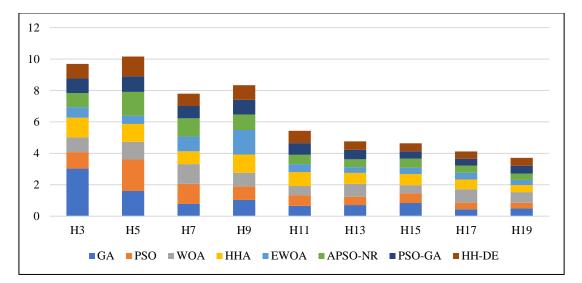

(HHO) were used to the 15-level asymmetric inverter for reducing the THD of output voltage and current as per IEEE519 standard. To improve the algorithm's performance (speed of convergence) and the quality and accuracy of the solution, the hybrid algorithms combine the algorithms above with appropriate ones. The Enhanced Whale Optimization algorithm (EWOA), hybrid Asynchronous Particle Swarm Optimization with Newton Raphson algorithm (APSO-NR), hybrid Particle Swarm Optimization with Genetic Algorithm (PSO-GA), and hybrid Harris Hawk with Differential Evolution (HH-DE) algorithms were applied to the 15-level asymmetric multilevel inverter to improve the performance of the designed inverter. The results of these algorithms are compared in terms of convergence rate, THD of output voltage, and currents. The THD of output voltage using PSO-GA is 5.34%, HH-DE is 5.33%, and the THD of output current using PSO-GA is 2.66%, HH-DE is 2.78%. These results show that the hybrid PSO-GA and HH-DE algorithms give better results than other algorithms implemented without a filter.

The third part of the thesis deals with the use of the proposed asymmetric 15-level inverter for grid integrating the solar photovoltaic system. For this, a grid-connected SPV system is implemented with the proposed asymmetric 15-level inverter. A closed-loop grid-connected controller has been developed with three individual voltage controllers, one overall voltage controller, and a current controller using a PI controller. The gain parameters of the PI controller are adjusted to ensure a steady current and voltage on the grid under variable temperature and irradiance conditions. An LCL filter is employed between the proposed inverter output and the grid to reduce the ripples and improve the waveform quality. The THD & efficiencies are determined to verify the grid-connected solar photovoltaic (GCSPV) system's performance under various irradiance and temperature conditions using PSO-PI, HHO-PI, and hybrid PSO\_GA-PI controllers. The obtained results show that the hybrid PSO\_GA-PI given the minimum THD value of 1.26% at higher efficiency of 95.82% compared to other control algorithms. Finally, the leakage current on the GCSPV system is measured to evaluate the proposed inverter's performance.

### ACKNOWLEDGMENT

This thesis would not have been possible without the support of the glorious people who motivated me during my doctoral study. I am thankful from my bottom of my heart toward the numerous persons who assisted me while conducting this study. First of all, I would like to thank my supervisor, Dr. Aman Ganesh, Professor in School of Electronics & Electrical Engineering, Lovely Professional University, for his worthy guidance, support, and suggestions, in every step of this research project during my Ph.D. journey. He is an optimistic personality with helpful nature, he has always made himself ready to clarify my doubts and it was a great opportunity to work under his supervision. He always shed light whenever I was feeling stuck in my path of research ambitions.

I would like to express my sincere gratitude to my co-supervisor Dr. Neerudi Bhoopal, Professor in Department of Electrical & Electronics Engineering, B V Raju Institute of Technology (UGC-Autonomous), Narsapur, for the continuous support of my Ph.D. study and research, for his patience, motivation, enthusiasm, and immense knowledge. His guidance helped me in all the time of research.

I would like to express my gratitude toward the entire Lovely Professional University family for providing suitable infrastructure and environment for completing my research work in a time-bound manner. Also, I would like to thank the Division of Research & Development and the School of Electronics and Electrical Engineering for their help and encouragement in my entire Ph.D. journey.

I am extremely thankful to the Management, Principal, HOD, and all Faculty members of B V Raju Institute of Technology, Narsapur, India for supporting and providing the necessary inputs.

Words are inadequate to express my gratitude to my father Mr. D. Subbaiah, my mother Mrs. D. Bharathamma, my spouse Mrs. N. Venkata Sireesha, my wards D. Rukesh Chowdary and D. Sourish Chowdary, and other members of my family for their gracious blessings and unfailing support throughout my research work. Finally, I extend my sincere thanks to the almighty who helped me to achieve such a big milestone.

#### Date: 19/03/2022

#### Devineni Gireesh Kumar

## **TABLE OF CONTENTS**

| S. No                                             | Description                                                 | Page  |

|---------------------------------------------------|-------------------------------------------------------------|-------|

| 57110                                             |                                                             | No    |

|                                                   | Declaration                                                 | i     |

|                                                   | Certificate                                                 | ii    |

|                                                   | Abstract                                                    | iii   |

|                                                   | Acknowledgment                                              | vi    |

|                                                   | List of tables                                              | xi    |

|                                                   | List of figures                                             | xiii  |

|                                                   | List of appendices                                          | xviii |

|                                                   | List of symbols & abbreviations                             | xix   |

| CHAI                                              | PTER-1: INTRODUCTION                                        |       |

| 1.1                                               | Introduction                                                | 1     |

| 1.2                                               | Inverter challenges                                         | 5     |

| 1.3                                               | Research objectives & Methodology                           | 8     |

| 1.4                                               | Organization                                                | 9     |

| CHAPTER-2: STATE OF THE ART OF THE GRID-CONNECTED |                                                             |       |

|                                                   | MULTILEVEL INVERTER                                         |       |

| 2.1                                               | Introduction                                                | 10    |

| 2.2                                               | Review of multilevel grid-connected PV inverters            | 10    |

| 2.3                                               | Review of switching and optimization algorithms             | 31    |

| 2.4                                               | Summary of literature                                       | 40    |

| 2.5                                               | Chapter summary                                             | 44    |

| CHAI                                              | PTER-3: DESIGN OF 15-LEVEL ASYMMETRIC MULTILEVEL            |       |

|                                                   | <b>INVERTER &amp; SWITCHING CONTROL</b>                     |       |

| 3.1                                               | Introduction                                                | 46    |

| 3.2                                               | Design of proposed asymmetric 15-level inverter             | 47    |

| 3.3                                               | Comparison with other topologies                            | 55    |

| 3.4                                               | Fundamental switching frequency control (SHEPWM)            | 57    |

| 3.5                                               | Computation of switching angles using Newton Raphson method | 61    |

| S. No |         | Description                                                  | Page |

|-------|---------|--------------------------------------------------------------|------|

| 5.110 |         | No                                                           |      |

| 3.6   | Results | s & discussions                                              | 63   |

| 3.7   | Chapte  | r summary                                                    | 69   |

| CHAI  | PTER-4  | : POWER LOSS ANALYSIS USING PLECS THERMAL                    |      |

|       |         | MODEL & SIMULINK PRECISE MODELS                              |      |

| 4.1   | Introdu | iction                                                       | 71   |

| 4.2   | Switch  | ing control methodology                                      | 71   |

|       | 4.2.1   | Phase disposition pulse width modulation (PDPWM)             | 72   |

|       | 4.2.2   | Selective harmonic elimination pulse width modulation        | 73   |

|       |         | (SHEPWM)                                                     |      |

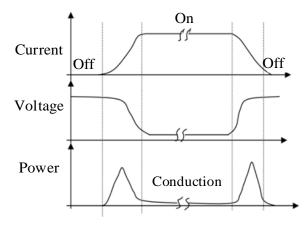

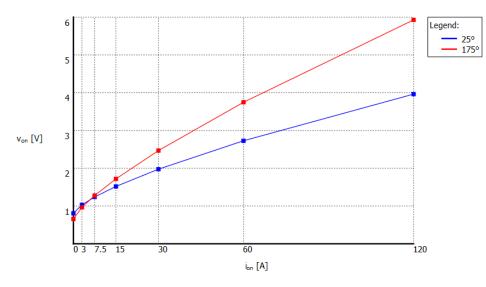

| 4.3   | Power   | loss models for the proposed inverter                        | 74   |

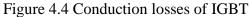

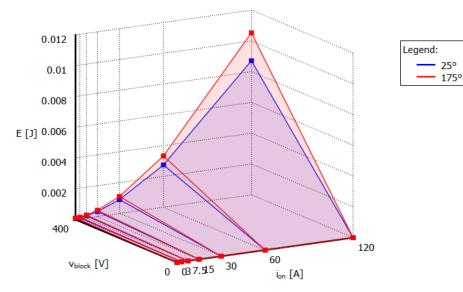

|       | 4.3.1   | Power losses in IGBT                                         | 74   |

|       | 4.3.2   | Datasheet specifications and thermal characteristics of IGBT | 75   |

|       | 4.3.3   | Thermal simulation: Accounting for switching and             | 76   |

|       |         | conduction losses                                            |      |

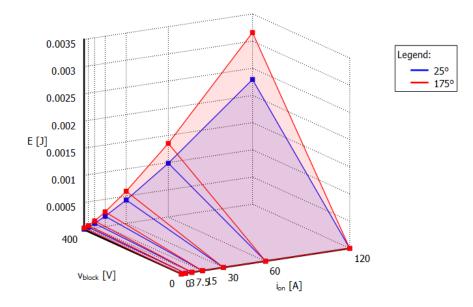

| 4.4   | Electro | -thermal modeling of IGBT using PLECS                        | 77   |

|       | 4.4.1   | Concept of the heat sink                                     | 79   |

|       | 4.4.2   | Calculation of total cycle average losses                    | 79   |

| 4.5   | Simuli  | nk precise curve fitting models for power loss calculation   | 80   |

|       | 4.5.1   | Conduction loss calculation model                            | 80   |

|       | 4.5.2   | Switching loss calculation model                             | 81   |

|       | 4.5.3   | Total power loss calculation model                           | 83   |

| 4.6   | Results | s & discussions                                              | 84   |

|       | 4.6.1   | Power loss analysis using PLECS thermal models               | 84   |

|       | 4.6.2   | Power loss analysis using precise Simulink models            | 93   |

| 4.7   | Chapte  | er summary                                                   | 95   |

| CHAI  | PTER-5  | : THD ANALYSIS OF 15-LEVEL INVERTER USING                    |      |

|       |         | TRADITIONAL & HYBRID SOFT COMPUTING                          |      |

|       |         | ALGORITHMS                                                   |      |

Introduction

5.1

97

| S. No | Description                                                           | Page<br>No |

|-------|-----------------------------------------------------------------------|------------|

| 5.2   | Total harmonic distortion                                             | 98         |

| 5.3   | Control methodology                                                   | 99         |

| 5.4   | Traditional soft computing algorithms to optimize switching angles of | 100        |

| 5.4   | the 15-level inverter                                                 | 100        |

|       | 5.4.1 Switching angle optimization of 15-level inverter using GA      | 100        |

|       | 5.4.2 Switching angle optimization of 15-level inverter using PSO     | 100        |

|       | algorithm                                                             | 105        |

|       | 5.4.3 Switching angle optimization of 15-level inverter using WOA     | 107        |

|       | algorithm                                                             | 107        |

|       | 5.4.4 Switching angle optimization of 15-level inverter using HHO     | 111        |

|       | algorithm                                                             |            |

| 5.5   | Hybrid soft computing algorithms to optimize switching angles of the  | 117        |

|       | 15-level inverter                                                     |            |

|       | 5.5.1 Switching angle optimization of 15-level inverter using EWO     | 117        |

|       | algorithm                                                             |            |

|       | 5.5.2 Switching angle optimization of 15-level inverter using         | 121        |

|       | hybrid APSO-NR algorithm                                              |            |

|       | 5.5.3 Switching angle optimization of 15-level inverter using         | 125        |

|       | hybrid PSO-GA algorithm                                               |            |

|       | 5.5.4 Switching angle optimization of 15-level inverter using         | 128        |

|       | hybrid HH-DE algorithm                                                |            |

| 5.6   | Comparative analysis of THD with different algorithms                 | 130        |

| 5.7   | Chapter summary                                                       | 134        |

| CHAI  | PTER-6: GRID INTEGRATION OF ASYMMETRIC 15-LEVEL                       |            |

|       | INVERTER                                                              |            |

| 6.1   | Introduction                                                          | 135        |

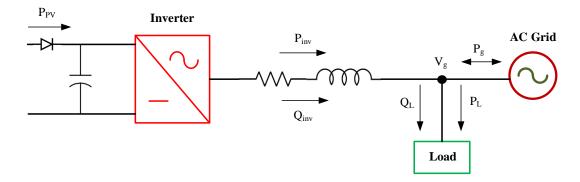

| 6.2   | Methods of grid integration of PV systems                             | 135        |

| 6.3   | Power flow in a single-phase grid-connected SPV system                | 137        |

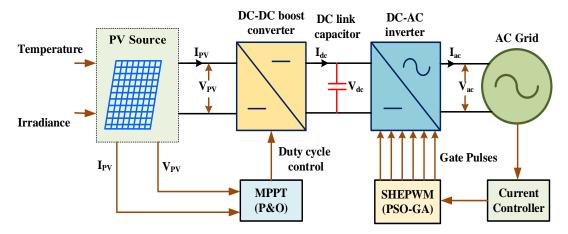

| 6.4   | Proposed two-stage grid-connected SPV system                          | 138        |

| S. No | Description                                                | Page         |

|-------|------------------------------------------------------------|--------------|

| 5.110 |                                                            | No           |

| 6.5   | Implementation of proposed grid-connected SPV system       | 139          |

| 6.6   | Modelling of SPV sources                                   | 141          |

| 6.7   | Design of dc-dc boost converter                            | 145          |

| 6.8   | Design of LCL filter                                       | 147          |

| 6.9   | Control methodology of proposed grid-connected PV system   | 148          |

|       | 6.9.1 Total DC voltage control                             | 149          |

|       | 6.9.2 Grid voltage and grid current control                | 151          |

|       | 6.9.3 Individual DC voltage control                        | 151          |

|       | 6.9.4 SHEPWM control for proposed grid-connected PV sy     | vstem 151    |

| 6.10  | Results & discussions                                      | 153          |

|       | 6.10.1 Simulation of dc sources under variable atmospheric | 154          |

|       | conditions for GCSPV system                                |              |

|       | 6.10.2 Implementation of PSO-PI controller for GCSPV syst  | tem 159      |

|       | 6.10.3 Implementation of HHO-PI controller for GCSPV sys   | stem 161     |

|       | 6.10.4 Implementation of a hybrid PSO_GA-PI controller fo  | or 162       |

|       | GCSPV system                                               |              |

| 6.11  | Chapter summary                                            | 166          |

| CHAF  | PTER-7: CONCLUSION & FUTURE SCOPE                          |              |

| 7.1   | Conclusion                                                 | 168          |

| 7.2   | Future scope                                               | 170          |

| REFE  | ERENCES                                                    | 171          |

| APPE  | ENDICES                                                    |              |

| A.1   | Parameters of optimization algorithms                      | 188          |

| A.2   | Specifications and parameters of PV module                 | 192          |

| A.3   | Relationship between dc input power and ac output power    | 192          |

| A.4   | Components comparison of various asymmetric MLIs with p    | proposed 194 |

|       | MLI for n-levels                                           |              |

| A.5   | Rating and specifications of the proposed inverter         | 195          |

| LIST  | OF PUBLICATIONS                                            | 196          |

## LIST OF TABLES

| Table<br>No | Description                                                                                               | Page<br>No |

|-------------|-----------------------------------------------------------------------------------------------------------|------------|

| 2.1         | Review of grid-connected PV inverters                                                                     | 14         |

| 2.2         | Review of optimization algorithms & switching algorithms                                                  | 32         |

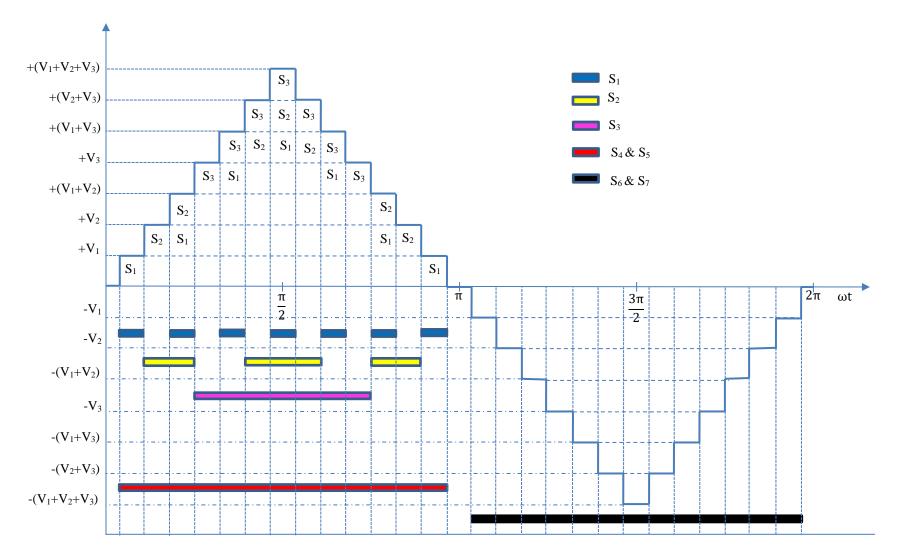

| 3.1         | Choice of dc sources for suggested topology                                                               | 49         |

| 3.2         | Asymmetric switching sequences and output voltage levels of proposed 15-level inverter                    | 50         |

| 3.3         | Comparison between switching control methods with SHEPWM                                                  | 60         |

| 3.4         | THD comparisons of proposed inverter with existing topologies NR Method                                   | 69         |

| 4.1         | Datasheet specifications of IGBT                                                                          | 75         |

| 4.2         | Power loss analysis using PLECS thermal model with PDPWM & SHEPWM switching control                       | 90         |

| 4.3         | Power loss analysis using precise Simulink models with SHEPWM control                                     | 93         |

| 4.4         | Power losses with the variation of modulation index by SHEPWM control                                     | 95         |

| 5.1         | Switching angles and THD of output voltage with the variation of modulation index using genetic algorithm | 102        |

| 5.2         | Switching angles and THD of output voltage with the variation of modulation index using PSO               | 105        |

| 5.3         | Switching angles with the variation of modulation index using<br>the whale optimization algorithm         | 110        |

| 5.4         | Switching angles with the variation of modulation index using<br>Harris hawk optimization algorithm       | 115        |

| 5.5         | Switching angles with the variation of modulation index using<br>Enhanced whale optimization algorithm    | 119        |

| 5.6         | Switching angles with the variation of modulation index using<br>hybrid APSO-NR algorithm                 | 123        |

| Table<br>No | Description                                                        | Page<br>No |

|-------------|--------------------------------------------------------------------|------------|

| 5.7         | Switching angles with the variation of modulation index using      | 126        |

|             | PSO-GA algorithm                                                   |            |

| 5.8         | Switching angles with the variation of modulation index using      | 129        |

|             | PSO-GA algorithm                                                   |            |

| 5.9         | Optimal switching angles and corresponding THD resulted from       | 131        |

|             | different optimization algorithms for 15-level multilevel inverter |            |

| 5.10        | Performance analysis of proposed inverter with different           | 131        |

|             | optimization algorithms                                            |            |

| 5.11        | Magnitudes of harmonic voltages                                    | 132        |

| 5.12        | Magnitudes of harmonic currents                                    | 133        |

| 6.1         | Specifications of the PV fed grid-connected system                 | 153        |

| 6.2         | Specifications and parameters of PSO                               | 160        |

| 6.3         | Specifications and parameters of HHO                               | 161        |

| 6.4         | Specifications and parameters of hybrid PSO-GA                     | 163        |

| 6.5         | Comparison of gain parameters and THDs of proposed GCSPV           | 165        |

|             | system                                                             |            |

| 6.6         | Efficiency of the proposed GCSPV system with different             | 165        |

|             | controllers                                                        |            |

| 6.7         | Comparative analysis with other techniques proposed in the         | 166        |

|             | literature                                                         |            |

## LIST OF FIGURES

| Figure<br>No | Description                                                             | Page<br>No |

|--------------|-------------------------------------------------------------------------|------------|

| 1.1          | Common grid-connected solar PV system                                   | 2          |

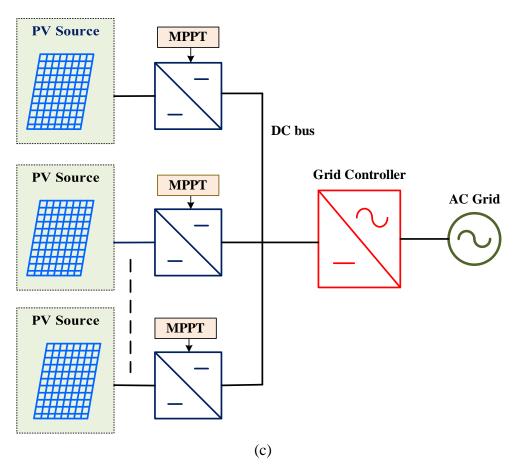

| 1.2          | Different configurations of grid-connected PV inverters                 | 3          |

| 1.3          | Near sinusoidal staircase waveform of multilevel inverter               | 4          |

| 1.4          | Classification of multilevel inverters presently used in the industries | 5          |

| 1.5          | An asymmetric inverter with a reduced number of switches                | 7          |

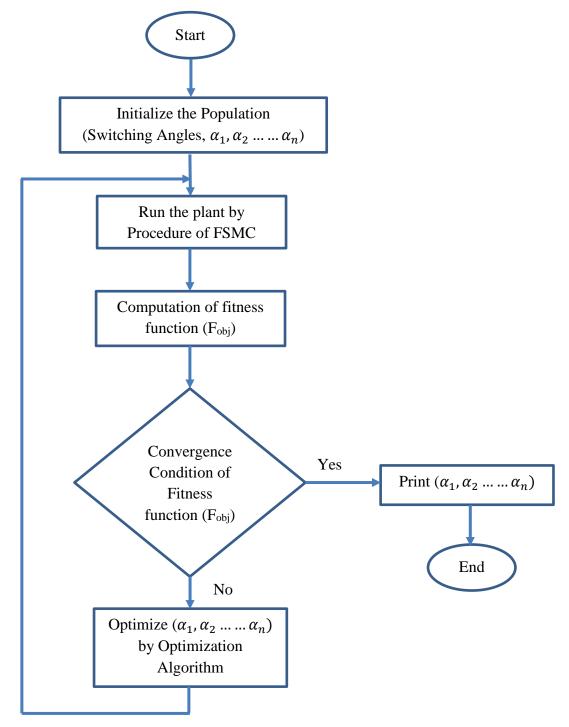

| 2.1          | Process of finding optimal switching angles of the inverter             | 43         |

|              | using optimation algorithms                                             |            |

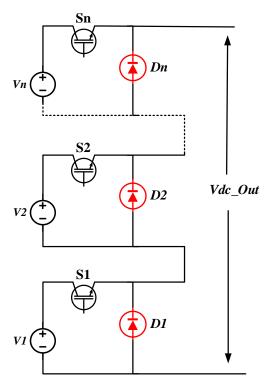

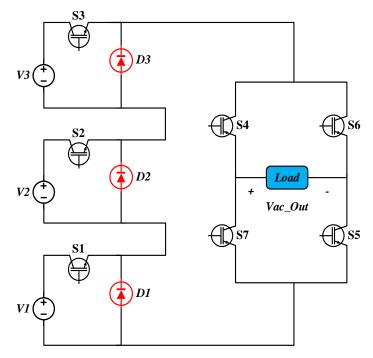

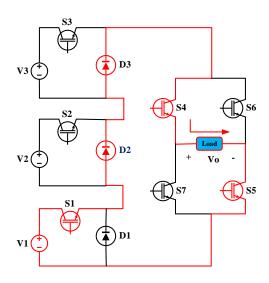

| 3.1          | Basic cell structure                                                    | 47         |

| 3.2          | 'n' cell cascaded primary circuit                                       | 47         |

| 3.3          | Auxiliary circuit                                                       | 48         |

| 3.4          | Proposed 15-level asymmetric inverter                                   | 48         |

| 3.5          | The approximated waveform of the proposed inverter and its              | 51         |

|              | switching pattern                                                       |            |

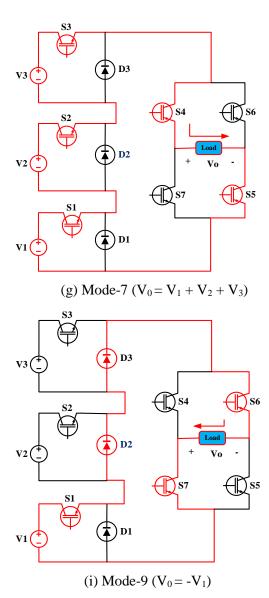

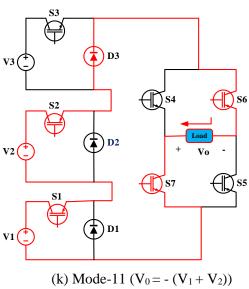

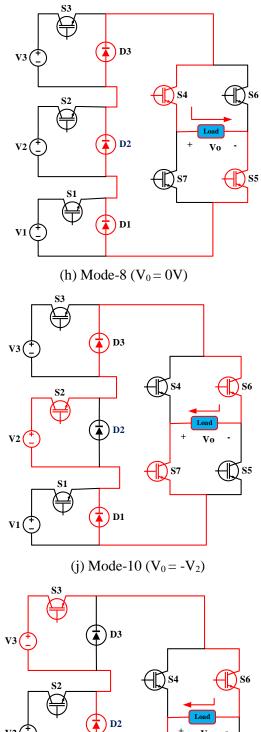

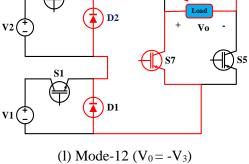

| 3.6          | Modes of operation of the proposed 15-level inverter                    | 54         |

| 3.7          | Comparison between the existing 15-level asymmetric                     | 55         |

|              | topologies and proposed 15-level inverter                               |            |

| 3.8          | DC sources, switches, diodes & capacitor ratio comparison               | 55         |

|              | for 15-level inverters with proposed inverter                           |            |

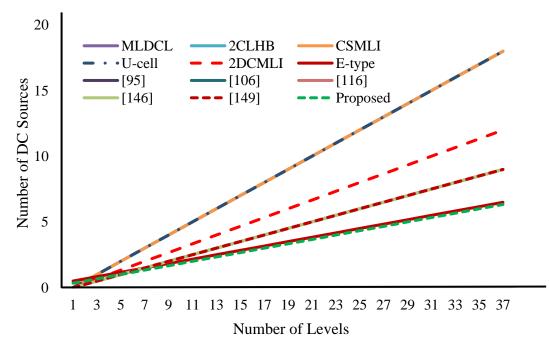

| 3.9          | Comparison between the design components of various MLIs                | 57         |

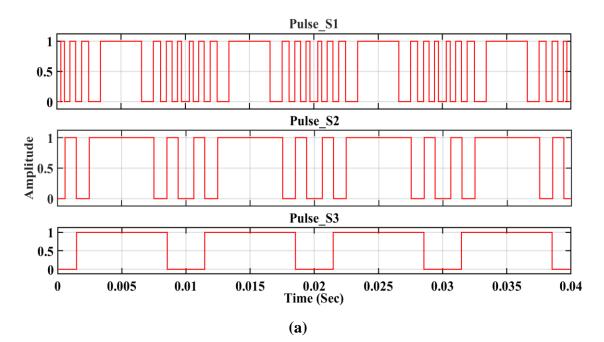

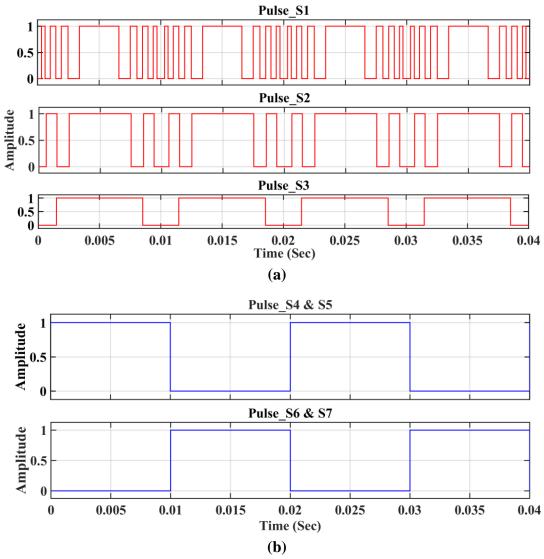

| 3.10         | Switching pulses of proposed inverter for seven-level                   | 64         |

|              | operation                                                               |            |

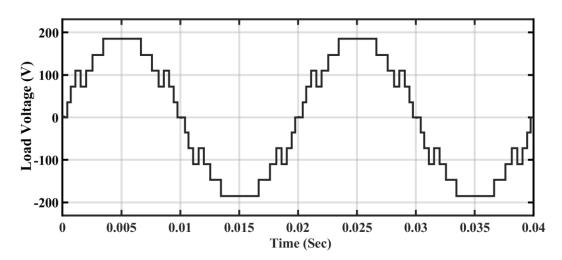

| 3.11         | Seven level output voltage of the proposed inverter                     | 64         |

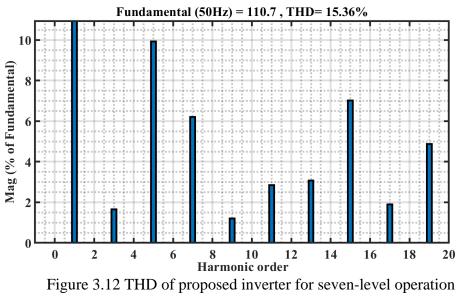

| 3.12         | THD of proposed inverter for seven-level operation                      | 64         |

| 3.13         | Switching pulses of proposed inverter for eleven level                  | 65         |

|              | operation                                                               |            |

| 3.14         | Eleven level output voltage of the proposed inverter                    | 66         |

| Figure | Description                                                  | Page |

|--------|--------------------------------------------------------------|------|

| No     | <b>F</b>                                                     | No   |

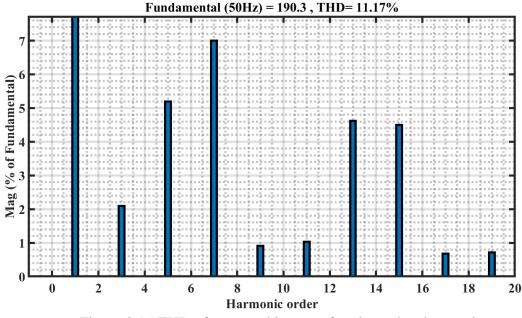

| 3.15   | THD of proposed inverter for eleven level operation          | 66   |

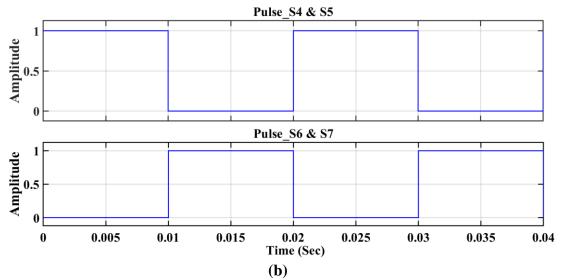

| 3.16   | Switching pulses of proposed inverter for 15-level operation | 67   |

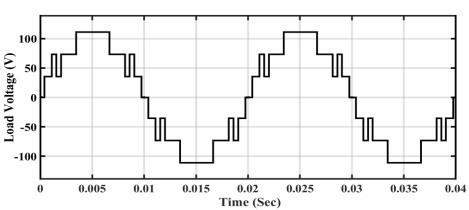

| 3.17   | Output voltage waveform of the 15-level asymmetric inverter  | 68   |

| 3.18   | Output current waveform of the 15-level asymmetric inverter  | 68   |

| 3.19   | THD of the output voltage of inverter for 15-level operation | 68   |

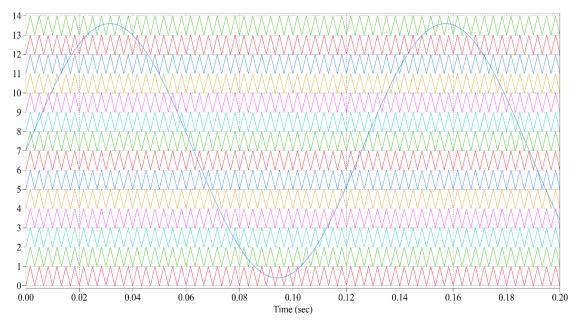

| 4.1    | Phase disposition pulse width modulation                     | 72   |

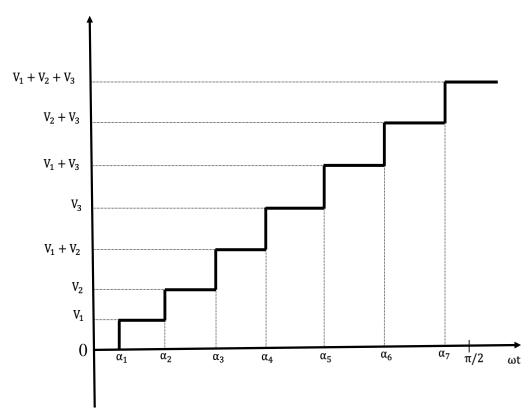

| 4.2    | Quarter wave approximation of 15-level output of MLI         | 73   |

| 4.3    | Switching cycle representation of IGBT over a cycle          | 74   |

| 4.4    | Conduction losses of IGBT                                    | 76   |

| 4.5    | Turn_ON losses of IGBT                                       | 76   |

| 4.6    | Turn_OFF losses of IGBT                                      | 77   |

| 4.7    | Foster electro-thermal model of IGBT                         | 78   |

| 4.8    | Electrical equivalent of thermal circuit                     | 79   |

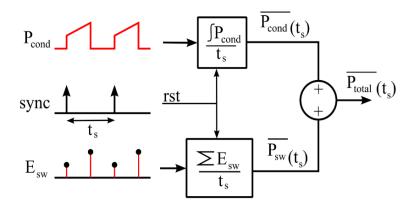

| 4.9    | Calculation of total cycle-average losses                    | 79   |

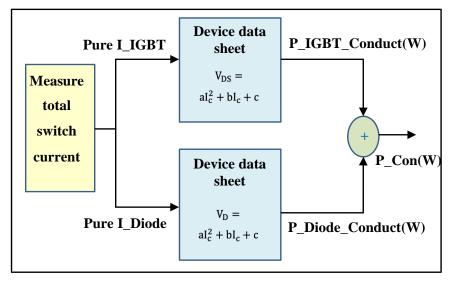

| 4.10   | Conduction loss calculation process using curve fitting      | 80   |

|        | Simulink model                                               |      |

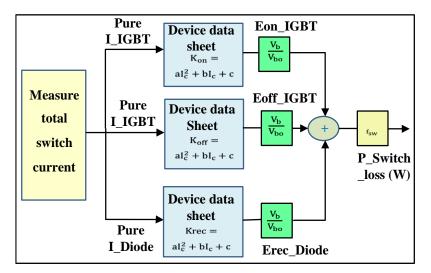

| 4.11   | Switching loss calculation process curve fitting Simulink    | 82   |

|        | model                                                        |      |

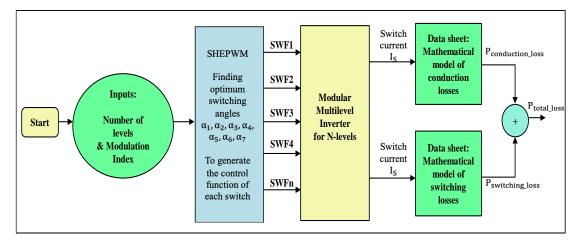

| 4.12   | Total power loss calculations with SHEPWM switching curve    | 83   |

|        | fitting Simulink model                                       |      |

| 4.13   | Device temperature, conduction losses & switching losses     | 86   |

|        | with high frequency (PDPWM) switching                        |      |

| 4.14   | Device temperature, conduction losses & switching losses     | 89   |

|        | with low frequency (SHEPWM) switching                        |      |

| 4.15   | Conduction losses comparison using PLECS thermal model       | 90   |

|        | with PDPWM & SHEPWM switching                                |      |

| 4.16   | Switching losses comparison using PLECS thermal model        | 91   |

|        | with PDPWM & SHEPWM switching                                |      |

| 4.17   | Power delivered and efficiency of the inverter using PLECS   | 91   |

|        | thermal model                                                |      |

| Figure | Description                                                  | Page |

|--------|--------------------------------------------------------------|------|

| No     |                                                              | No   |

| 4.18   | Power loss analysis using low frequency (SHEPWM)             | 93   |

|        | Switching                                                    |      |

| 4.19   | Power delivered and efficiency of the inverter using precise | 92   |

|        | Simulink models                                              |      |

| 4.20   | Power losses Vs modulation index using precise Simulink      | 93   |

|        | models                                                       |      |

| 5.1    | Control methodology of proposed MLI                          | 99   |

| 5.2    | Convergence characteristics using genetic algorithm          | 102  |

| 5.3    | Voltage harmonic distortion using genetic algorithm          | 103  |

| 5.4    | Current harmonic distortion using genetic algorithm          | 103  |

| 5.5    | Convergence characteristics using PSO algorithm              | 105  |

| 5.6    | Voltage harmonic distortion using PSO algorithm              | 106  |

| 5.7    | Current harmonic distortion using PSO algorithm              | 106  |

| 5.8    | Convergence characteristics using the whale optimization     | 110  |

|        | algorithm                                                    |      |

| 5.9    | Voltage harmonic distortion using the whale optimization     | 111  |

|        | algorithm                                                    |      |

| 5.10   | Current harmonic distortion using the whale optimization     | 111  |

|        | algorithm                                                    |      |

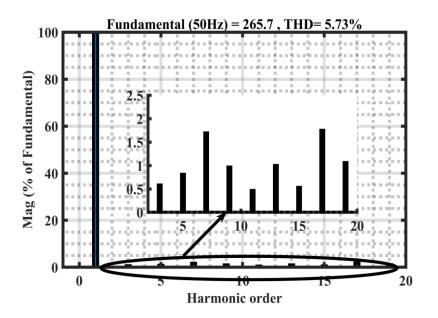

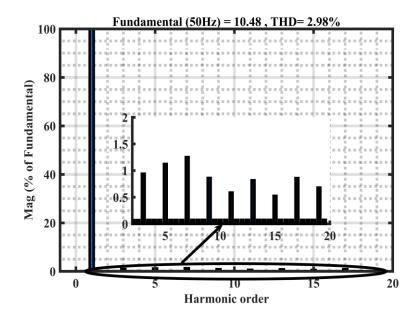

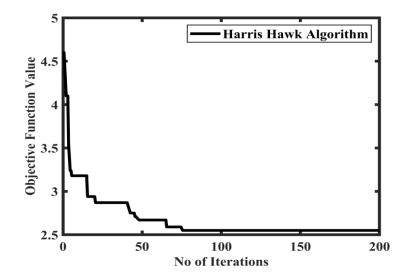

| 5.11   | Convergence characteristics using harris hawk algorithm      | 116  |

| 5.12   | Voltage harmonic distortion using harris hawk algorithm      | 116  |

| 5.13   | Current harmonic distortion using harris hawk algorithm      | 116  |

| 5.14   | Convergence characteristics using EWOA algorithm             | 120  |

| 5.15   | Voltage harmonic distortion using EWOA algorithm             | 120  |

| 5.16   | Current harmonic distortion using EWOA algorithm             | 120  |

| 5.17   | Convergence characteristics using APSO-NR algorithm          | 124  |

| 5.18   | Voltage harmonic distortion using APSO-NR algorithm          | 124  |

| 5.19   | Current harmonic distortion using APSO-NR algorithm          | 124  |

| 5.20   | Convergence characteristics using PSO-GA algorithm           | 126  |

| 5.21   | Voltage harmonic distortion using PSO-GA algorithm           | 127  |

| Figure | Description                                                           | Page |

|--------|-----------------------------------------------------------------------|------|

| No     | Description                                                           | No   |

| 5.22   | Current harmonic distortion using PSO-GA algorithm                    | 127  |

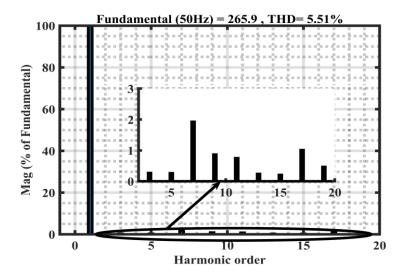

| 5.23   | Convergence characteristics using HH-DE algorithm                     | 129  |

| 5.24   | Voltage harmonic distortion using HH-DE algorithm                     | 130  |

| 5.25   | Current harmonic distortion using HH-DE algorithm                     | 130  |

| 5.26   | Comparison of voltage harmonics with different                        | 133  |

|        | optimizations                                                         |      |

| 5.27   | Comparison of current harmonics with different optimizations          | 134  |

| 6.1    | Types of grid integration of SPV systems                              | 136  |

| 6.2    | Power flow diagram for single-phase grid-connected SPV                | 137  |

|        | system                                                                |      |

| 6.3    | Proposed two-stage grid-connected SPV system                          | 139  |

| 6.4    | Schematic diagram of proposed grid-connected SPV system               | 140  |

| 6.5    | A two-diode model of photovoltaic cell                                | 141  |

| 6.6    | I-V & P-V curves at a constant temperature of $25^0$ C with           | 143  |

|        | variable irradiance                                                   |      |

| 6.7    | I-V & P-V curves at constant irradiation (1000 $W/m^2$ ) with         | 144  |

|        | variable temperature                                                  |      |

| 6.8    | Asymmetric PV sources for the input of proposed 15-level              | 145  |

|        | inverter                                                              |      |

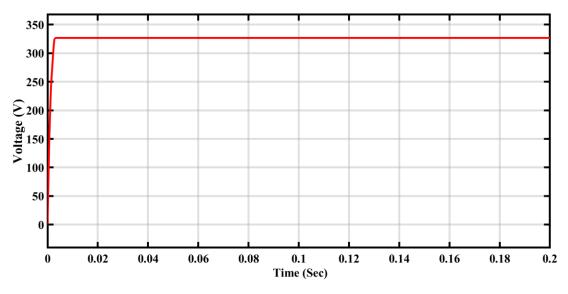

| 6.9    | Total dc-link voltage of the three PV sources                         | 145  |

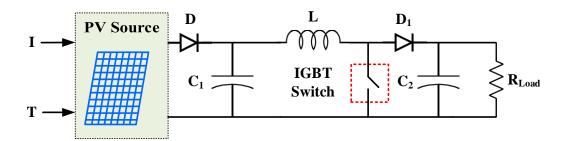

| 6.10   | PV connected dc-dc boost converter                                    | 146  |

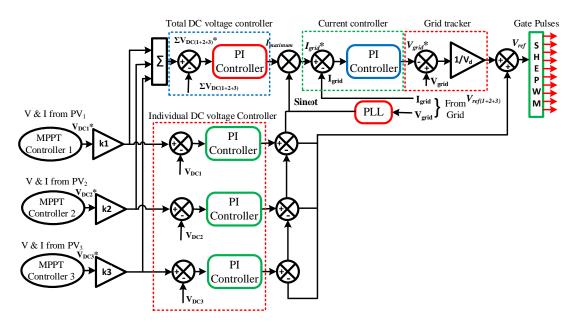

| 6.11   | Grid-connected controller for proposed 15-level inverter              | 149  |

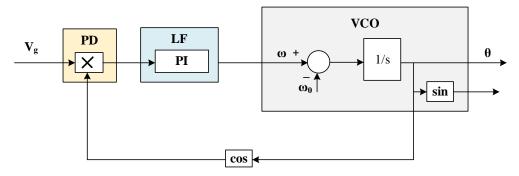

| 6.12   | A typical model of single-phase PLL                                   | 150  |

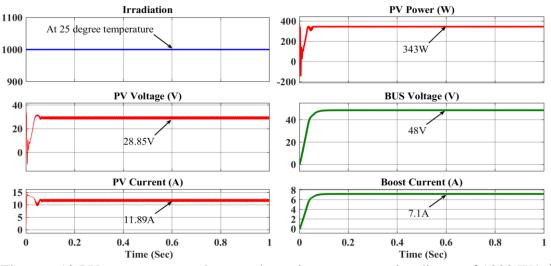

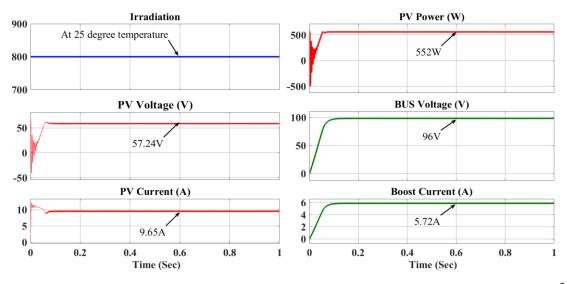

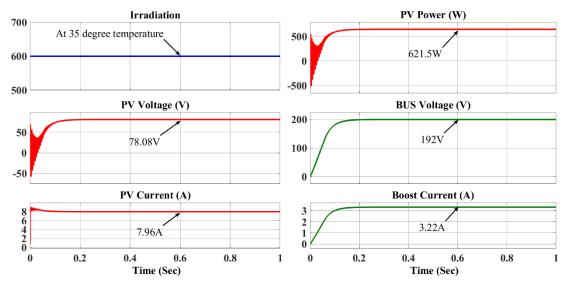

| 6.13   | PV measurements, boost voltage & current at an irradiance of          | 154  |

|        | 1000 W/m <sup>2</sup> and temperature of $25^0$ C for PV <sub>1</sub> |      |

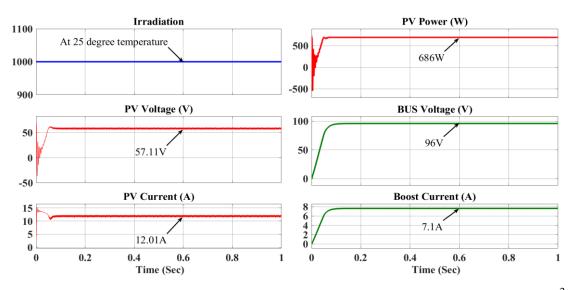

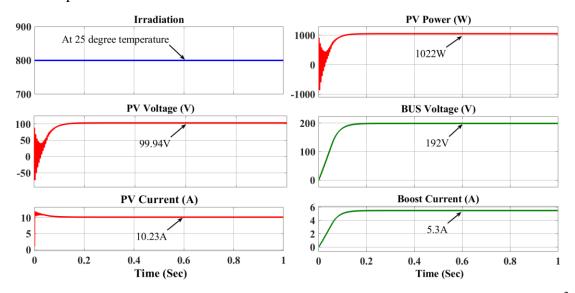

| 6.14   | PV measurements, boost voltage & current at an irradiance of          | 155  |

|        | 1000 W/m <sup>2</sup> and temperature of $25^0$ C for PV <sub>2</sub> |      |

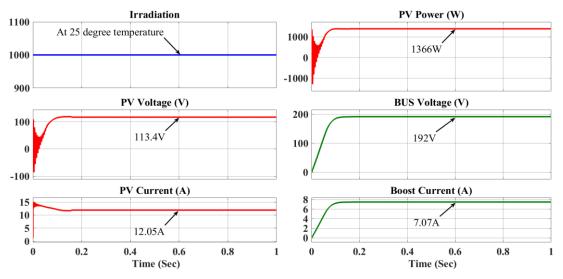

| 6.15   | PV measurements, boost voltage & current at an irradiance of          | 155  |

|        | 1000 W/m <sup>2</sup> and temperature of $25^0$ C for PV <sub>3</sub> |      |

| Figure<br>No | Description                                                          | Page<br>No |

|--------------|----------------------------------------------------------------------|------------|

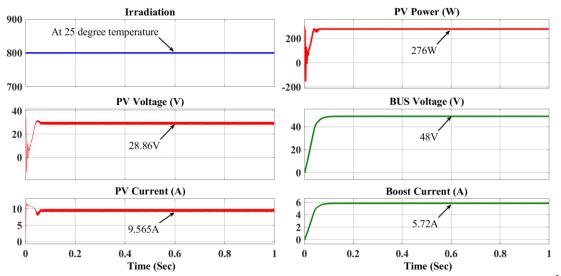

| 6.16         | PV measurements, boost voltage & current at an irradiance of         | 156        |

|              | 800 W/m <sup>2</sup> and temperature of $25^0$ C for PV <sub>1</sub> |            |

| 6.17         | PV measurements, boost voltage & current at an irradiance of         | 157        |

|              | 800 W/m <sup>2</sup> and temperature of $25^0$ C for PV <sub>2</sub> |            |

| 6.18         | PV measurements, boost voltage & current at an irradiance of         | 157        |

|              | 800 W/m <sup>2</sup> and temperature of $25^0$ C for PV <sub>3</sub> |            |

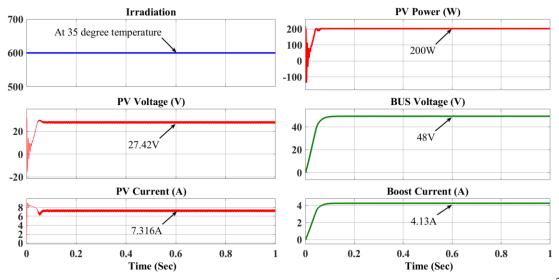

| 6.19         | PV measurements, boost voltage & current at an irradiance of         | 158        |

|              | 600 W/m <sup>2</sup> and temperature of $35^0$ C for PV <sub>1</sub> |            |

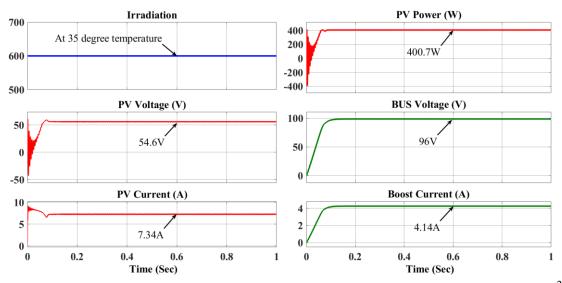

| 6.20         | PV measurements, boost voltage & current at an irradiance of         | 158        |

|              | $600 \ W/m^2$ and temperature of $35^0 \ C$ for $PV_2$               |            |

| 6.21         | PV measurements, boost voltage & current at an irradiance of         | 159        |

|              | $600 \ W/m^2$ and temperature of $35^0 \ C$ for $PV_3$               |            |

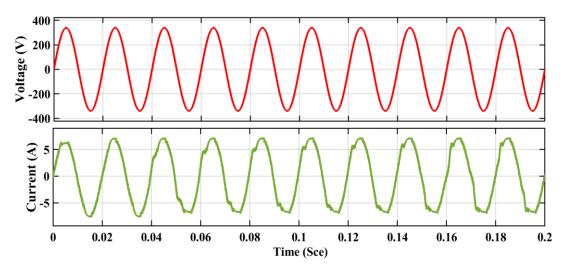

| 6.22         | Grid voltage and grid current waveforms with PSO-PI                  | 160        |

|              | controller                                                           |            |

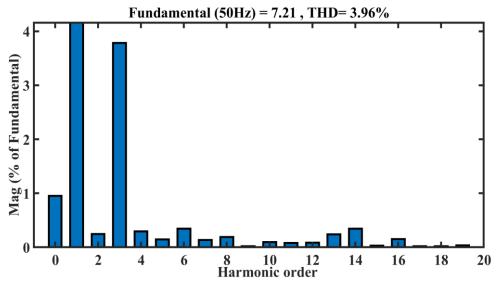

| 6.23         | THD analysis of grid current waveform with PSO-PI                    | 160        |

|              | controller                                                           |            |

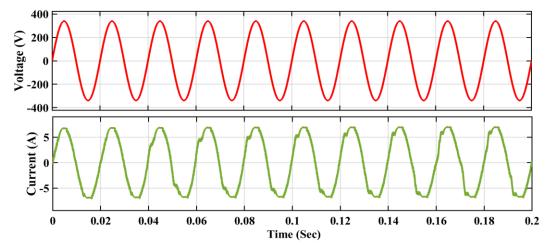

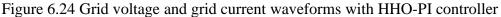

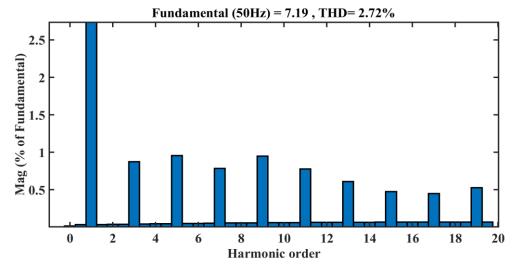

| 6.24         | Grid voltage and grid current waveforms with HHO-PI                  | 161        |

|              | controller                                                           |            |

| 6.25         | THD analysis of grid current waveform with HHO-PI                    | 162        |

|              | controller                                                           |            |

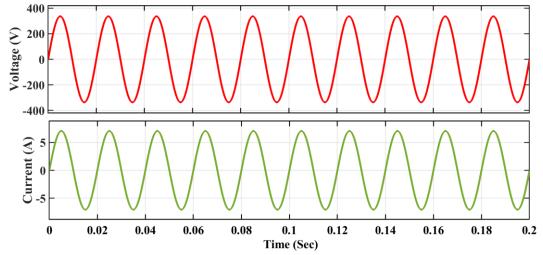

| 6.26         | Grid voltage and grid current waveforms with PSO_GA-PI               | 163        |

|              | controller                                                           |            |

| 6.27         | THD analysis of grid current waveform with PSO_GA-PI                 | 163        |

|              | controller                                                           |            |

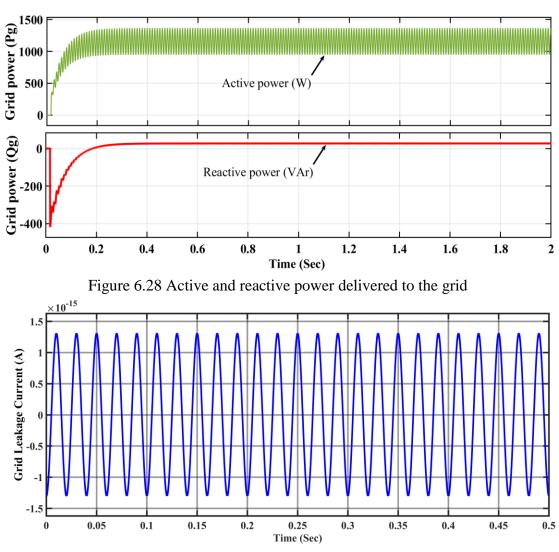

| 6.28         | Active and reactive power delivered to the grid                      | 164        |

| 6 20         | Lealrage automation the axid convected DV system                     | 164        |

| 6.29         | Leakage current in the grid-connected PV system                      | 164        |

## LIST OF APPENDICES

| Appendices<br>No | Description                                                                    | Page<br>No |

|------------------|--------------------------------------------------------------------------------|------------|

| A.1              | Parameters of optimization algorithms                                          | 186        |

|                  | A.1.1 Parameters & Specifications of genetic algorithm                         | 186        |

|                  | A.1.2 Parameters & Specifications of PSO algorithm                             | 186        |

|                  | A.1.3 Parameters & Specifications of the whale optimization algorithm          | 187        |

|                  | A.1.4 Parameters & Specifications of harris hawk<br>optimization algorithm     | 187        |

|                  | A.1.5 Parameters & Specifications of the enhanced whale optimization algorithm | 188        |

|                  | A.1.6 Parameters & Specifications of hybrid PSO-GA algorithm                   | 188        |

|                  | A.1.7 Parameters & Specifications of hybrid HH-DE algorithm                    | 189        |

|                  | A.1.8 Parameters & Specifications of hybrid APSO-NR algorithm                  | 189        |

| A.2              | Specifications and parameters of PV module                                     | 190        |

| A.3              | Relationship between dc input power and ac output power                        | 190        |

|                  | in proposed inverter                                                           |            |

| A.4              | Components comparison of various asymmetric MLIs                               | 192        |

|                  | with proposed MLI for N-levels                                                 |            |

| A.5              | Rating and specifications of the proposed inverter                             | 195        |

## LIST OF SYMBOLS & ABBREVIATIONS

| SPV                     | - | Solar photovoltaic system                             |

|-------------------------|---|-------------------------------------------------------|

| GCSPV                   | - | Grid-connected photovoltaic system                    |

| P&O                     | - | Perturb and observe                                   |

| MPPT                    | - | Maximum power point tracking                          |

| MLI                     | - | Multilevel inverter                                   |

| SHEPWM                  | - | Selective harmonic elimination pulse width modulation |

| PDPWM                   | - | Phase disposition pulse width modulation              |

| SVPWM                   | - | Space vector pulse width modulation                   |

| MV                      | - | Medium voltage                                        |

| HV                      | - | High voltage                                          |

| THD                     | - | Total harmonic distortion                             |

| $V_{dc}$                | - | DC input voltage                                      |

| FSFC                    | - | Fundamental switching frequency control               |

| α                       | - | Switching angle                                       |

| V <sub>1max</sub>       | - | Peak fundamental voltage                              |

| V <sub>1</sub>          | - | Actual fundamental voltage                            |

| k                       | - | Degree of freedom                                     |

| Ν                       | - | No of output voltage levels                           |

| N <sub>DC</sub>         | - | Number of DC sources                                  |

| Ns                      | - | Number of switches                                    |

| N <sub>D</sub>          | - | Number of diodes                                      |

| N <sub>C</sub>          | - | Number of capacitors                                  |

| М                       | - | Modulation index                                      |

| OF                      | - | Objective function                                    |

| P <sub>Conduction</sub> | - | Conduction losses                                     |

| I <sub>C</sub>          | - | Conduction Current                                    |

| Von                     | - | ON State voltage of the IGBT                          |

| $E_{on_SW_loss}$        | - | ON state energy loss of IGBT                          |

| $E_{off\_SW\_loss}$     | - | OFF state energy loss of IGBT                         |

| V <sub>CE</sub>         | - | Collector emitter voltage of IGBT                     |

|                         |   |                                                       |

| T <sub>on</sub>              | - | ON time of IGBT                                       |

|------------------------------|---|-------------------------------------------------------|

| T <sub>off</sub>             | - | OFF time of IGBT                                      |

| E <sub>SW_loss</sub>         | - | Total switching losses of IGBT                        |

| Т                            | - | Operating time of IGBT Switch                         |

| f <sub>SW</sub>              | - | Switching frequency                                   |

| $v_D$                        | - | Diode voltage                                         |

| GA                           | - | Genetic algorithm                                     |

| PSO                          | - | Particle swarm optimization                           |

| WOA                          | - | Whale optimization algorithm                          |

| HHA                          | - | Harris hawk algorithm                                 |

| EWOA                         | - | Enhanced whale optimization algorithm                 |

| APSO-NR                      | - | Asynchronous Particle Swarm Optimization with Newton  |

|                              |   | Raphson Algorithm                                     |

| PSO-GA                       | - | Particle Swarm Optimization with Genetic Algorithm    |

| HH-DE                        | - | Harris Hawk with Differential Evolution Algorithms    |

| $\mathbf{V}_{\mathrm{grid}}$ | - | Grid voltage                                          |

| $V_{PV}$                     | - | PV cell voltage                                       |

| $I_{PV}$                     | - | PV cell current                                       |

| $P_{PV}$                     | - | PV cell power                                         |

| $V_{\text{Boost}}$           | - | The output voltage of the dc-dc boost converter       |

| I <sub>Boost</sub>           | - | The output current of the dc-dc boost converter       |

| $K_{Vp}$                     | - | The proportional gain value of the voltage controller |

| K <sub>Vi</sub>              | - | The integral gain value of the voltage controller     |

| K <sub>Cp</sub>              | - | The proportional gain value of the current controller |

| K <sub>Ci</sub>              | - | The integral gain value of the current controller     |

| PI                           | - | Proportional plus integral                            |

|                              |   |                                                       |

### **CHAPTER-1**

### INTRODUCTION

### **1.1 INTRODUCTION**

The advancement in day-to-day technology and cost-effectiveness are the two significant factors that use solar energy to meet increased energy demands. From 2007 to 2022, there was an 85% reduction in the cost of solar panels, which steers to decrease the cost of generation from solar PV panels. The power generation cost dropped to 83.5%, from INR 24.82 to INR 4.12 per kWh during 2010–2022 [1]. The cost of solar power production in India is expected to fall to about INR 1.9 per unit by 2030, according to TERI-CPI research. Thus, the multi-megawatt rating PV energy has become a reality. The standard solar power plants mainly consist of PV modules, which are physically exposed to the environment to convert solar radiation into DC power. With the frequency of the solar radiation and operating temperature, the peak power produced by the PV panel varies. A PV array's maximum power can be extracted using MPPT control algorithms. In MPPT, many algorithms were used to maximize the PV system's power output power.

Power modulator (Power electronic converter that converts dc to dc and dc to ac) is one of the significant components of the solar PV system. Power electronics is about converting power from one form to another form, while power conversion takes place in the field of electricity. The power conversion from the existing state to the required should happen with minimal power losses, minor deviation in quality of power, low cost, reduced number of switching devices and electronic components. Also, there should be minimal mathematical overheads.

Today India is looking towards renewable energy sources for its power demands. The Atmospheric conditions of India can harness enormous solar energy. Annually about 5000 trillion kWh power is incident in the land areas of India. Almost every component receives 4-7 kWh per sq.m per day. Due to this, conversions from solar radiation to heat and from solar radiation to electricity are successfully utilized. Photovoltaic generations are available in both grid-connected mode and islanded mode. It is generously available and meets energy demands such as power, heating, cooling, etc., in urban and rural areas. Photovoltaic generation is the most secure power and green energy generation of all Renewable resources [2].

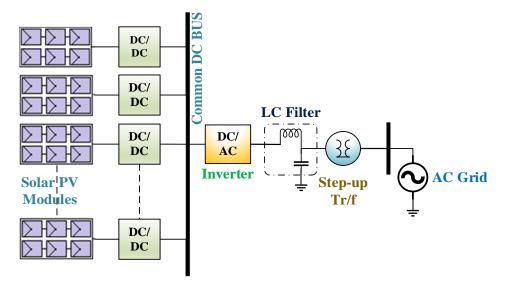

Figure 1.1 Common grid-connected solar PV system

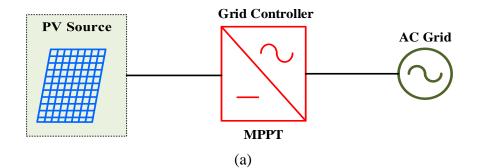

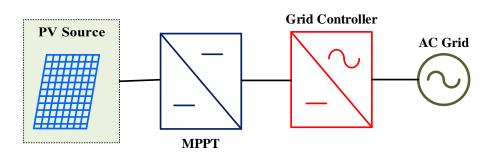

Solar energy can fulfill the entire country's needs if harnessed effectively. There are still numerous places in India that are not electrified. Photovoltaic generating systems are an excellent alternative for electrifying these formerly unconnected locations. Photovoltaic generation uses series & parallel-connected PV modules, power electronic converters, energy storage devices (battery), step-up transformers and filters, etc. Figure 1.1 shows the standard grid-connected PV system setup with a common dc bus. The inverter is a significant component of the grid-connected PV system since it costs 59% of the total cost. The researcher developed many inverter topologies to test the GCSPV system's applicability, efficiency, and lifetime.

There are four different types of inverters utilized for grid-connected photovoltaic systems. The four different configurations of PV inverters are listed as follows:

- 1. AC- module inverter

- 2. String inverter

- 3. Multi string inverter

- 4. Centralized inverter

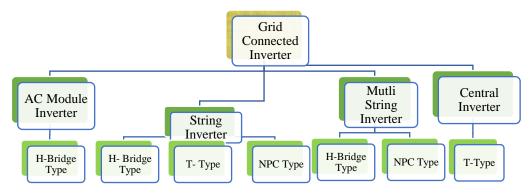

Figure 1.2 Different configurations of grid-connected PV inverters

Figure 1.2 shows different PV inverters available in the market, such as ACmodule inverter, string inverter, multi-string inverter, and centralized inverter. NPC, Ttype, and H-bridge are the most common designs for high-power and residential applications in the KW to MW range.

From the above configurations, AC-module inverter is used for the small-scale applications, i.e. < 350 W range, string, and multi-string inverters are used for medium-scale applications, i.e. > 10 KW and < 500 KW respectively, centralized inverter are used for the large-scale applications, i.e. > 850 KW range. The unit cost for string inverters is as high as it is only suitable for low-power applications. The efficiency of the central inverter is more elevated, i.e. about 98.6%. Still, there are several disadvantages. It needs blocking diodes and gives poor MPPT performance, i.e. only a single MPPT is used for the entire system, and the centralized inverters are not flexible. Whereas in the case of the multi-string inverter, separate MPPT systems are available for each string. Related research is also carried out in [3]-[5].

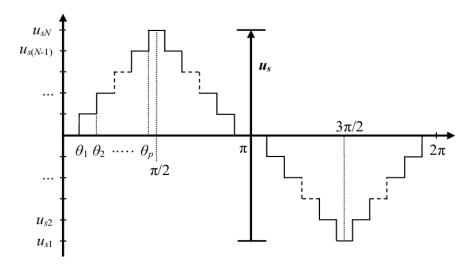

To get a near sinusoidal staircase waveform, the multilevel inverter employs several power electronic switches that are connected to several small dc voltage sources. The multilevel inverter's most pleasant trademarks are Common mode voltage, Input current, Switching frequency, Reduced harmonic distortion etc.

Specific applications of multilevel inverters are Variable frequency AC motor drives, Active power filters, Electric vehicle motor drives, DC source utilization, Power factor correction equipment, Renewable energy conversion system, Consecutive frequency link systems, Integration of non-conventional energy resources. A staircase type approximated near sinusoidal waveform of multilevel inverter output is shown in figure 1.3.

Figure 1.3 Near sinusoidal staircase waveform of multilevel inverter

Many industrial applications nowadays need significant power. Nonetheless, most of the industrial equipment runs on medium or low energy. While certain industrial loads may gain from high-power sources, others may suffer. For medium and high-voltage applications, the multilevel inverter has been used since 1975.

Multilevel inverters can be conveniently applied to solar PV systems due to their ability to produce variable voltage from a constant dc source and remove harmonics in the conversion process when incorporating PV power into the grid. The appreciable features of multilevel converters are as follows:

- i. *Stairway waveforms quality:* multilevel inverters may alleviate electromagnetic compatibility (EMC) issues by having extremely low distortion and lowering dv/dt.

- ii. *Switching Frequency:* one of a multilevel inverter's key advantages is running at both a high and low switching frequency.

- iii. *More sinusoidal output waveform:* by raising the levels of the multilevel inverter, the voltage output becomes more sinusoidal, and the harmonic content is decreased.

- iv. *Source current*: Multilevel converters will draw the low distortion current. There are currently several multilevel inverters being developed. The

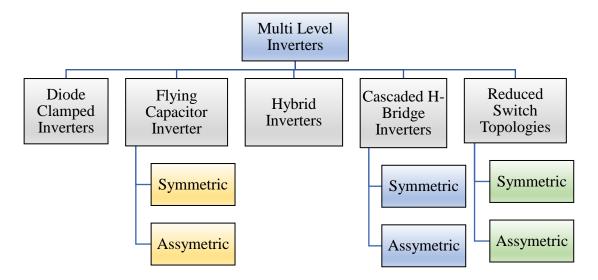

following improvements have been observed for multilevel inverters and are presently being used by the industries. The classification of these MLIs is given in figure 1.4.

Figure 1.4 Classification of multilevel inverters presently used in the industries

### **1.2 INVERTER CHALLENGES**

Solar PV systems can be stacked or integrated into the grid using inverters. A variety of inverters are developed and designed for solar PV systems. Currently, 2- level and 3-level inverters transformerless inverters are being used in solar PV plants due to their low cost, simple, compact design, and control. Among these, the transformerless inverter is highly efficient and can operate with an efficiency of around 99% [6]. Although these inverters are highly efficient, the major drawback is that there is no isolation between the solar PV system and the grid. With the lack of galvanic isolation, transformerless inverters damage the solar PV plant during the short circuit faults on the grid. Even though these low-level inverters are cost-effective, the problem with these inverters is that they have constant dv/dt. But all the load equipment is designed to operate with variable dv/dt with the instantaneous change in voltage magnitude. The constant dv/dt in 2-level and 3-level inverters decreases the load equipment life and gives the deviated characteristics compared to their actual operating characteristics. Hence it is essential to use high-level inverters that provide the variable dv/dt output voltage in the near-sinusoid for safe loading equipment operation. Many researchers have carried out the study to obtain multilevel output and have proposed advanced developments. Three MLIs are used in practice: diode clamped, flying capacitor, and

H-bridge inverters. When the number of levels is high, such multilevel inverters are more expensive since they require more semiconductor switches, capacitors, DC sources, and clamping diodes. Also, the control circuit becomes complicated using more switching devices, which increases the harmonics and further increases switching losses. Modern MLI topologies are not commercially feasible for solar photovoltaic (SPV) systems with limited energy conversion potential (performance in commercial applications is less than 20%).

To reduce the volume, cost, and losses in the multilevel inverter and to meet the load requirements, multilevel inverters with reduced power switches and fewer circuit elements are required to build. On the other hand, the symmetrical MLI can increase the voltage levels of the inverter while operating at a low switching frequency, making it a potential PV inverter with greater efficacy. With a reduced number of switches, the inverter operates relatively at a low switching frequency, which improves the inverter's performance and reduces the filter requirements for stand-alone or grid-connected PV applications.

The present research focused on identifying and developing an asymmetric multilevel inverter with reduced switches to optimize the power and control circuits. The proposed multilevel inverter configuration is quite simple and easy to extend for higher levels, as well as its gating circuits are simplified due to the optimized number of switches. The primary factor influencing the inverter's performance is the harmonics of the multilevel output. Although in the proposed topology of the inverter, the number of switches is reduced for the operation with different switching angles, which often causes harmonics in the output. The goal here is to optimize the switching angles to minimize the lower-order harmonics of the proposed inverter.

Several optimization algorithms were reported to evaluate the optimal switching angles for the inverters, thereby reducing the harmonics content in the inverter output. However, these algorithms are designed to operate at higher switching frequencies, unsuitable for effectively eliminating the lower-order harmonics. The study carried out by various researchers mainly develops symmetrically reduced switch inverters with optimization methods, which are not relevant for solar PV applications since the solar PV system's output is variable with the variation of solar irradiance and temperature. The inverters must accept variable input from solar PV to produce a constant output voltage suitable for stand-alone or grid operation.

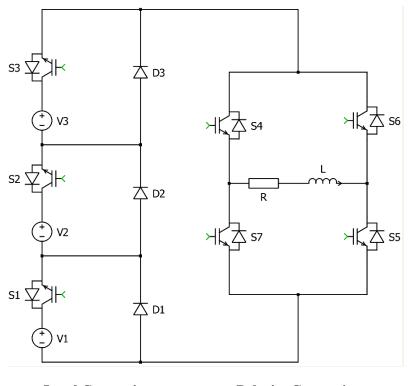

The above motivation leads this research to implement an asymmetric multilevel inverter with optimal switches and dc sources. The proposed topology is implemented for a 15-level inverter with seven power switches, three diodes, and three dc sources as shown in figure 1.5.

Level Generation Polarity Generation

Figure 1.5 An asymmetric inverter with a reduced number of switches

The proposed topology consists of two parts namely, the level generation part and the polarity generation part. The level generation part consists of three switches, three dc sources, and three switched diodes. By cascading the basic units, the number of output levels was increased. The polarity generation part is an H-bridge inverter consisting of four switches and a load circuit, which is responsible to reverse the polarity of the output waveform for every half cycle. Three input sources were chosen based on the binary approach as the ratio of 1:2:4 for asymmetric sources. The detailed methods of choice input sources and the structure of the 15-level asymmetric inverter are presented in chapter-3.

#### **1.3 RESEARCH OBJECTIVES & METHODOLOGY**

The objectives of the research are summarized as follows

- 1. To select and develop the asymmetric multilevel PV inverters with reduced switch count for the limited number of commutations by considering nonlinear loads.

- 2. To reduce the switching losses by the low switching frequency control.

- 3. To implement different hybrid soft computing algorithms for optimizing the switching angles of the proposed asymmetric multilevel inverter to reduce total harmonic distortion.

- 4. To simulate and test the performance of the proposed inverter on a gridconnected PV system.

The proposed research is aimed to minimize the THD in reduced switch multilevel PV inverters using different soft computing techniques. To accomplish this, an asymmetric grid-connected PV inverter is considered for commercial loads. The research is carried out in two phases. The first phase is focused on selecting and developing an asymmetric multilevel inverter with reduced switching losses using the low frequency switching modulation technique. The following methodology is adopted in this phase.

- (i) Developing an efficient asymmetrical multilevel inverter with reduced switch count for the minimum number of commutations which includes.

- a) Investigation of the current topologies of multilevel PV inverters to explore the limitations of the traditional multilevel inverters.

- b) Study of the various factors affecting the performance of grid-connected inverters.

- c) Study of various factors affecting the power quality of the inverter and explore the remedial measures.

- (ii) Formulation of low/variable switching frequency control to eliminate the power losses in the proposed inverter.

The second phase is committed to optimizing the proposed inverter's switching angles, which involves the following steps;

- (i) Study and implementation of selected traditional optimization algorithms in solving various types of problems related to power electronic converters to explore their limitations.

- (ii) Implementation of various soft computing algorithms, including hybrid algorithms, to reduce the proposed inverter's lower order harmonics.

- (iii) Analyzing and validating the results obtained from the applied algorithms on a grid-connected PV system.

#### **1.4 ORGANIZATION**

Chapter-1 gives an overview of grid-connected inverters and their challenges.

Chapter-2 presents the comprehensive literature review of grid-connected multilevel inverters and a review of various optimization techniques and their application to multilevel inverters. Based upon the conducted review, the research gaps are also presented in the last section of the chapter.

Chapter-3 presents the design and development of a 15-level asymmetric inverter and its modes of operation. The chapter further presents the use of a low switching frequency control method for mitigating the switching losses. The proposed inverter performance is then compared to seven-level and eleven-level inverters.

Chapter-4 analyzes the power losses in the proposed 15-level inverter with highfrequency switching (PDPWM) and low-frequency switching (SHEPWM) control using PLECS thermal model. These power losses are validated using curve fitting based on precise models on Simulink, and the inverter's efficiency is computed.

Chapter-5 presents the comparative analysis of various traditional and hybrid optimization techniques as applied to the designed inverter for reducing the generated harmonics by optimizing the switching angles.

Chapter-6 discusses the implementation of the proposed inverter to a gridconnected solar PV system. The chapter evaluates the performance of the proposed inverter under different operating conditions.

Chapter-7 presents the conclusive summary of the entire research and recommendations for future work.

### **CHAPTER-2**

# STATE OF THE ART OF THE GRID-CONNECTED MULTILEVEL INVERTER

### 2.1 INTRODUCTION

Multilevel inverters are applied to solar PV systems due to their inherent ability to convert input dc voltage to output ac voltage. Many MLI topologies and control methodologies have been proposed in the literature to get the optimum output from the inverter, which injects the least harmonics into the system. This chapter presents an exhaustive literature review on multilevel inverters for grid-connected applications and their control methodologies. The first section presents the review on multilevel gridconnected PV inverters considering different configurations, topologies and switching methodologies, followed by the research gaps and scope of research in the second section.

### 2.2 REVIEW OF MULTILEVEL GRID-CONNECTED PV INVERTERS

While designing the medium-voltage converters for multiple applications such as motor drives, solid-state transformers, and solar photovoltaic presents some common problems such as difficulties with large-scale photovoltaic systems, complicate the converter and control circuit. Multilevel inverter theory was first introduced in 1971 as a substitute for medium-power applications for a series of connected power electronic switching devices [6]. During the 1971-1981 era, the MLIs such as neutral point clamped (NPC), a flying capacitor (FC), and cascaded H-bridge (CHB), were suggested [7-8].

Because of its basic circuit design, the idea of a three-level NPC converter has become more popular and are still commercially available. However, the rise in levels of neutral point clamped topology considerably increases the number of clamping diodes. [9], [10]. The inverse retrieval times of the clamping diode render this topology feasible to develop an inverter with more levels for medium power applications [11]. Hence, the neutral point clamped topology and the flying capacitor topologies are too inadequate for MV and HV applications because they use many condensers requiring prior charging and balancing the capacitors [9], [11]. Furthermore, a large dc-link capacitor needs for single-cell topology limits its application to medium and high voltages, particularly solar PV applications, where different PV panels are connected in series [12-13]. This vast number of series-connected PV panels will decrease the overall system efficiency due to common MPPT and series resistance [14].

Modular structures have been developed by cascading the full-bridge inverters, named multi-cell multilevel CHB converter topology, which provides MPPT operation at the module level and is scalable to various voltage levels. Also, clamping diodes and capacitors are not used by CHB topologies [11]. The CHB is getting rid of the more series PV modules; however, continuous module parameters and the partial shading will cause mismatch problems [15-18]. These mismatch problems create imbalance and result in low quality of power to the grid [19]. While using CHB converters for PV applications, this module mismatch is another challenge compared to converters in solid-state transformers [20-23] and solid-state motor drives [24-25].

Multilevel Inverter (MLI) in solar photovoltaic (PV) systems is increasingly used for standalone or grid-connected applications [26-28]. Traditional two and threelevel inverters are widely used for standalone and GCSPV systems [26]-27]. These are, however, affected by high THD and high dv/dt stress on the switches of the inverter. Furthermore, the switching frequency of pulse width modulation is increased; hence the THD and power losses are often high.

For grid-connected PV systems, there are several MLIs, such as the neutral point clamped MLI [28], flying capacitor-based MLI [29], cascaded H-bridge MLI [30-32], and hybrid topologies [33-36]. Symmetric cascaded MLIs become more prominent due to their modular design, increased rating capability, and near sinusoidal voltage levels. On the other hand, traditional inverters have significant power losses because they require many power switches and often operate at a high switching frequency. Asymmetrically configured cascaded MLIs can increase to more voltage levels with less number of comonents [37-38]. Nevertheless, the numbers of switches are still high in the traditional cascaded inverter and increase with the inverter levels.

Many MLIs with a limited number of components have continuously been used in numerous power electronics applications [39-51], [61-63], [78], [82-83], [88], [102], [106-110]. Many MLIs have two parts: the level generating part and the polarity generating part [43-51], [106-110]. Some of these topologies are ideal for the symmetrical configurations [44-46], [49], [50]. In [48], [82-83], an asymmetric inverter with packed U-cells is proposed that may not function under symmetrical source conditions.

In certain inverter topologies, the level generation portion is composed of numerous bidirectional switches connected back to back [44-46], [49], [51]. A cascaded switched diode structure with controlled switches and multiple power diodes is proposed for the MLI to enhance the voltage level (symmetrical and asymmetrical arrangement) [41]. Although the MLIs have more voltage blocking capacity in the polarity generating part than the level generating part.

However, an inverter with asymmetric sources will not be able to create all of the voltage levels. For higher voltages, the circuit with bi-directional switches increases inverter costs. The MLI with a low number of switches may significantly improve the efficiency and harmonics of PV systems interconnected to the grid.

Several researchers recently proposed the number of reduced switch MLIs for GCSPV systems [45], [52-54]. In [45], a 7-level inverter with a minimum number of components and a dc input with a capacitor divided into three equal parts is proposed. Nevertheless, there are no specifics about the voltage balance of the capacitor. A simplified cascaded MLI with reduced witches is suggested for the GCSPV system [53] discussed the voltage balance of dc ties between several dc links. On the other hand, the inverters mentioned above are built only for symmetrical PV voltages and require extra switches. Some of the researchers reported the asymmetric MLI for the PV application; however, the performance of the inverter is the central issue.

Multilevel inverter design has got plenty of literature, among the existing investigations, some of the research investigations for four arm current source inverter [55], quasi-z-source inverter [56], single phase direct grid integrated transformer less converter [57], single-stage direct grid-connected inverter [58], transformerless grid-connected PV inverter [59], modified z-source inverter [60], transformerless cascaded h-4 inverter [61], three phase cascaded h-5 inverter [62], common mode h-5 topology

[63], enhanced h5-d topology [64], two-half-bridge h4 topology [65], common mode grounding topology [66], conventional two-level inverter [67], common mode grounding topology [68], multi cell voltage-source inverter (VSI) [69], multilevel diode clamped inverters [70], h-bridge topology with bipolar switch [71], diode-clamped topology [72], grid-connected PV inverter [73], neutral point clamped inverter [74], two level 3-phase VSI [75], two-stage transformerless dual-buck PV grid-connected inverters [76], single source and double source mli [77], reduced switch asymmetric multilevel inverter [78], three-level NPC inverter [79], multi-phase neutral point clamped 3-level inverter [80], cascaded h-bridge multilevel inverter [81], seven-level packed u-cell inverter [82], seven-level packed u- cell inverter [83], cascaded h-bridge multilevel inverter [84], four-leg voltage-source multilevel inverter [85], single-phase asymmetrical four-level diode-clamped inverter [86], multi-paralleled three-level ttype inverters [87], asymmetrical reduced switched multilevel inverter [88], parallel operated multilevel inverters [89], single-phase hybrid multilevel inverter [90], multilevel voltage source inverter [91], single-phase  $\pi$ -type 5-level inverter [92], 9level cascaded inverters [93], symmetric and asymmetric MLIs [94], cascaded 11-level inverter [95], voltage source inverters [96], cascaded h-bridge diode clamped inverter [97], 7-level switched capacitor mli topology [98], zero current switching dc-dc boost converter based mli [99], bidirectional switch based reduced switch MLIs [100], 5level diode clamped multilevel inverter [101], reduced switch count multilevel inverter [102], multi-topology mode inverter [103], hybrid 7-level cascaded multilevel inverter [104], 5-level h-bridge dual buck inverter topology [105], multilevel converter topology with reduced components [106], optimized three-phase multilevel inverter topology [107], hybrid cascaded multilevel inverter (HCMLI) [108], five-level inverter using PODPWM technique [109], symmetrical & asymmetrical MLIs with minimal switches [110]. The detailed summary, problems addressed and solution methods suggested in the literature is listed in table 2.1.

| Authors                    | Type of<br>Inverter               | Problems addressing                                                                                                                                                                                                      | Journal/<br>Conference                                                     | Year of<br>Publication | Reference |

|----------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------|-----------|

| Sandeep<br>et al.          | 4-Arm CSI                         | <ul> <li>Improve the performance of CSI due to reduced DC-link capacitance.</li> <li>Reduce the leakage current injected into the grid, thereby limiting the need for an isolation transformer.</li> </ul>               | IEEE Transactions on industrial electronics                                | 2014                   | [55]      |

| Mohammad<br><i>et al</i> . | Quasi-Z-source inverter<br>(qZSI) | <ul> <li>Reduction in common mode current.</li> <li>Eliminate the conduction of the H-bridge body diode, which has lower reverse recovery characteristics.</li> <li>Eliminating the use of a dc-dc converter.</li> </ul> | IEEE Journal of<br>emerging and selected<br>topics in power<br>electronics | 2019                   | [56]      |

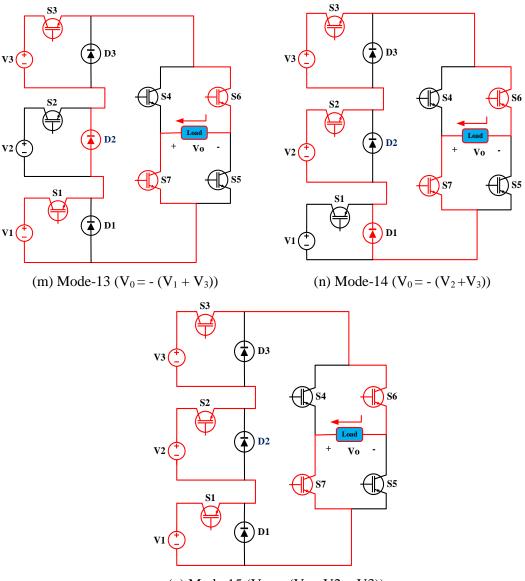

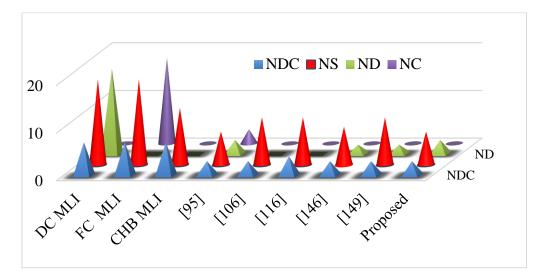

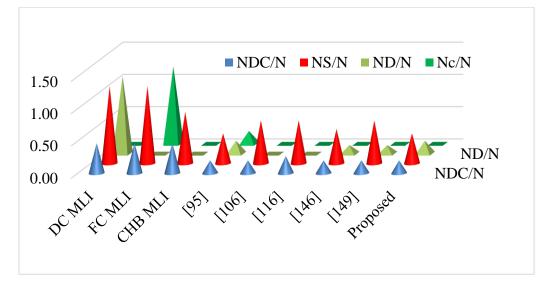

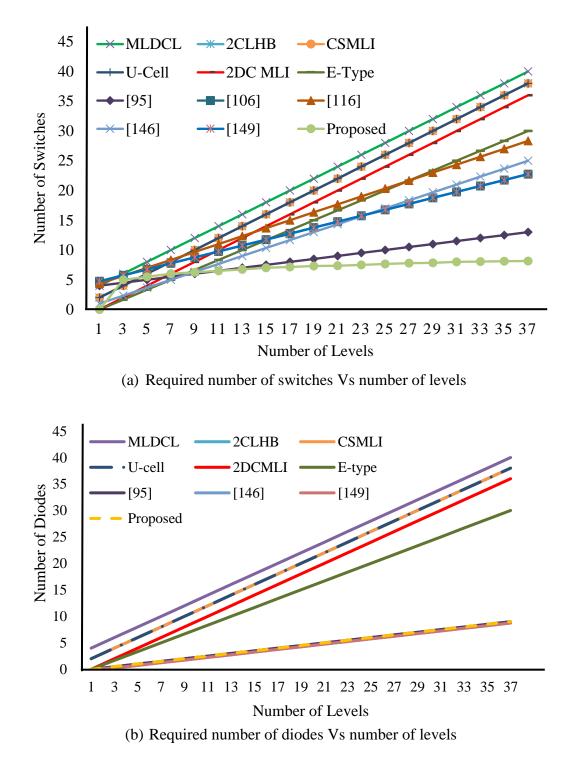

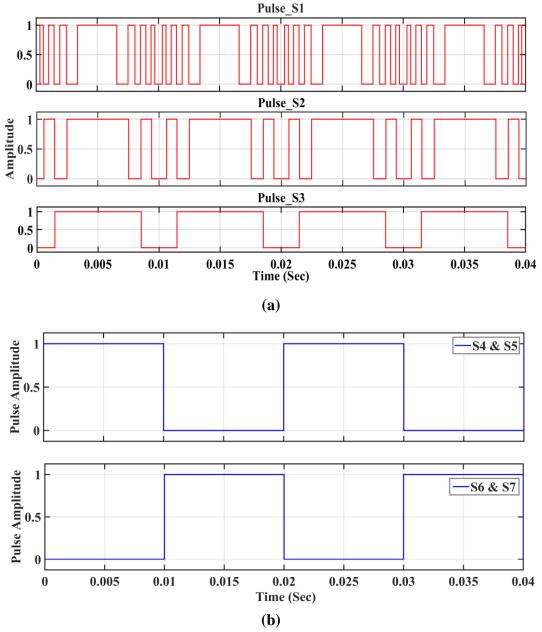

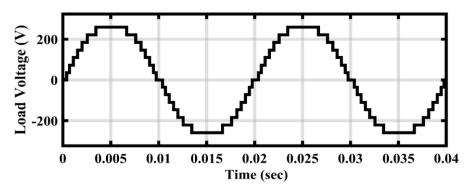

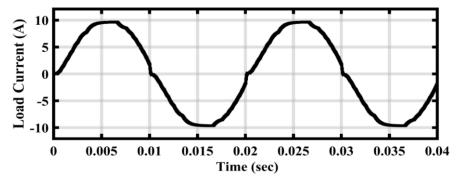

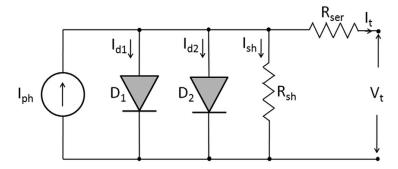

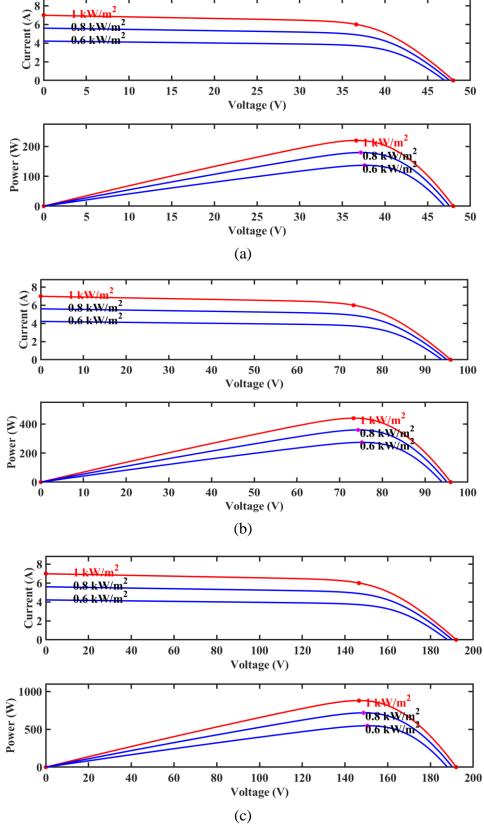

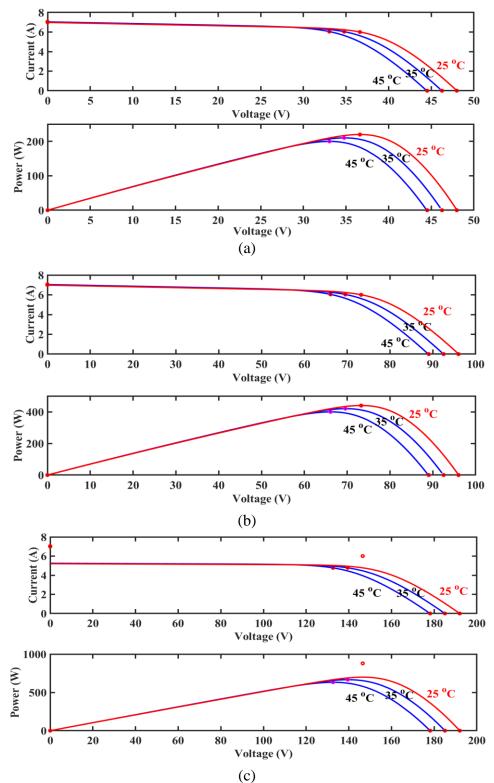

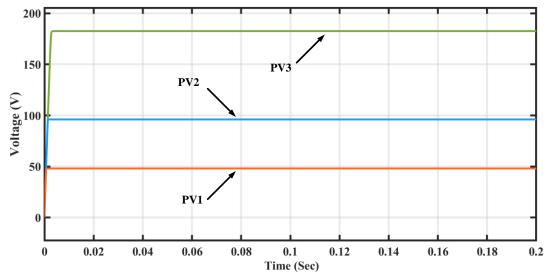

## Table 2.1 Review of grid-connected PV inverters