# DESIGN OF HYBRID NEGATIVE CAPACITANCE FIELD EFFECT TRANSISTOR (HYB-NCFET) FOR LOW POWER VLSI CIRCUITS

Thesis Submitted for the Award of the Degree of

### **DOCTOR OF PHILOSOPHY**

in

Electronics and Communication Engineering

Submitted by Amandeep Singh (41800068)

**Supervised By:**

**Co-Supervised By:**

Dr. Sanjeet Kumar Sinha

Dr. Sweta Chander

Transforming Education Transforming India

## LOVELY PROFESSIONAL UNIVERSITY PUNJAB 2022

### DECLARATION

I hereby declare that the work being presented in this thesis report entitled "DESIGN OF HYBRID NEGATIVE CAPACITANCE FIELD EFFECT TRANSISTOR (HYB-NCFET) FOR LOW POWER VLSI CIRCUITS", is an authentic record of my own work carried out in fulfilment of requirements for the award of degree of Doctor of Philosophy in Electronics and Communication Engineering at Lovely Professional University, Phagwara under the supervision of **Dr. Sanjeet K. Sinha**, Associate Professor, School of Electronics and Electrical Engineering and Co-supervision of **Dr. Sweta Chander**, Assistant Professor, School of Electronics and Electrical Engineering. The matter presented in this thesis has not been submitted elsewhere in part or fully to any other University or Institute for the award of any degree.

Amandeep Singh Registration Number: 41800068 School of Electronics and Electrical Engineering Lovely Professional University Phagwara, Punjab, India.

### CERTIFICATE

This is to certify that Amandeep Singh (Registration Number: 41800068) has completed objective formulation of his thesis titled, "DESIGN OF HYBRID NEGATIVE CAPACITANCE FIELD EFFECT TRANSISTOR (HYB-NCFET) FOR LOW POWER VLSI CIRCUITS" for the award of degree of Doctor of Philosophy in Electronics & Communication Engineering at Lovely Professional University, Phagwara under my guidance and supervision. The matter presented in this thesis has not been submitted elsewhere in part or fully to any other University or Institute for the award of any degree.

Dr. Sanjeet K. Sinha Associate Professor School of Electronics and Electrical Engineering, Lovely Professional University Phagwara, Punjab, India.

Dr. Sweta Chander Assistant Professor School of Electronics and Electrical Engineering, Lovely Professional University Phagwara, Punjab, India.

### ACKNOWLEDGEMENT

I would like to express my deepest gratitude to my supervisor **Dr. Sanjeet K. Sinha**, Associate Professor and my co-supervisor **Dr. Sweta Chander**, Assistant Professor, School of Electronics & Electrical Engineering, Lovely Professional University (Phagwara, Punjab) for their constant support, encouragements, constructive discussions and critical analysis of the research topics. Their positive attitude and belief have always motivated me to carry forward my research even during the days of my struggle. I am truly very fortunate to have the opportunity to work with them. Thank you sir and mam for providing me with the resources for carrying out my research work, for believing in me and motivating me time and again to stretch my limits.

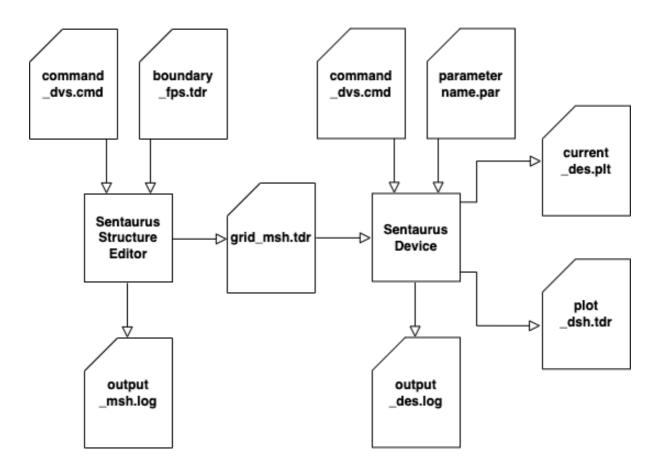

I am grateful to Science and Engineering Research Board (SERB), Department of Science & Technology, Government of India for supporting this work. The simulations and analysis is carried out in Synopsys TCAD Tool funded by **SERB**, **DST**, **CRG/2020/006229**, dated: 05/04/2021.

I am thankful to **Dr. Loviraj Gupta**, Executive Dean, Lovely Faculty of Technology & Sciences, and **Prof. Bhupinder Verma**, HOS, School of Electronics & Electrical Engineering, Lovely Professional University (Phagwara, Punjab) for providing me all the resources and motivation to carry out my research work.

I am thankful to **Dr. Gaurav Sethi,** COS, School of Electronics & Electrical Engineering, **Dr. Rajeev Sobti,** Dean, School of Computer Science Engineering and **Mr. Navdeep Dhaliwal,** HOW, Lovely Professional University (Phagwara, Punjab) for the extended support and guidance throughout my research work.

I am thankful to **Dr. Amandeep Singh,** Associate Professor, National Institute of Technology, Srinagar, and **Dr. Rekha Chaudhary,** Research Associate, Lovely Professional University, Punjab, for their guidance during my initial phase of research work. Their encouragement has instilled a positive attitude in me.

I am highly thankful to **Dr. Ashok Mittal**, Honorable Chancellor, Lovely Professional University (Phagwara, Punjab) for making all the necessary research related licensed software's available at my disposal.

I extend my deepest gratitude to my family members for their love, affection, encouragement and support during this whole journey. To my family, I give everything, including this. I am also thankful to all my colleagues of Electronics and Communication Engineering Department and my friends who contributed directly or indirectly through there constructive criticism in my research work. My acknowledgements would not be complete without expressing my gratitude towards Almighty God. I feel very fortunate to come to know Him during all these months of my life and have continually been blessed by His endless love ever since. I thank God for blessing me with sound health and strength to carry out my work.

Amandeep Singh

# **TABLE OF CONTENTS**

| ACKNOWLEDGEMEN     | VT                                    | iv   |

|--------------------|---------------------------------------|------|

| TABLE OF CONTENT   | S                                     | V    |

| LIST OF FIGURES    |                                       | vii  |

| LIST OF TABLES     |                                       | x    |

| LIST OF SYMBOLS    |                                       | xi   |

| LIST OF ABBREVIAT  | IONS                                  | xiii |

| ABSTRACT           |                                       | XV   |

| CHAPTER 1: INTRODU | UCTION                                | 17   |

| 1.1 CMOS Sca       | aling                                 |      |

| 1.2 Short Char     | nnel Effects in MOSFETs               |      |

| 1.2.1              | Mobility Degradation                  |      |

|                    | 1.2.1.1 Lateral Field Effect          |      |

|                    | 1.2.1.2 Vertical Field Effect         |      |

| 1.2.2              | Drain Induced Barrier Lowering (DIBL) | 19   |

| 1.2.3              | Drain Punch Through                   |      |

| 1.2.4              | Boltzmann's Tyranny                   |      |

| 1.3 New age F      | ET Devices                            |      |

| 1.4 Concept of     | f Negative Capacitance in FETs        | 21   |

| 1.5 Tunnel Fie     | eld Effect Transistor                 |      |

| 1.6 Subthresho     | old Swing in TFETs                    |      |

| 1.7 Ambipolar      | Current in TFETs                      |      |

| CHAPTER 2: LITERAT | ΓURE REVIEW                           |      |

| 2.1 Introduction   | n                                     |      |

| 2.2 Drawbacks      | in TFETs and Reported Improvements    |      |

| 2.3 Literature S   | Survey                                |      |

| 2.4 Problem Sta    | atement and Research Gap              |      |

| 2.5 Objectives     | of Proposed work                      |      |

| 2.6 Research M     | fethodology                           |      |

| CHAPTER 3: MODELLING OF PROPOSED NCTFET DEVICE                                                     | 43 |

|----------------------------------------------------------------------------------------------------|----|

| 3.1 Introduction                                                                                   | 43 |

| 3.2 Model Description                                                                              | 44 |

| 3.2.1 Capacitance Charge Model                                                                     | 44 |

| 3.2.2 Band to Band Tunneling Model                                                                 | 46 |

| 3.2.3 Ferroelectric Material Model                                                                 | 46 |

| 3.3 Device Calibration                                                                             | 48 |

| 3.4 Device Characteristics                                                                         | 48 |

| 3.4.1 Voltage amplification                                                                        | 49 |

| 3.4.2 Transfer Characteristics and Sub-threshold swing                                             | 50 |

| CHAPTER 4: ELECTRICAL CHARACTERISTICS OF PROPOSED DEVICE                                           | 52 |

| 4.1 Introduction                                                                                   | 52 |

| 4.2 Effect of Source Overlapping/Underlapping on Device Performance                                | 53 |

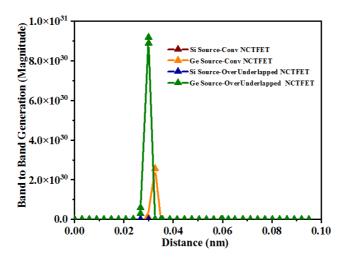

| 4.2.1 Band to Band Generation in Overlapped and Underlapped Structures                             | 54 |

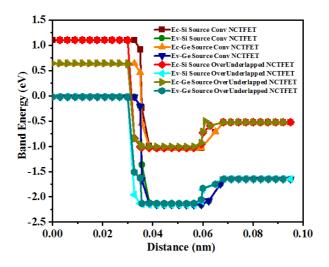

| 4.2.2 Comparison of Energy Band Diagrams with Different Source Materials                           | 55 |

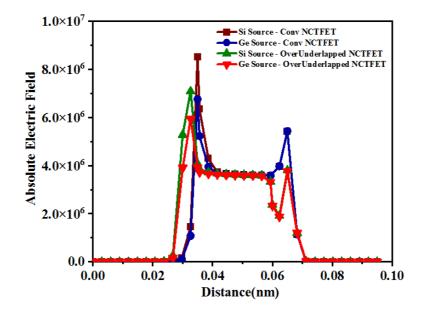

| 4.2.3 Electric Field of Different Source Materials                                                 | 56 |

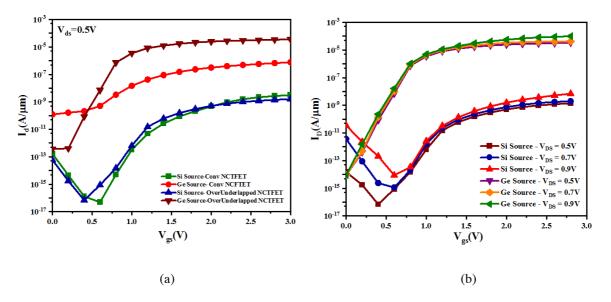

| 4.2.4 Impact of Overlapping/Underlapping with different source materials on $I_D$ -V <sub>GS</sub> | 56 |

| 4.2.5 Impact of Overlapping/Underlapping with different source materials on $I_D$ - $V_D$          | 57 |

| 4.3 Device architectures and their simulation setup                                                | 58 |

| 4.3.1 Effect of Fe Material on performance of NCTFET                                               | 60 |

| 4.3.2 Effect of Fe Thickness on performance of NCTFET                                              | 61 |

| 4.4 Comparison of device characteristics of various NCTFET Devices                                 | 63 |

| 4.4.1 Energy Band Diagram of NCTFET Devices                                                        | 64 |

| 4.4.2 Electric Field of NCTFET Devices                                                             | 65 |

| 4.4.3 Electric Potential of NCTFET Devices                                                         | 66 |

| 4.4.4 eBand to Band Generation of NCTFET Devices                                                   | 66 |

| 4.4.5 Transfer Characteristics of NCTFET Devices                                                   | 67 |

| 4.4.6 Output Characteristics of NCTFET Devices                                                     | 68 |

| 4.4.7 AC Analysis of NCTFET Devices                                                                | 69 |

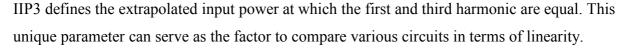

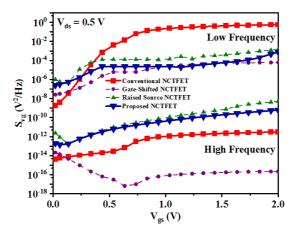

| 4.4.8 Intermodulation Distortion and Linearity Analysis of NCTFET Devices                          | 71 |

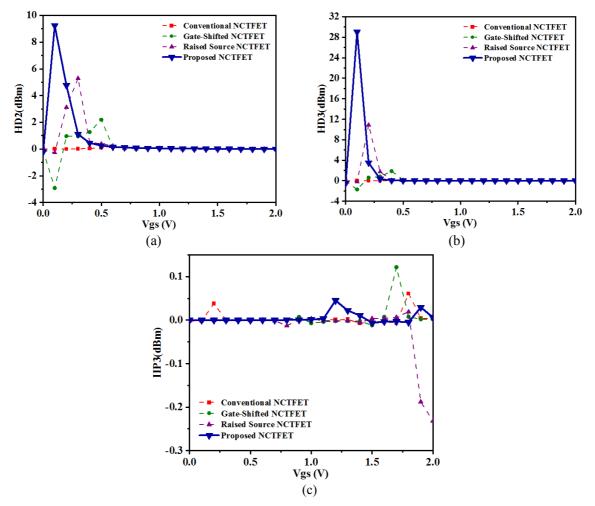

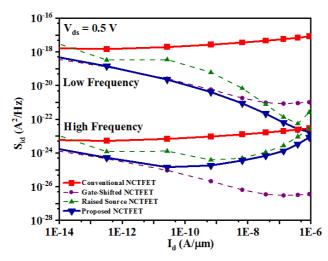

| 4.4.9 Electrical Noise Analysis of NCTFET Devices                        | 74  |

|--------------------------------------------------------------------------|-----|

| CHAPTER 5: IMPLEMENTATION AND ANALYSIS OF LOW POWER INVERTER AND 1T DRAM |     |

| MEMORY USING PROPOSED NCTFET DEVICE                                      | 77  |

| 5.1 Implementation of Inverter using proposed NCTFET device              | 77  |

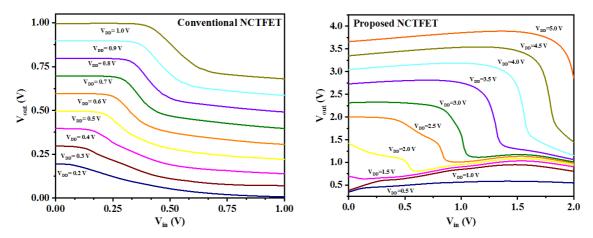

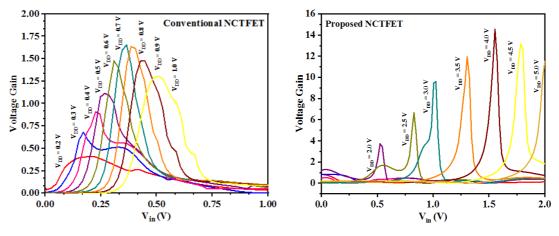

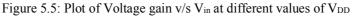

| 5.1.1 Inverter Characteristics                                           | 79  |

| 5.2 Implementation of 1T-DRAM using proposed NCTFET device               | 80  |

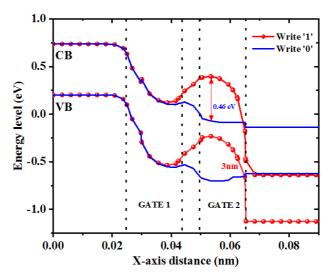

| 5.2.1 Write '1' operation                                                | 82  |

| 5.2.2 Write '0' operation                                                | 82  |

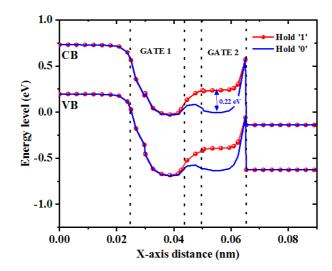

| 5.2.3 Hold operation                                                     | 83  |

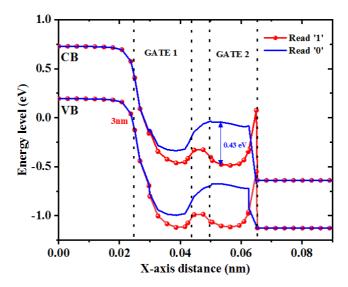

| 5.2.4 Read operation                                                     | 83  |

| CHAPTER 6: CONCLUSION AND FUTURE SCOPE OF THE WORK                       | 85  |

| 6.1 Conclusion                                                           | 85  |

| 6.1.1 Contributions made                                                 | 86  |

| 6.2 Future Scope of the Work                                             | 87  |

| REFERENCES                                                               | 88  |

| APPENDIX                                                                 | 101 |

| LIST OF PUBLICATIONS                                                     | 107 |

## LIST OF FIGURES

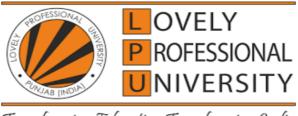

| Figure 1.1 Moore's Law[5]                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

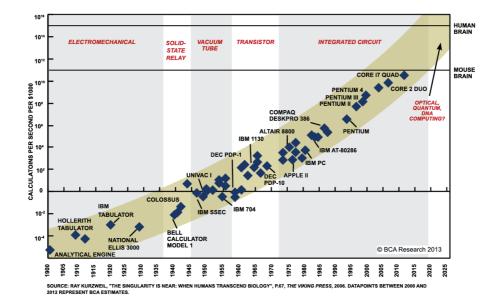

| Figure 1.2 Subthreshold swing in case of MOSFET and TFET[8]20                                                                                                            |

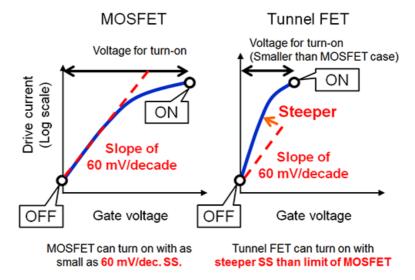

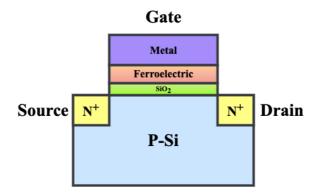

| Figure 1.3 Device Structure of Negative Capacitance FET (NCFET)                                                                                                          |

| Figure 1.4 Schematic Diagram of Negative Capacitance Field Effect Transistor (NCFET)22                                                                                   |

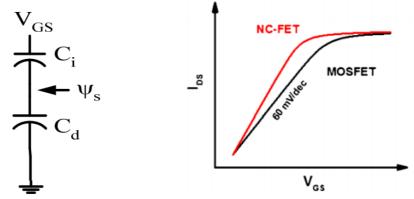

| Figure 1.5 a) Capacitance Model[26] b) Comparison of SS for NCFET and Conventional MOSFET23                                                                              |

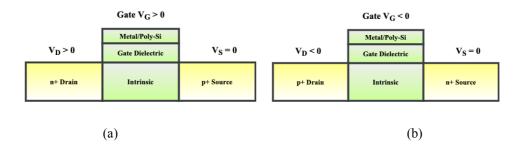

| Figure 1.6 Biasing conditions of (a) n-TFET (b) p- TFET24                                                                                                                |

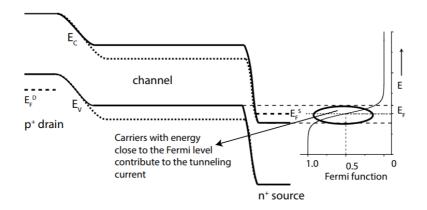

| Figure 1.7 Band diagram at subthreshold region of p-type TFET at two different gate voltages [30]26                                                                      |

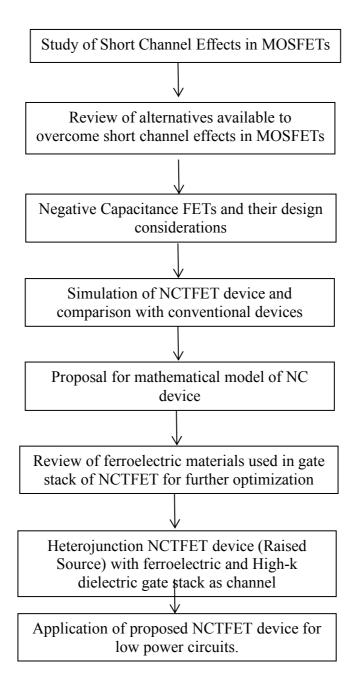

| Figure 2.1 Research Methodology40                                                                                                                                        |

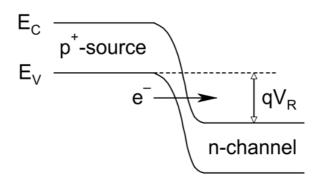

| Figure 3.1 Band Diagram of Heterojunction                                                                                                                                |

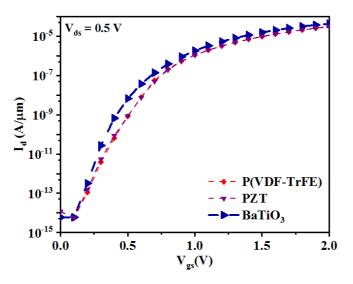

| Figure 3.2 $I_{\text{\tiny D}}V_{\text{\tiny GS}}$ characteristics of proposed NCTFET with various Fe materials                                                          |

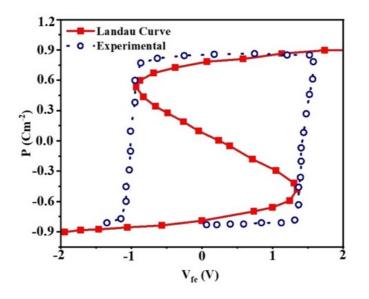

| Figure 3.3 P-V <sub>R</sub> curve of Proposed NCTFET with BaTiO <sub>2</sub> Fe Material                                                                                 |

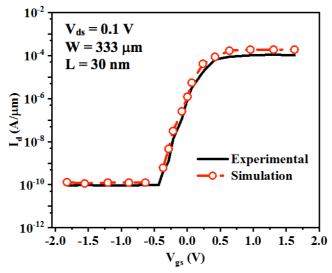

| Figure 3.4 Calibration of TCAD set up of optimized device with experimental data of reported paper [72]49                                                                |

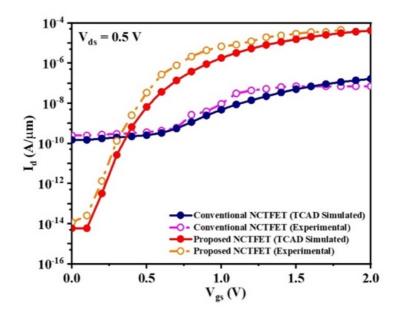

| Figure 3.5 Experimental validation of transfer characteristics of proposed NCTFET against Conventional NCTFET                                                            |

|                                                                                                                                                                          |

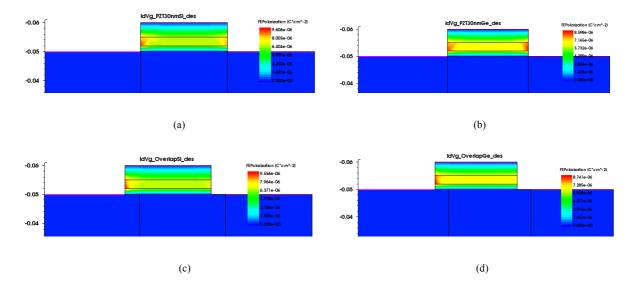

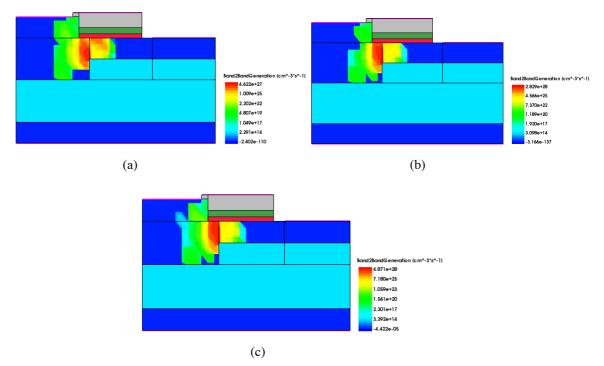

| Figure 4.1: Fe Polarization in case of (a) & (b) for conventional NCTFET with Si and Ge Source (c) & (d) for Proposed NCTFET                                             |

|                                                                                                                                                                          |

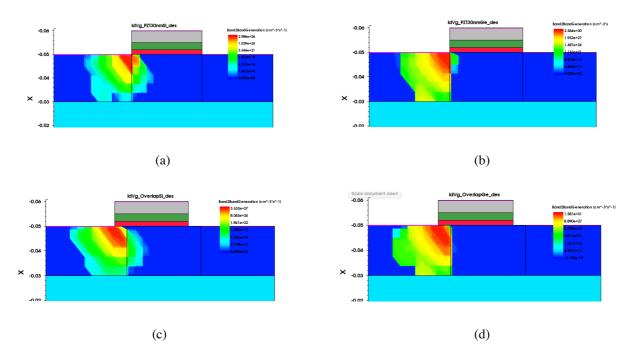

| Figure 4.2 Band to Band Generation (a) Si Source and (b) Ge Source in Conventional NCTFET; (c) Si Source and                                                             |

| (d) Ge Source in Proposed NCTFET                                                                                                                                         |

| Figure 4.3 Band to Band Tunnelling Concentration                                                                                                                         |

| Figure 4.4 Energy Band Diagram for Conventional NCFET and Proposed NCTFET with different sources (Si and                                                                 |

| Ge)                                                                                                                                                                      |

| Figure 4.5 Absolute Electric Field for Conventional NCFET and Proposed NCTFET with different sources (Si and                                                             |

| Ge)                                                                                                                                                                      |

| Figure 4.6 (a) $I_{\text{o}}$ -V <sub>a</sub> characteristics of Conventional NCTFET and Proposed NCTFET with Si and Ge Source (b)                                       |

| $I_{D}$ - $V_{GS}$ characteristics of Proposed NCTFET at different values of $V_{DS}$                                                                                    |

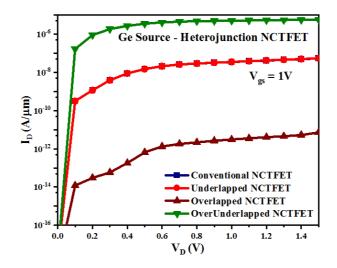

| $Figure \ 4.7 \ I_{\scriptscriptstyle D} V_{\scriptscriptstyle D} \ Characteristics \ in \ case \ of \ Conventional, \ Underlapped, \ Overlapped, \ Proposed \ NCTFET58$ |

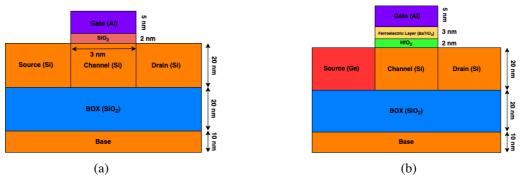

| Figure 4.8 Schematic of (a) Conventional TFET and (b) Negative Capacitance TFET                                                                                          |

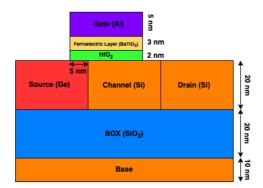

| Figure 4.9 Schematic of Overlapped/Underlapped NCTFET59                                                                                                                  |

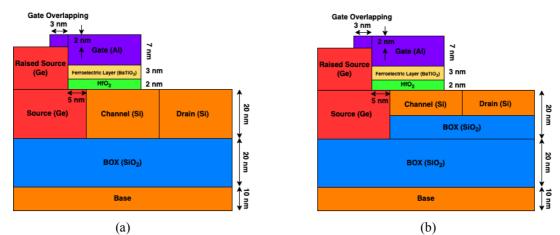

| Figure 4.10 Schematic of (a) Raised Source NCTFET (b) Raised Source Suppressed Channel NCTFET59                                                                          |

| Figure 4.11 Electron Band to Band Generation with (a) BaTiO3 (b) P(VDF-TrFE) (c) PZT Fe Materials60                                                                      |

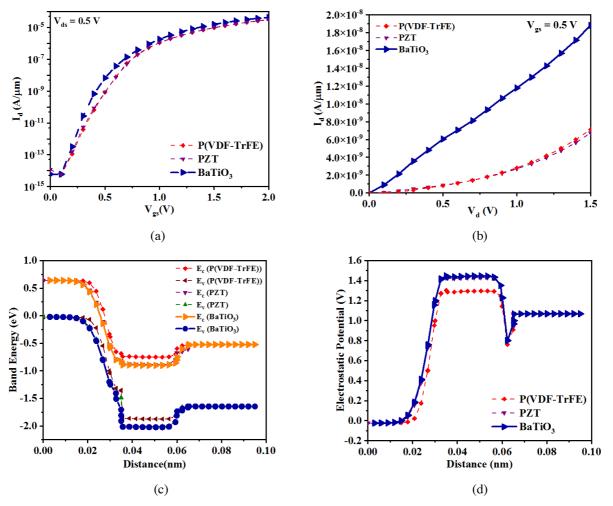

| Figure 4.12 (a) I <sub>D</sub> V <sub>GS</sub> characteristics (b) I <sub>D</sub> V <sub>D</sub> characteristics (c) Energy Band Diagram (d) Electrostatic Potential of  |

| optimized NCTFET with different Fe materials61                                                                                                                           |

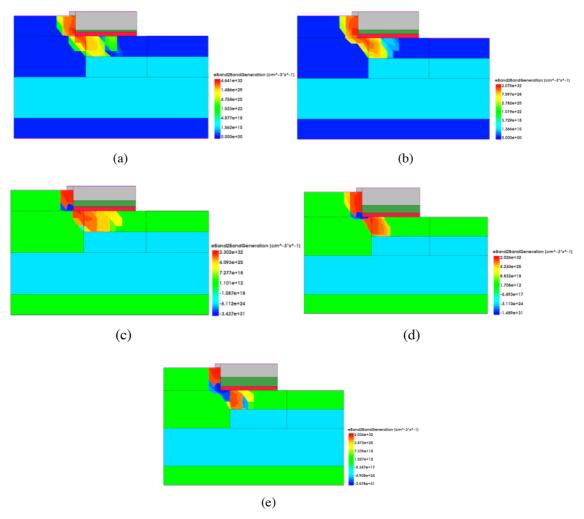

| Figure 4.13 Electron Band to Band Generation in case of Fe Thickness (a) 1nm (b) 2 nm (c) 3 nm (d) 4 nm (e)                                                              |

| 5nm                                                                                                                                                                      |

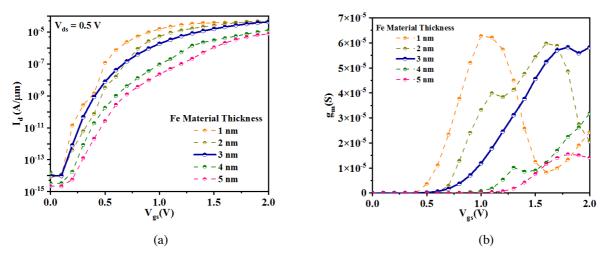

| Figure 4.14 (a) $I_{0}V_{\alpha}$ characteristics (b) $g_{\mu}$ plot for Optimized NCTFET with different Fe material thickness62                                         |

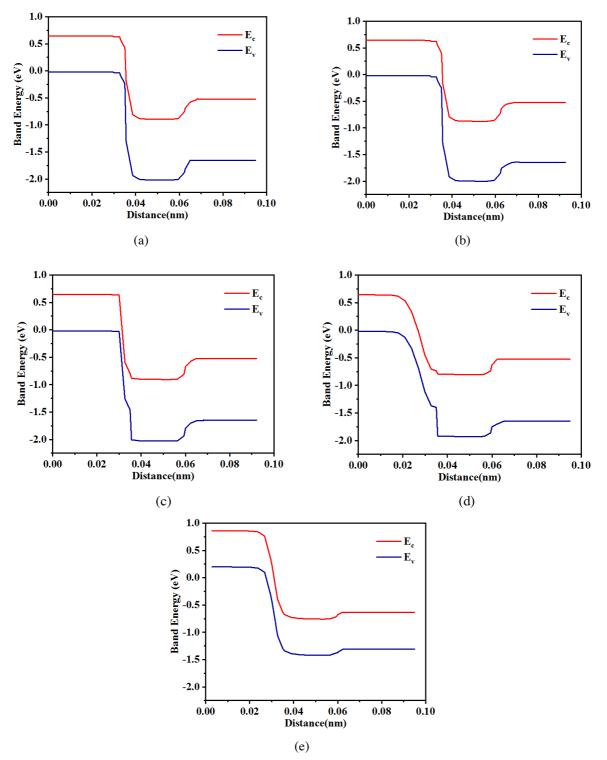

| Figure 4.15 Energy Band Diagram in case of a) Conventional TFET, (b) Conventional NCTFET, (c) Over-                                                                      |

| underlapped NCTFET, (d) Raised source NCTFET and (e) Proposed NCTFET64                                                                                                   |

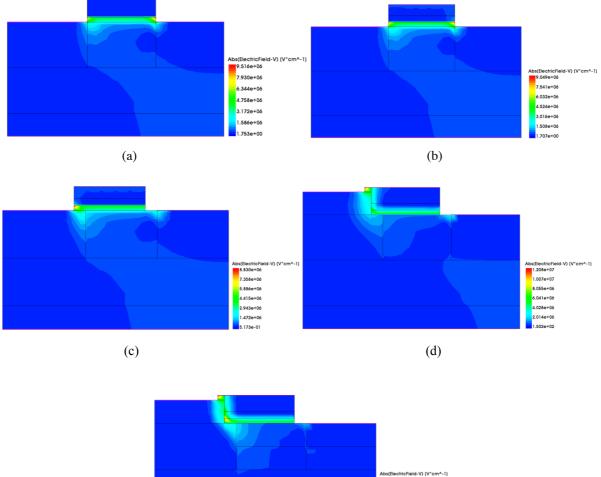

| Figure 4.16 Electric Field Generation in a) Conventional TFET, (b) Conventional NCTFET, (c) Over-underlapped      |

|-------------------------------------------------------------------------------------------------------------------|

| NCTFET, (d) Raised source NCTFET and (e) Proposed NCTFET65                                                        |

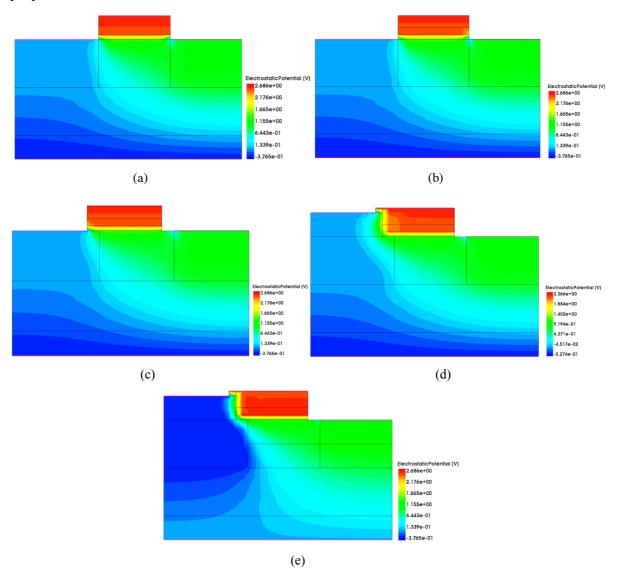

| Figure 4.17 Surface Potential in a) Conventional TFET, (b) Conventional NCTFET, (c) Over-underlapped              |

| NCTFET, (d) Raised source NCTFET and (e) Proposed NCTFET66                                                        |

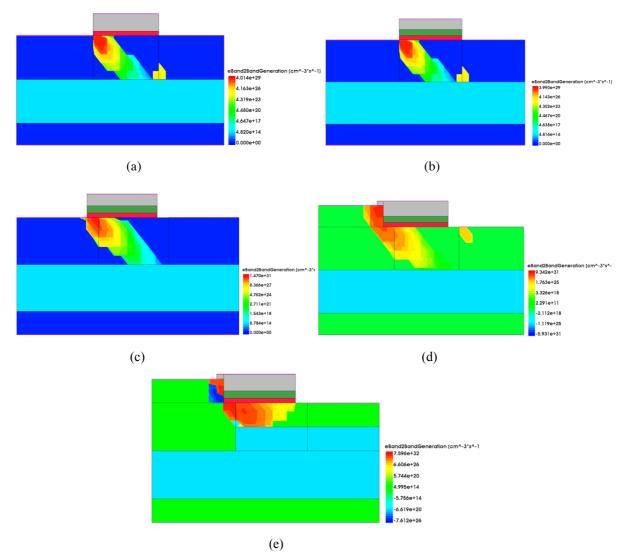

| Figure 4.18 e-Band to Band Generation in a) Conventional TFET, (b) Conventional NCTFET, (c) Over-                 |

| underlapped NCTFET, (d) Raised source NCTFET and (e) Proposed NCTFET67                                            |

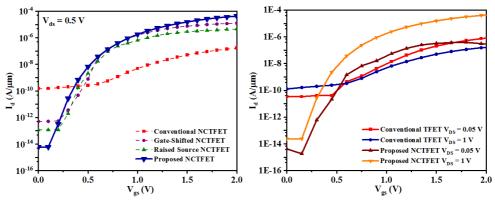

| Figure 4.19 (a) Transfer characteristics of NCTFET devices (b) Plot for calculating DIBL                          |

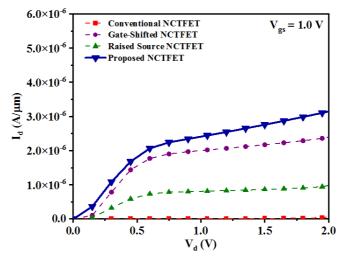

| Figure 4.20 Output Characteristics of simulated devices                                                           |

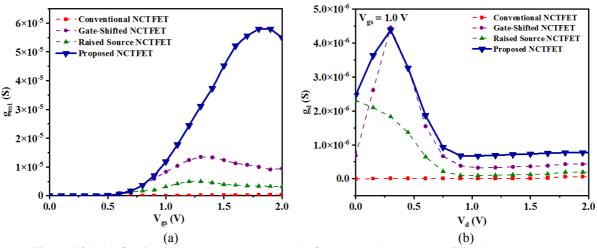

| Figure 4.21 (a) Obtained Transconductance (gm) (b) Output conductance (g <sub>s</sub> ) of simulated structures69 |

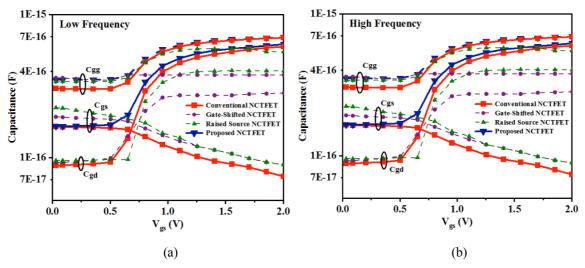

| Figure 4.22 Obtained Capacitance at (a) Low frequency (b) High frequency70                                        |

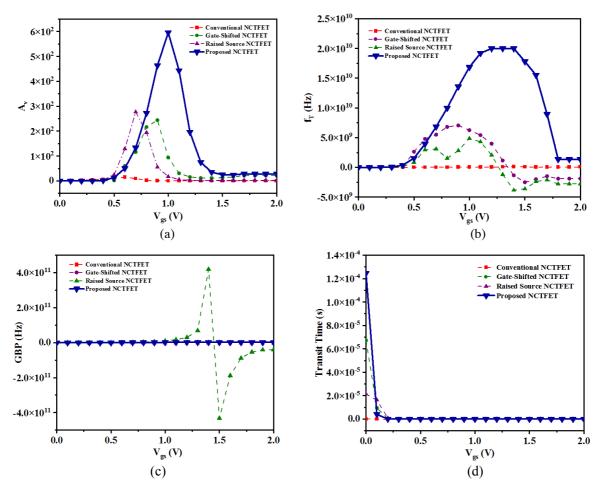

| Figure 4.23 $A_{\nu}$ , $f_{\tau}$ , GBP and Transit Time plot for NCTFET Devices                                 |

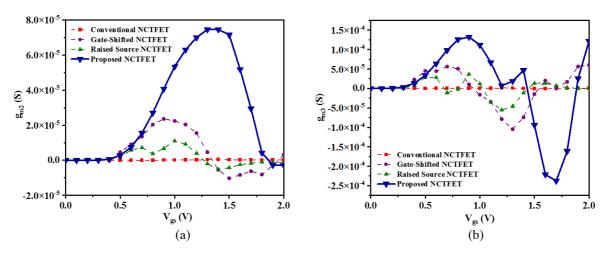

| Figure 4.24 gm <sub>2</sub> and gm <sub>3</sub> plots for NCTFET devices                                          |

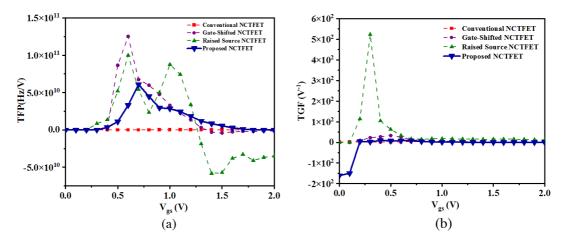

| Figure 4.25 TFP and TGF plots for NCTFET devices72                                                                |

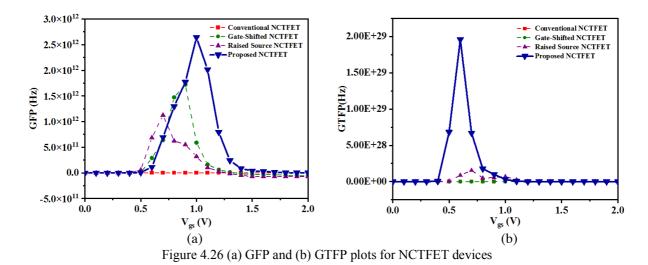

| Figure 4.26 GFP and GTFP plots for NCTFET devices                                                                 |

| Figure 4.27 HD2, HD3 and IIP3 plots for NCTFET Devices                                                            |

| Figure 4.28 SID vs. L at Low frequency and High frequency                                                         |

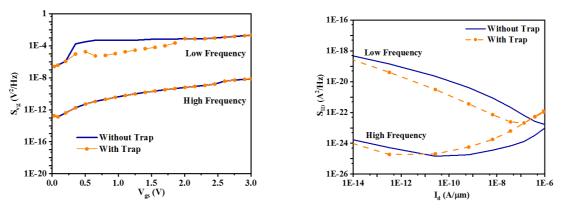

| Figure 4.29 $S_{v_s}$ vs. $V_{g_s}$ at Low and High frequency                                                     |

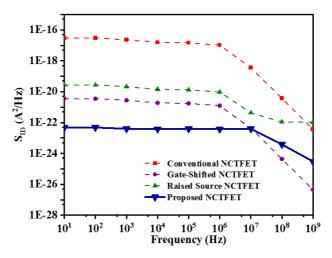

| Figure 4.30 $S_{\text{D}}$ vs. Freq plots for NCTFET Devices                                                      |

| Figure 4.31. (a) $S_{vg} v/s V_{gs}$ (b) $S_{ID} v/s I_d$ with and without traps at Low and High Frequency        |

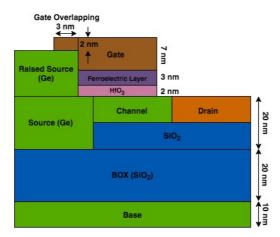

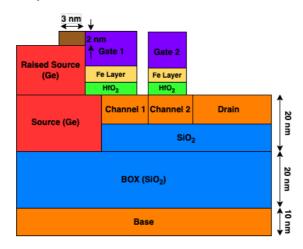

| Figure 5.1 Schematic of Proposed NCTFET Device                                                                    |

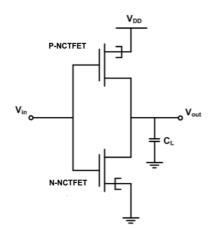

| Figure 5.2 Schematic of NCTFET Inverter                                                                           |

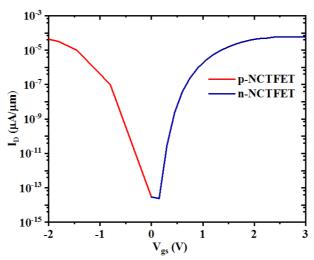

| Figure 5.3 Transfer Characteristics of N-NCTFET and P-NCTFET devices                                              |

| Figure 5.4 Voltage Transfer Characteristics of NCTFET Inverter                                                    |

| Figure 5.5 Voltage gain v/s $V_{in}$ at different values of $V_{DD}$                                              |

| Figure 5.6 Schematic of 1-T DRAM using NCTFET                                                                     |

| Figure 5.7 Energy band diagram during Write '1' and '0' operation                                                 |

| Figure 5.8 Energy band diagram during Hold '1' and '0' operation                                                  |

| Figure 5.9 Energy band diagram during Read '1' and '0' operation                                                  |

## LIST OF TABLES

| Table 3-1: Landau Coefficients for Various Ferroelectric Materials.                    | 47 |

|----------------------------------------------------------------------------------------|----|

| Table 4-1: Device Parameters of NCTFET                                                 | 53 |

| Table 4-2: Design wise changes in Proposed Device in comparison with Conventional TFET | 54 |

| Table 4-3: Design changes done in Conventional TFET to Proposed NCTFET                 | 60 |

| Table 4-4: Device Parameters at Different Fe Thickness                                 | 63 |

| Table 4-5: SID vs Frequency                                                            | 76 |

| Table 5-1: Device Dimensions and Simulation Parameters                                 | 82 |

| Table 5-2: Biasing Conditions of 1T DRAM                                               | 83 |

# LIST OF SYMBOLS

| Cd                                | Depletion capacitance                       |

|-----------------------------------|---------------------------------------------|

| V <sub>TH</sub>                   | Threshold voltage                           |

| Cin                               | Intrinsic capacitance                       |

| Cox                               | Oxide capacitance                           |

| C <sub>eq</sub>                   | Equivalent capacitance                      |

| *                                 | Channel to Source Capacitance               |

| Cs                                | Depolarization field                        |

| EDE                               | -                                           |

| CMOS                              | Semiconductor Capacitance                   |

| C <sub>FE</sub>                   | Ferroelectric Capacitance                   |

| fs(E)                             | Fermi-Dirac distribution function           |

| v(E)                              | Velocity of carriers                        |

| D(E)<br>EFs                       | Density of state                            |

| T                                 | Fermi energy level at source<br>Temperature |

| k                                 | Boltzmann constant                          |

|                                   | Fe material thickness                       |

| T <sub>FE</sub>                   |                                             |

| LCH                               | Channel length                              |

| ρ                                 | Internal resistivity On current             |

| I <sub>ON</sub>                   |                                             |

| IOFF                              | Off/Leakage current                         |

| I <sub>ON</sub> /I <sub>OFF</sub> | Current Ratio                               |

| V <sub>ds</sub>                   | Drain to Source Voltage                     |

| V <sub>DD</sub>                   | Drain Voltage                               |

| $\alpha$ , $\beta$ , and $\gamma$ | Landau constants                            |

| Р                                 | Electric polarization                       |

| Ex                                | Transverse field                            |

| Ey                                | Longitudinal Field                          |

| V <sub>PT</sub>                   | Punch through voltage                       |

| FL                                | Ferroelectric layer                         |

| DL                                | Gate dielectric layer                       |

| e                                 | Electronic charge                           |

| Qg                                | Gate charge                                 |

| Qd                                | Drain charge                                |

| Qb                                | Base charge                                 |

| Qs                                | Source charge                               |

| Qacc                              | Accumulation charge                         |

| Qinv                              | Inversion charge                            |

| Qdep                              | Depletion charge                            |

| Qdep0                             | Depletion charge at zero drain bias         |

| V <sub>FB</sub>                   | Flat band voltage                           |

| h                                 | Reduced planck's constant                   |

| q                                 | Coulomb's charge                            |

| Wactive                           | Width of channel                            |

| $A_{bulk}$ Effective Area $m_r$ Average effective mass $m_e$ Effective mass of electrons in conduction band $m_v$ Effective mass of electrons in valence band $V_{FE}$ Voltage across ferroelectric materialGGibb's energy $F_{barrier}$ Potential across barrier $V_{ox}$ Voltage across oxide layer $A_v$ Voltage across the heterojunction $F_e$ Coercive field $V_{eff}$ Effective voltage across the heterojunction $N_A$ Source doping $N_1$ Channel doping $N_0$ Drain doping $T_{OX}$ Oxide Thickness $L_{sov}$ Source gate overlap length $L_{cout}$ Gate drain underlap length $L_{cout}$ Gate drain capacitance $g_{a0}$ Output Transconductance $g_{a0}$ Output TransconductancesTTemperature $N_t$ Interface trap density $C_{gd}$ Gate-drain capacitance $C_{gs}$ Gate-drain capacitance $C_{gs}$ Gate-drain capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{vin}$ Input Voltage $S_{vig}$ Voltage noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $V_{OIIS}$                                                    | Lactive           | Length of channel                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------|

| mcEffective mass of electrons in conduction band $m_v$ Effective mass of electrons in valence band $V_{FE}$ Voltage across ferroelectric materialGGibb's energyEbarrierPotential across barrier $V_{0x}$ Voltage across oxide layer $A_v$ Voltage aross oxide layer $A_v$ Voltage across the layer $V_{eff}$ Effective voltage across the heterojunction $N_h$ Source doping $N_h$ Drain doping $N_h$ Drain doping $T_{OX}$ Oxide Thickness $L_{SOV}$ Source gate overlap length $L_{GUL}$ Gate drain underlap length $g_m$ Transconductance $g_{m2}$ , $g_{m3}$ Higher order transconductances $T$ Temperature $N_t$ Interface trap density $C_{gd}$ Gate-drain capacitance $C_{gs}$ Gate-drain capacitance $f_T$ Cut-off frequency $\tau$ Transit time <th>A<sub>bulk</sub></th> <th>Effective Area</th> | A <sub>bulk</sub> | Effective Area                                 |

| mvEffective mass of electrons in valence band $W_{FE}$ Voltage across ferroelectric materialGGibb's energyEbarrierPotential across barrier $V_{ox}$ Voltage across oxide layer $A_v$ Voltage amplification $P_r$ Remnant polarization $E_c$ Coercive field $V_{gifet}$ Gate voltage of conventional TFET $V_{eff}$ Effective voltage across the heterojunction $N_A$ Source doping $N_I$ Channel doping $N_D$ Drain dopingToxOxide Thickness $L_{SOV}$ Source gate overlap length $L_{GUL}$ Gate drain underlap length $g_{m}$ Transconductance $g_{m2}$ , $g_{m3}$ Higher order transconductancesTTemperature $N_1$ Interface trap density $C_{gd}$ Gate-drain capacitance $fr$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $S_{vg}$ Voltage noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $V_{GIS}$ Voltage across spate 1                                                                                                                                                                                                                                                                                                                                                                 | mr                | Average effective mass                         |

| ImageVoltage across ferroelectric materialGGibb's energyEbarrierPotential across barrier $V_{ox}$ Voltage across oxide layer $A_v$ Voltage anplificationPrRemnant polarizationEcCoercive field $V_{gifet}$ Gate voltage of conventional TFET $V_{eff}$ Effective voltage across the heterojunctionNASource dopingNrChannel dopingNrChannel dopingToxOxide ThicknessLsovSource gate overlap lengthLGULGate drain underlap lengthgmTransconductancegm2, 2gm3Higher order transconductancesTTemperatureNtInterface trap densityCgdGate-crain capacitancefTransconductancegm1Gate-source capacitancefTransitimeVinInterface trap densityCgdGate-source capacitancefTransitimeVinInput VoltageVinDrain current noise spectral densitySvgVoltage noise spectral density $\lambda$ Tunneling parameterfFrequencyValueVoltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                | m <sub>c</sub>    | Effective mass of electrons in conduction band |

| $V_{FE}$ Voltage across ferroelectric materialGGibb's energyEbarrierPotential across barrier $V_{ox}$ Voltage across oxide layer $A_v$ Voltage across oxide layer $A_v$ Voltage amplification $P_r$ Remnant polarizationEcCoercive field $V_{gflet}$ Gate voltage of conventional TFET $V_{eff}$ Effective voltage across the heterojunction $N_A$ Source doping $N_h$ Channel doping $N_h$ Drain dopingToxOxide ThicknessLsovSource gate overlap lengthLGULGate drain underlap lengthgmTransconductancegm2, gm3Higher order transconductancesTTemperature $N_t$ Interface trap density $C_{gd}$ Gate-frain capacitance $C_{gs}$ Gate-source capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $N_{out}$ Output Voltage $V_{out}$ Output Voltage $N_b$ Drain current noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $V_{G1S}$ Voltage across                                                                                                                              | mv                | Effective mass of electrons in valence band    |

| GGibb's energyEbarrierPotential across barrier $V_{ox}$ Voltage across oxide layer $A_v$ Voltage across oxide layer $A_v$ Voltage amplification $P_r$ Remnant polarization $E_c$ Coercive field $V_{uffet}$ Gate voltage of conventional TFET $V_{eff}$ Effective voltage across the heterojunction $N_A$ Source doping $N_i$ Channel doping $N_D$ Drain dopingToxOxide ThicknessLsovSource gate overlap lengthLGULGate drain underlap length $g_m$ Transconductance $g_{d}$ Output Transconductances $T$ Temperature $N_t$ Interface trap density $C_{gd}$ Gate-drain capacitance $C_{gs}$ Gate-drain capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $V_{out}$ Output Voltage $S_{Vg}$ Voltage noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $V_{GIS}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                 |                   | Voltage across ferroelectric material          |

| VoxVoltage across oxide layer $A_v$ Voltage amplification $P_r$ Remnant polarization $E_c$ Coercive field $V_{gtfet}$ Gate voltage of conventional TFET $V_{eff}$ Effective voltage across the heterojunction $N_A$ Source doping $N_i$ Channel doping $N_D$ Drain doping $Tox$ Oxide Thickness $Lsov$ Source gate overlap length $L_{GUL}$ Gate drain underlap length $g_m$ Transconductance $g_m4$ Output Transconductance $g_m2$ , $g_m3$ Higher order transconductancesTTemperature $N_t$ Interface trap density $C_{gs}$ Gate-drain capacitance $fr$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $S_{vg}$ Voltage noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $V_{G1S}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   | Gibb's energy                                  |

| AvVoltage amplification $P_r$ Remnant polarization $E_c$ Coercive field $V_{gtfet}$ Gate voltage of conventional TFET $V_{eff}$ Effective voltage across the heterojunction $N_A$ Source doping $N_l$ Channel doping $N_D$ Drain dopingToxOxide Thickness $L_{SOV}$ Source gate overlap length $L_{GUL}$ Gate drain underlap length $g_m$ Transconductance $g_{d4}$ Output Transconductance $g_{m2}, g_{m3}$ Higher order transconductancesTTemperature $N_t$ Interface trap density $C_{gd}$ Gate-drain capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $V_{out}$ Output Voltage $V_{GIS}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                           | Ebarrier          | Potential across barrier                       |

| $P_r$ Remnant polarization $E_c$ Coercive field $V_{gffet}$ Gate voltage of conventional TFET $V_{eff}$ Effective voltage across the heterojunction $N_A$ Source doping $N_I$ Channel doping $N_D$ Drain doping $T_{OX}$ Oxide Thickness $Lsov$ Source gate overlap length $LGUL$ Gate drain underlap length $g_m$ Transconductance $g_{dd}$ Output Transconductances $g_{m2}$ , $g_{m3}$ Higher order transconductancesTTemperature $N_t$ Interface trap density $C_{gd}$ Gate-drain capacitance $f_T$ Cut-off frequency $r$ Transit time $V_{in}$ Input Voltage $V_{out}$ Output Voltage $S_{vg}$ Voltage noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $V_{G18}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>ox</sub>   | Voltage across oxide layer                     |

| EcCoercive field $V_{gtfet}$ Gate voltage of conventional TFET $V_{eff}$ Effective voltage across the heterojunctionNASource dopingNIChannel dopingNDDrain dopingToxOxide ThicknessLsovSource gate overlap lengthLGULGate drain underlap lengthgmTransconductancegdOutput TransconductancesTTemperatureNtInterface trap densityCgdGate-drain capacitancefTCut-off frequencyrTransit timeVinInput VoltageVoutOutput VoltageSIDDrain current noise spectral density $\lambda$ Tunneling parameterfFrequency $V_{G18}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Av                | Voltage amplification                          |

| $V_{gtfet}$ Gate voltage of conventional TFET $V_{eff}$ Effective voltage across the heterojunction $N_A$ Source doping $N_I$ Channel doping $N_D$ Drain doping $Tox$ Oxide Thickness $Lsov$ Source gate overlap length $LGUL$ Gate drain underlap length $g_m$ Transconductance $g_{d4}$ Output Transconductances $g_{m2}, g_{m3}$ Higher order transconductancesTTemperature $N_t$ Interface trap density $C_{gd}$ Gate-drain capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $V_{out}$ Output Voltage $S_{vg}$ Voltage noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $V_{G18}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pr                | Remnant polarization                           |

| $V_{eff}$ Effective voltage across the heterojunctionNASource dopingNiChannel dopingNbDrain dopingToxOxide ThicknessLsovSource gate overlap lengthLGULGate drain underlap lengthgmTransconductancegdOutput Transconductancesgm2, gm3Higher order transconductancesTTemperatureNtInterface trap densityCgdGate-drain capacitancecgsGate-drain capacitancefTCut-off frequency $\tau$ Transit timeVinInput VoltageVoutOutput VoltageStiDDrain current noise spectral density $\lambda$ Tunneling parameterfFrequencyVG18Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Ec                | Coercive field                                 |

| NaSource dopingNaSource dopingNbDrain dopingToxOxide ThicknessLsovSource gate overlap lengthLGULGate drain underlap lengthgmTransconductancegdOutput Transconductancesgm2, gm3Higher order transconductancesTTemperatureNtInterface trap densityCgdGate-drain capacitanceCgdGate-drain capacitancefTCut-off frequency $\tau$ Transit timeVinInput VoltageVoutOutput VoltageStipDrain current noise spectral density $\lambda$ Tunneling parameterfFrequency $\chi_{G1S}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Vgtfet            | Gate voltage of conventional TFET              |

| N1Channel dopingNDDrain dopingToxOxide ThicknessLsovSource gate overlap lengthLGULGate drain underlap lengthgmTransconductancegdOutput Transconductancesgm2, gm3Higher order transconductancesTTemperatureNtInterface trap densityCgdGate-drain capacitanceCgsGate-source capacitancefrCut-off frequency $\tau$ Transit timeVinInput VoltageVoutOutput VoltageStiDDrain current noise spectral density $\lambda$ Tunneling parameterfFrequencyVG1SVoltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>eff</sub>  | Effective voltage across the heterojunction    |

| NDDrain dopingToxOxide ThicknessLsovSource gate overlap length $L_{GUL}$ Gate drain underlap length $g_m$ Transconductance $g_d$ Output Transconductance $g_{m2}, g_{m3}$ Higher order transconductancesTTemperatureNtInterface trap density $C_{gd}$ Gate-drain capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $V_{out}$ Output Voltage $V_{out}$ Output Voltage $S_{Vg}$ Voltage noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $V_{G1S}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | NA                | Source doping                                  |

| ToxOxide ThicknessLsovSource gate overlap lengthLGULGate drain underlap length $g_m$ Transconductance $g_d$ Output Transconductance $g_{m2}, g_{m3}$ Higher order transconductancesTTemperatureNtInterface trap density $C_{gd}$ Gate-drain capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $V_{out}$ Output Voltage $V_{out}$ Drain current noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $\chi_{G1s}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | NI                | Channel doping                                 |

| LsovSource gate overlap length $L_{GUL}$ Gate drain underlap length $g_m$ Transconductance $g_d$ Output Transconductance $g_{m2}, g_{m3}$ Higher order transconductancesTTemperatureNtInterface trap density $C_{gd}$ Gate-drain capacitance $C_{gs}$ Gate-source capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $V_{out}$ Output Voltage $S_{Vg}$ Voltage noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $V_{G1S}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ND                |                                                |

| LGULGate drain underlap length $g_m$ Transconductance $g_d$ Output Transconductance $g_{m2}, g_{m3}$ Higher order transconductancesTTemperatureNtInterface trap density $C_{gd}$ Gate-drain capacitance $C_{gs}$ Gate-source capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $V_{out}$ Output Voltage $S_{ID}$ Drain current noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $V_{G1S}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Tox               | Oxide Thickness                                |

| $g_m$ Transconductance $g_d$ Output Transconductance $g_{m2}, g_{m3}$ Higher order transconductancesTTemperatureNtInterface trap density $C_{gd}$ Gate-drain capacitance $C_{gs}$ Gate-source capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $V_{out}$ Output Voltage $S_{ID}$ Drain current noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $V_{G1S}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Lsov              | Source gate overlap length                     |

| $g_{d}$ Output Transconductance $g_{m2}, g_{m3}$ Higher order transconductancesTTemperatureNtInterface trap density $C_{gd}$ Gate-drain capacitance $C_{gs}$ Gate-source capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $V_{out}$ Output Voltage $S_{ID}$ Drain current noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $V_{G1S}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Lgul              | Gate drain underlap length                     |

| $g_{m2}, g_{m3}$ Higher order transconductancesTTemperatureNtInterface trap density $C_{gd}$ Gate-drain capacitance $C_{gs}$ Gate-source capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $S_{ID}$ Drain current noise spectral density $S_{vg}$ Voltage noise spectral density $\lambda$ Tunneling parameterfFrequencyVG1SVoltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | g <sub>m</sub>    | Transconductance                               |

| TTemperature $N_t$ Interface trap density $C_{gd}$ Gate-drain capacitance $C_{gs}$ Gate-source capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $V_{out}$ Output Voltage $S_{ID}$ Drain current noise spectral density $\lambda$ Tunneling parameter $f$ Frequency $V_{G1S}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | gd                | Output Transconductance                        |

| $N_t$ Interface trap density $C_{gd}$ Gate-drain capacitance $C_{gs}$ Gate-source capacitance $f_T$ Cut-off frequency $\tau$ Transit time $V_{in}$ Input Voltage $V_{out}$ Output Voltage $S_{ID}$ Drain current noise spectral density $\lambda$ Tunneling parameter $f$ FrequencyVG1SVoltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | gm2, gm3          | Higher order transconductances                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Т                 | Temperature                                    |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Nt                | Interface trap density                         |

| $\begin{array}{c c} f_{T} & Cut-off \ frequency \\ \hline \tau & Transit \ time \\ \hline V_{in} & Input \ Voltage \\ \hline V_{out} & Output \ Voltage \\ \hline S_{ID} & Drain \ current \ noise \ spectral \ density \\ \hline S_{vg} & Voltage \ noise \ spectral \ density \\ \hline \lambda & Tunneling \ parameter \\ \hline f & Frequency \\ \hline V_{G1S} & Voltage \ across \ gate \ 1 \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Cgd               | Gate-drain capacitance                         |

| $\tau$ Transit time $V_{in}$ Input Voltage $V_{out}$ Output Voltage $S_{ID}$ Drain current noise spectral density $S_{vg}$ Voltage noise spectral density $\lambda$ Tunneling parameterfFrequency $V_{G1S}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Cgs               | Gate-source capacitance                        |

| $\begin{tabular}{ c c c c } \hline V_{in} & Input Voltage \\ \hline V_{out} & Output Voltage \\ \hline S_{ID} & Drain current noise spectral density \\ \hline S_{vg} & Voltage noise spectral density \\ \hline \lambda & Tunneling parameter \\ \hline f & Frequency \\ \hline V_{G1S} & Voltage across gate 1 \\ \hline \end{tabular}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | fT                | Cut-off frequency                              |

| $\begin{tabular}{ c c c c } \hline V_{out} & Output Voltage \\ \hline V_{out} & Output Voltage \\ \hline S_{ID} & Drain current noise spectral density \\ \hline S_{vg} & Voltage noise spectral density \\ \hline \lambda & Tunneling parameter \\ \hline f & Frequency \\ \hline V_{G1S} & Voltage across gate 1 \\ \hline \end{tabular}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | τ                 | Transit time                                   |

| $\begin{tabular}{ c c c c c } \hline S_{ID} & Drain current noise spectral density \\ \hline S_{Vg} & Voltage noise spectral density \\ \hline $\lambda$ & Tunneling parameter \\ \hline $f$ & Frequency \\ \hline $V_{G1S}$ & Voltage across gate 1 \\ \hline \end{tabular}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Vin               | Input Voltage                                  |

| $\begin{tabular}{ c c c c c } \hline S_{Vg} & Voltage noise spectral density \\ \hline $\lambda$ & Tunneling parameter \\ \hline $f$ & Frequency \\ \hline $V_{G1S}$ & Voltage across gate 1 \\ \hline \end{tabular}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>out</sub>  | Output Voltage                                 |

| $\begin{tabular}{ c c c c c } \hline $\lambda$ & Tunneling parameter \\ \hline $f$ & Frequency \\ \hline $V_{G1S}$ & Voltage across gate 1 \\ \hline \end{tabular}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SID               | Drain current noise spectral density           |

| λ         Tunneling parameter           f         Frequency $V_{G1S}$ Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Svg               | Voltage noise spectral density                 |

| f     Frequency       VG1S     Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   | Tunneling parameter                            |

| V <sub>G1S</sub> Voltage across gate 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | f                 |                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>G1S</sub>  |                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>G2S</sub>  | Voltage across gate 2                          |

# LIST OF ABBREVIATIONS

| CMOS         Complementary Metal Oxide Semiconductor Field Effect Transistor           VLSI         Very Large Scale Integration           FET         Field Effect Transistor           MOSFET         Metal Oxide Semiconductor Field Effect Transistor           TFET         Tunnel Field Effect Transistor           SS         Subthreshold Swing           FinFET         Fin Field Effect Transistor           DIBL         Drain induced barrier lowering           DIBL         Drain induced barrier lowering           NCTFET         Negative Capacitance Field Effect Transistor           LK Equation/Model         Landau-Khalatnikov Equation/Model           PZT         Lead Zirconate Titanate           P(VDF-TrFe)         Poly(Vinylidene Fluoride-trifluoroethylene           SBT         Strontium Bismuth Tantalate           BaTiO3         Barium Titanate           P(VDF-TrFe)         Poly(Vinylidene Fluoride-trifluoroethylene           SIG2         Silicon Dioxide           CNTFET         Carbon Nanotube Field Effect Transistor           TTI         Transistor Transistor Logic           TTI         Transistor Transistor Iogic           TTET         Lateral Tunnel Field Effect Transistor           VTFET         Vertical Tunnel Field Effect Transistor <t< th=""><th></th><th></th></t<>                         |                                  |                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------|

| FET     Field Effect Transistor       MOSFET     Metal Oxide Semiconductor Field Effect Transistor       TFET     Tunnel Field Effect Transistor       SS     Subthreshold Swing       FinFET     Fin Field Effect Transistor       DIBL     Drain induced barrier lowering       BTIBT     Band to Band Tunnelling       NCTFET     Negative Capacitance Field Effect Transistor       LK Equation/Model     Landau-Khalatnikov Equation/Model       PZT     Lead Zirconate Titanate       P(VDF-TrFe)     Poly(Vinylidene Fluoride-trilluoroethylene       SBT     Strontium Bismuth Tantalate       BaTiO <sub>3</sub> Barium Titanate       HZO/ HfO <sub>2</sub> Hafnium Oxide       SiO <sub>2</sub> Silicon Dioxide       CNTFET     Carbon Nanotube Field Effect Transistor       TTL     Transistor Transistor Logic       LTFET     Lateral Tunnel Field Effect Transistor       VTFET     Vertical Tunnel Field Effect Transistor       VTFET     Vertical Tunnel Field Effect Transistor       UTBB     Ultra-thin hody and ultra-thin insulator       SG-FET     Suspended gate FET       ADC     Analog to digital converter       PLLs     Phase locked loops       VTC     Voltage to time converter       IF     Interfacial       BOX     Barlium arsenide <td>CMOS</td> <td>Complementary Metal Oxide Semiconductor Field Effect Transistor</td> | CMOS                             | Complementary Metal Oxide Semiconductor Field Effect Transistor |