# DESIGN AND IMPLEMENTATION OF EZ-PASS ROUTER FOR ENERGY AND PERFORMANCE EFFICIENT NETWORK ON CHIPS

Thesis Submitted For the Award of the Degree of

# DOCTOR OF PHILOSOPHY

in

**Electronics and Communication Engineering**

By

Mr.Ashish Ashok Mulajkar

(41800225)

Supervised By Dr.Sanjeet K Sinha

Co-Supervised by

Dr.Govind Singh Patel

LOVELY PROFESSIONAL UNIVERSITY

PUNJAB

2022

## **DECLARATION**

I hereby declare that the thesis entitled "Design and Implementation of EZ-Pass Router For Energy and Performance Efficient Network on Chips" has been prepared and submitted by me under the guidance of Supervisor Dr. Sanjeet K. Sinha, Associate Professor, School of Electronics & Electrical Engineering, Lovely Professional University, Phagwara, Punjab and Co-Supervisor Dr. Govind Singh Patel, Professor, Department of Electronics & Telecommunication Engineering, SITCOE, Ichalkaranji, Maharashtra as per the requirement for the award of the degree of Doctor of Philosophy (Ph.D.) in Electronics & Communication Engineering is entirely my original work and ideas, references are duly acknowledged. It does not contain any work that has been submitted for the award of any other degree or diploma from any University.

Mough

Mr. Ashish A Mulajkar

Reg. No- 41800225 Lovely Professional University, Phagwara, Punjab, India.

# **CERTIFICATE**

This is to certify that Mr. Ashish Ashok Mulajkar has completed his Doctor of Philosophy (Ph.D.) in Electronics & Communication Engineering thesis entitled "Design and Implementation of EZ-Pass Router For Energy and Performance Efficient Network on Chips" is a bonafide work carried out by him under my supervision and guidance. To the best of my knowledge, the present work is the result of his original investigation and study. No part of the thesis has ever been submitted to any other University or Institute for the award of any degree or diploma.

39

03

## Dr.Sanjeet K. Sinha

# **Supervisor**

Associate Professor,

School of Electrical & Electronics Engineering,

Lovely Professional University,

Phagwara, Punjab, India

#### **Dr.Govind Singh Patel**

#### **Co-Supervisor**

Professor,

**E&TC** Department

SITCOE,

Ichalkaranji, MH, India

#### ABSTRACT

Network-on-chips is developed as the typical transmission framework to connect Processing Elements and memories on the chip. The NoC acts in areas of enhanced security of networks and also helps to resolve queries in the networking domain. NoC delivers lower scalability, lesser latency and power between PEs associated with chip. Nowadays static power is considered as a leading ingredient in the power utilization in routers while scaling down the technology into a nanometer systems. Also, the effectiveness of the NoC can be influenced by the most important component called buffer because it consumes more power. The area overhead of the NoC architecture design must be minimized for improving the efficiency of the design. In this thesis work a power-gating method is utilized to reduce static power by disabling the power delivered to the routers during their idle condition. Also, an enhanced bypass path method is introduced for reducing the latency during the low traffic condition. But, the main limitations of NoC arbitrations are traffic starvation, worse speed, complication, pipelining, and weak fairness difficulties. The method proposed in this thesis gives suitable solutions to the above limitations.

In the fields of multiprocessing chip architecture and elevated computation, NoCs are becoming increasingly significant. System execution can be upgraded by reducing use of superfluous hardware in router architecture without activating all settings. This study conducts a practical review of several routers that will be used in the future of networking. This analysis looks at the most common interconnection network technologies as well as some new topologies. To reduce latency, enhance throughput of a router, reduce loss of power, design area are the utmost outcomes of this project. A brief comparison of previously constructed several routers as well as design factors for the 3D Torus router is discussed in this thesis work. Also examined were their performance along with their advantages and disadvantages. NoCs is a popular communication channel for connecting several processors and memory modules on a single chip. NoCs

utilize a bigger portion of the whole chip architecture, resulting in higher power costs. The issue comes when the transistor is scaled down.

NOC provides an important router design on comparison with SoCs. NoC provides superior results to the ad-hoc based and bus-based designs since it offers cheap latency, low scalability, and power over processing elements that are linked to a chip. When there is less traffic, the advanced bypass path approach is employed to reduce packet arrival latency. On-chip design area occupancy also gets reduced to improve chip performance. In router design, an EB (Elastic Buffer) control mechanism is utilized to eliminate the cost of the buffer. In such situations, , it becomes essential to propose router with powerefficient routing as well as discard buffer cost In order to make a power-efficient router design, low power NoC router architecture based on Easy Pass (EZ-Pass) routing with IRR and UFDQ is proposed in this system. An advanced NoC router architecture is initiated to enhance the EZ-pass routing and input-port modules of the router architecture with IRR and UFDQ respectively. The proposed circuit includes both a conventional router and an EZ-Pass switch to handle high-traffic, sporadic and low-traffic modes respectively. The IRR arbiter has very short arbitration latency, low power consumption, and a small chip area. In a traditional port topology, the number of multiplexers is grown exponentially as the area of the input buffer is enlarged. Critical track latency, router hardware, and power consumption overhead will skyrocket in this instance. To address these concerns, UFDQ is presented as a way to boost router performance. UFDQ improves router performance at varied injection rates while consuming less power.

A basic partition table is being used by UFDQ for controlling the input port buffer structure. NoC's performance analysis design which is using BLESS, TCMP, BBUS NoC and CHIPPER router design is explained. The NoC module in router architecture is, responsible for connecting chip cores and memory components. Bus and ad-hoc architectures were employed in previous attempts however, NoC is a better option. It provides low scalability, low power, and low latency between computing components embedded on-chip. An improved bypass method is being used when there is less traffic to

reduce packet arrival delay. To increase area utilization and chip performance in the onchip design should also be reduced. In router design, an Elastic Buffer control mechanism is utilized to eliminate the expanse of buffers. The usage of virtual channels reduces the chips size, latency as well as power loss.

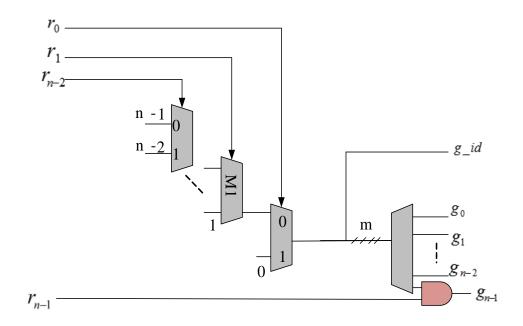

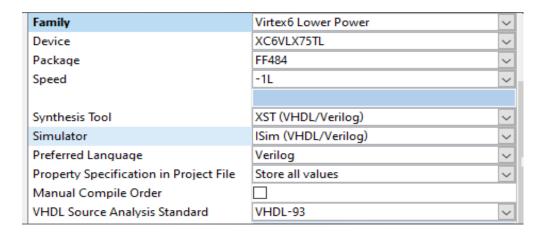

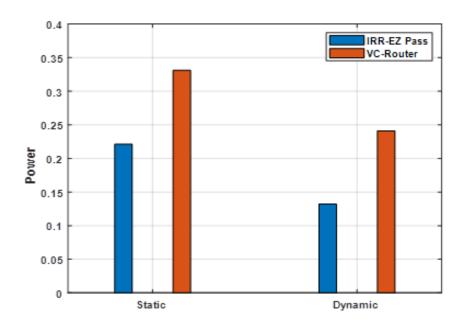

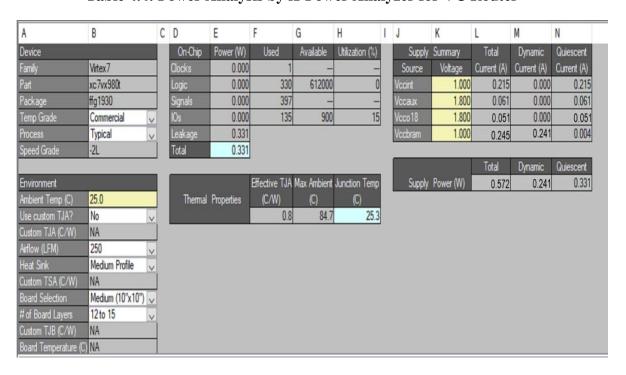

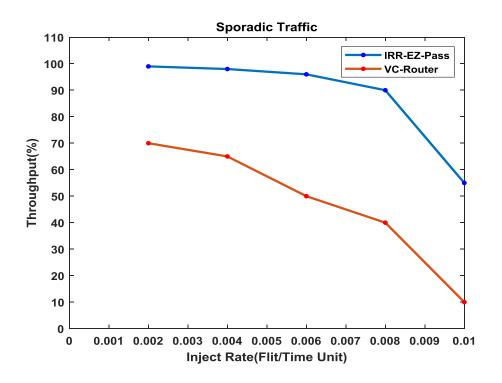

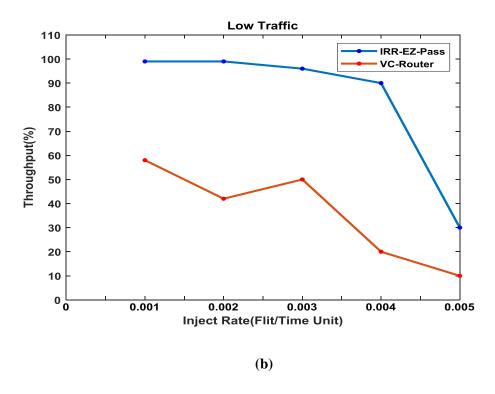

Here, the model of BBUS NoC is deliberated for tackling the latency issue of CHIPPERbased NoC. The proposed router is synthesized using the family of Virtex 6 with device XC6VLX75TL and package FF484. Simulation result shows the potency of IRR on EZ pass routing through the requirement of 41.05% lesser combinational elements and 75 % lesser registers as compared to the RoR arbiter for 16-bit input formation. Simulation remarks also shows a framework which surges bandwidth of router design which requires only 349 Slice LUT and 277 slice registers on FPGA. This proves the efficiency of the proposed router on 16x16 Mesh topology. Also, the concept of Golden Packets is elaborated in terms of BBUS and CHIPPER routers at a lower rate of injection. However, the area overhead of the BLESS is the same as that of the CHIPPER design. The experimental results show that the IRR-EZ pass switch consumes 11% less power as compared to the VC router with UFDQ for 16x16 Mesh topology. The latency of the proposed structure is about 75% less in comparison to VC router while assuming very low rate of injection of 0.005 flits/cycle/node for low traffic. In sporadic traffic mode when the rate of injection is 0.01 flits/time/unit throughput of the VC router is about 40% and the IRR-EZ-Pass router throughput is 90%. In the low traffic mode when the rate of injection is 0.005 flits/time/unit throughput of the VC router is about 20% and the IRR-EZ-Pass router throughput is 80%. A simulation result signifies that the throughput of the novel IRR-EZ-Pass system is higher in accordance with traditional Virtual Channel Router during low as well as a sporadic bottleneck.

**Keywords:-** Network on Chip (NoC), Mesh Topology, Static Power, Easy pass (EZ), Index based round robin (IRR), Arbiter, VC Router, Buffer-less (BLESS), Ultra-fast Dynamic Queues (UFDQ), TCMP, CHIPPER.

#### **ACKNOWLEDGEMENT**

The successful completion of any task would be incomplete without complementing those who made it possible, under whose guidance and encouragement, the efforts are made successful. First of all, I acknowledge without hesitation, the grace of god the Almighty, in this arduous journey, it is he alone who deserves all the credit for this work. I owe my sincere gratitude to my project supervisor **Dr. Sanjeet K. Sinha**, Associate Professor, Lovely Professional University, Punjab, India for his valuable guidance, direction, and persistent encouragement. He has always motivated me and supported me in the constructive and creative process of the entire research journey. It is really a matter of pride and joy for me to work under his guidance. I hope to seek his guidance for my future endeavors also. I owe my sincere gratitude to my project Co-supervisor **Dr. Govind Singh Patel**, Professor, SITCOE, Ichalkaranji, Maharashtra, India for his vital guidance, direction, and persistent encouragement. He has always motivated me and supported me in the constructive and creative process of the entire research journey. It is really a matter of pride and joy for me to work under his guidance. I hope to seek his guidance for my future endeavors also.

I would also like to express my deeply felt gratitude to the Department of Research Program, Lovely Professional University, Punjab, India for providing me with an opportunity to work in the best academic environment.

I also would like to thank **Dr. Bhupinder Verma**, Professor & Dean, School of Electrical & Electronics Engineering, Lovely Professional University, Punjab for his kind support.

I am also thankful to **Dr. Prasantha Reddy**, **Dr. Suman Lata Tripathi**, **Dr. Sweta Chander**, **Dr. Cherry Bhargava**, and **Dr. Manwinder Singh** for their kind support.

I would also like to express my deeply felt gratitude to **Padmashree Dr. D. Y. Patil**, Founder President D. Y. Patil Group, **Dr. Vijay D. Patil**, President, and Chancellor D. Y. Patil University, Ambi, Pune for providing unconditional support during this journey.

I also would like to thank **Dr. Adv. Sushant V. Patil**, and all staff members of D. Y. Patil Technical Campus, Ambi, Pune for their kind support.

I am really grateful to Dr. Sayalee Gankar, Vice Chancellor, D. Y. Patil University,

Ambi, Pune, for her kind support.

I am really thankful to Mr. B. V. Gaikwad, Admin Officer, D. Y. Patil University, Ambi,

Pune, for his kind support.

I am really thankful to **Dr. Rajesh Kherde**, Principal, D. Y. Patil School of Engineering

Academy, Ambi, Pune, for his kind support.

I also would like to extend special thanks to my colleague friends Dr.Moresh

Mukhedkar, Mr. Vinod Bharat and Dr. Sandeep Shelke for their valuable suggestions,

support, and encouragement. Many thanks to D. Y. Patil Technical Campus colleagues

for their kind support.

I am really happy to be blessed and encouraged by my Mother Ms.Pushpa Mulajkar,

My father Late. Ashok N Mulajkar, My Brother in law Shri. Amol Khamaswadikar,

My Sister Mrs. Amruta A Khamaswadikar. I also express sincere gratitude to all my

family members. I really have no words to express my feelings for them.

It is a great privilege to express my profound thankfulness, deep love, and fondness to my

wife Mrs. Mrudula, and my dearest son Anvit, who stood like a rock in my difficult

times. Their love, patience, persistent encouragement, and good virtuous understanding

enabled me to complete the research work successfully.

Finally, I express my sincere thanks to Almighty Shri Krishna and his beautiful nature for

allowing me an opportunity to complete this research work.

"Krishnam Vande Jagadgurum"

Ashish A Mulajkar

Reg No: 41800225

vii

# TABLE OF CONTENTS

|                                    | PAGE NOS |

|------------------------------------|----------|

| DECLARATION                        | i        |

| CERTIFICATE                        | ii       |

| ABSTRACT                           | iii      |

| ACKNOWLEDGEMENT                    | vi       |

| TABLE OF CONTENTS                  | viii     |

| LIST OF FIGURES                    | xii      |

| LIST OF TABLES                     | XV       |

| ACRONYMS AND ABBREVIATIONS         | xvii     |

| CHAPTER 1                          |          |

| INTRODUCTION                       |          |

| 1.1 Basics of SoC (System on Chip) | 1        |

| 1.2 NoC Architecture and Function  | 3        |

| 1.2.1 NoC Architecture             | 3        |

| 1.2.2 NoC Function                 | 5        |

| 1.3 Building blocks of NoC         | 8        |

| 1.3.1 Communication Link           | 8        |

| 1.3.2 Routers                      | 8        |

| 1.3.3 Network Interface            | 9        |

| 1.4 NoC Routing Concept            | 10       |

| 1.4.1 Static Routing               | 12       |

| 1.4.2 Dynamic Routing              | 12       |

| 1.5 NoC Switching                  | 13       |

| 1.5.1 Circuit Switching            | 14       |

| 1.5.2 Packet Switching             | 14       |

| 1.6 Topologies used in NoC         | 15       |

| 1.6.1 Mesh Topology                | 15       |

| 1.6.2 Ring Topology                | 16       |

| 1.6.3 Star Topology                                         | 17 |

|-------------------------------------------------------------|----|

| 1.6.4 Butterfly Topology                                    | 18 |

| 1. 7 Metrics for Comparing Various Topologies               | 19 |

| 1.8 Router Architecture design for 3D Torus                 | 20 |

| 1.9 NoC design in Tiers                                     | 21 |

| 1.9.1NoC Tier 1 – first aid                                 | 21 |

| 1.9.2 NoC Tier 2 – More complex issues                      | 21 |

| 1.9.3 NOC Tier 3 – Advanced problems                        | 22 |

| 1.9.4 Build an orderly NoC                                  | 22 |

| 1.10 Advantages of Mesh Topology                            | 22 |

| 1.11 Motivation for Thesis                                  | 23 |

| 1.12 Research Challenges                                    | 24 |

| 1.13 Applications                                           | 26 |

| 1.14 Research Methodology                                   | 27 |

| 1.15 Thesis Outline                                         | 28 |

| CHAPTER 2                                                   |    |

| LITERATURE SURVEY                                           |    |

| 2.1 Emerging Trends in Network on Chip Design               | 31 |

| 2.2 Performance of Efficient Network on Chips               | 35 |

| 2.3 Different Framework for Power Efficient NoC Design      | 42 |

| 2.4 Key Research Problems in NoC Design                     | 51 |

| 2.5 Research Objectives                                     | 52 |

| 2.6 Summary of the Chapter                                  | 52 |

| CHAPTER 3                                                   |    |

| EFFICIENT 3D TORUS ROUTER FOR NETWORK ON                    |    |

| CHIP (NOC) WITH DIFFERENT TOPOLOGIES                        |    |

| 3.1 Introduction                                            | 54 |

| 3.2 Performance Inspection of various Frameworks of NoC for | 55 |

| different topologies                                        |    |

| 3.2.1 NoC (Networks-on-chip)                                | 55  |

|-------------------------------------------------------------|-----|

| 3.2.2 Topologies                                            | 56  |

| 3.3 Various Routing Algorithms                              | 62  |

| 3.4 Flow Control                                            | 66  |

| 3.5 3D Torus Router Module for Structured NoC Design        | 66  |

| 3.5.1 Router Architecture                                   | 68  |

| 3.6 Summary of the Chapter                                  | 70  |

| CHAPTER 4                                                   |     |

| RESULTS AND DISCUSSIONS BASED ON IRR AND UFDQ               |     |

| TECHNIQUES                                                  |     |

| 4.1 Overview                                                | 71  |

| 4.2 Communication in NoCs                                   | 72  |

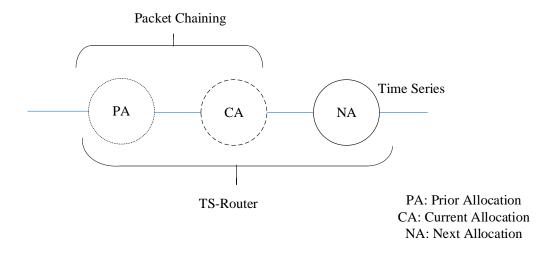

| 4.2.1 Communication Module                                  | 73  |

| 4.3 Virtual Channel NoC Router Architecture                 | 74  |

| 4.3.1 Router Pipeline                                       | 75  |

| 4.3.2 Components of Architecture                            | 76  |

| 4.4.EZ-Pass Architecture                                    | 82  |

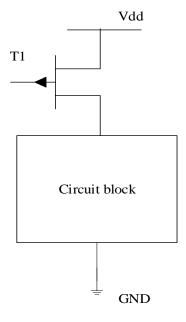

| 4.4.1 Power Gating of NoC Routers                           | 83  |

| 4.4.2 IBRR Arbiter                                          | 86  |

| 4.4.3 Flow Control                                          | 93  |

| 4.4.4 Ultra Fast Dynamic Queue Input Port                   | 95  |

| 4.5 Simulation Results                                      | 99  |

| 4.5.1 Hardware requirements of IRR EZ-Pass router based NoC | 102 |

| 4.5.2 Performance Evaluation of Latency, dropping           | 108 |

| probability and throughput                                  |     |

| 4.6 Summary of the Chapter                                  | 118 |

| CHAPTER 5                                                   |     |

| PERFORMANCE ANALYSIS OF NOC USING BLESS,BBUS,               |     |

| TCMP AND CHIPPER ROUTER CONCEPT                             |     |

| 5.1 Introduction                            | 120 |

|---------------------------------------------|-----|

| 5.2 Basic Model of NoC Router using Mesh    | 121 |

| 5.3 NoC Routing                             | 122 |

| 5.4 NoC Routing Switch arbitration          | 124 |

| 5.5 Buffer less deflection routing          | 124 |

| 5.5.1 The functions of buffers in NoC       | 125 |

| 5.5.2 BLESS Routing Concept                 | 126 |

| 5.5.3 BLESS Livelock freedom                | 127 |

| 5.5.4 Expensive priority depending on age   | 128 |

| 5.6 TCMP Router design                      | 128 |

| 5.7 Concept of Golden Flit                  | 129 |

| 5.8 Concept of BBUS                         | 130 |

| 5.9 Latency and Pattern                     | 131 |

| 5.10 Analysis of CHIPPER Router Performance | 132 |

| 5.11 Experimental Outcomes                  | 134 |

| 5.12 Drawback in BBUS                       | 137 |

| 5.13 Zero Load Latency Review               | 137 |

| 5.14 Concept of Deadlock and Live lock      | 139 |

| 5.15 Summary of the Chapter                 | 140 |

| CHAPTER 6                                   |     |

| CONCLUSION APPLICATIONS AND FUTURE SCOPE    |     |

| 6.1 Conclusion                              | 141 |

| 6.2 Applications of Proposed Architecture   | 144 |

| 6.3 Future Scope                            | 144 |

| 6.4 Benefits to Society                     | 146 |

| PUBLICATION DETAILS                         | 147 |

| REFERENCES                                  | 150 |

# LIST OF FIGURES

|                                                                | PAGE NOS |

|----------------------------------------------------------------|----------|

| Figure 1.1 Basic SoC Architecture                              | 2        |

| Figure 1.2 Basic NoC Architecture                              | 4        |

| Figure 1.3 NoC Layer Structure                                 | 5        |

| Figure 1.4 Switching Strategies                                | 14       |

| Figure 1.5 Model of Mesh Topology in NoC                       | 16       |

| Figure 1.6 Ring Topology                                       | 17       |

| Figure 1.7 Star Topology                                       | 17       |

| Figure 1.8 Butterfly Topology in NoC                           | 18       |

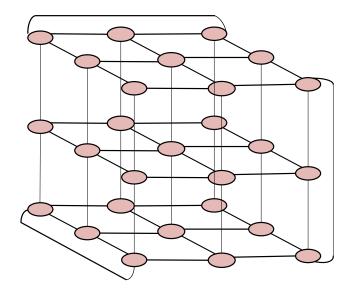

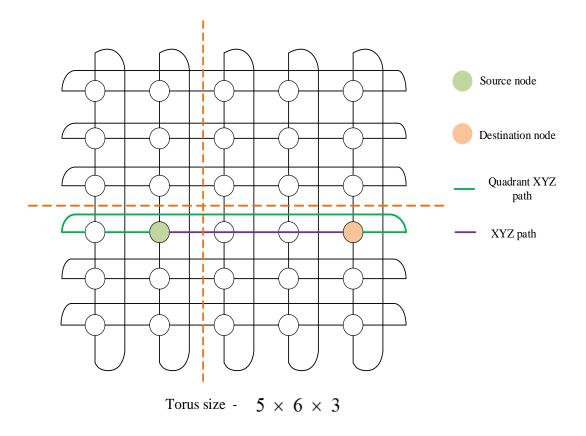

| Figure 1.9 3D Torus Architecture                               | 20       |

| Figure 1.10 Node arrangements in Mesh and Full Mesh Topologies | 21       |

| Figure 1.11 Proposed Methodology                               | 28       |

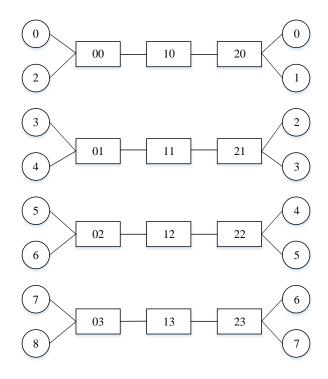

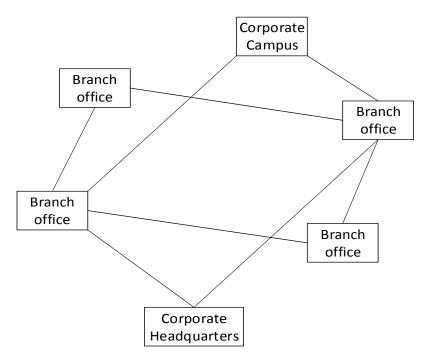

| Figure 3.1 Structure of NoC                                    | 56       |

| Figure 3.2 2D Mesh Topology in Network on Chip                 | 57       |

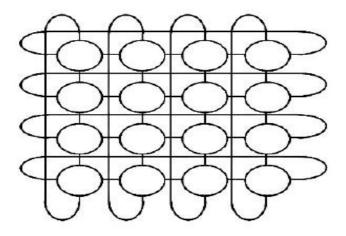

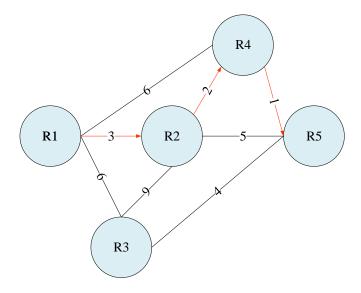

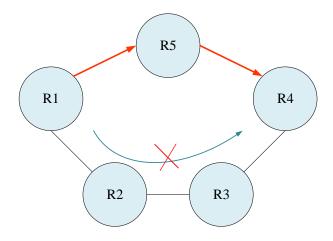

| Figure 3.3 Torus Topology                                      | 58       |

| Figure 3.4 Ring Circulant Topology                             | 59       |

| Figure 3.5 Star Topology                                       | 61       |

| Figure 3.6 Butterfly Network                                   | 62       |

| Figure 3.7 Routing Algorithm Classification                    | 63       |

| Figure 3.8 Adaptive Routing Algorithm                          | 64       |

| Figure 3.9 Non Adaptive Routing Algorithm                      | 65       |

| Figure 3.10 Switch Allocation Strategy                         | 67       |

| Figure 3.11 Quadrant based 3D Torus Topology                   | 68       |

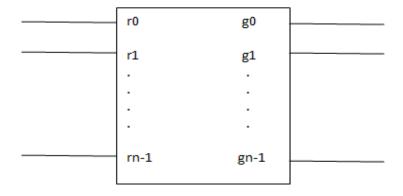

| Figure 4.1 Point to Point Communication in NoC                 | 73       |

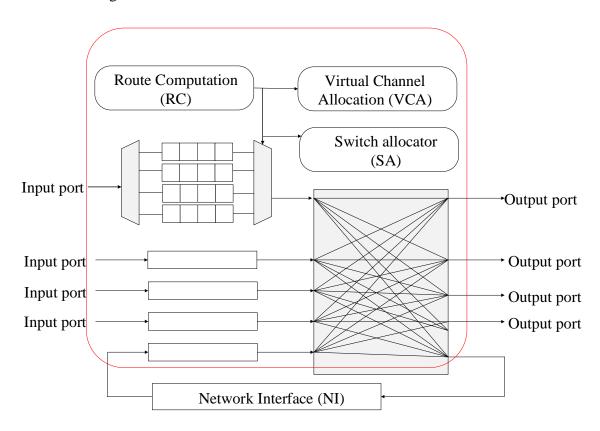

| Figure 4.2 VC NoC Router Architecture                          | 74       |

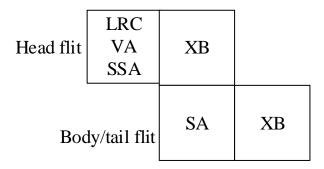

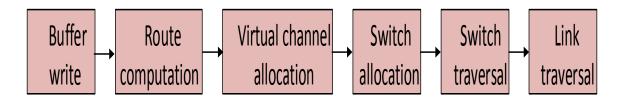

| Figure 4.3 Router Pipeline                                     | 75       |

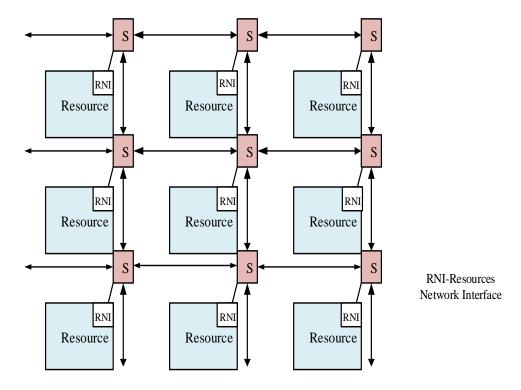

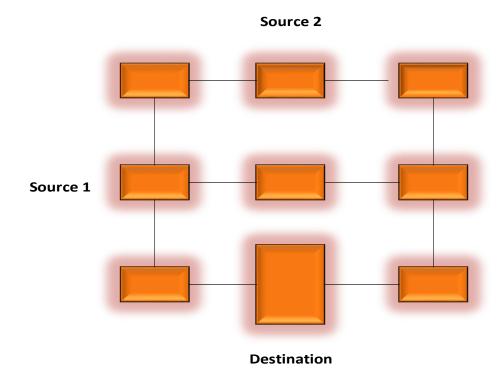

| Figure 4.4 3X3 network topology with 9 resources and switches  | 77       |

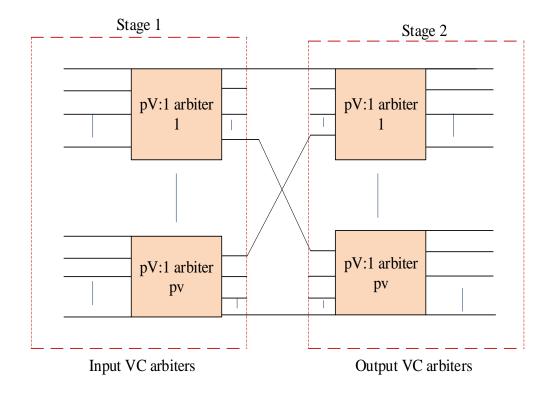

| Figure 4.5 Virtual Channel Allocation                          | 80       |

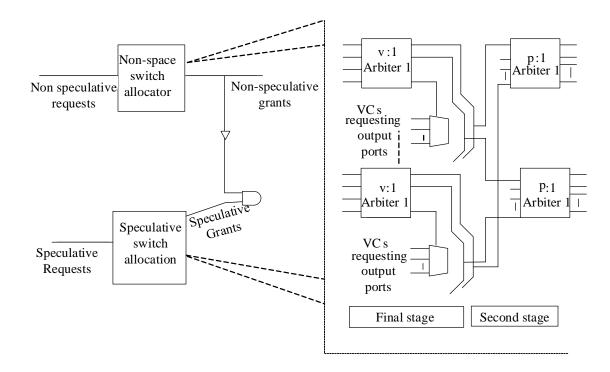

| Figure 4.6 Switch Channel Allocation                                 | 81  |

|----------------------------------------------------------------------|-----|

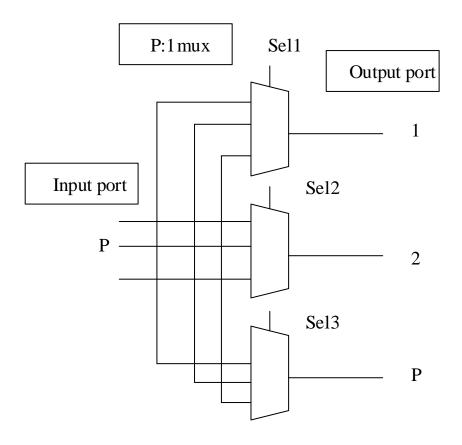

| Figure 4.7 Crossbar Structure                                        | 82  |

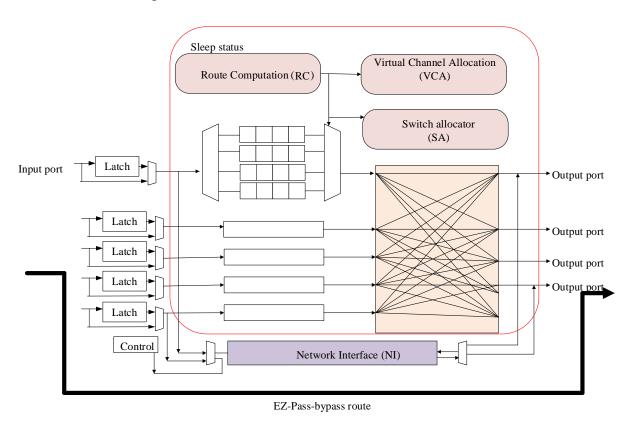

| Figure 4.8 EZ-Pass Router Architecture                               | 83  |

| Figure 4.9 Power Gating Technique                                    | 84  |

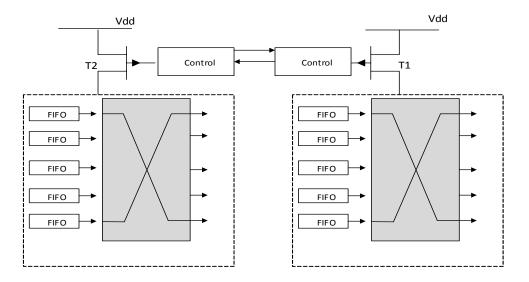

| Figure 4.10 Usage of Power Gating techniques in Noc Routers          | 84  |

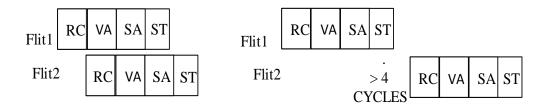

| Figure 4.11 Usage of router pipeline in traffic mode                 | 86  |

| Figure 4.12 Priority arbiter                                         |     |

| (a) n input Fixed priority arbiter                                   | 88  |

| (b) Block diagram of Arbiter                                         | 88  |

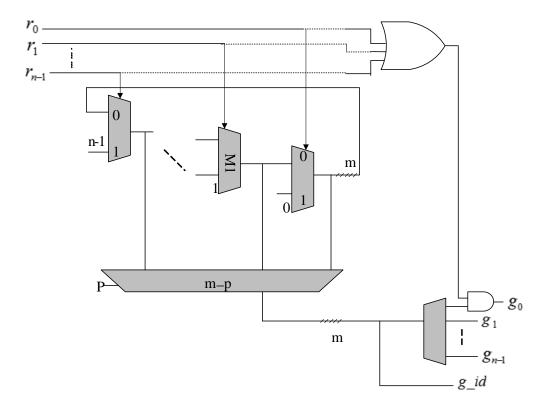

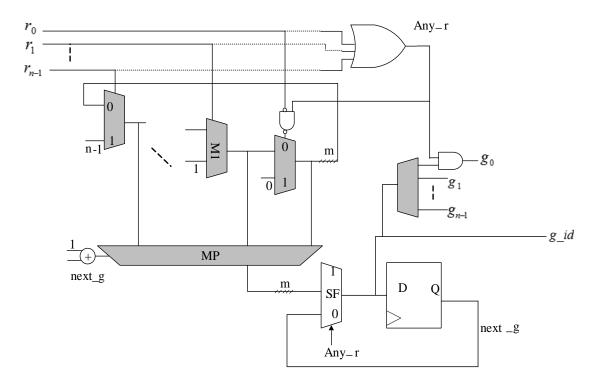

| Figure 4.13 n input varying priority arbiter                         | 90  |

| Figure 4.14 Input request framework for strong fairness RoR arbiters | 91  |

| Figure 4.15 Input request framework for weak fairness RoR arbiters   | 92  |

| Figure 4.16 IRR n-input arbiter                                      | 92  |

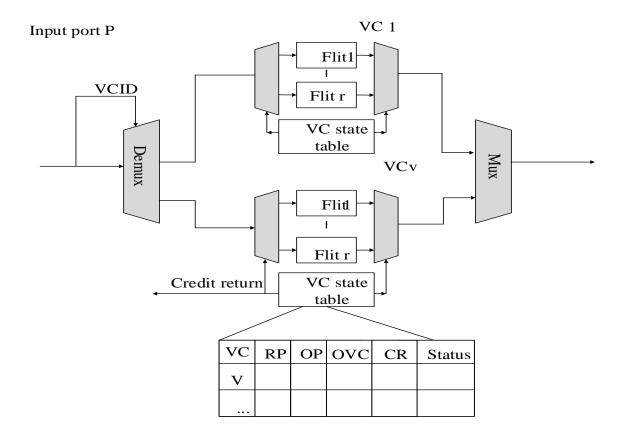

| Figure 4.17 Conventional Virtual Channel                             | 94  |

| Figure 4.18 VC State Table                                           | 95  |

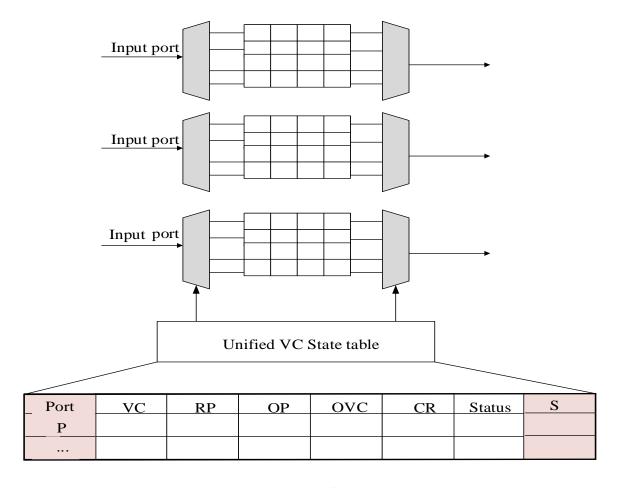

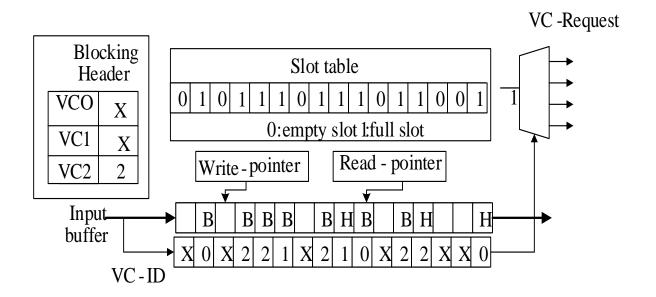

| Figure 4.19 Ultra Fast Dynamic Queue input port in EZ-Pass router    | 96  |

| architecture                                                         |     |

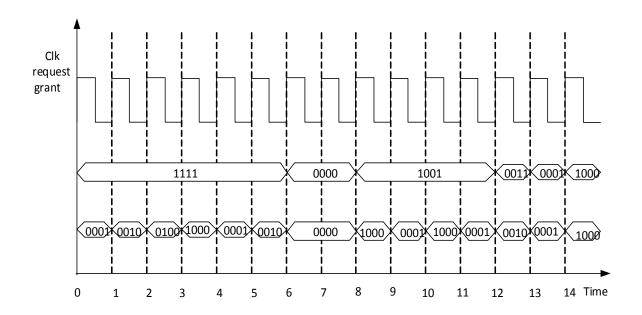

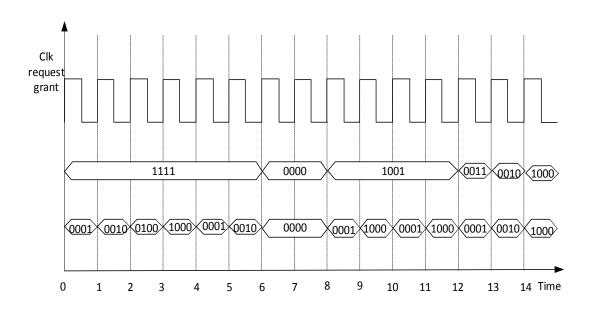

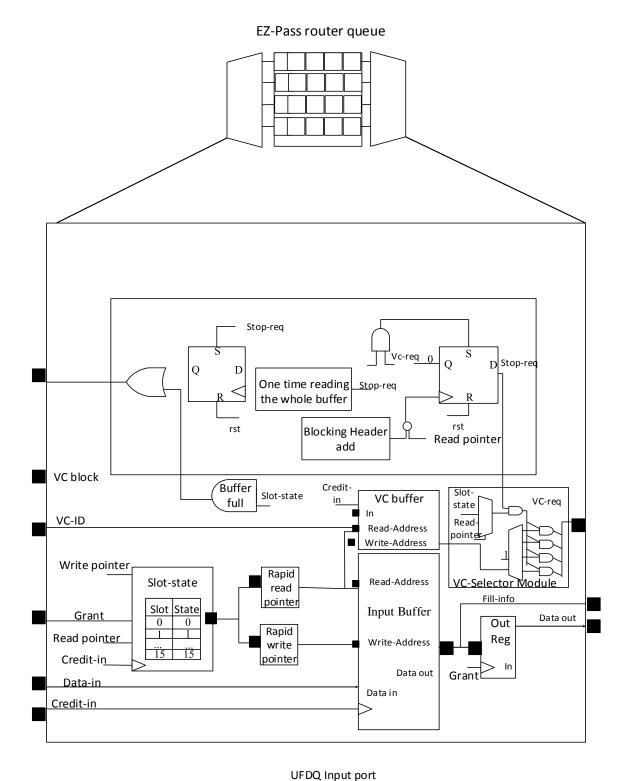

| Figure 4.20 UFDQ Input port operation                                | 97  |

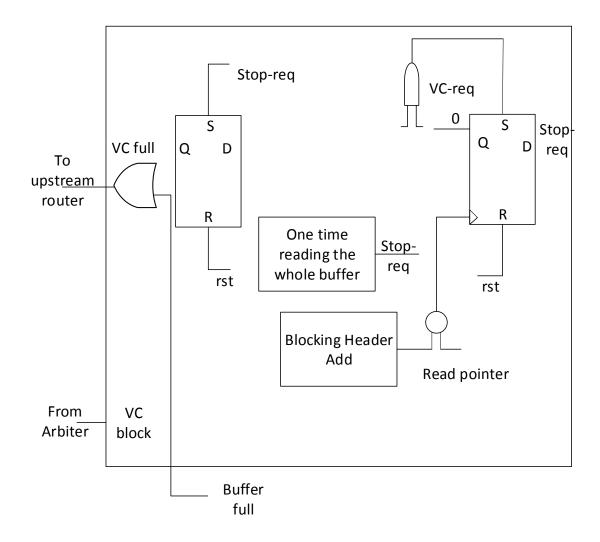

| Figure 4.21 Blocking Circuit associated with VC                      | 98  |

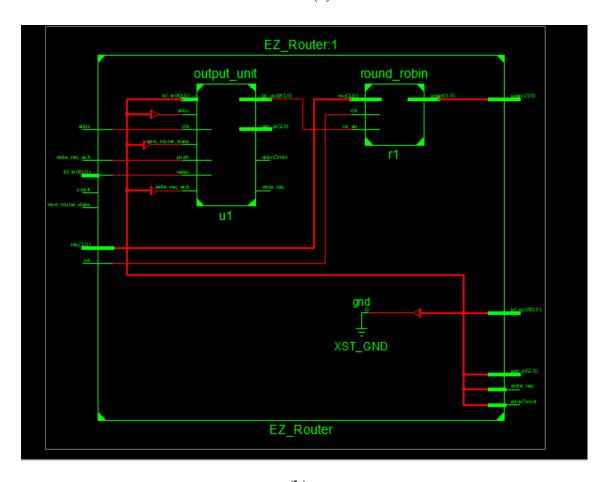

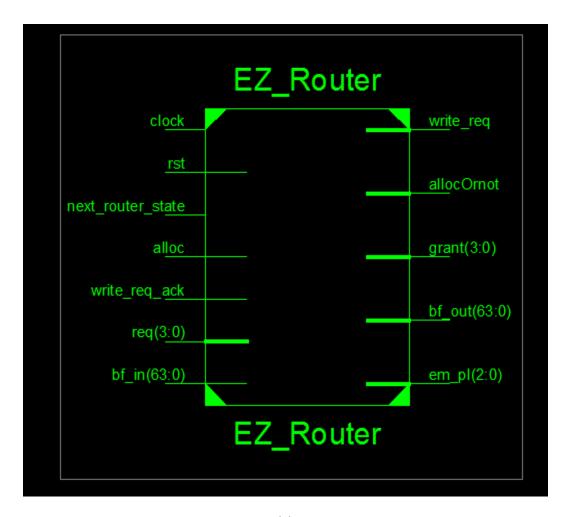

| Figure 4.22 RTL schematic of                                         |     |

| (a) VC Router                                                        | 101 |

| (b) IRR EZ-Pass switch (single node)                                 | 101 |

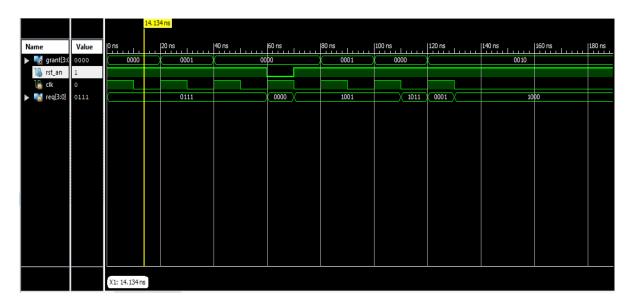

| Figure 4.23 Simulation result of IRR Arbiter                         | 102 |

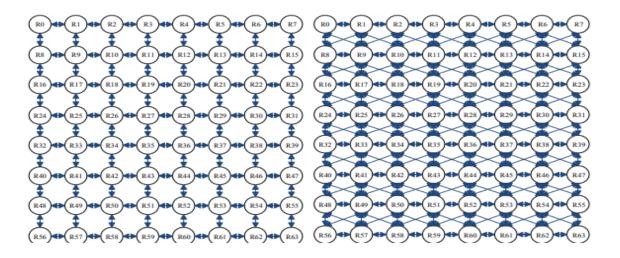

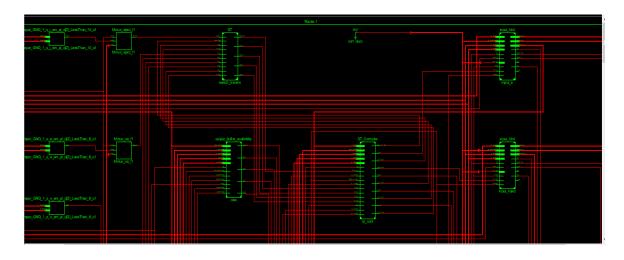

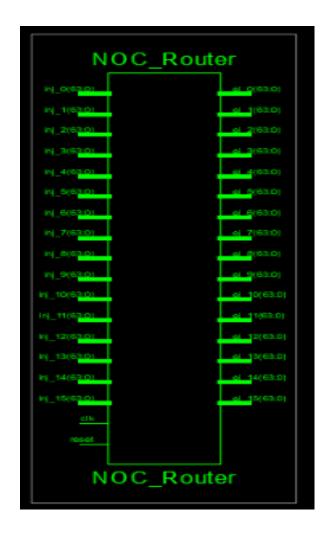

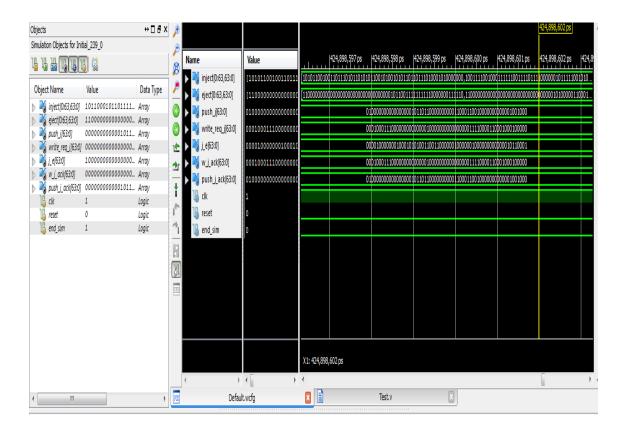

| Figure 4.24 RTL schematic of the top view of 4x4 NOC structure       | 104 |

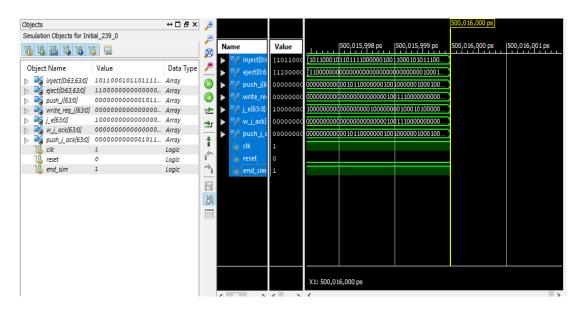

| Figure 4.25 Simulation results of 4x4 Mesh Topology                  | 105 |

| Figure 4.26 Power Analysis                                           | 107 |

| Figure 4.27 Throughput analysis                                      |     |

| (a) Sporadic Traffic                                                 | 110 |

| (b) Low traffic                                                      | 111 |

| Figure 4.28 Analysis for 100 % traffic load             |     |

|---------------------------------------------------------|-----|

| (a) Throughput                                          | 112 |

| (b) Dropping probability                                | 113 |

| Figure 4.29 Latency analysis                            |     |

| (a) Sporadic traffic                                    | 114 |

| (b) low traffic                                         | 115 |

| Figure 4.30 EZ-Pass router                              |     |

| (a) RTL Schematic                                       | 117 |

| (b) Implementation Simulation result for EZ-Pass router | 118 |

| Figure 5.1 NoC Router Pipeline                          | 121 |

| Figure 5.2 NoC basic Model using Mesh Topology          | 121 |

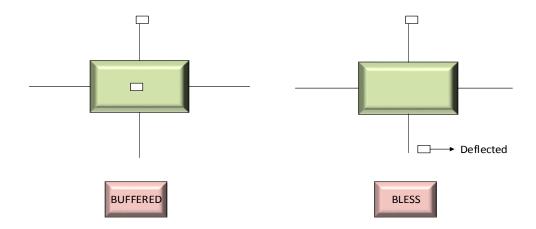

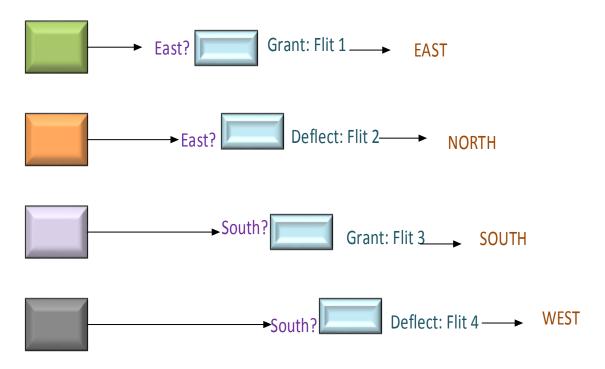

| Figure 5.3 Buffer less deflection router                | 125 |

| Figure 5.4 BLESS routing concept                        | 127 |

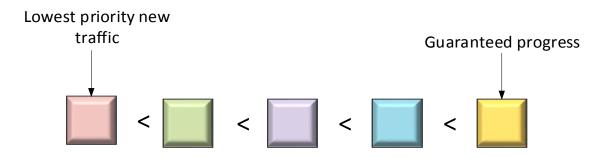

| Figure 5.5 Ordering of flits                            | 127 |

| Figure 5.6 Age based flits priority                     | 128 |

| Figure 5.7 Architecture of TCMP                         | 129 |

| Figure 5.8 Golden Flit Technique                        | 130 |

| Figure 5.9 Analysis of Normalized Router Area           | 133 |

| Figure 5.10 Analysis of Normalized Critical Path        | 134 |

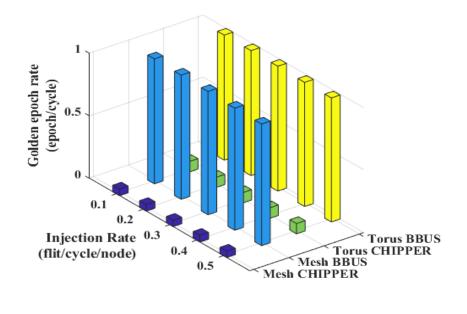

| Figure 5.11 Golden epoch Rate of Mesh/Torus Topology    | 135 |

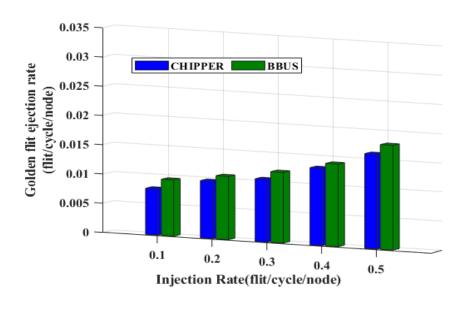

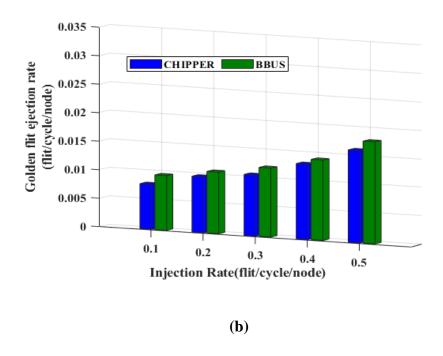

| Figure 5.12 Injection Rate                              |     |

| (a) Torus Topology                                      | 135 |

| (b) Mesh Topology                                       | 136 |

| Figure 5.13 Deadlock Concept                            | 139 |

# LIST OF TABLES

|                                                                | PAGE NOS |

|----------------------------------------------------------------|----------|

| Table 1.1 Hop Counts-Mesh and Full Mesh                        | 23       |

| Table 2.1 The comparison of Related works based on Emerging    | 33       |

| Trends in NoC Design                                           |          |

| Table 2.2 The comparison of Related works based on Performance | 38       |

| of Efficient NoC                                               |          |

| Table 2.3 The comparison of Related works based on Different   | 45       |

| Framework for Power Efficient NoC design                       |          |

| Table 2.4 Analysis of Power Reduction Techniques               | 51       |

| Table 3.1 Design parameters of 3D Torus Router                 | 61       |

| Table 4.1 Simulation Settings                                  | 100      |

| Table 4.2 Comparative analysis of IRR and RoR                  | 103      |

| Table 4.3 Device utilization summary of the IRR EZ-Pass switch | 106      |

| Table 4.4 Power Analysis by X-Power Analyzer for VC Router     | 107      |

| Table 4.5 Power Analysis by X-Power Analyzer for EZ-Pass       | 108      |

| Router                                                         |          |

| Table 4.6 Power Analysis of EZ-Pass versus VC Router           | 108      |

| Table 4.7 Throughput Analysis for Sporadic Traffic             | 109      |

| Table 4.8 Throughput Analysis for Low Traffic                  | 110      |

| Table 4.9 Dropping Probability for 100% Traffic Load           | 113      |

| Table 4.10 Latency for Sporadic Traffic                        | 115      |

| Table 4.11 Latency for Low Traffic                             | 116      |

| Table 4.12 Delay Analysis                                      | 116      |

| Table 4.13 Frequency Analysis                                  | 117      |

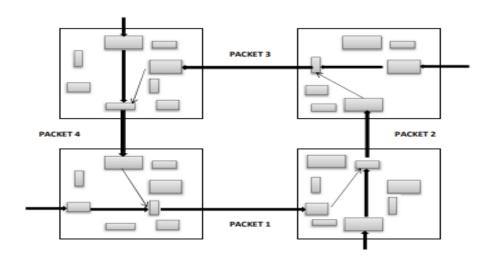

| Table 5.1 Mesh NoC Packet flow structure (4x4)                 | 122      |

| Table 5.2 Square Mesh topology 25 core machines (5x5)          | 123      |

| Table 5.3 Parameters of Golden Epoch                           | 126      |

| Table 5.4 Traffic Patterns and Packet Latency                  | 131      |

| Table | 5.5 Mesh NoC Topology with XY Routing (8x8)     | 132 |

|-------|-------------------------------------------------|-----|

| Table | 5.6 ZLL Calculation for Single Write Operations | 138 |

| Table | 5.7 ZLL Calculation for Single Read Operations  | 139 |

# ACRONYMS AND ABBREVIATIONS

ALO Ant Lion Optimized

ANN Artificial Neural Network

ASIC Application Specific Integrated Circuit

BiNoC Bimodal Network on Chip design

BW Buffer Writes

BPG Beneficial Power Gating

CBCF Cycles between consecutive flits

CE Combinational Elements

CUDA Compute Unified Device Architecture

CMP Chip Multiprocessors

CR Credits

CE Combinational Elements

DAMQ Dynamically Allocated Multi-Queue

DEMUX De-Multiplexer

DVFS Dynamic Voltage and Frequency Scaling

DT Detection Time

DSM Deep Submicron

DOR Dimension Order Routing

EB Elastic Buffer

EMI Electromagnetic Interference

FIFO First Input First Output

FDTR Fault-tolerant Defection Routing

FPGA Field Programmable Gate Array

GPU Graphics Processing Unit

GPS Global Positioning System

GLONASS Global Navigation Satellite System

HASE Hierarchical Architectural Simulation Environment

IP Intellectual Properties

IC Integrated circuit

ISI Inter Symbol Interference

IRR Index based Round Robin arbiter

LAN Local Area Network

LRC Look ahead Routing Computation

LUT Look up Table

MDM Mode Division Multiplexing

MFC Multi Function Channel

MPSoC Multiprocessor System on Chip

MUX Multiplexer

NoC Network on Chip

NoRD Node-router decoupling

NI Network Interface

NDS NoC Design Search

NAS Neural Architecture Search

NT Network Topology

OP Output port

OVC Output VC

PE Processing Elements

PG Power Gating

QoS Quality of Service

RTL Register Transfer Level

RC Routing Computation

RL Reinforcement Learning

RoR Round Robin

RP Read Pointer

SA Switch Allocation

SSA Speculative Switch Allocation

SoC System on Chip

ST Switch Traversal

STT\_MRAM Spin Transfer Torque Magneto-Resistive Random Access

Memory

SSA Speculative Switch Allocation

TSV Through-Silicon vias

UDSM Ultra Deep Sub Micron

UFDQ Ultra-fast Dynamic Queues

UBPG Unbeneficial Power Gating

VC-ID VC Identifier

VCT Virtual Cut Through

VC Virtual Channel

WL Wake up Latency

WiNoC Wireless Network on Chip

# **CHAPTER 1**

#### INTRODUCTION

NoC is a networking technique implemented on an IC which connects each parameter of SoC. It enhances networking techniques in all respects as compared to the conventional bus as well as crossbar systems. NoC architecture is available in a variety of topologies in which research is still in progress. NoC enhances system scalability by reducing power consumption in terms of Static and Dynamic power. Modern networking components use GPU (Graphics Processing Unit) and allied parts. NoC is widely used in Artificial Intelligence enhancement, gaming zones, and also in Visual Graphics. NoC has substantial growth estimates in the future as multi-core computer process becomes the most popular nowadays. This chapter provides fundamental information regarding the NoC architectural representation and routing technologies for the NoC.

# 1.1 Basics of SOC (System on Chip)

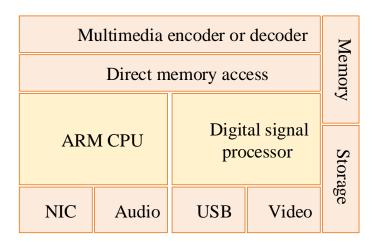

SoC is relatively a novel design model that integrates a CPU or several memories, processors, and a peripheral set linked through buses on a single chip. The trend towards multi-core processing processors is now well established based on Moore's law. Because computing power is developed based on dynamic power dissipation calculation exponentially most designers prefer energy-efficient CPUs paired with hardware acceleration to provide the best combination of performance and power consumption [1]. The SoC essentially is an IC (Integrated Circuit) which merges the entire computing modules in a unique platform. I/O ports, CPU, and internal memories are some of the components that an SoC attempts to combine inside it. SoC provides multiple operations like Artificial Intelligence, Neural Networks as well as Mobile Computing [2]. SoC systems are developed by aiming for power saving, and low chip size to reduce the overall cost of the system. SoC meets all objectives by embedding multiple chip modules

onto a single chip with an aim to reduce power and design area [3]. SoC chips help to construct compact devices which can be comfortably carried with us anytime, anywhere without sacrificing the capacity and performance of the gadgets. As a result, they are commonly utilized in systems related to IoT, Embedded Designs, Mobile Phones, Automobiles, and many more areas. Whereas just a few decades ago, an SoC was nothing more than a term, it has now become an essential component of modern technology and the electronics field. Figure 1.1 shows the basic SoC Architecture.

Figure 1.1: Basic SoC Architecture

The practical applications of SoCs are essentially endless and priceless. They are found in almost all portable devices including smart phones, optical lenses, i-pods as well as wireless technology. The Cell Phone is the best paradigm showing how SoC operates. More than making or receiving calls, a person also plays games, browses the internet, makes voice and video calls, makes digital payments, and so on mobile phones. These activities are possible because of web connectivity, Graphics Interface Cards, GPS, and GLONASS systems. SoC technology allows users to reduce the size of the system, and make it more compact which can be easy handled and easier to carry. SoC allows users to reduce battery usage, improve browsing time as well as surge the performance of a system. But due to certain limitations in SoC design, the technology is shifted towards implementing NoC design.

#### 1.2 NoC Architecture and Function

A major issue in NoC design is router architecture, which impacts on price and performance of the system. The thesis highlights on design and implementation of a novel router for better performance of the system. Despite the increased number of processing components, SoC designers are facing some challenges of scalability and connecting on-chip components. Traditional systems including buses and buffers are incapable of meeting the rising scalability, performance, timing closure, power, and other features [4].

#### 1.2.1 NoC Architecture:

An organized and scalable connectivity model for NoC is developed for minimizing complicated on-chip design problems for addressing the signal integrity and design productivity concerns of designing a next-generation system [5]. An application may be conceived of as a collection of computer units that need to interact with one another via a collection of communication blocks. To differentiate the impact of these two critical elements on compute time, performance is influenced by delay in gate signals. Computing time is affected by the delay in gate signals while Communication time is affected by wire delay. Ad-hoc communication block can be conducted when the number of processing units is modest. However, as transistor sizes have shrunk in recent years, gate delay has decreased in comparison to wire delay. As a result, in order to put more sophisticated applications on a single chip, we need an organized as well as scalable, and on-chip efficient model.

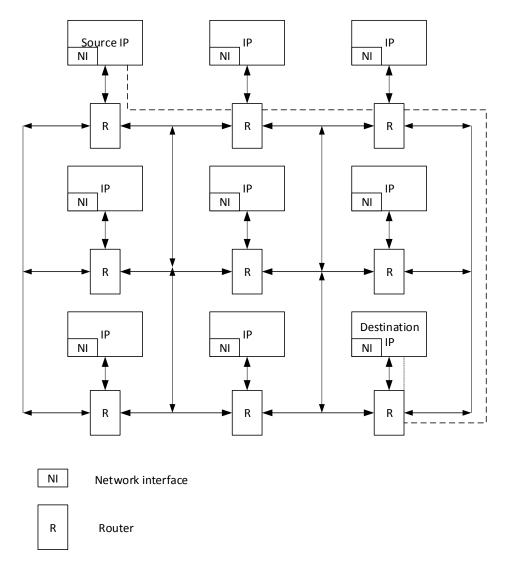

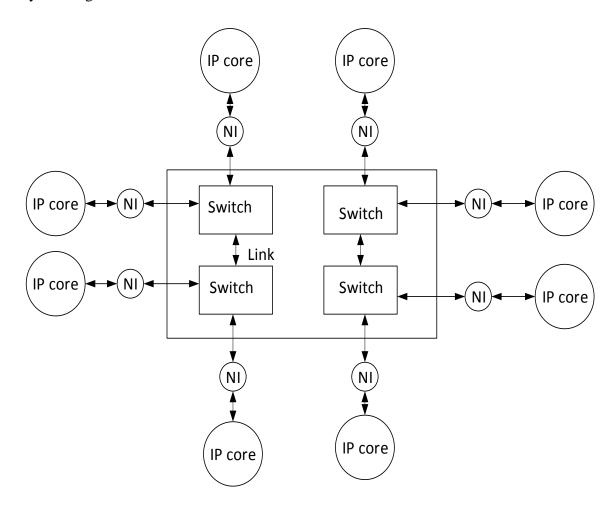

Figure 1.2: Basic NoC Architecture

As a result, the on-chip communications architecture design becomes dominant as design concepts are shifted from computing basics to advanced communication techniques. In the face of advancement in communication, the phrase "network on chip" refers to an architecture that maintains a conveniently designable solution. We will go over some key concepts for creating an NoC communication system in this part. Furthermore, the function of NoC may be divided into several levels, which will be brought in the right order. Figure 1.2 indicates the basic NoC Architecture which contains numerous lengths of cables as well as routers. The wire and router type NoC system is designed similarly to the city street grid, while the user is set on wire-separated blocks. The client's logic

processor core data packets are converted to fixed packets by NI modules. Data packet flit is made up of tail flit, header flits as well as in between body packets [6]. This flit array will be sent in the direction hop by hop via adjacent routers.

#### 1.2.2 NoC Function:

The NoC function is divided into various layers: network, transport, application, physical and data connection. To provide layer functions, an NoC router needs to have both, software and hardware implementations. Different layers in NoC structure are shown in Figure 1.3

Figure 1.3: NoC Layer Structure

#### Application layer

The target application is separated into communication activities and computer collection at the application layer allowing performance characteristics such as energy and speed to be regulated. The location of cores on the NoC must be altered in order to minimize overall communication or energy consumption while also taking into consideration the constrain of any single link. Communication scheduling and task mapping are examples of NP-hard restricted quadratic assignment problems. A set of concurrent tasks is described by a given target application with an NoC architecture. There are some fundamental questions to be answered which are (1) how the complex network condition effect is accounted, for which changes at text execution dynamically; and (2) how to put chosen core set on the network components topologically in order to maximize the metrics of interest application. Scheduling and mapping should be reviewed in conjunction with a design range of elements to obtain the best balance of power and performance.

#### Transport Layer

In order to minimize buffer overflow and traffic congestion, various organization strategies are supposed to be used to show packet transmission in NoC. Congestion and Flow control concerns are addressed by the transport layer. NoC key performance indicators are high throughput rate and low packet delivery delay, both of which be severely damaged by system congestion induced by source arguments. As a result contention resolution is critical for avoiding network congestion. One of the most important concerns for contention resolution is to improve the available network resources efficiently to achieve higher communication performance under the assumption of a dead-lock and live lock-free routing algorithm.

#### Network layer

Network topology is also known as interconnected design. The Network layer becomes important because it influences how network resources are connected and therefore it is referred to static channel configuration node for the associated network. Combining and splitting various communication architecture types in a mixed fashion that provides more customizability and connectivity at the complexity price and area forms irregular topologies. Furthermore, optimizing a topology that affects router connections and the distance between cores is a complex issue. Moreover, the balance between customization and generality is crucial for performance and scalability. The architecting cost along with manufacturing semiconductor cost climbs due to high complexity. A homogeneous NoC employed identical cores and routers, but a heterogeneous design chooses IP library cores and can adjust the communication architecture along with application necessities. Most cutting-edge chip designs employ Mesh and Torus topology for two-dimensional systems as it has better performance with a high degree of scalability, which may not provide the greatest performance for a particular application.

Also, the network layer must dispense with data routing among processing components. The first packetizing algorithm deals with breaking down a single message into small packets at the source node and assembling them at a destination node. Transmission of packets can then be carried out using a number of routing techniques based on various network topologies. A routing method verifies how a packet will be routed via the source node to the destination node. The router's main responsibilities include identifying flit routes and solving disputes among packets when a similar path is required for boosting on-chip communication speed.

A router's traditional architecture comprises an arbitration controller and circuit-switched fabrics. As long as there is no dispute between these pathways, the crossroad switch can be used to create more than one path in each arbitration decision. VC flow control-based router design is a known approach from an area of multiprocessor networks for most existing switch designs allowing increased elasticity as well as channel usage with reduced space of buffer.

#### Physical and Data link layer

The prior purpose of data link layer protocols reducing link dependability to a lower necessary level, assuming that the physical layer is insufficiently dependable on its own. The physical layer's concentration is on signal receivers and drivers and design solutions for pipelining and resorting signals on a wire. Furthermore, when technology evolved to UDSM (Ultra Deep Sub-micron) lower voltage fluctuations and diminishing feature size translates to lower noise margins, on-chip interconnects, lower noise resistance making, and increasing non-determinism likelihood in data transmission across wires. Electric noise caused by radiation-induced charge injection, electromagnetic interference (EMI), and crosstalk would almost certainly result in timing and data mistakes making dependable on-chip connectivity difficult to accomplish. These layers are primarily concerned with error control systems and the use of physical connections to improve dependability. To begin, a plausible fault model must be created. Then a high bandwidth, low-area, low-power, low-latency error control method should be created. Packet-based transmission of data is an effective technique for handling data faults in NoC architecture

since the error effect is presented through packet boundaries which are retrieved flit by flit.

# 1.3 Building blocks of NoC

A network-on-chip is made up of three primary components [7].

- The most crucial one is the Communication Links that physically link nodes and allow making communication.

- The router is the second block that is responsible for implementing the communication protocol.

- NA (Network Adapter) and NI (Network Interface) is the last construction piece.

This block establishes a logical link between networks and IP cores.

#### 1.3.1 Communication Link:

A communication link is a series of cables that links two routers in a network. A couple of logical channels are required to form links and each is made up of a wire set. The defining of the integration protocol among source as well as target nodes is included in the implementation of connection [8]. It can be analyzed using specified wires during communication and different methods like First Input First Output (FIFO).

#### 1.3.2 Routers:

An NoC router consists of many input and output ports, a switching matrix that connects IOs as well as a local port that connects to the core IP. The router includes a logic block that executes flow control rules and determines the overall strategy for transferring data through the NoC.

The following are the route's key design elements

- Flow Control Defines packet flow in an NoC, both globally and locally. The control logic ensures communication performance and quality of service. Control can be either-

- Centralized or diffused Routing choices are made globally and implemented to all nodes in centralized control, using a technique that ensures no traffic congestion. This necessitates that all nodes have the same sense of time. Each router makes choices locally in a distributed control system.

- Routing Algorithm Logic that chooses one of the output ports to route a packet received at the input port: Deterministic Routing and Adaptive Routing are two types of routing available. In Deterministic Routing, a similar path is considered among two particular nodes to take a packet. Alternative pathways between two nodes may be employed in adaptive routing when a local link or original path is crowded.

- Arbitration Logic The Routing Algorithm selects the output port to the packet router's arbitration logic and picks one input port when many flits are present.

- Buffering This policy retains information in the router if there is network congestion and packets are not transmitted quickly.

- Switching Switching governs how information is shared from source to destination. The payload is not transmitted until the entire route is reserved. This can result in increased delay, but once the path is determined, this strategy provides several assured throughputs for instance. Header creates the link between routers and sends all flits of the packet in a packet-based switching strategy.

#### 1.3.3 Network Interference:

NI block provides a logic link between the network and the IP cores as every IP uses a different network interface protocol [9]. This block is crucial since it provides for the

separation of communication and computation. This enables independent reuse of both communication infrastructure and core.

The adaptor is separated into two parts:

- The front end is in charge of the core plea, and should be not able to detect NoC.

It is commonly implemented at VSI Alliance (VCI) sockets, OCPIP (OCP),

Philips Semiconductors (DTL), AXI 2011, and so on.

- The Network protocol is handled by a back end (disassembles and assembles the

packet. helps the router in storage, reorders buffers, implements synchronization

protocols, etc.).

## 1.4 NoC Routing Concept

NoC is a network-based communication system on a semiconductor IC that is usually used to communicate amongst SoC modules. A system on a chip (SoC) is a chip that incorporates computer components such as a Central Processing Unit (CPU), graphics, and memory interfaces. Pre-designed intellectual property (IP) cores/blocks are becoming increasingly significant in SoC architectures. As semiconductor chip dimensions drop and more IP cores are added to them, many SoC devices have become too complicated to use a typical data bus or crossbar connectivity architecture. Physical resources holding data on chips and service quality begin to deteriorate. NoC technology offers significant advantages over traditional data bus and crossbar communication designs [10]. The purpose of NoC scheme is to organize communication amongst operational modules that are placed on the same chip. The technique boosts the scalability and energy efficiency of complicated SoCs.

Some of the benefits of NoC versus SoC [11] are as follows-

- 1. NoC provides structured architecture, reducing chip design complexity and expense.

- 2. NoC enables the re-use of components, architectures, design processes, and tools.

- 3. Offers an economical and high-performance interconnection

- 4. Increases the scalability of the communication architecture

- 5. Establishes a link between processing blocks by routing data packets, allowing for flexible and easy change adaptation.

- 6. Reduces cable routing congestion and eliminates timing closure difficulties.

- 7. Reduces the complexity of switching and routing tasks in order to reach greater operating frequencies.

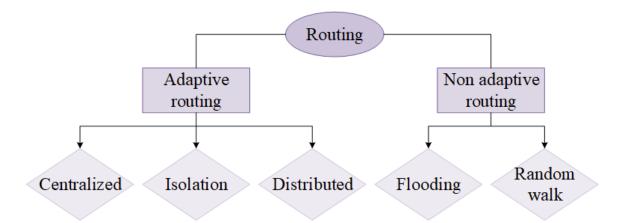

A mechanism is created considering the on-chip IP ports for ensuring proper communication. Proper Algorithm only allows proper communication via source to destination. Previously noted routing algorithms are free of starvations and deadlocks are crucial in chip design. The routing algorithm may be chosen built on a variety of interconnected properties, which results in tradeoffs between associated parameters like energy consumption, packet delay, and footprint which define routing method standards. By keeping the routing simple, power for routing may be less hence the power consumption is decreased. Furthermore, routing tables should be reduced to improve speed. This will aid in assuring reduced latency, increased resilience, a small footprint, and efficient network use. Generally NoC routing methods are divided depending on characteristics like distance, decision state as well as routing paths. NoC algorithms are separated into dynamic and static routing algorithms. Determination of routing choices is

done by using distributed, minimum, source, or non-minimal routing algorithms. The static and dynamic routing algorithms are discussed in this section.

#### 1.4.1 Static Routing:

The simplest and most often used routing technique in NoCs is Static Routing, also called-deterministic or oblivious routing. It is used for data transport between a given destination and source which uses fixed (predefined) pathways. Furthermore, the present status of the network will not be considered in Static Routing. As a result, if a routing decision is being made, the load on connections and routers is ignored. Static routing needs relatively minimal router logic, making it simple to build. Furthermore, packets can be planned to be shared across numerous pathways between the source and destination. In addition in a case where only one path is used static routing can guarantee in-order packet delivery [12]. In this way, reordering and identification of packets at the destination do not require adding bits at the NI. Static Routing techniques include random walk routing, directed flood, probabilistic flood, Dimension Order Routing (DOR) destination tag, turn model, XY, surrounding XY, and pseudo-adaptive XY. Deterministic distributive routing is a kind of XY routing. The coordination of destination address in this approach is employed to send a packet through a network. The path is then followed along the Y coordinate vertically until it reaches the final destination. XY Routing is a common approach to Mesh as well as Torus topologies since it reduces deadlocks. However, because of the load that is regularly produced in the center of a network, the accompanying traffic may be irregular and the XY algorithm is incapable of eliminating crowded and congested lines.

#### 1.4.2 Dynamic Routing:

Dynamic and Adaptive Routing depends on the current underlying state of the network. Aspects such as system availability and connection load status are considered while deciding routing decisions in this routing method. As a result, the path between the destination and source may change as application needs and traffic circumstances change [13]. Dynamic routing allows traffic to be distributed across several routers more

efficiently than static routing. Furthermore, it can employ different channels in the network congestion case in particular NoC lines. In this sense, its topology may be able to support more traffic and network capacity utilization can be minimized. The ability of adaptive routing to employ global information about current traffic status in optimum path selection is one of its distinctive features. The flexibility of this strategy, however, comes as the extra resource requires regular upgrading of network conditions for assuring comparable variable shifts among routing patterns. It typically increases the router's complexity. Furthermore, adaptive routing performance is limited by the amount of global knowledge that can be sent to each router as well as interference. As previously stated, a static routing system is normally utilized in situations where traffic requirements are stable and predictable, whereas dynamic routing is frequently employed in unpredictable and irregular traffic conditions. Slack time aware, turn around-turns back, congestion look-ahead, odd-even, entirely adaptive, turn back when possible, minimal adaptive, and deflection are examples of adaptive navigation algorithms (hot potato). Adaptive and Deterministic routing strategies will be utilized in NoC to communicate between the destination and source. The odd-even routing approach is a non-deadlocking adaptive routing paradigm. East-to-North and East-to-South turns are thus prevented in even columns. As a result, the odd-even routing strategy helps to eliminate potential live locks in the systems. The deflection routing method is economical since no buffers are employed. As a result, arriving packets are not queued by the routers and are routed simultaneously to their destinations using the routing tables. When a busy router gets other packets, misrouting might occur. In such a server environment, distort packets in a network might generate more misrouting, causing every flit to bounce around the network like a hot potato technique. By allowing sufficient gaps between packets, misrouting may be significantly reduced.

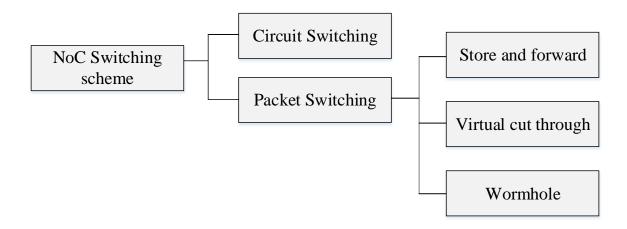

# 1.5 NoC Switching

NoC switching scheme specifies data transmission granularity and identifies the switching strategy used for data control in routers. The primary switching mechanisms in

NoCs are Packet Switching and Circuit Switching [14]. Figure 1.4 denotes the classification of various Switching Schemes in NoC.

Figure 1.4: Switching Strategies

#### 1.5.1 Circuit Switching:

Prior to the transmission of data, this switching is dependent on reserved physical channel development between the source & destination which consists of routers and connections. Although circuit switching provides low latency transmission by utilizing the whole connection capacity it wastes existing lines when no data is transmitted posing scalability issues. Virtual-circuit switching can be used to increase network scalability. It allows several virtual links to be multiplexed onto a physical link. Allotted buffers determine the number of essential connections that physical links will sustain.

#### 1.5.2 Packet Switching:

Another prominent switching mechanism is packet switching. In contrast to circuit switching, where the way is established before data transfer there is no requirement to build before packet transfer a route (no link reservation) before packet switching. The transmit packets in this context take distinct pathways from transmitter to receiver. As an outcome, the packets will incur varying delays [15]. Furthermore, unlike circuit switching, which frequently has a certain standby time and minimum latency, this switching has a

null start-up time and fluctuating delay owing to the congestion. Furthermore, due to the conflict, ensuring QoS (Quality of Service) in packet switching is more exacting as compared to Circuit-Based switching. VCT (Virtual Cut Through), wormhole, store, and forward are common packet-switching strategies.

## 1.6 Topologies used in NoC

Topology design is quite important in NoC. Throughput, rate of injection, latency, chip area, and hop counts are network performance parameters [16]. The role of NoC in ensuring seamless and effective communication amongst IPs (Intellectual Properties) is critical. Topologies are constructed and classed according to factors like hop counts, throughput, latency, and injection rates.

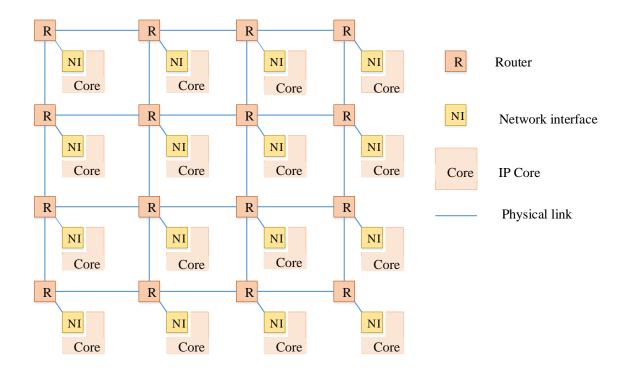

#### 1.6.1 Mesh Topology:

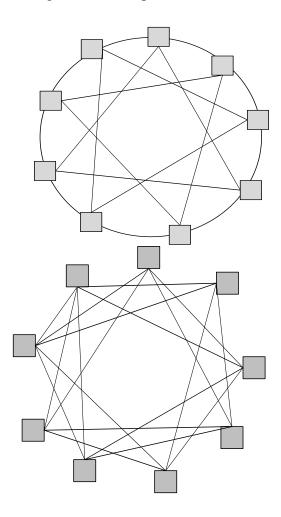

It is a sort of direct topology in which nodes are connected directly to one another. It increases route variety while simultaneously improving scalability. Mesh topology was originally created for military uses, but it is now employed in home automation, multimedia processing, and smart cities. This data is shared among all nodes. It has several sources-to-destination paths and an efficient addressing method that prevents network disruption. All the nodes are linked together in form of a 2D lattice and nearby nodes are linked together. In Mesh Topology inter-switch delays and network, robustness may be avoided. Figure 1.5 shows a model of Mesh Topology in NoC.

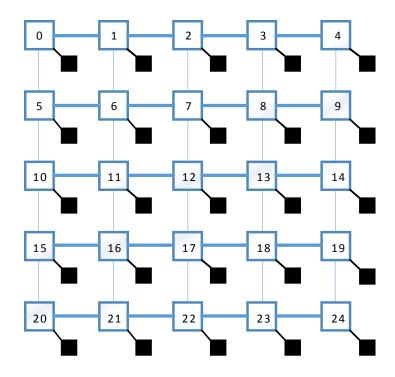

Figure 1.5: Model of Mesh Topology in NoC

#### 1.6.2 Ring Topology:

It is a network architecture where a circular link is built to convey data between nodes. It is a one-way ring network in which packets only move in a single direction. It is regarded as one of the most popular topologies. Because each neighboring node is connected by a single cable, each node has two nearby neighbors. Figure 1.6 shows the Ring Topology [Source: CISCO Packet Tracer]. Because equal bandwidth is supplied to each node, the degree of each node in the Ring topology is two [17]. The shortcoming of Ring topology is that if a single cable fails, the entire network fails and as a result network growth affects overall network performance. The data is routed via each node in the ring until it arrives at the target node.

Figure 1.6: Ring Topology

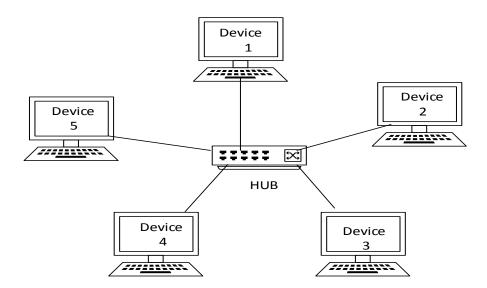

# 1.6.3 Star Topology:

Star topology is simple among all other existing topologies in terms of construction [18].

Figure 1.7: Star Topology

It is a Local Area Connection (LAN) structure where each node is connected to a central location similar to a hub. This design needs extra wires than other typical topologies. The fundamental disadvantage of star topology is that if the central node fails, the entire network fails. The width of the center node grows as the number of nearby nodes connecting to it grows. Figure 1.7 shows the Star Topology model [Source: CISCO Packet Tracer].

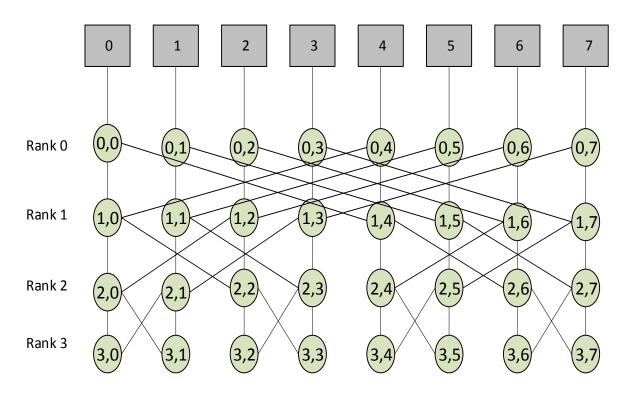

### 1.6.4 Butterfly Topology:

This architecture connects a large number of computers to extremely fast networks. The main components of this design are processor nodes, routers, and connections. The node connections are depicted in the model. Butterfly topology design and implementation take into account network factors such as bisection bandwidth, degree, and diameter. Figure 1.8 shows the Butterfly Topology in NoC

Figure 1.8: Butterfly topology in NoC

# 1.7 Metrics for Comparing Various Topologies

**Degree:** The number of links at each node refers to a degree. The Ring Topology as shown in Figure 1.6 has two links at every node. Hence it has a degree of 2. The Torus Topology has a degree of 4 as every node has four links connected to four neighboring nodes. The implementation complexity has increased to a greater degree and needs maximum ports at the routers.

**Maximum Channel Load:** This parameter is useful to estimate as a proxy the higher bandwidth supported by the network. It is somewhat synonymous with the injection bandwidth. If the channel load is two determines the load on a channel is twice the injection bandwidth.

**Hop Count:** When a packet is passed from one network segment to another is called a hop count. Hops are useful as proxy methods used to calculate network latency. The diameter of a network determines the maximum hop count. The hop count for Star Topology is 4 as shown in Figure 1.7, for Mesh Topology hop count is also 4, while for Torus Topology the hop count improves to 2.

**Data Packets:** The Bundle protocols link numerous subnets to a common single network. Bundles consume less channel width. A system can have a modified or variable bundle length. Generally, a bundle will be prefixed with data about the destination. In a system, with variable-length parcels, the length is to be integrated at the end of the bundle. Typically the parcels are split into bounces. The bounce is having the same size as that of channel width, which is the biggest measure of information that can be parallel moved.

### 1.8 Router Architecture design for 3D Torus

The router is built using a credit-based flow control method. It entails the design of an adaptive routing algorithm that uses switching techniques to execute virtual cuts. Torus is bun shape object represented as an O ring which is formed by rotating a circle via three dimension spaces about the axis that lies in the same. The mathematical expression in Cartesian coordinate for torus is mentioned in Equation No.1.1

$$Centre_C = \sqrt{u^2 - v^2 + z^2} = R^2$$

(1.1)

Where the radius of the torus from the center of the circle to the Centre of the Torus tube is represented as  $Centre_C$ , u-v-z is the indication of three axes and  $R^2$  represents the radius of the tube. The router is built to support a novel topology known as 3D Torus [19]. Figure 1.9 shows the 3D Torus Architecture. It has 1 port that is connected to the PE port and 6 ports that are connected to neighboring nodes. The hardware parameters of the 3D Torus are implemented on devices like the Xilinx Kinetic 7 and confirmed using the Xilinx 14.7 tool as illustrated.

Figure 1.9: 3D Torus Architecture

- **i. Buffer:** Buffers are FIFO (First Input First Output) devices that store flits and packets while the output port is busy.

- **ii. Routing Path Controller:** It is used to perform adaptive routing algorithms and manages the path for packets to be sent across the network.

- **iii. Virtual Channel Controller:** This component manages any system deadlocks. VCs are driven by adaptive routing algorithms, which give a fixed route for packets coming via numerous channels.

- **iv. Arbiter:** The Arbiter connects both input and output connections. It is put through a fairness test. Basic arbiters include variable priority arbiters, roundrobin arbiters, and fixed concern arbiters.

- v. Allocator: Its purpose is to create switching between input and output channels. The allocator aids in the management of connections between both channels while taking into account requests made via a specific channel.

# 1.9 NoC design in Tiers

As per the abilities and expertise of NoC designers as well as the complex issues they deal with in multi-tier architecture for network operations center design help properly share duties with different NoC levels [20].

#### 1.9.1 NoC Tier 1 - first aid:

At this level, the NoC receives architecture-related queries and handles network issues including login difficulties and network configuration checks. NoC Tier 1 professional employee's problem-solving scripts that include step-by-step guidance for efficiently resolving difficulties. NoC Tier 2 professionals are assigned to problems that demand a higher level of technical competence.

#### 1.9.2 NoC Tier 2 - More complex issues:

This level is made up of more complex professionals and deals with more complicated network difficulties which typically need a better grasp of the supporting IT architecture.

Resolving configuration difficulties, account management, and service restart are all regular responsibilities of NoC Tier 2. If a problem necessities additional in-depth investigation at the code level, it is escalated to NoC Tier 3.

#### **1.9.3 NOC Tier 3 - Advanced problems:**

Tier 3 serves as a top escalation point for NOC Tier 1 and Tier 2 specialists. Tier 3 architects are responsible for handling issues on the code and database levels and providing hotfixes. Resolving issues at NOC Tier 3 requires major skills, so you can either keep it in-house or outsource to a vendor who is ready to work at the backend level.

#### 1.9.4 Build an orderly NoC:

The foundation for well functioning network operations center is a well-chosen structure. We may tackle various issues of complex variables quickly making our network architecture genuinely trustworthy by adopting a multi-user model with correct escalation protocols for our NoC.

# 1.10 Advantages of Mesh Topology

Figure 1.10: Node arrangements in Mesh and Full Mesh Topologies (Ng Yen et al.)

The diameter for node arrangements in Mesh and Full Mesh Topologies is given by 2n-2 where n equals the number of nodes. The bisection of Mesh is given by n. The Mesh topology improves network performance by considering power reduction and less latency. Figure 1.10 indicates Node arrangements in terms of hops for Mesh and Full Mesh Topologies. Table 1.1 denotes Hop Counts in Mesh and Full Mesh Topologies respectively.

**Table 1.1: Hop Counts-Mesh and Full Mesh**

|             |           | Path            |             | Hoj  | p counts  |

|-------------|-----------|-----------------|-------------|------|-----------|

| Transmitter | Reception | Mesh Topology   | Full Mesh   | Mesh | Full Mesh |

|             |           |                 | Topology    |      |           |

| 0           | 63        | 0-8-16-24-32-   | 0-9-18-27-  | 14   | 7         |

|             |           | 40-48-56-57-58- | 36-45-54-63 |      |           |

|             |           | 59-60-61-62-63  |             |      |           |

| 5           | 35        | 5-3-21-29-37-   | 5-13-21-28- | 6    | 4         |

|             |           | 36-35           | 35          |      |           |

| 20          | 38        | 20-28-36-37-38  | 20-29-38    | 4    | 2         |

# 1.11 Motivation for Thesis

A packet-based NoC, in general is made up of routers, Network Interface between the routers, the processing units, and the interconnection networks. Each processing unit can be a general-purpose CPU, DSP an embedded memory, or something else entirely. Each processing unit is linked to a router, which links it to the processing units next to it. Later in the article, we will refer to a processing unit and its associated router as a node. The

main motivation for developing this thesis is to propose an EZ-Pass Architecture for improved performance and energy-efficient NoC.

The following issues must be addressed in the design of an NoC system.

*Scalability:* The interconnection network in an NoC system plays a vital role in offering scalability to accept a higher number of transistors and close the design productivity gap. To keep wire lengths short, on-chip networks will most likely adopt networks with reduced dimensions.

Energy Efficiency: When developing an NoC system, power must be considered as a primary design constraint because the interconnection network consumes a substantial amount of power. The interconnection network's power consumption is mostly determined by the energy consumed by the routers and the energy consumed on behalf of interconnections, which is connected to the architecture itself, the routing and switching strategies used and the power implementation approaches.

**Re-configure:** One of the most essential architectural paradigms for meeting the concurrent needs for application performance and adaptability is to re-configure the architecture. Re-configured architecture is especially appealing to reality applications owing to high efficiency, cost savings, reaching markets faster, increased flexibility, and upgradability[22]. Topology selection, communication protocol selection, and application mapping to processing units are all critical trade-offs in the design of NoCs. Systematic classification of NoC design concerns, an overview of the topologies and communication protocols utilized in NoCs is presented here as they are directly connected to router design.

# 1.12 Research Challenges

The primary purpose of the communication-centric design and the NoC paradigm is to improve design productivity and performance by dealing with rising parallelism, manufacturing complexity, wiring issues, and dependability. According to Owens et al.,

the three main hurdles for NoC are power, latency, and CAD compatibility. Several ways for networks-on-chip to solve the issues associated with bus-based interconnects have been developed allowing increased reusability and programmability through the use of standardized and layered communication protocols thus leaving reuse of communication resources and enabling increased reusability and programmability. A common strategy for NoCs is to use a regular Mesh Topology with packet switching which allows total system capacity to raise for each additional network node as the number of concurrent communication channels increases [23]. In contrast to shared bus techniques, NoCs offer better performance scalability and handle several concurrent transactions, resulting in more efficient network resource consumption. Furthermore, the relationship between wire length and system size is affected by the distribution of area between network components, and hence by the network's regularity, 2D mesh NoC assumes a constant wire length, regardless of system size. To boost system productivity, an architect must be able to abstract, represent, and handle the majority of design challenges and concerns at a high degree of abstraction. The system-level design allows one to swiftly trade-off between several QoS criteria like latency, power, cost, size, and ease of integration by reviewing many potential software-hardware architectures that match the functional standards equally well. Similarly, there are various NoC concerns to consider including the type of the NoC link, link length, serial versus parallel links, bus versus packet-based switching, and leakage current.

#### Serial versus Parallel Link

The transfer of data packets between cores in an NoC can be accomplished via either a serial or a parallel connection. Parallel connections have a buffer-based design and may be run at a lower clock rate to save power dissipation. However, the silicon cost of these parallel lines will be considerable due to inter-wire spacing, shielding, and repeaters. This can be reduced to a certain extent by using additional metal layers. Serial connections, on the other hand, provide for wire space reductions, reduced signal interference and noise, and the elimination of the requirement for buffers. Serial linkages provide the benefits of a simpler layout and easier timing verification. When running at high clock rates, serial

connections might experience ISI (Inter symbol Interference) between subsequent signals [24]. Nonetheless, such limitations can be mitigated using encoding and asynchronous communication methods.

#### **Interconnect Optimization**

Communication in NoC is based on modules connected by a network of routers with extended interconnects between the routers. As a result, it is critical reducing interconnects in order to achieve the desired system performance. The installation of repeaters is commonly used to optimize the timing of global wires. It has a considerable impact on cost, area, and power usage. According to recent research, inverters acting as repeaters will consume a significant percentage of chip resources in the near future. As a result, there is a need to optimize power on the NoC. Encoding is an efficient method of lowering dynamic power use. To make NoC designs more successful, novel approaches to optimizing the power spent by on-chip repeaters must be developed.

# 1.13 Applications

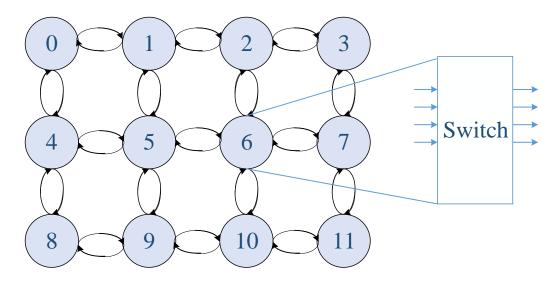

Messages can travel from the source module to the destination module over many links that include routing choices at switches in a network on a chip. It has several point-to-point data lines that are linked together via switches. It may be categorized as a scalable homogeneous switching fabric network [25].

The following characteristics are found in NoC which are as below

- NoC reduces the amount of hardware required for routing and switching activities.

- Different portions of the network can provide multi-topology and multi-option support.

- When integrated with a network on a chip, scalability, interoperability, and feature development are improved.

- When compared to alternative designs, a network on a chip improves the power efficiency of complicated system-on-chips.

- Synchronization problems are addressed more effectively than in previous approaches. The network on a chip also handles wire routing congestion better than other system-on-chips.

- Network-on-chip enables higher operating frequencies, and timing closure is considerably simpler to implement.

- Because of its well-designed and tiered strategy, problem verification is significantly easier.

### 1.14 Research Methodology

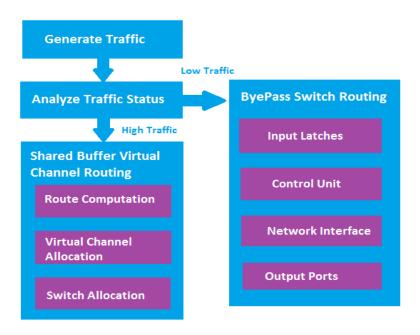

Basically, NoCs consume large amounts of entire chip power in a range of 10% to 36%. Hence a Novel approach to reduce power loss in terms of Static and Dynamic must be implemented. NoC connects various memory modules on a chip. Hence the architecture is proposed to reduce Static Power by Power Gating Techniques and reduce Dynamic Power by shared buffer concept to improve systems performance. Figure 1.11 indicates the proposed methodology.

Figure 1.11: Proposed Methodology

#### 1.15 Thesis Outline

Chapter 1: This chapter is a brief introduction to NoC and its functions. It also includes NoC architecture, Network Interface, Building block of NoC, Routers, NoC routing, Static routing, Dynamic routing, Switching strategy, NoC topology, Router architecture design for 3D Torus, NoC topology, NoC design in tiers, Motivation, Challenges, Application, and problem statement.

Chapter 2: This Chapter includes a literature review of the different techniques used in the design and implementation of EZ-pass routers for energy and performance-efficient NoC design. Several methods are used in energy and performance-efficient NoC design, they are included in this chapter with the advantages and disadvantages of each standard. Also includes the emerging trends used in NoC design, different performances used in NoC designs, and different frameworks used for designing energy and performance-efficient NoC designs can be analyzed using various techniques with advantages and disadvantages - analyzed with existing methods.

Chapter 3: This Chapter offers a realistic review of numerous routers that will be utilized in networking in the future. This chapter examines the most widely used interconnection network technologies, as well as several novel topologies. To reduce latency, enhance the throughput of a router, reduce power consumption and design area are the major outcomes of this chapter. This chapter includes a brief comparison of previously built routers as well as design criteria for the 3D Torus router. Examine their performance and build a list of their benefits and drawbacks. NoCs are a common communication route used to connect several processors and memory modules on a single device.

Chapter 4: In this chapter, a new NoC router design is proposed by extending the router architecture's Easy Pass routing and input-port modules with IRR and UFDQ respectively. This system comprised both a traditional VC router and an EZ-Pass switch to manage heavy traffic as well as intermittent and low-traffic modes. It also employed a control block and the power gating approach to turn off routers after a period of inactivity. The simulation results show that the proposed IRR-EZ pass switch has very low latency, reduced chip area, and power consumption when compared to a typical VC router. Furthermore, the addition of UFDQ and IRR helps to increase the router's performance at diverse injection rates while consuming minimal power due to its simplest hardware construction.

Chapter 5: In this chapter, the performance analysis of NoC design using BLESS, BBUS NoC, TCMP, and CHIPPER router design. When compared to standard buffer-less routers, the use of a permutation deflection network with parallel output port allocation minimizes the average flit latency of CHIPPER. The Golden Era is vastly superior in BBUS. The normalized critical path and normalized router areas of CHIPPER routers were reduced by 29.1 % and 36.2 %, respectively. When nodes require a diverse number of packets before data processing, the proposed BBUS technique can be credibly implemented. Better results are the product of high-quality effort. The approach proposed enables the development of multi-core processors.

**Chapter 6:** This Chapter includes concluding remarks, applications, and the future scope of the proposed architecture.

# **CHAPTER-2**

#### LITERATURE SURVEY

This chapter summarizes the different techniques used in the design and implementation of EZ-pass routers for energy and performance-efficient NoC design. Several methods are used in energy and performance efficient of NoC design is included in this chapter with advantages and disadvantages of each standard. Also includes the emerging trends used in NoC design, different performance parameters used in NoC designs and different frameworks used for designing energy and performance-efficient NoC can be analyzed using various techniques with advantages and disadvantages compared with existing methods.

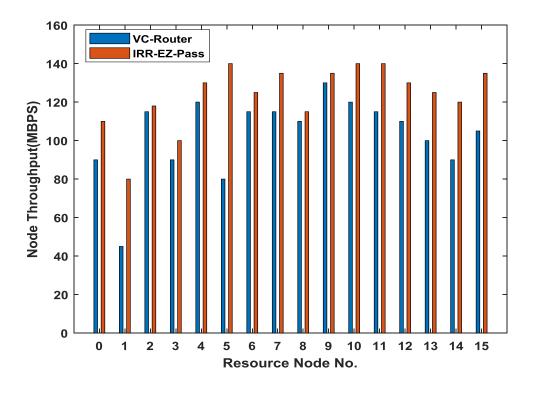

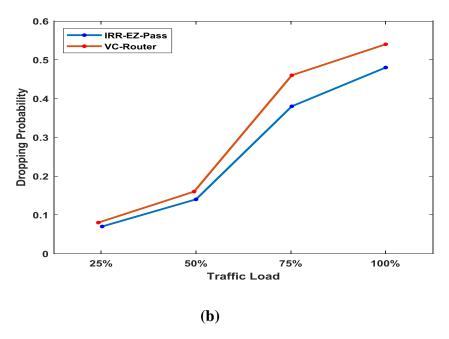

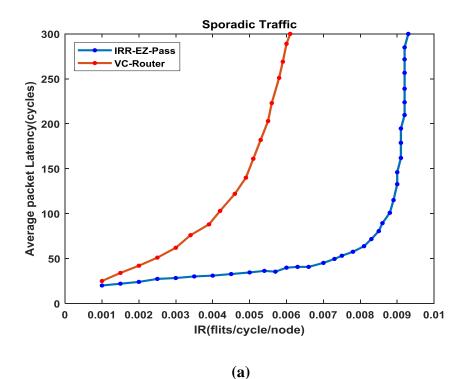

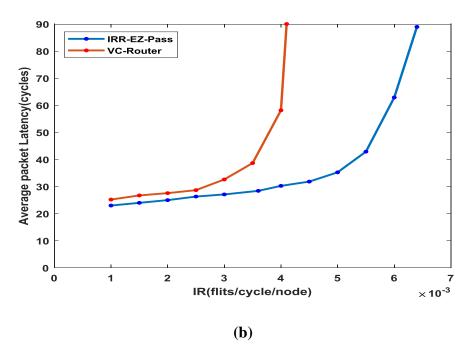

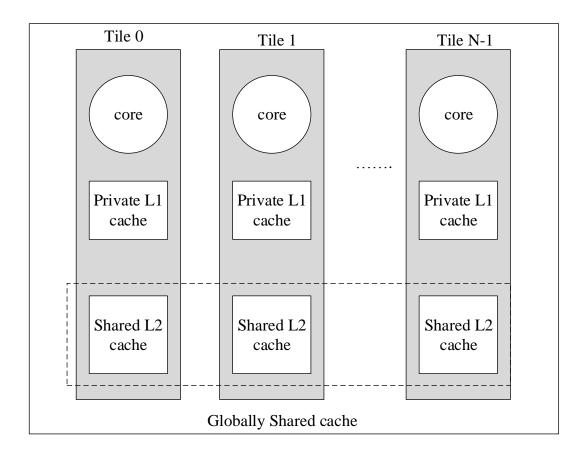

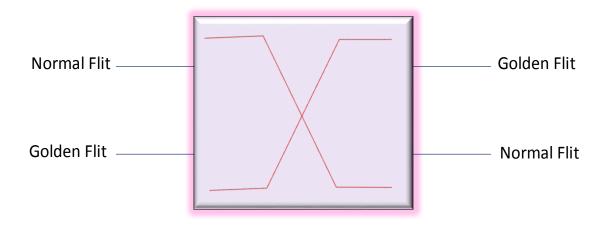

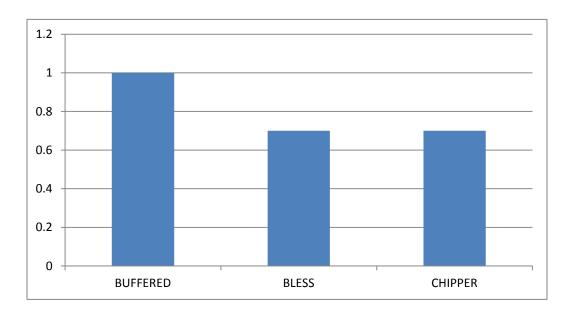

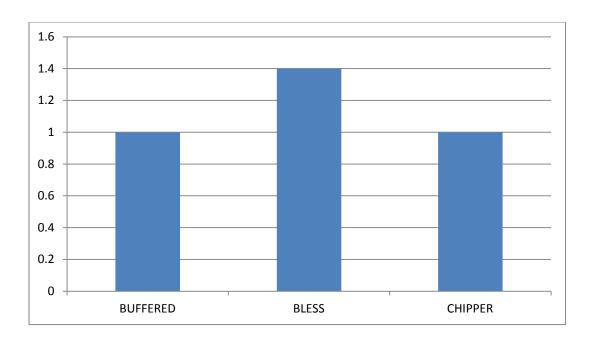

### 2.1 Emerging Trends in Network on Chip Design