# DESIGN AND PERFORMANCE EVALUATION OF GATE ENGINEERED DOUBLE GATE JUNCTIONLESS MOSFET STRUCTURE FOR LOW POWER APPLICATIONS

Thesis Submitted For the Award of the Degree of

# **DOCTOR OF PHILOSOPHY**

in

**Electronics and Communication Engineering**

By

Namrata Mendiratta

## Registration No.11816280

Supervised by

Co- Supervised by

Dr. Suman Lata Tripathi

Dr. Sweta Chander

Transforming Education Transforming India

# LOVELY PROFESSIONAL UNIVERSITY PUNJAB 2022

## DECLARATION

I hereby declare that the thesis entitled "Design and Performance Evaluation of Gate Engineered Double Gate Junctionless MOSFET Structure Low Power Applications" is submitted by me for the Degree of Doctor of Philosophy in Electronics and Communication Engineering is the result of my original and independent research work carried out under the guidance of Supervisor Dr. Suman Lata Tripathi and Co-Supervisor Dr. Sweta Chander, Professor, Lovely Professional University, Punjab. It has not been submitted for the award of any degree, diploma, associateship, fellowship of any University or Institution.

Place: **Phagwara** Date: **24/08/2022**

Nameata

Signature of the Candidate

## CERTIFICATE

This thesis entitled "Design and Performance Evaluation of Gate Engineered Double Gate Junctionless MOSFET Structure Low Power Applications" submitted by Namrata Mendiratta of Lovely Professional University is a record of bona fide research work done by her and it has not been submitted for the award of any degree, diploma, associate ship, fellowship of any University/Institution.

Place: Phagwara Date: 24/08/2022

summer.

Signature of the Supervisor

Swetz Chander

Signature of the Co-Supervisor

### ABSTRACT

The performance of conventional MOSFETs is good when its channel length exceeds 100 nm. Semiconductor sizes are shrinking all the time, and have now reached the nanoscale range. Because the size of MOSFETs is shrinking, the amount of transistors increases twice every two years. When the MOSFETs size is reduced, the channel length is reduced, resulting in short channel effects and increased leakage of the current. Short channel effects have been caused by the shrinking of semiconductor devices (SCEs). Parasitic capacitances, drain-induced barrier lowering, mobility degradation, and hot carrier effects are only a few of the short channel effects. Devices must be constructed utilising various approaches like as gate engineering and channel engineering to mitigate these effects. Due to extension of breadth of the drain barrier into the drain and the source area barrier lowers, SCEs occur. Many MOSFETs structures have been created to overcome SCEs, including gate all around MOSFETs, double gate MOSFETs, triple gate MOSFETs, SOI MOSFETs & double step buried oxide MOSFETs. The advantages of a double gate MOSFETs over a bulk MOSFETs are numerous. Short channel effects and junction capacitance are reduced. It also offers SOI dielectric isolation (silicon on insulator). It is also employed in CMOS technology as it has speed of performance is high and the power usage is low.

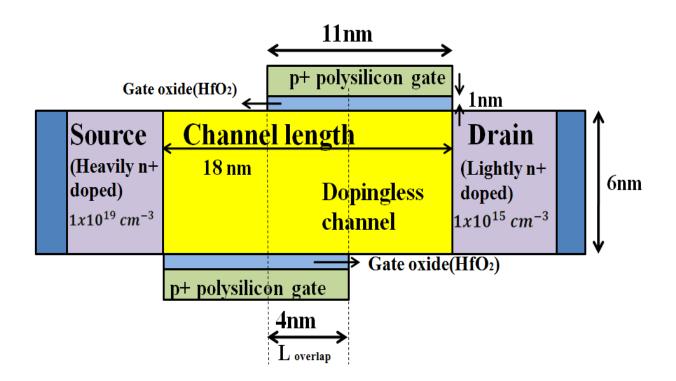

Memory is also stored using MOSFETs and is utilised to make SRAM cells, which are used to store data. For low power applications, an asymmetrical junctionless dopingless (AJ) double gate (DG) MOSFETs, with an 18 nm channel length has been proposed to decrease short channel effects (SCEs). The transistor's main goal is to achieve a desired ON/OFF state current ratio while keeping subthreshold performance characteristics within limits. Various parameters affecting the sensitivity of dopingless AJ DG MOSFETs, such as drain extension and channel lengthgate overlapping and oxide thickness of the AJ DG MOSFET with doped channel region are compared. The ON state current achieved was  $3.80 \times 10^6$  A/m, with an leakage current decrease of up to  $1.37 \times 10^{17}$  A/m. The suggested device's SS & DIBL are  $59.5 \ mV/decade$  and  $10.5 \ mV/V$ , respectively. A nanogap

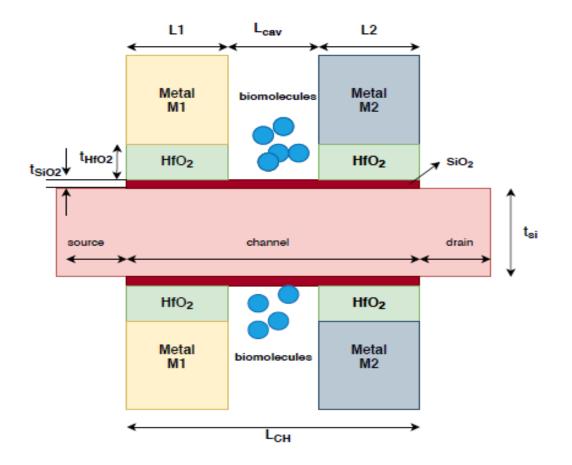

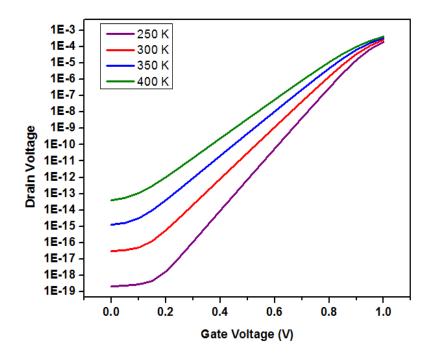

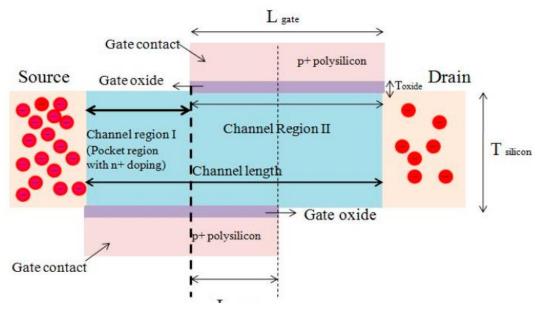

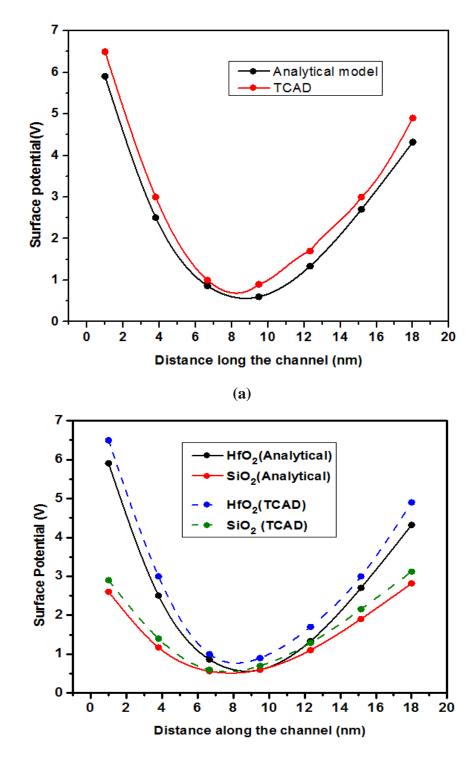

cavity area is inserted at the gate-oxide interface to create a strongly doped n+ pocket AJ MOSFET for its applications in biomedical . The nanogap cavity region is placed in such a way that when the biomolecules existing in the cavity region are changed, the device demonstrates sensitivity. The research is centred on dielectric modulation, or changes in dielectric properties caused by biomolecule variations in the human body and environment. For the examination of asymmetrical junctionless double-gate MOSFETs, several gate oxide materials such as SiO<sub>2</sub> and HfO<sub>2</sub> are employed, as well as diverse gate contact materials such as aluminium, copper, and polysilicon (AJDG-MOSFET). Temperature analysis was carried out at temperatures of 250 K, 300 K, 350 K, and 400 K. When temperature increases, increase in the OFF state current or the leakage current is observed. The surface potential of an AJDG MOSFET with a channel length of 18 nm and a gate length of 11 nm is calculated using solutions derived from 2-D Poisson's equations. The suggested device is split into three pieces, with the first two acting as single gate MOSFETs and the third acting as a double gate MOSFET. The surface potential calculated using simulation data.

### **OBJECTIVES**

- To design a double gate junctionless MOSFET by applying gate and channel engineering with the variation in material, dimensions and doping level.

- Suppressing Short Channel Effects (SCEs) for MOSFET below 20 nm technology.

- To derive and analyse the capacitive model of the proposed device structure.

- To design SRAM cell with the help of proposed nMOSFET and pMOSFET structure for low power applications

### ACKOWLEGMENT

First and foremost, I am thankful to almighty for making things possible at the right time. I owe my success to my supervisor and would like to sincerely thank Dr. Suman Lata Tripathi and co-supervisor Dr. Sweta Chander for their guidance. I greatly appreciate his support, positive attitude, and their vast knowledge in a wide range of topics. Their guidance not only in terms of giving ideas and solving research problems, but also in terms of giving freedom to do research in my own way has proved to be useful and invaluable. I am deeply influenced by my supervisor's way of guidance and sincerely thankful for standing by my side in tough times. I would like to thank my husband Sidharth Sharma, for his unconditional love, support and encouragement. Last but not least, I would like to thank my family (especially my mother and father) and my friends for their continuous love and support. Finally, special thanks to all the people who helped me in direct and indirect ways to accomplish this work.

# TABLE OF CONTENTS

| DECLARATION                                      | II |

|--------------------------------------------------|----|

| CERTIFICATE                                      |    |

| ABSTRACT                                         |    |

| ACKNOWLEDGEMENT<br>TABLE OF CONTENTS             |    |

| LIST OF TABLES.                                  |    |

| LIST OF FIGURES                                  |    |

| LIST OF ABBREVATIONS                             |    |

| CHAPTER 1: INTRODUCTION                          | 1  |

| 1.1 Evolution of VLSI                            | 1  |

| 1.2 Moore's Law                                  | 2  |

| 1.3 Basics of MOSFET                             | 3  |

| 1.4 Basic operating principle of MOSFET          | 4  |

| 1.5 Need and challenges                          | 5  |

| 1.6 Effects of MOSFET scaling                    | 7  |

| 1.7 Importance of High K Dielectric              |    |

| 1.8 Reasons for selecting DG MOSFET              | 14 |

| 1.9 Different MOSFET structures and Applications | 14 |

| 1.10 Motivation for Research work                | 17 |

| 1.11 Performance parameters of MOSFET            | 19 |

| 1.12 TCAD Simulating Tool                        | 21 |

| 1.13 Gate and channel engineering                | 22 |

| 1.13.1 Gate Engineering                          | 22 |

| 1.13.2 Channel engineering                       | 24 |

| 1.14 Thesis Outline                              |    |

| CHAPTER 2   | : LITERATURE REVIEW                                               | 27       |

|-------------|-------------------------------------------------------------------|----------|

| 2.1 Effect  | of gate engineering on DG MOSFET                                  | 27       |

| 2.2 Gate a  | ll around junctionless MOSFET having source/drain extension       | 28       |

| 2.3 Reliab  | ility of junctionless double gate (JLDG) MOSFET                   | 29       |

| 2.4 A dou   | ble step buried oxide(DSBO) SOI MOSFET                            | 29       |

| 2.5 Gate u  | nderlap junctionless double gate MOSFET (JL DG MOSFET)            | 31       |

| 2.6 Silicon | based MOSFET                                                      | 32       |

| 2.7 Black   | phosphorus junctionless recessed channel MOSFET                   | 33       |

| 2.8 Dual n  | naterial surrounding gate (DMSG) MOSFET                           | 34       |

| 2.9 Gradeo  | d channel dual material gate junctionless (GC-DMGJL) MOSFET       | 35       |

| 2.10 Junct  | ionless MOSFET structure for detecting biomolecule                | 36       |

| 2.11 Pock   | et of n-MOSFET                                                    | 37       |

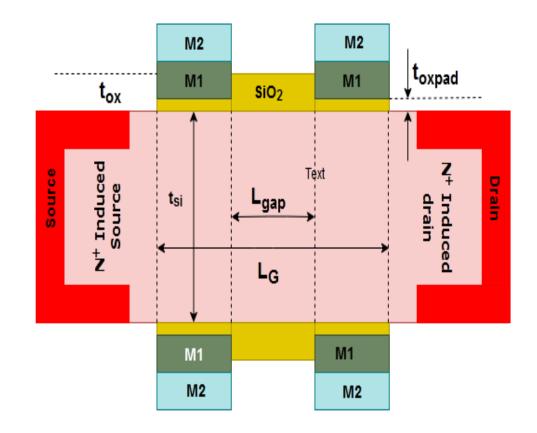

| 2.12 Nano   | scale SOI MOSFET with electrically induced and drain extension    |          |

| 2.13 Cyline | drical Surrounding gate MOSFET with dual material                 | 39       |

| 2.14 DG jı  | unctionless MOSFET using gate engineered material and source/dr   | ain ext- |

| ension      | ns                                                                | 40       |

| 2.15 Juncti | onless MOSFET with asymmetrical gates                             | 41       |

| 2.16 MOSI   | FET with recessed channel and transparent gate                    | 42       |

| 2.17 Juncti | onless transistor based 6-T SRAM cell                             | 43       |

| 2.18 Short  | channel junctionless double-gate MOSFET                           | 44       |

| 2.19 DM g   | ate with short channel with recessed source and drain SOI MOSFET. | 45       |

| 2.20 DG M   | IOSFET                                                            | 46       |

| 2.22 DG ci  | rcular MOSFET                                                     | 47       |

| 2.23 Gate   | underlap dielectric modulated MOSFET based on charge plasma       | ı a bio  |

| sense       | or                                                                | 48       |

| 2.24 Dual   | material surrounding split gate junctionless transistor (DMSG JL  | T) as    |

| biose       | ensor                                                             | 49       |

| 2.25 Resear | rch Gap and Motivation for research work                          | 58       |

| 2.26 Summary                                                                             | 59        |

|------------------------------------------------------------------------------------------|-----------|

| CHAPTER 3: 18 nm N-CHANNEL AND P-CHANNEL DOPINGLESS ASY<br>TRICAL JUNCTIONLESS DG-MOSFET |           |

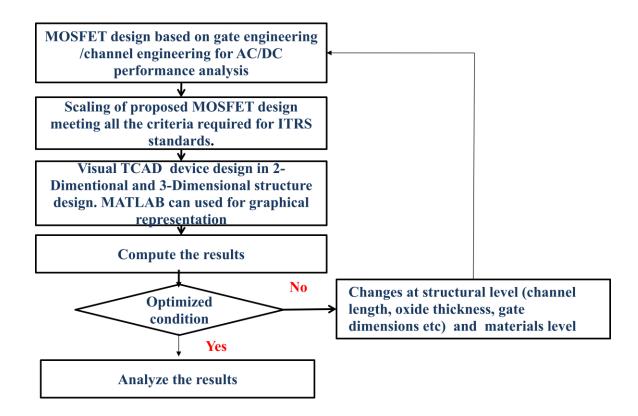

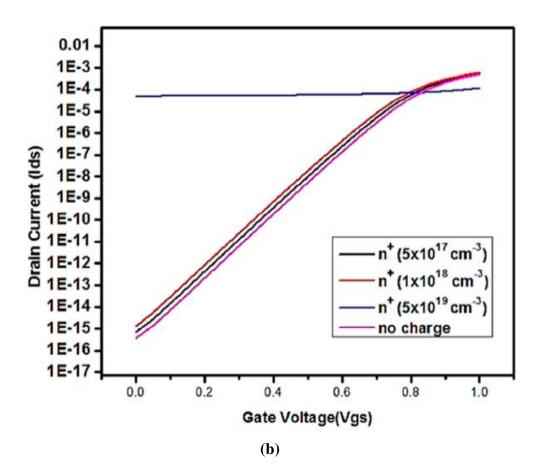

| 3.1 Design Methodology                                                                   | 60        |

| 3.2 Device structure and dimension of dopingless asymmetrical junctionless               | DG        |

| MOSFET                                                                                   | 61        |

| 3.3 Result and discussion                                                                | 64        |

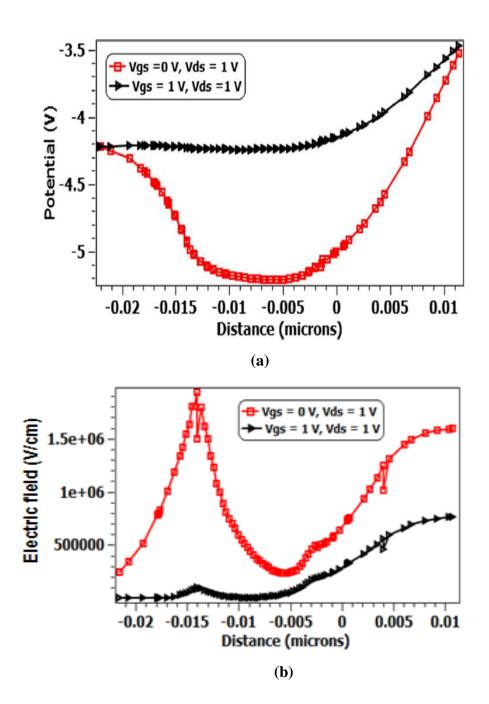

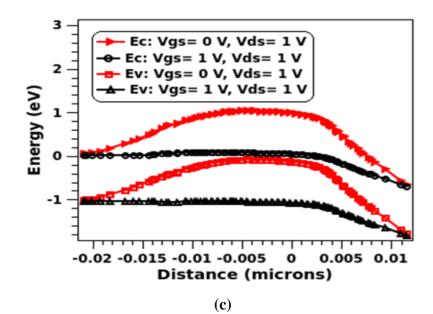

| 3.3.1 Electric potential, electric field and energy band diagram                         | 64        |

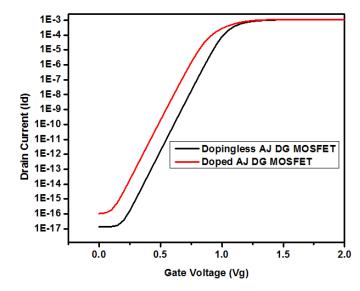

| 3.3.2 ON State Current and OFF State Current of the Proposed Device                      | 66        |

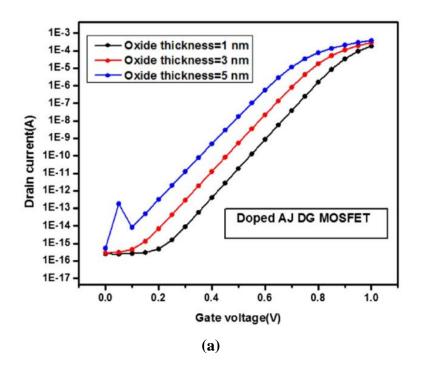

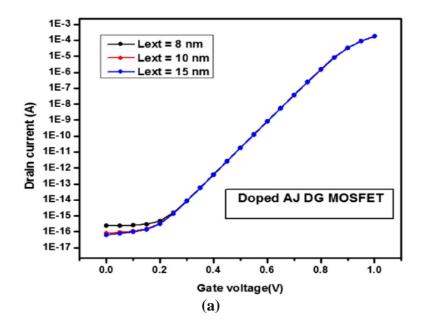

| 3.3.3 Sensitivity Analysis of the Proposed Device                                        | 68        |

| 3.3.4 Reduction in Short Channel Effects (SCEs)                                          | 72        |

| 3.3.5 Different gate contact materials                                                   | 74        |

| 3.3.6 Temperature analysis                                                               | 76        |

| 3.4 Summary                                                                              | 78        |

| CHAPTER 4: HEAVILY DOPED N+ POCKET ASYMMETRICAL JUNC<br>LESS DOUBLE GATE MOSFET          | 79        |

| MOSFET with n+ pocket                                                                    |           |

| 4.2 ON State Current and OFF State Current of the Proposed Device                        |           |

| 4.3 Reduction in Short Channel Effects (SCEs)                                            | 83        |

| 4.4 Summary                                                                              |           |

| CHAPTER 5 : APPLICATIONS OF THE PROPOSED DEVICES                                         | 87        |

| 5.1 Proposed Heavily Doped n+ Pocket AJ DG MOSFET with a Nanoga                          | ap-Cavity |

| Region                                                                                   |           |

| 5.2 Sensitivity of the device for detecting biomolecules                                 | 90        |

| 5.3 P-channel dopingless AJ DG MOSFET                                                    | 95        |

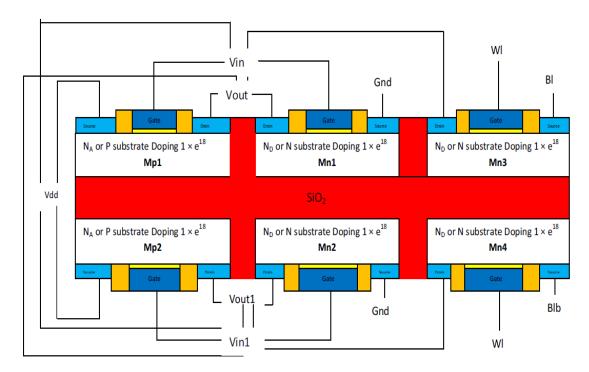

| 5.4 CMOS based logic and memory design               | 98  |

|------------------------------------------------------|-----|

| 5.4.1 CMOS inverter design using proposed transistor | 98  |

| 5.4.2 6T SRAM CELL with Proposed Transistors         | 101 |

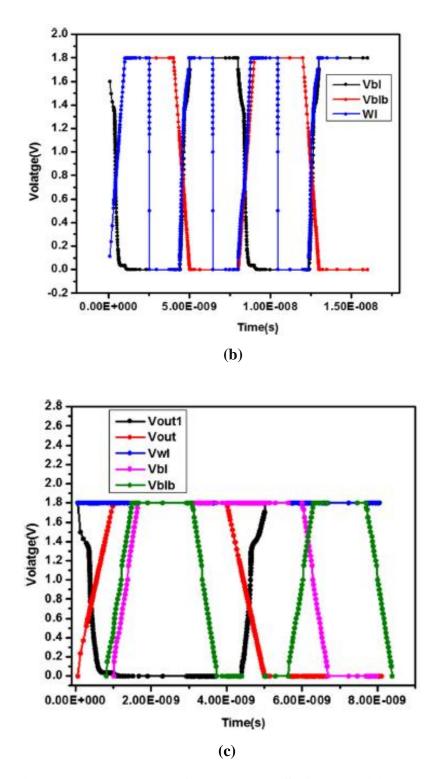

| 5.5 Proposed Fabrication steps of Inverter           | 104 |

| 5.6 Summary                                          | 106 |

# CHAPTER 6 : ANALYTICAL AND CAPACITANCE MODELLING OF

| PROPOSED AJ DG MOSFET                                                | 107 |

|----------------------------------------------------------------------|-----|

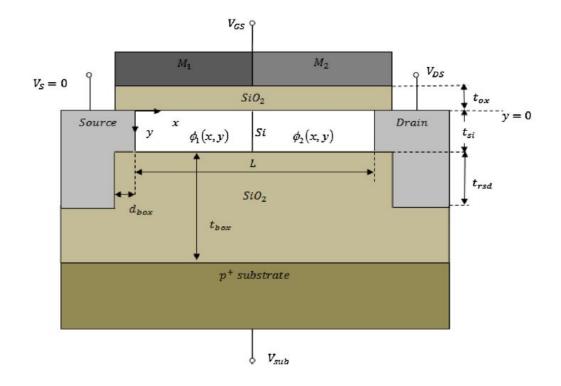

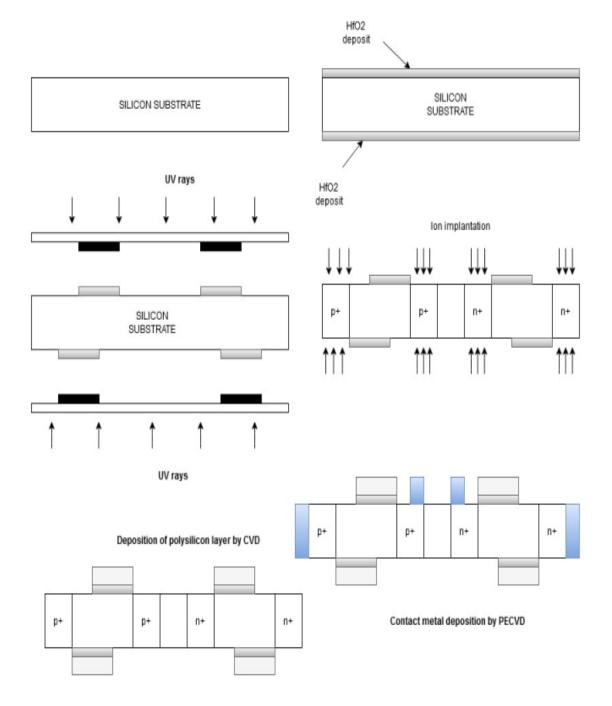

| 6.1 Surface potential for proposed AJDG MOSFET                       |     |

| 6.2 Results and discussion for analytical model of surface potential | 113 |

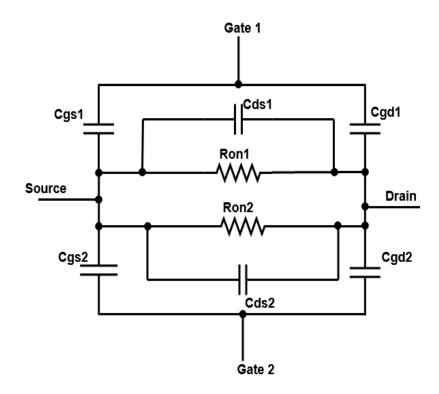

| 6.3 Capacitance Model                                                | 115 |

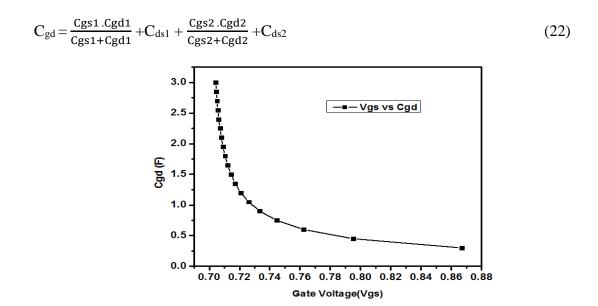

| 6.4 Subthreshold parameter variations with gate capacitance          | 119 |

| 6.5 Summary                                                          | 121 |

| 123 |

|-----|

|     |

| BIBLIOGRAPY          | 124 - 136 |

|----------------------|-----------|

| LIST OF PUBLICATIONS | 137       |

# LIST OF TABLES

| <b>2.1</b> Literature review                                                 | 51          |

|------------------------------------------------------------------------------|-------------|

| 3.1 Dimensions of the proposed dopingless AJ DG MOSFET                       | 63          |

| 3.2 Comparison of ON state and OFF state current of dopingless AJ DG MOSH    | FET and     |

| doped AJ DG MOSFET                                                           | 67          |

| 3.3 Comparison of performance parameters of different MOSFET structures      | 75          |

| 3.4 Comparison table of improvement /deterioration in performance par        | rameters of |

| proposed dopingless AJ DG MOSFET in percentage                               | 76          |

|                                                                              |             |

| <b>4.1</b> Dimensions of the proposed heavily doped $n+$ pocket AJ DG MOSFET | 80          |

| 4.2 Comparison of ON state and OFF state current of AJ DG MOSFET with n+     | pocket      |

| region and AJ DG MOSFET without pocket region                                | 82          |

| 4.3 Comparison of existing MOSFET structures                                 |             |

| 6.1 Parameters along with their symbol for Surface potential of AJ DG MOSFE  | ET110       |

| 6.2 Comparison table of surface potential for Analytical model and TCAI      | D model of  |

| proposed AJ DG MOSFET along the channel length                               | 115         |

| 6.3 Parameters along with their symbol for capacitance model of AJ DG MOSE   | ÆТ116       |

# LIST OF FIGURES

| 1.1 Moore's Law                                                                           | 3  |

|-------------------------------------------------------------------------------------------|----|

| <b>1.2</b> Single gate MOSFET                                                             | .4 |

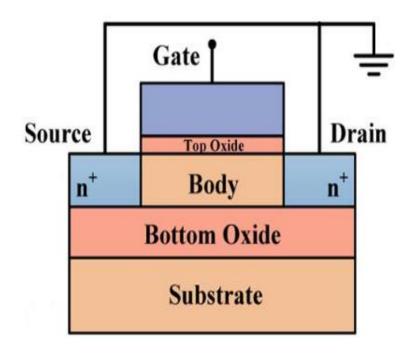

| 1.3 Double gate (DG) MOSFET                                                               | .7 |

| 1.4 Channel Length Modulation                                                             | .9 |

| <b>1.5</b> Hot Carrier Effect1                                                            | 0  |

| 1.6 Impact Ionization1                                                                    | .2 |

| <b>1.7</b> Source/ Drain parasitic capacitances1                                          | 2  |

| <b>1.8</b> Different advanced MOSFET Structures1                                          | 7  |

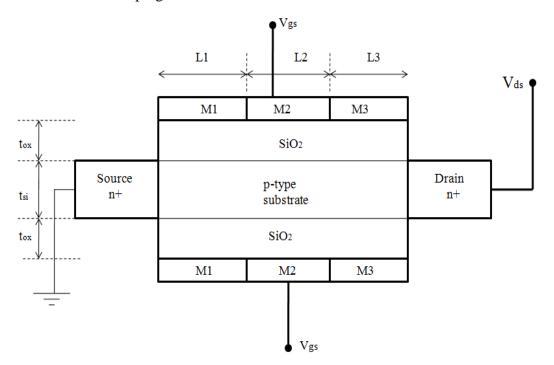

| <b>1.5</b> Dual material gate FET (DMGFET) structure2                                     | 23 |

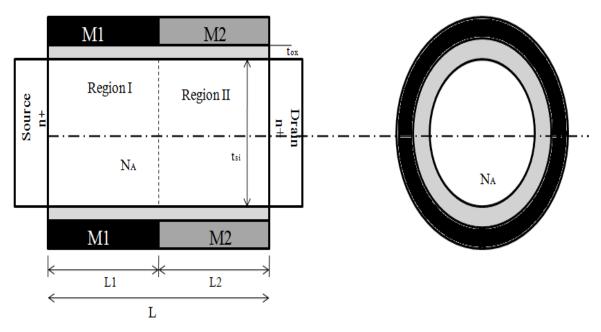

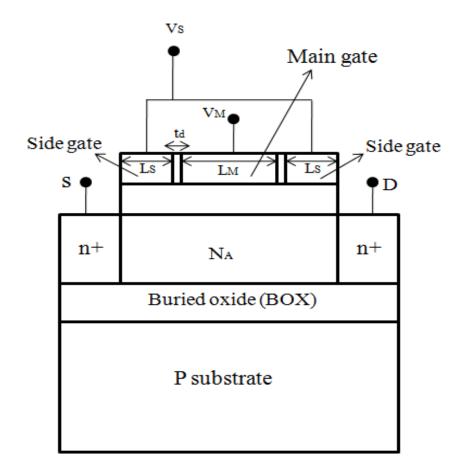

| 2.1 TM-DG MOSFET Structure                                                                | 28 |

| 2.2 GAAJ MOSFET with S/D extensions regions                                               | 29 |

| 2.3 Schematic diagram of n-type JLDG MOSFET                                               | 0  |

| 2.4 Schematic cross-sectional view of DSBO-SOI structures                                 | 0  |

| 2.5 The gate underlap region is considered at the source end of the channel region of .   | JL |

| DG MOSFET3                                                                                | 1  |

| 2.6 The gate underlap region is considered at the drain end of the channel region of JL D | G  |

| MOSFET                                                                                    | 2  |

| 2.7 Silicon based MOSFET for high temperature operation                                   | 33 |

| 2.8 Design of BP JL RC MOSFET                                                             | 4  |

| 2.9 Structure of DMSG MOSFET                                                              | 5  |

| 2.10 Structure of GC-DMGJL MOSFET                                                         | 6  |

| 2.11 Junctionless MOSFET structure for detecting biomolecules                             | 7  |

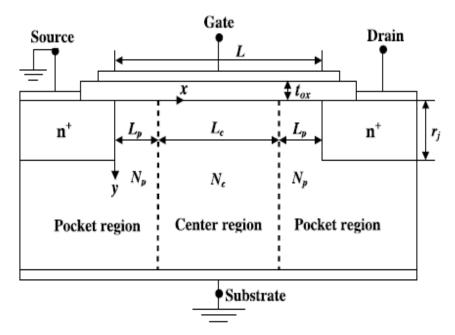

| 2.12 Structure of a pocket n-MOSFET                                                       | 8  |

| <b>2.13</b> Structure of EJ-SOI MOSFET                                                           |

|--------------------------------------------------------------------------------------------------|

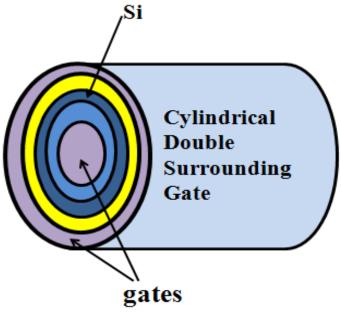

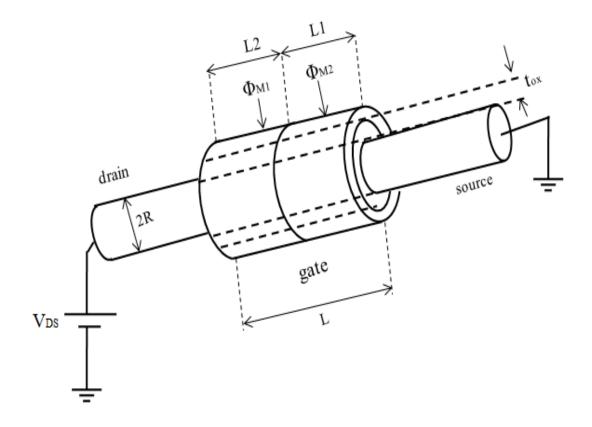

| <b>2.14</b> Cylindrical Surrounding gate MOSFET40                                                |

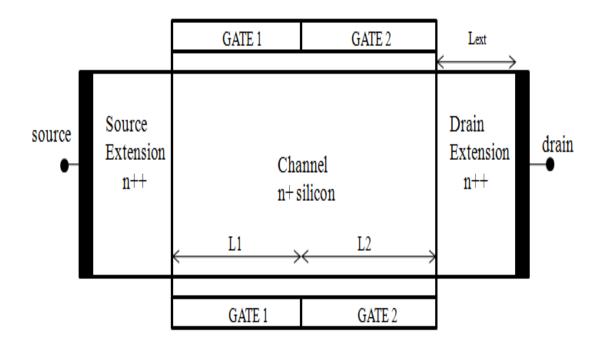

| 2.15 DG junctionless MOSFET with extensions and engineering of gate materia41                    |

| <b>2.16</b> Junctionless MOSFET with asymmetrical gates                                          |

| 2.17 Structure of recessed channel MOSFET with transparent gate43                                |

| <b>2.18</b> 6T SRAM cell using SOI44                                                             |

| 2.19 Junctionless double-gate MOSFET45                                                           |

| <b>2.20</b> Dual metal gate (DMG) with recessed source and drain UTB SOI MOSFET46                |

| <b>2.21</b> Structure of DG MOSFET47                                                             |

| <b>2.22</b> Double gate Circular MOSFET48                                                        |

| <b>2.23</b> Dielectric modulated MOSFET based on charge plasma concept49                         |

| <b>2.24</b> DMSGJLT as biosensor                                                                 |

| <b>3.1</b> Design Methodology61                                                                  |

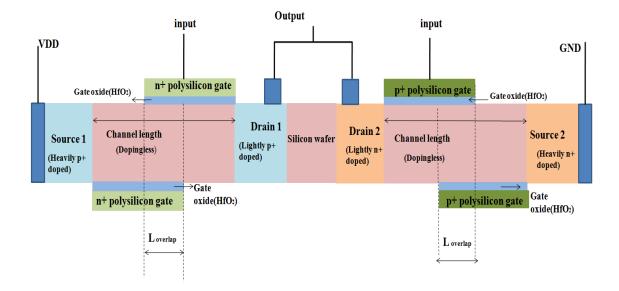

| <b>3.2</b> Dopingless asymmetrical junctionless DG MOSFET                                        |

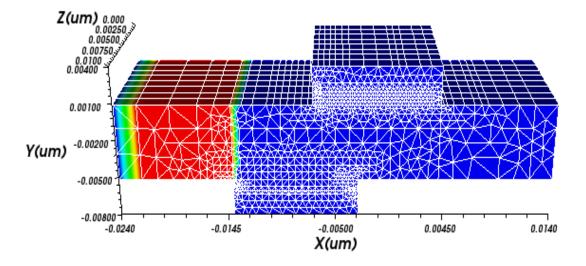

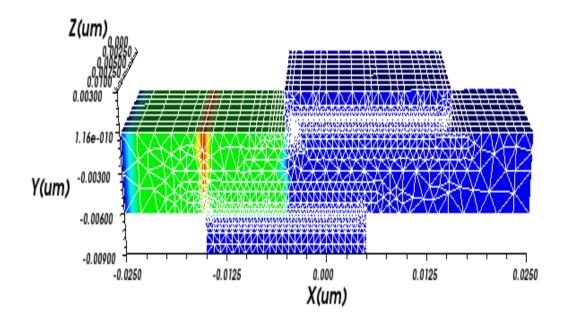

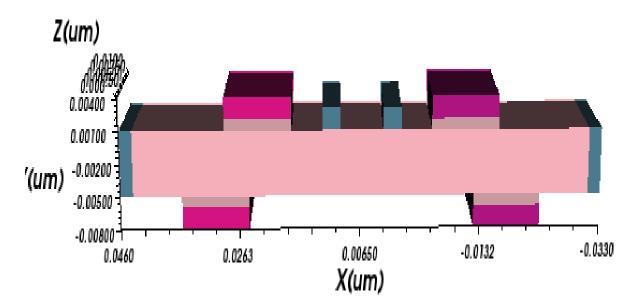

| <b>3.3</b> 3-D view of simulated dopingless AJ DG MOSFET along with mesh63                       |

| <b>3.4</b> (a) Electric potential of dopingless AJ DG MOSFET (b) Electric field of dopingless AJ |

| DG MOSFET (c) Energy band diagram of dopingless AJ DG MOSFET65-66                                |

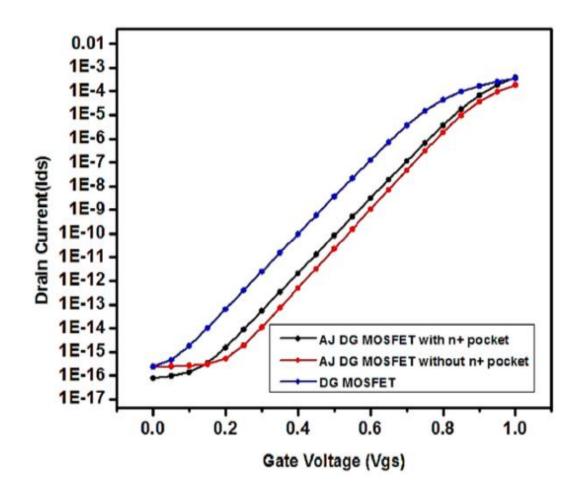

| <b>3.5</b> Vgs v/s Id graph for dopingless AJ DG MOSFET and doped AJ DG MOSFET67                 |

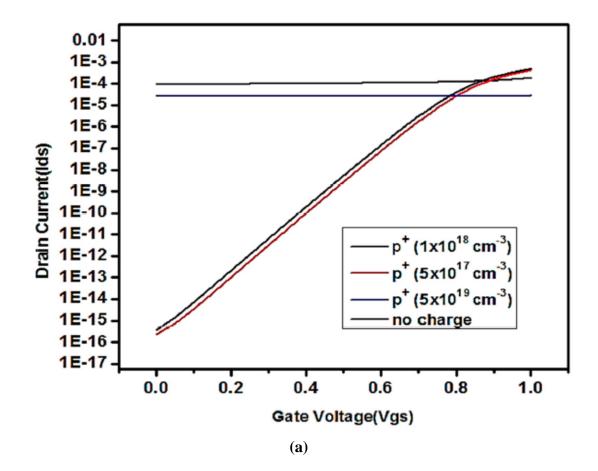

| <b>3.6</b> Gate voltage versus drain current graph of (a) Variation in oxide thickness of doped  |

| AJ DG MOSFET (b) Variation in oxide thickness of dopingless AJ DG MOSFET of                      |

| 18nm                                                                                             |

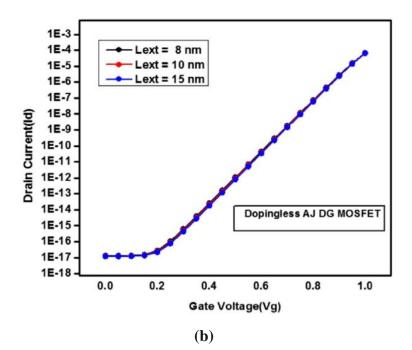

| 3.7 Gate voltage versus drain current graph of (a) Variation in length of drain extension of     |

| doped AJ DG MOSFET (b) Variation in drain extension of dopingless AJ DG                          |

| MOSFET of18 nm                                                                                   |

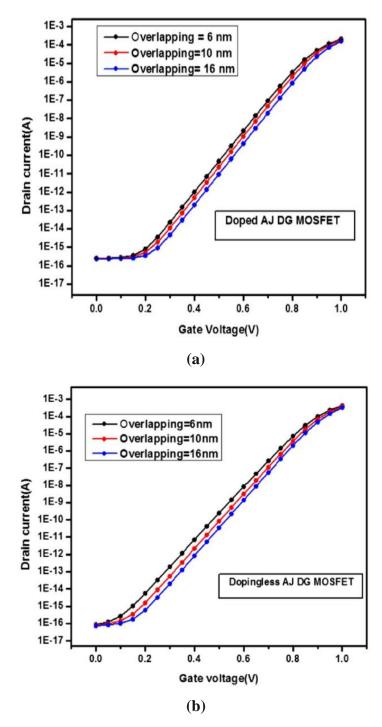

| 3.8 Gate voltage versus drain current graph (a) Variation in the overlapping region of           |

| doped AJ DG MOSFET of (b) Variation in an overlapping region of dopingless AJ                    |

| DG MOSFET71                                                                                      |

|                                                                                                  |

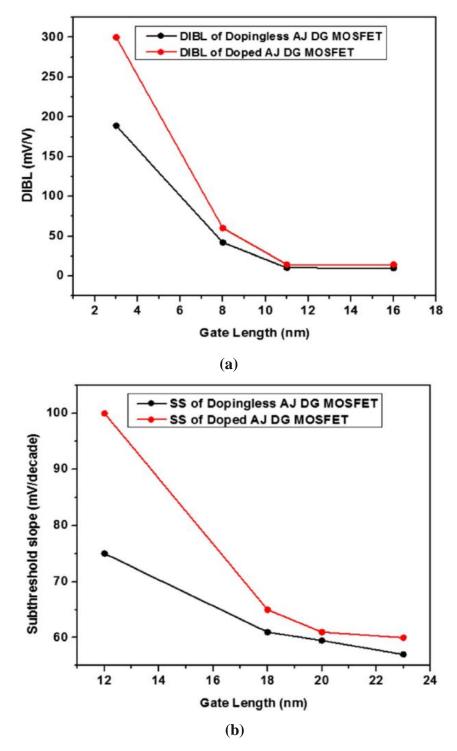

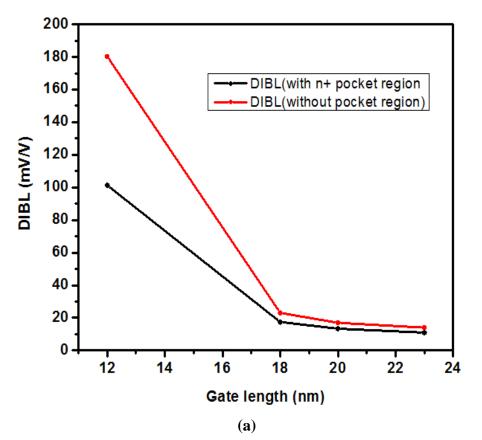

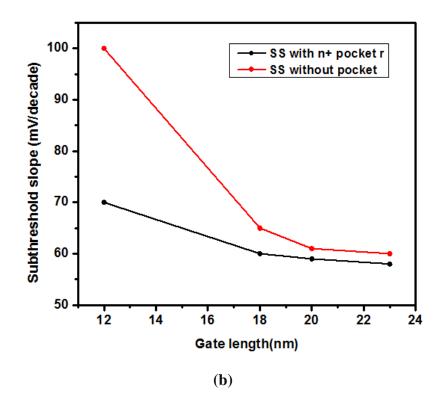

| $\boldsymbol{3.9}$ (a) DIBL values at different gate length of dopingless AJ DG MOSFET and doped AJ   |

|-------------------------------------------------------------------------------------------------------|

| DG MOSFET (b) SS values at different gate length of dopingless AJ DG MOSFET                           |

| and doped AJ DG MOSFET73                                                                              |

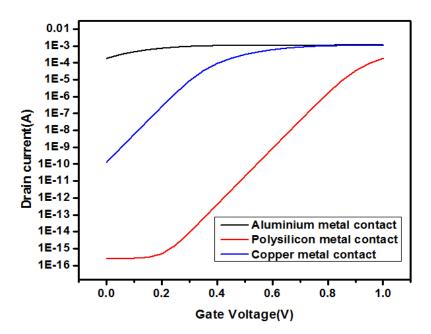

| <b>3.10</b> Vgs versus Id plot of different gate contact material                                     |

| 3.11 Temperature Analysis of dopingless AJ DG MOSFET77                                                |

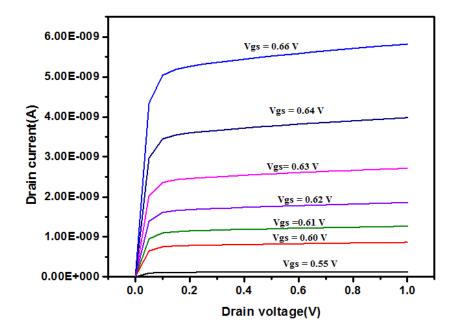

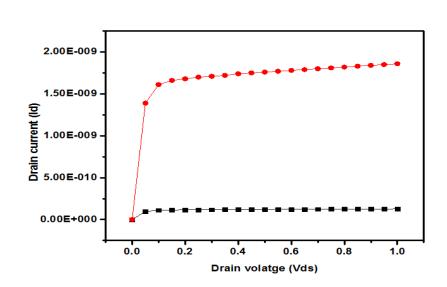

| <b>3.12</b> Graph of drain voltage versus drain current77                                             |

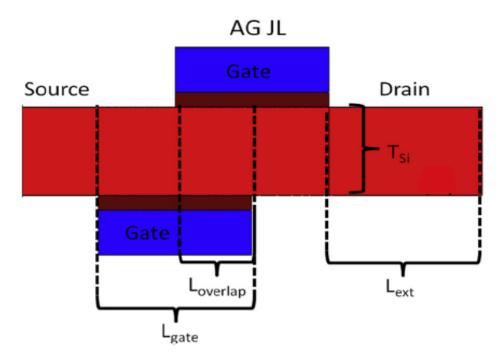

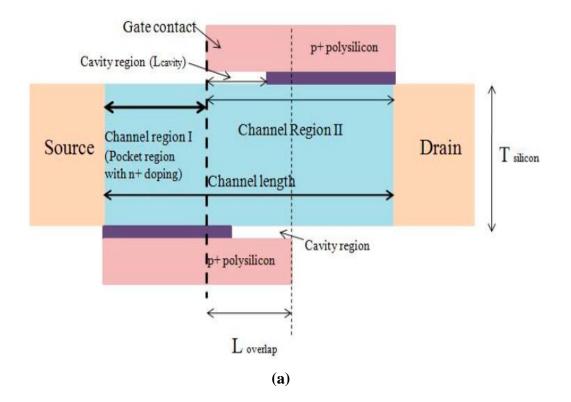

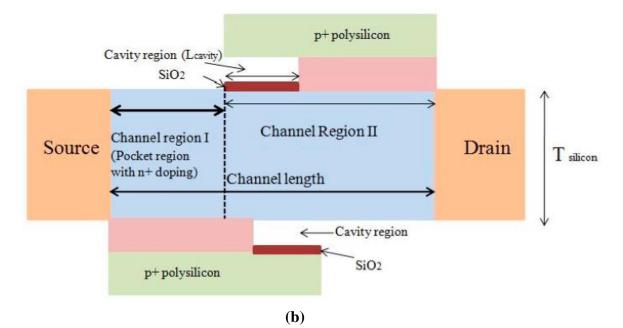

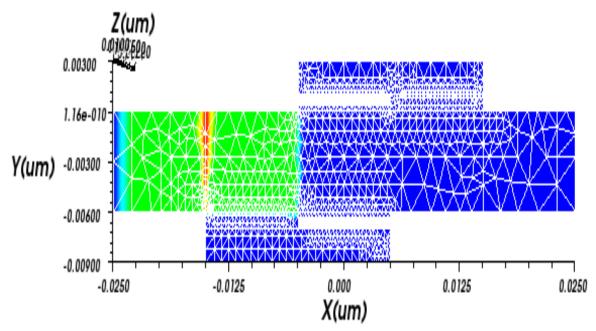

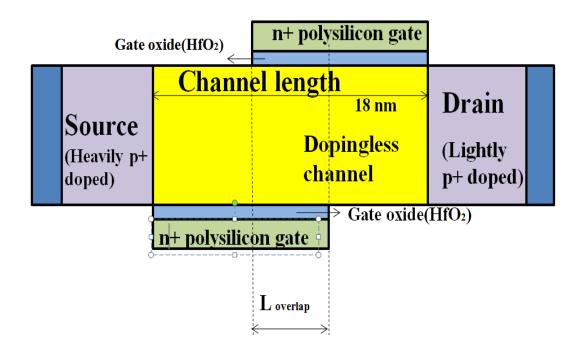

| <b>4.1</b> Design of dopingless asymmetrical JLDG MOSFET with n+ pocket region80                      |

| <b>4.2</b> 3-D Schematic of asymmetrical junctionless DG MOSFET with n+ pocket region                 |

| using TCAD simulation80                                                                               |

| 4.3 Drain current variations concerning gate voltage for heavily doped n+ pocket AJ DG                |

| MOSFET82                                                                                              |

| <b>4.4</b> (a) DIBL values at different gate length of AJ DG MOSFET with $n+$ pocket and AJ           |

| DG MOSFET without pocket (b) SS values at different gate length of AJ DG                              |

| MOSFET with n+ pocket and AJ DG MOSFET without pocket83 -84                                           |

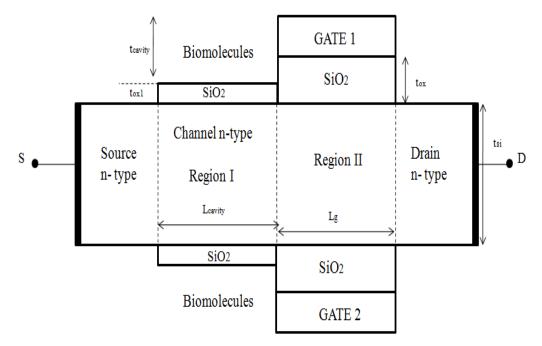

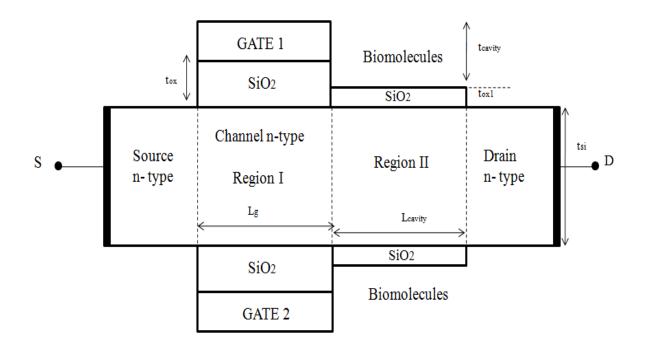

| 5.1 (a) n+ pocket AJ DG MOSFET with a cavity region; (b) n+ pocket AJ DG MOSFET                       |

| with a cavity region over a SiO <sub>2</sub> layer                                                    |

| <b>5.2</b> Simulation of n+ pocket AJ DG MOSFET with a cavity region using TCAD89                     |

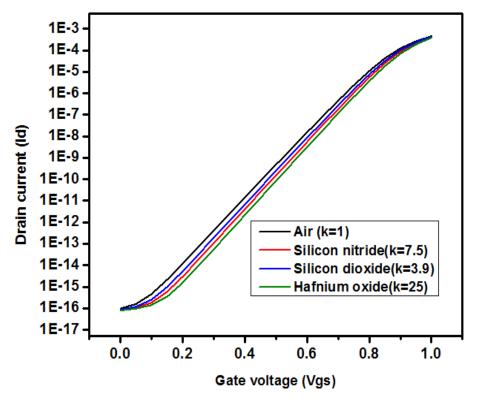

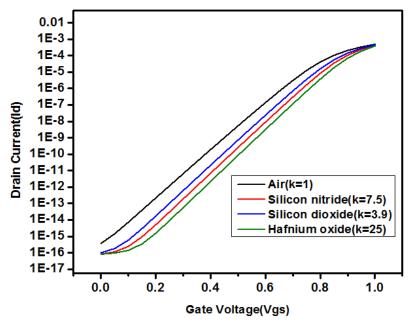

| 5.3 (a) Id v/s Vgs with different dielectric constants ( $L_{cavity}=3$ nm) (b) Id v/s Vgs with       |

| different dielectric constants ( $L_{cavity}=5$ nm) (c) Id v/s Vgs with different dielectric          |

| constants (L <sub>cavity</sub> =7 nm)90 - 91                                                          |

| <b>5.4</b> Drain current versus gate voltage curve, with (a) air $(K = 1)$ as the dielectric material |

| (b) silicon nitride (K = 7.5) as the dielectric material (c) silicon dioxide (K = 3.9) as             |

| the dielectric material                                                                               |

| 5.5 (a) Drain current versus gate voltage of the proposed $n+$ pocket AJ DG MOSFET for                |

| p+ charge concentration in the cavity region (b) Drain current versus gate voltage of                 |

| the proposed n+ pocket AJ DG MOSFET for n+ charge concentration in the cavity                         |

| region                                                                                                |

| <b>5.6</b> A p-channel dopingless AJ DG MOSFET96                                                      |

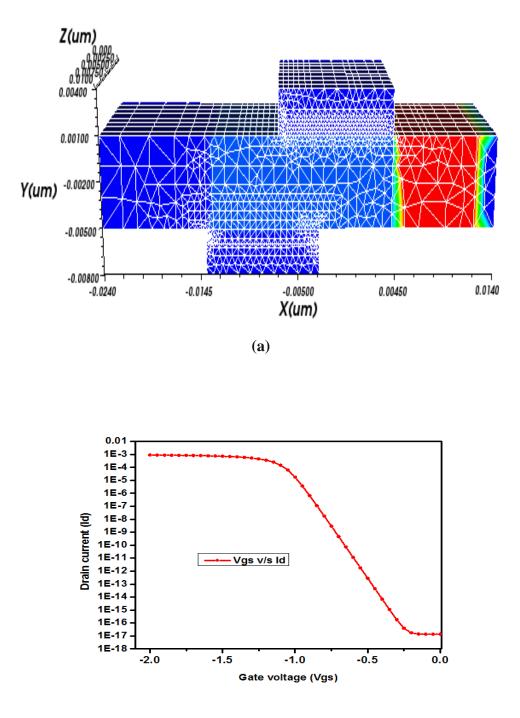

| 5.7 (a) 3-D Schematic p channel asymmetrical junctionless DG MOSFET using TCAD                    |

|---------------------------------------------------------------------------------------------------|

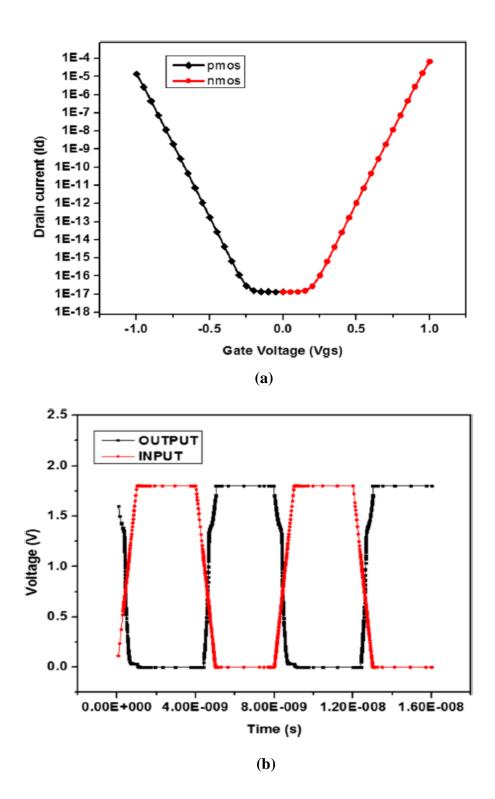

| simulation tool (b) Vgs versus Id for 4 p-channel dopingless AJ DG MOSFET97                       |

| <b>5.8</b> Design of inverter using nmos and pmos of dopingless AJ DG MOSFET99                    |

| <b>5.9</b> 3-D Schematic of inverter using TCAD simulation tool                                   |

| 5.10 (a) Matching of nmos and pmos of dopingless AJ DG MOSFET (b) INPUT and                       |

| OUTPUT response for the CMOS inverter with respect to time100                                     |

|                                                                                                   |

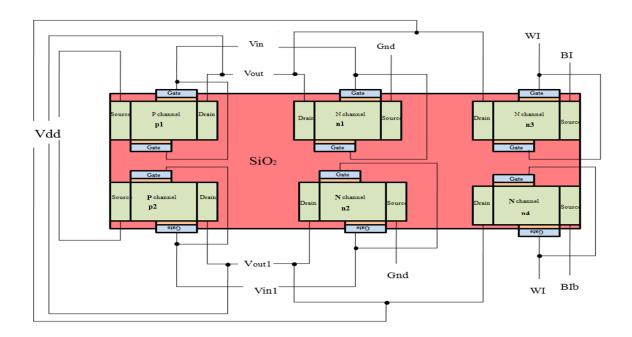

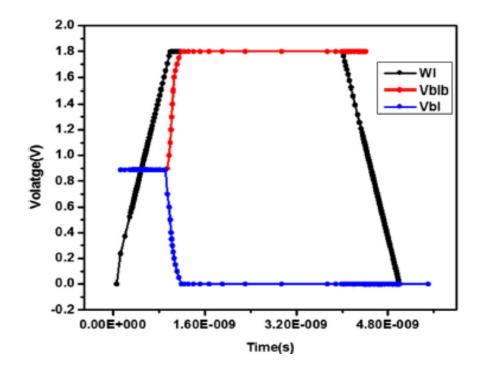

| 5.11 6T SRAM cell using dopingless AJ DG MOSFET101                                                |

| <b>5.12</b> (a) Hold state analysis of proposed 6T SRAM cell. (b) Read analysis of proposed 6T    |

| SRAM cell (c) Write analysis of proposed 6T SRAM cell 102 -103                                    |

| <b>5.13</b> Fabrication steps of Inverter105                                                      |

| 6.1 AJ DG MOSFET divided into three parts                                                         |

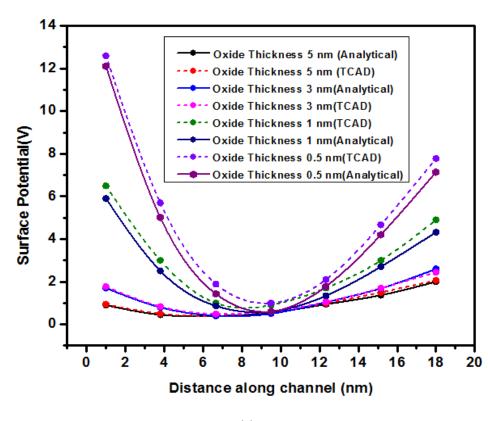

| 6.2 (a) Variation of Surface potential along the channel length for analytical model and          |

| TCAD simulation (b) Variation of surface potential along the channel length for                   |

| different gate oxide material SiO2 and HfO2 (c)Variation of surface potential along the           |

| channel length for different oxide thickness113-114                                               |

| <b>6.3</b> Equivalent capacitance model                                                           |

| <b>6.4</b> Variation of respect to gate voltage with respect to capacitance                       |

| <b>6.5</b> Variation of drain voltage with drain current                                          |

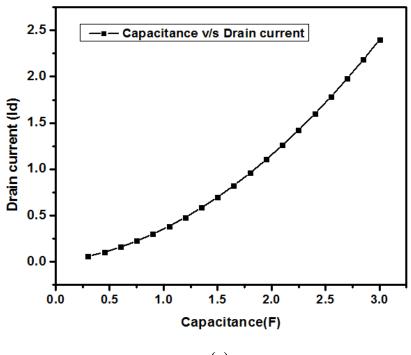

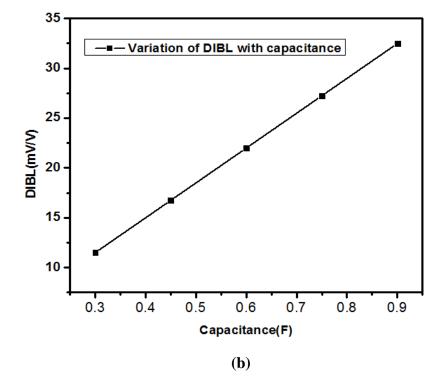

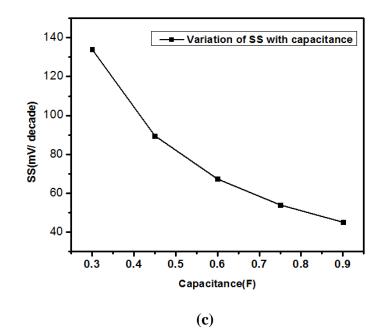

| <b>6.6</b> (a) Variation of capacitance with drain current (b) Variation of DIBL with capacitance |

| (c) Variation of SS with capacitance                                                              |

| · · · · · · · · · · · · · · · · · · ·                                                             |

# LIST OF ABBRIVATIONS

| MOSFET | Metal oxide field effective transistor  |

|--------|-----------------------------------------|

| SG     | Single gate                             |

| DG     | Double gate                             |

| SCE    | Short channel effect                    |

| SRAM   | Static random access memory             |

| 2-D    | 2-dimensional                           |

| 3-D    | 3-dimensional                           |

| SOI    | Silicon on inductor                     |

| CMOS   | Complementary metal-oxide semiconductor |

| GAA    | Gate all around                         |

| RF     | Radio Frequency                         |

| ТМ     | Triple material                         |

| DM     | Dual material                           |

| JL     | Junctionless                            |

| SS     | Subthreshold slope                      |

| DIBL   | Drain induced barrier lowering          |

| FET    | Field effective transistor              |

| AJ     | Asymmetrical junctionless               |

| DSBO   | Double step buried oxide                |

| BP     | Black phosphorus                        |

| RC     | Recessed channel                        |

| GC     | Graded channel                          |

### **CHAPTER 1**

### **INTRODUCTION**

#### 1.1 Evolution of VLSI

In 1947, the introduction of the bipolar transistor took place, the growth being very positive in the semiconductor industry with a social impact. Significant growth in the semiconductor industry in high-resolution (VLSI) integration technology is observed. And this huge growth in VLSI technology has led to the creation of smaller transistors in much smaller sizes. The advantages of having greater packing density, high rotation speed and , low power dispersion are important features of the evolutionary process, leading to the development of modern computers and high-performance communication systems, combined size at a much-reduced cost compared to the previous ones. Global investment in the semiconductor industry will continue as long as tangible terms will be agreed [1]. Bipolar transistor technology was developed in early 1947 and used in the first integrated circuit memory on mainframe computers in 1958. However, the severe power dissipation of bipolar circuits had significantly reduced their integration rate, by approximately 104 circuits per chip. MOSFET on a silicon substrate containing SiO<sub>2</sub> as a gate guard was developed Kahng and Atalla in 1960 [2]. During the 1960's and 1970's nchannel and p-channel MOSFETs were widely used along with bipolar transistors. In 1963, a major breakthrough in the integration phase occurred with the introduction of Complementary Metal Oxide Semiconductor (CMOS) technology by Wanlass and Sah 1963. Frank Wanlass patented CMOS in 1967. In CMOS architecture, both n-channel and p-channel MOSFETs are built together in the same substrate. Another feature of CMOS devices is their high noise protection. Since a single pairing transistor is always turned off, the series combination draws only a significant momentary moments during switching between opening and closing circuits (logical transition of the train line to the train)[3].

As a result, CMOS devices provide high packing density, fast rotation speed, low power dissipation and do not release much waste heat as other types of concepts do such as Transistor Transistor Logic (TTL) or NMOS logic. Therefore, CMOS technology is used to design microprocessors, microcontroller, static RAM and other digital logic circuits. Finally a single transistor DRAM (Dynamic Random Access Memory) cell and microprocessor were developed in 1968 and 1971 respectively. The emergence of VLSI applications occurred in the 1980's .For more than two decades of uninterrupted measurement, CMOS technology has become an existing technology for Very Large Scale Integration (VLSI) applications. These advances have led to more efficient computers and networks and lower costs per capita. Even more significant is the speed at which the reduction of the transistor size is used in order to obtain more instructions for improving performance and reducing costs.

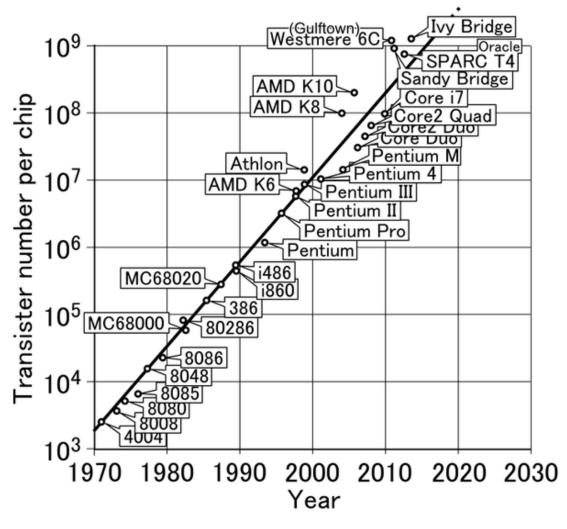

### 1.2 Moore's law

The law was coined by Intel founder Gordon E. Moore, who described the trend of the number of transistors in integrated circuits compared to the launch year. Moore in 1965 "stated that the amount of units in IC doubled a year from the establishment of an integrated circuit in 1958 until 1965 and predicted that this trend would continue at least ten years"[4]. This doubling was based on 50-60 parts chips produced in 1965 compared to those produced in previous years. Moore in 1975 saw that their predictions proved to be incredibly accurate. However, they predicted that in the future the number of parts of each chip would need about two years to double rather than one year as shown in figure 1.1[5].

Figure 1.1: Moore's Law

#### **1.3 Basics of MOSFET**

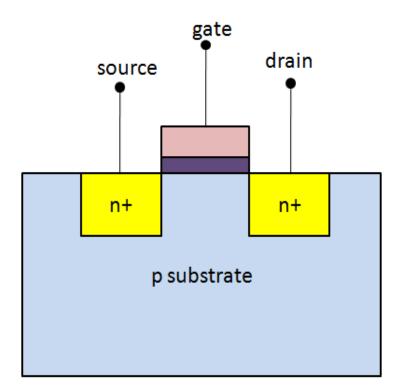

MOSFET (metal oxide field effective transistor) is a three terminal device having an insulated gate where voltage controls the flow of current in the device shown in figure 1.2. It is used for switching and amplification of electronic signals[6]. There are three different operation regions in MOSFET, the cut – off region, the triode or linear region and the saturation region. Cut-off region is used as switch OFF. In this region the voltage of gate to source ( $V_{gs}$ ) is always below than the threshold voltage of the device ( $V_{th}$ ) and current does not flows in this region between Drain to Source i.e.  $I_d = 0$ . Triode region is used for

switching ON . The voltage of gate – source  $V_{gs}$  is above the threshold voltage  $V_{th}$  and voltage between drain to source  $V_{ds}$  is less than the saturation voltage. The current flows from drain to source in this region. Saturation region is used in Amplifier. When the voltage between drain to source is increased and we meet a point on the graph  $V_{ds} > V_{gs} - V_{th}$  which is called saturation region and the current does not depends on  $V_{ds}$  [2].

Figure 1.2 : Single gate MOSFET

#### 1.4 Basic operating principle of MOSFET

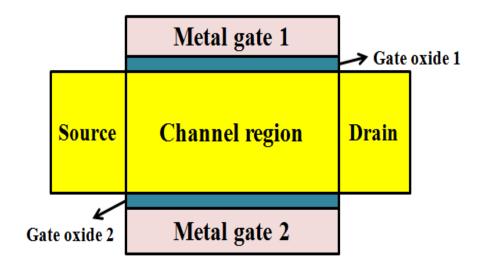

When positive voltage at the gate terminal is applied, the minority charge carriers (electrons) present in the P substrate is attracted towards the gate and gets accumulated on the gate contact which forms a conductive bridge between the two n+ regions known as channel [7]. Depending upon the strength of the gate voltage applied the number of free electrons accumulates at the gate contact. If the applied voltage is higher the width of

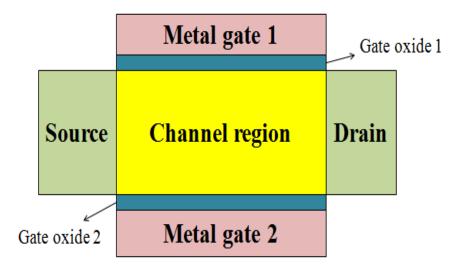

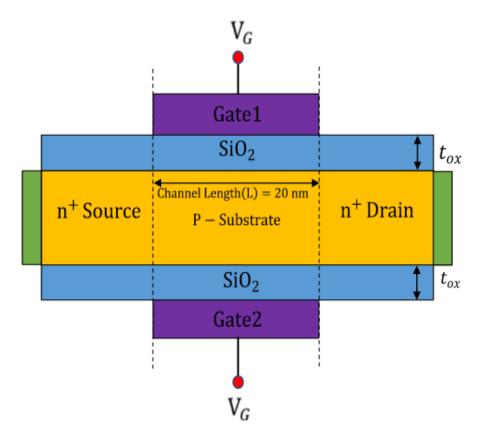

the n-channel formed due to electron accumulation is also greater, therefore the conductivity of the device increases eventually and the drain current  $(I_D)$  starts to flowing between the source and drain. In DG MOSFET two gates are used to control the channel from both sides[8].

#### 1.5 Need and challenges

Reduction in the size of the MOSFETs is one of the biggest challenges in IC technology[3]. Scaling of the device is important for integrating more number of transistors in a single chip. MOSFET scaling gives rise to short channel effects (SCEs) that degrades the performance of the MOSFET[4,5]. Single gate or conventional MOSFET does not works when the channel is short. MOSFET scaling decreases the size of  $SiO_2$  to few nm, further reduction in size of  $SiO_2$  is not feasible causing current leakage. There is the need to replace the oxide with high K material having more physical thickness[6]. Methods like channel & gate engineering are implemented to make changes in the structure for decreasing short channel effects (SCEs)[9-15]. An example of gate engineering technique is double gate MOSFET (DG MOSFET) which is one of the techniques for reducing SCEs .The gate to channel coupling is increased, control of gate over the channel gets better in DG MOSFET[16]. Current leakage due to OFF-state is minimized and also provides good mobility. The gates on both sides of the channel region of DG MOSFET controls the electric field and also provides a better subthreshold slope[17]. Hence, improving the performance of the device. Changing the gate contact material from metal to polysilicon also enhances MOSFET performance[18]. MOSFET has applications in various fields like biotechnology as a biosensor for detecting molecules and enzymes, memory application like SRAM cell, low power applications in digital circuits for switching[19-25].

This reduction in device size is important to integrate the maximum amount of devices into Integrated Circuits (ICs). The IC industry adheres to the Moore's Law to date. Today, the semiconductor industry also follows a road map provided by the International Technology Roadmap for Semiconductor (ITRS) predicting future device sizes and the number of transistors in the IC based on Moore's law.

As a result of Moore's law, each year the length of the MOSFET channel decreases, resulting in Short Channel Effect (SCEs). SCEs affect the power consumption of circuits. Transistor measurement target has been achieved due to improved lithographic ability to create a shorter / smaller channel. Initially, measurement was possible with conventional structures and material technology, but it is understandable that standard measurement technology could not continue indefinitely. Therefore, the investigation of non-antique device properties has been necessary. As the size of the transistors is reduced, the control of the gate electrode to the power flow in the channel area decreases due to the close proximity between — source and —gate. A major problem related to the short channel effect is the reduction of the channel junction of the channel. Reduced gate control reduces fence transmission. Transconductance of a device is very important in its analog use. In the short-term device and transconductance, lowering the water-causing barrier, ballistic transmission by Short Channel Effects (SCEs) can affect device performance. The solution to all the problems lies in increasing the network connection between the gate and the station and the reduction of the electrical connection between the source / trash and the station. Normally, different effects of six short channels can be divided into Drain Induced Barrier Lowering (DIBL), Hot Electron Effect, Punch through Velocity Saturation, Impact Ionization, Surface scattering and Threshold voltage roll-off. As SCEs impose restrictions on device performance and performance of the device deteriorates, these effects should be suppressed or removed, so that a device with a relatively short channel length can maintain the necessary features of the device. Researchers have attempted to overcome these problems by reducing the oxide thickness of the gate and the depth of the spring / water source cross while lowering the gate length to normal MOSFETs. But this measurement has reached a body size limit. As a remedy, high-density dielectric gate materials were used. The use of these high-k materials as gate oxide allowed to achieve an equal thickness of oxide with a larger body size. But declining MOSFET at a sub 10 nm scale is challenging and new technologies were

needed. As per the ITRS predictions and published literature, it is understood that the main research was carried out in two different ways: the possible modification of the layout structure and the use of random 3D structure [26] to push its physical boundaries, or a new way of making transistors using nanomaterials and nanotechnologies such as silicon nanowires, carbon nanotubes or graphene, single electron transistors, and other emerging tools such as quantum cellular automata and spin-based electronics [27]

Figure 1.3 : Double gate (DG) MOSFET

#### 1.6 Effects of MOSFET Scaling

#### **1.6.1 Short channel Effects**[26][31]

- 1. Drain induced barrier lowering (DIBL)

- 2. Channel Length Modulation (CLM)

- 3. Punchthrough

- 4. Channel scattering

- 5. Velocity saturation

- 6. Hot carrier effect (HCE)

- 7. Impact ionization

- 8. Source/Drain parasitic resistance/capacitances

- 9. Mobility degradation

- 10. Gate to source/drain charge sharing

- 11. Fringing field effects

#### **Drain-induced barrier lowering (DIBL)**

DIBL (drain-induced barrier lowering) is a SCE in MOSFETs that indicates a reduction in the transistor's threshold voltage with increasing drain voltages. The channel's potential energy barrier for electrons is decreased. The drain induced barrier lowering (DIBL) happens when the gate length is lowered without the other dimensions being suitably scaled. At first look, the current stream in the channel is depends on creation and control of inversion layer. The electrons that are the carriers in the channel faces a potential barrier that obstructs the stream if the gate predisposition voltage is insufficient to change the surface (Vgs>Vth). The gate voltagewhen increased, lowers the potential barrier and, in the long term, allows the carrier stream effected by the channel electric field.

In a small size MOSFETs , the potential barrier is controlled as voltage between gate to source Vgs & voltage between drain-source Vds. As the drain voltage increases, the potential barrier becomes Channels are shrinking. Reduce potential barriers in the long run allows carriers (electrons) to enter the channel from the source. Generates an increase in drain current. This effect is kmown as drain induced barrier lowering.

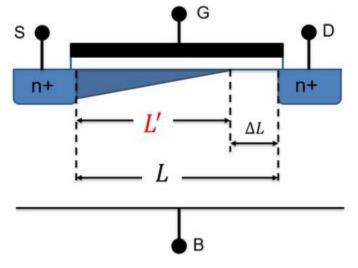

#### **Channel Length Modulation (CLM)**

Channel Length Modulation (CLM) is to decrease the length of the inverted channel region while increasing the drain offset for large drain offsets. The result of CLM is that when the drain is biased, the current increases and the output impedance decreases. Channel length modulation in MOSFETs occurs due to an increase in the drain depletion layer width as the drain voltage increases as shown in figure 1.4. This shortens the channel length and increases the drain current. The effectiveness of channel length modulation is generally increased in small devices with few doped substrates. Proper

scaling can reduce channel length modulation, i.e. increasing doping density with decreasing gate length.

**Figure 1.4 : Channel Length Modulation**

#### Punchthrough

In a MOSFET, punchthrough is a case of channel length modulation in which the the drain and source are surrounded by depletion layer and converge into a single depletion zone. The field beneath the gate is then found to be strongly influenced by the drain source voltage. The drain surrounded by depletion zones stretch out to the source, the two depletion layers consolidate (XdS + XdD = L) into a single depletion region, punchthrough occurs. More thinner oxides, larger substrate doping, shallower intersections, and channels with longer length can reduce punchthrough. The field, as well as the depletion current beneath the gate, is then completely dependent on the voltage between drain to source.

#### **Channel scattering**

The impacting framework's scattering channel is a quantum situation that exists before or after the collision. The longitudinal electric field portion Ey increases as the channel length decreases due to the lateral expansion of the depletion layer into the channel region. Surface mobility evolves in this direction, becoming field-subordinate. Channel scattering occurs as a result of the collisions that electrons meet when they are accelerated toward the interface by field Ex. When compared to mass mobility, this results in less normal surface mobility.

#### **Velocity saturation**

The highest velocity attained by a charge carrier in a semiconductor, usually an electron, in the presence of extremely strong electric fields is known as saturation velocity. The semiconductor is considered to be in a condition of velocity saturation when this happens. When the dimensions of short-channel devices are scaled without lowering the bias voltages, the device performance degrades, resulting in a reduction in transconductance in the saturation state. The electron drift velocity in the channel is directly proportional to the electric field intensity at low Ey. However, when Ey rises over 104 V/cm, the drift velocity slows and eventually reaches a saturation value of  $107 \ cm/s$  about y = 105 V/cm at 300 K. As a result, the drain current is reduced.

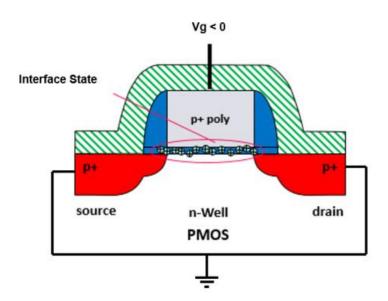

Hot carrier effect (HCE)

**Figure 1.5: Hot Carrier Effect**

Another issue associated with strong electric fields is the presence of so-called hot electrons as shown in figure 1.5 [31]. This high-energy electrons can penetrate the oxide and become stuck, resulting in oxide charging, which can damage performance of the device by raising Vth and negatively affecting the gate's control over the drain current. The highest electric field encountered by the carriers present in the channel area towards the end of drain increases when the channel length L, is lowered while the voltage between drain to source remains constant. As the carriers travel from the source to the drain, they accumulate enough kinetic energy in the drain junction's high electric field area to generate impact ionization. Some of them penetrate the oxide after crossing the Si-SiO2 contact. Because they are not in thermal equilibrium with the lattice and have energy greater than thermal energy, these high energy carriers are called as hot carriers (kT). The Channel Hot Carrier Effect is caused by the strong electric field experienced by the carriers from the channel during normal MOSFET operation. The device's performance is harmed when the threshold voltage, Vth, rises, affecting the gate's control over the drain current.

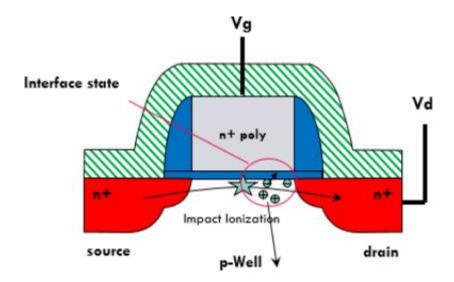

#### **Impact ionization**

A primary hot carrier forms a secondary electron-hole pair during impact ionisation shown in figure 1.6 [31]. While the drain current is made up of both primary & secondary electrons in the case of n MOSFET, the secondary holes created by impact ionisation migrate onto the substrate, resulting in the substrate current Ib. The Ib value regulates the heating of channel carriers as well as the electric field in the drain zone. A low Ib number has no negative consequences. However, if the substrate current, Ib, grows too high, the circuit will fail.

**Figure 1.6: Impact Ionization**

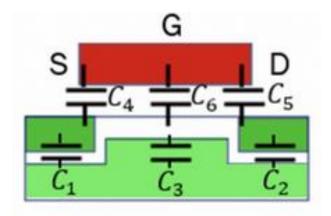

#### Source/Drain parasitic resistance/capacitances

A MOSFET's source/drain junction is a parasitic component. Resistance and capacitances (S/D pn junction capacitances and gate-to-source/drain overlap capacitances) are present in these junctions as shown in figure 1.7 [25]. These parasitic components (resistance and capacitances) limit the device's driving capabilities and switching speed and should thus be avoided.

Figure 1.7: Source/ Drain parasitic capacitances

#### **Mobility degradation**

Both lateral field Ey (drain voltage) and normal field Ex cause mobility deterioration (gate voltage). As carriers in the channel travel which are influenced by lateral field caused by the drain voltage and normal field caused by the gate voltage, they experience greater dispersion as the fields grow. The reason for this is that the normal field functions in such a way that it accelerates charge carriers towards the surface, causing carriers to disperse more often than in the absence of a gate field The lateral field, on the other hand, causes charge carriers to travel faster, to the point where carriers become velocity saturated at high voltage between drain to source. The device current is more affected by lateral field mobility degradation than by normal field mobility degradation. This is because an increase in the lateral field eventually leads the carriers' velocity to be saturated.

#### **Fringing field effects**

The gate overlaps the source and drain areas when the device length and breadth are lowered. Electric field lines grow thick along the channel's side walls as a result of this overlapping. The charge at the channel's borders is effectively increased by these fringing field lines, which has a significant impact on device properties. Ferry calls this phenomena the fringing field effect (1988). Fringing field lines can be seen in a crosssectional picture of a short channel MOSFET.

#### Gate to source/drain charge sharing

The absolute value of the threshold voltage drops as the channel length decreases due to the gate's poorer controllability over the channel depletion zone induced by increasing charge sharing from source/drain. SCE is distinguished by the absence of pinch-off and a threshold shift with decrease in channel length at increased drain voltage. Increase in charge sharing from the source/drain reduces gate voltage controllability over the channel. This deterioration is represented as charge sharing by the electric fields of the gate and drain in the channel depletion layer, which was the first SCE model disclosed.

#### **1.7 Importance of High K Dielectric** [27]

- Thinner gate oxides are increasingly required for nanoscale devices as device dimensions continue to shrink for high performance and low power operation.A good solution to this problem is to use double gate MOSFETs with a high dielectric.

- MOSFETs have a greater gate capacitance and are more suitable than pure SiO2

DG MOSFETs because of the higher dielectric constant.

- Reduced Current Leakage

#### 1.8 Reasons for selecting DG MOSFET

The double gate MOSFET was chosen to efficiently regulate the Si channel. The DG MOSFET has superior control over the three critical variables listed below.

- Threshold voltage roll-off and

- Short channel effects (SCE)

- Drain induced barrier lowering (DIBL)

In comparison to SG MOSFETs, the DG MOSFET has a lower subthreshold swing. All of these factors contribute to the decision to choose a double gate MOSFET.

#### **1.9 Different MOSFET structures and Applications**

New architectures, such as double gate MOSFETs, tri-gate MOSFETs, and multigate MOSFETs[28], have been devised to compensate for SCEs, as illustrated in figure 1.8[28]. These MOSFETs were developed as a replacement for bulk MOSFETs with channel lengths more than 45nm. The advantages of a double gate MOSFET over a bulk MOSFET are numerous[29,30]. Short channel effects, junction capacitance, and dielectric isolation are all reduced. SOI (silicon on insulator) is also employed in CMOS technology[31] because of its fast speed and low power consumption. For improved control of short channel effects, DG MOSFETs were employed to create amplifiers[34]. The linearity and analogue performance of TM DG SOI MOSFETs are improved[36]. The square GAA MOSFET was created for device simulators and may be readily integrated into tiny models [34]. MOSFETs with surrounding gates have a wider channel, which improves the driving current[35]. For the enhancement of short channel effects, a capacitance model of material tailored CGT has also been proposed[35]. CSDG MOSFETs were developed to store more energy and increase current flow from source to drain[38]. JL DG MOSFETs are developed to provide good RF performance. Various structures for like multi channel FINFET and multi channel GAA are developed for further improvement in different performance parameters of the device.

(a) Junctionless DG MOSFET

(b) SOI MOSFET

#### (d) TM DG MOSFET

**Figure 1.8 : Different advanced MOSFET Structures**

#### **1.10 Motivation for Research work**

The planar bulk MOSFET structure needs be changed in order to maintain device growth without incurring OFF state leakage current while also attaining increased performance. New device designs are required to give improved gate controllability and reduced short-channel effects (SCEs). Researchers are primarily attempting to tackle the challenges listed above in two ways: I multi-gate architectures for improved gate controllability and larger ON current at constant over-drive voltage, and (ii) channel materials with enhanced carrier mobility. Both solutions were used in this study to minimise SCEs and improve analog/RF performance.

Many advantages of Junctionless MOSFETs over traditional devices have been noted, including increased protection against Short Channel Effects (SCEs), superior scalability, and enhanced drain-induced barrier lowering (DIBL). FinFETs have already surpassed planar MOSFETs as the most popular option at or below the 22-nm technology node due to their lower Short Channel Effects (SCEs) and superior gate controllability[38]. In compared to planar devices, they also have a larger  $I_{ON}/I_{OFF}$  current ratio and a higher driving current per unit area. FinFET device structure fabrication is relatively simple and compatible with traditional CMOS technology.

Lower channel doping is desirable for junctionless MOSFETs in order to produce an appropriate threshold voltage (Vth), low SS, and greater ION/IOFF. Lower channel doping, on the other hand, increases undesired source/drain series resistances. In junctionless FinFETs, an extra doping density in the source and drain regions is used as a solution. Junctionless Accumulation Mode FinFETs have greater doping concentrations in the source and drain regions than in the channel regions and operate in accumulation mode [38]. In compared to SOI FinFETs, FinFETs produced on bulk silicon have higher heat dissipation capabilities, reduced defect density, and cheaper wafer cost. Bulk-FinFETs also aid in the elimination of the floating body effect. As a result, junctionless accumulation mode bulk FinFETs have been a hot issue in current research [39]. High mobility channel materials are being studied for greater driving current and transconductance than Si-based counterparts [40]. By altering the Indium mole percentage of the compound semiconductor, InGaAs-based channel materials provide further advantages in terms of tuneable bandgap [41]. Using an appropriate barrier layer, higher electron mobility and performance can be achieved [42].

As a result, it is critical to analyse and investigate the performance of InGaAs/InP material based MOSFETs with variable barrier layer characteristics and channel composition. When employed in a System of Chip (SoC), analogue and RF circuits of a digital CMOS technology present several obstacles. Device optimization gets more difficult with System on Chip (SoC). As a result, device structure must be investigated in order to improve device performance for digital and analog/RF circuit applications.

The proposed work is focused on the study and design of emerging nanoscale junctionless MOSFETs and their applications, based on the literature review. Different SCEs of the devices under study are investigated in detail, including DIBL, Subthreshold Slope (SS), digital performance parameters such as  $I_{ON}/I_{OFF}$ .

#### **1.11 Performance parameters of MOSFET**

The performance of different MOSFET structures are based on their ON and OFFstate performance. The deciding factor in further scaling of new MOSFET structures is the ON and OFF state performance. The important transistor performance parameters are as follows:

#### **Surface potential**

The difference between the voltage of the MOSFET top layer of polysilicon / metal above the oxide and the voltage in the bulk of the MOSFET is the surface potential of the MOSFET. It is important for determining the gate to source threshold voltage.

#### **ON-state current**

When the gate voltage surpasses the threshold voltage, the MOSFET enters the ON state. As a result, when current flows in this condition, it is referred to as ON current, indicated by the symbol Ion, with electrons flowing from source to drain

#### **OFF-state current**

The MOSFET is in the OFF state when the threshold voltage is more than the gate voltage. However, there is current flow in the OFF state due to minority charge carriers between the drain and source. Subthreshold current is the name given to this type of current.

#### **DIBL** (drain induced barrier lowering)

The barrier between the source and channel is reduced when the drain voltage is increased, and electrons flow from source to channel. When the drain bias is raised, the depletion area under the channel expands, lowering the threshold voltage.

$$DIBL = \frac{V_{Th}^{DD} - V_{Th}^{low}}{V_{DD} - V_{D}^{low}}$$

#### Subthreshold slope

Subthreshold slope is a SCE that occurs in the subthreshold region due to current leakage. SS is calculated as the slope of the gate voltage and drain current during the subthreshold

$$zone.ss = \frac{dV_{gs}}{d(logI_{d})}$$

#### Transconductance

In a FET, transconductance is the ratio of change in drain current to change in gate voltage during a short time interval in the drain current vs gate voltage curve. It is denoted as gm.

$$g_m = \frac{2 I_{DSS}}{|V_P|} \left(1 - \frac{V_{GS}}{V_P}\right)$$

#### Junction capacitance

Junction capacitances form in MOSFETs due to charge depletion between the source/drain and the substrate. Depending on the source/drain voltage, the charged depletion changes. The creation of a channel at the surface occurs when the gate voltage surpasses the threshold value.

#### **Stability factor**

The stability factor (K) is primarily determined by MOS transistors' two-port equivalent circuit characteristics. It determines whether transistors are conditionally or unconditionally stable in the RF frequency spectrum. The stability factor is calculated as follows:

$$\mathbf{K} = \frac{2 \, Re[Y_{11}] Re[Y_{22}] + Re[Y_{12}Y_{21}]}{|Y_{12}Y_{21}|}$$

At port 1 and 2,  $Y_{11}$  and  $Y_{22}$  are the input and output admittance parameters, respectively. Transfer admittances are referred to as the  $Y_{12}$  and  $Y_{21}$ .

#### **Critical frequency**

For a small signal transistor model, as well as maintaining an acceptable AC transistor gain and frequency bandwidth, the critical frequency (fk) is crucial. The critical frequency may be calculated with a stability factor of K = 1. MOSFET capacitance (Cgs, Cgd, and Cds, ) and other parasitic capacitances are the main determinants of critical frequency. The critical frequency is denoted by the following:

$$f_k = \frac{f_T N}{\sqrt{g_{ds}g_m R_{gs} M^2 + NM(g_m R_{gd} + 1)}}$$

fT, gds, Rds, and Rgs are the frequencies at unity gain, output conductance, drain to source, and gate to source resistances, respectively. Additionally, the M and N values are given in Cgs and Cgd, respectively.

#### **1.12 TCAD** Simulating Tool

TCAD (Technology Computer Aided Design) is an effective method for reducing plan costs, enhancing device design efficiency, and developing superior device and innovation designs. While the cost of building a cutting-edge manufacturing plant continues to climb, owing to Moore's law and subsequent advances in execution, identifying the power has become a comparatively low-cost component. The simulations are used to anticipate the electrical properties of a device design rapidly and affordably, instead of an expensive and time taking process of production. If the display is prepared and the fabrication procedure can be recreated, physical properties like as oxide thickness and doping distribution may be delivered with great precision. Device modeling and simulation describes the electrical characteristics of a certain device architecture. TCAD has a number of advantages, one of which is that it can help you understand the working of semiconductor devices. Evaluation of specific device function, including the change of energy levels and carrier (electrons and holes) with biasing circumstances, can give useful insight into the link between changes in process conditions or device plan and their impact on device execution. On a speculative basis, these figures are usually impossible to get.

#### 1.13 Gate and channel engineering

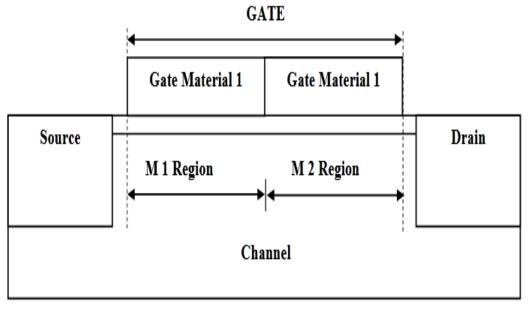

# 1.13.1 Gate Engineering

As device functioning is imbalanced at short gate lengths even with low drain bias, a standard MOS structure will ultimately hit its scaling limit, resulting in Drain Induced Barrier Lowering (DIBL)& (CLM). Asymmetric MOSFET architectures have been presented as a way to overcome the drawbacks in transportation productivity and SCE's (Buti 1989, Chen 1998, Hiroki 1995, Horiuchi 1994, Long 1997 and Zhou 1998). The basic idea behind an asymmetric MOSFET is to change the channel electric-field profile such that it is bigger at the source side to accelerate carriers and smaller at the drain side to reduce short-channel and hot-carrier effects as compared to a symmetric MOSFET. The following are examples of asymmetric MOSFET structures:

- Asymmetric channel doping by Hiroki in 1995 and Kaur in 2007,

- Asymmetric halo source (HS) by Buti in 1989,

- Asymmetric sidewall by Horiuchi in 1994,

- Asymmetric S/D implant by Chen in 1998 and

- Dual-Material-Gate (DMGFET) by Long in 1997, Long in 1999 and Zhou in 1998.

Unlike asymmetric structures with doping engineering given by Buti in 1989, Chen in 1998, Hiroki in 1995, and Horiuchi in 1994, where the channel field distribution is continuous, dual-material gate engineering by Long and Zhou in 1998 introduces a field discontinuity along the channel, resulting in simultaneous transport enhancement and SCE suppression. The gate metal of the Dual Material Gate electrode (DMG) design, as shown in Figure 1.5, is made up of two different materials. The one next to the source

side (M1) has a longer length, L1, and a more noticeable work function, m1, than the other gate's workfunction, m2, which is close to the drain end and has a shorter length, L2 (M2). Unless otherwise stated, the L1 and L2 are maintained equal. The control gate is located at the source end, whereas the screen gate is located near the drain end. When compared to the drain region, the workfunction contrast causes an electric field peak in the channel, resulting in an increase in electric field near to the source area. As a result, the average electron velocity at the source area is substantially greater, which improves carrier transport efficacy and hence reduces the hot electron impact.

Figure 1.9 Dual material gate FET (DMGFET) structure

In figure 1.9 The DMGFET (dual material gate FET) construction that has been presented. In the case of n-channel FETs, Material 1's work function is bigger than Material 2's, resulting in a higher positive threshold voltage near the source. For p-channel FETs, a reversed configuration is required. MOSFET, MESFET, and HFET are examples of FETs by Long in 1997. The dual material gate electrode architecture's main principle is to add a step function into the channel potential profile, boosting the electric field

distribution present at source side for increasing carrier velocity while screening the drainpotential shift to avoid short channel effects .The screen gate protects the control gate from drain potential variations, which reduces channel length modulation and drain conductance. The drain current and transconductance are both raised when the carrier transport efficiency improves. As a result, considerable gains in device efficiency (gm/Ids) ), intrinsic gain (gm/gd), early voltage (Ids/gd), I<sub>ON</sub>/I<sub>OFF</sub>, and speed to power dissipation performance (gm-Ion) have been achieved. Various integration schemes are available for fabricating dual material gate architecture, including tilt angle evaporationmetal gate deposition , metal inter diffusion process, chemical mechanical polishing , and fully silicided (FUSI) metal gate fabrication. A poly-silicon gate doping approach is used to effectively create a dual material gate architecture by regulating the source and drain side gates separately. Another type of engineering strategy has been adopted to increase the carrier transport efficiency in the channel, better screening of the channel area from drain bias changes, and therefore enhancing the onstate driving current and DIBL reduction of traditional planar MOSFETs.

#### **1.13.2** Channel engineering

Under the 0.25 micrometre innovation hub, halo doping or a non-uniform channel profile in a parallel bearing was proposed as a new way to limit the dependency of the threshold voltage on channel length. Close to the source and drain implants, halo implants increase the doping. All of the most extremely p-type doped patches in n-channel MOSFETs are near to the channel's two ends. Asymmetrical or symmetrical implants at the source or drain are possible. They're usually added once the gate pattern is complete. Between the source drain junctions with the channel, the implants have a larger degree of impediment.

Channel engineering is in charge of managing the pocket implants or halo implants that are inserted in the channel to adjust the doping convergence and make it doped. Asymmetrical or symmetrical halo implants are available. The presence of halo implants in a MOSFET tends to lower the surface potential, resulting in an additional step up independent of the number of step-ups induced by channel engineered MOSFETs.

#### 1.14 Thesis Outline

In thesis different advanced structure and their applications are explained . Proposed structures with its detailed dimensions are analyzed in terms of  $I_{on}$  / $I_{off}$  current ratio, DIBL and SS .Sensitivity parameters are also analyzed. Different application in biotechnology as well as in low power circuits is designed . Analytical and capacitance modeling of the device is also derived.

**Chapter 1** explains the basics of MOSFET, its need and challenges, operating principle different advanced MOSFETs and performance parameter of MOSFET.

**Chapter 2** emphasizes that for the sub 45 nm technology node, many gate and channel developed advanced MOSFET architectures are evaluated and compared. The SS I<sub>ON</sub>/I<sub>OFF</sub> and DIBL values of several MOSFET architectures are compared.

**Chapter 3** explains about the designing of asymmetric gate junctionless MOSFET and its dimension .It also describes results obtained including the ON and OFF current of the device. The sensitivity characteristics of dopingless AJ DG MOSFETs, such as drain extension, gate overlapping length, and oxide thickness, were compared to those of AJ DG MOSFETs with doped channel regions.

**Chapter 4** explains the n+ pocket AJ DG MOSFET is analyzed by calculating  $I_{on}$  and  $I_{off}$  current .The dimensions of the device is mentioned in tabular form and also SCEs like DIBL and SS are also calculated .

**Chapter 5** discusses about the applications of asymmetric gate junctionless MOSFET. It describes results obtained for biomedical application and low power application of the proposed device.

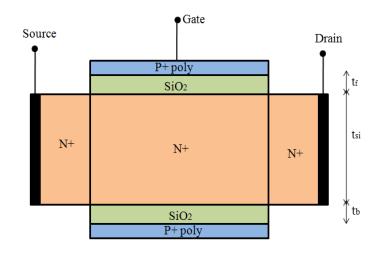

**Chapter 6** describes surface potential for proposed AJ DG MOSFET of channel length 18 nm and gate length is 11 nm is derived using solutions from 2D Poisson's equations. The proposed device is divided into three segments .The first and third part act as a single

gate MOSFET and the second part as double gate MOSFET. Surface potential for each segment is calculated and added . The capacitance model of the device is also derived. **Chapter 7** explains about the conclusion and future scope of the research work done.

# **CHAPTER 2**

# LITERATURE REVIEW

Several sophisticated MOSFET topologies are compared based on their ON and OFF state performance. The performance of innovative transistor designs in both the ON and OFF states will influence future scaling trends. Many applications, such as digital circuits, memory, analog/RF, and medicinal applications, have an impact on MOSFET structure design. To identify application-based MOSFET designs, the study investigates DC and AC performance measures. Using the circuit simulators in the TCAD software, many MOSFET designs are created to test circuit performance. This sort of transistor structure and circuit design analysis is essential for achieving the desired performance while minimising failure or defect in the produced sample.

Various advanced MOSFET architectures are explored and compared for the sub 45 nm technology node in this chapter. Performance characteristics such as ION/IOFF, subthreshold slope, and DIBL values are compared between the structures. Analog/RF performance is evaluated for transconductance, capacitances, and other factors. This chapter also discusses the many uses of MOSFET architectures in various fields.

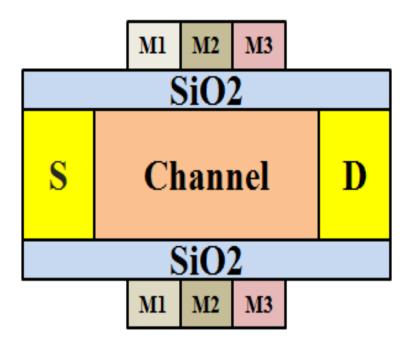

# 2.1 Effect of gate engineering on DG MOSFET

Sarkar et al.[52] submitted a study demonstrating the effect of gate engineering on DG MOSFETs in figure 2.1. The use of a completely depleted tri material DG MOSFET is considered. The DM DG MOSFET and SM DG MOSFET are evaluated in terms of RF performance, linearity, and analogue performance. The structure is designed using 35 nm CMOS technology. Varying gate materials with different work functions are taken into account in n-MOSFETs. M1 = 5.0 eV, M2 = 4.75 eV, and M3 = 4.5 eV are the work functions of the materials used. The gate material with the highest work function is positioned closest to the source, while the gate material with the lowest work function is placed closest to the drain. The Si layer = 10 nm thick, whereas SiO2 = 2 nm thick. The source and drain both have a dopant concentration of  $10^{20}$  cm<sup>-3</sup>. The length ratio of

three distinct materials is calculated as L1:L2: L3 = 1:1:0. The p substrate has a concentration of doping as  $10^{16} cm^{-3}$ .

Figure 2.1 : TM-DG MOSFET STRUCTURE

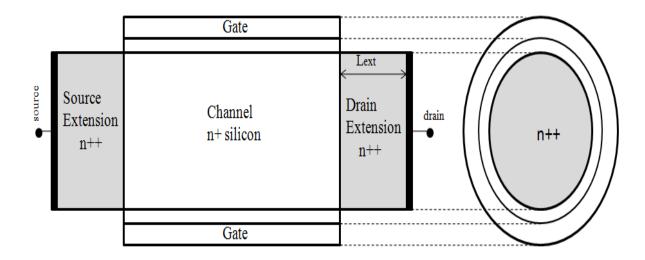

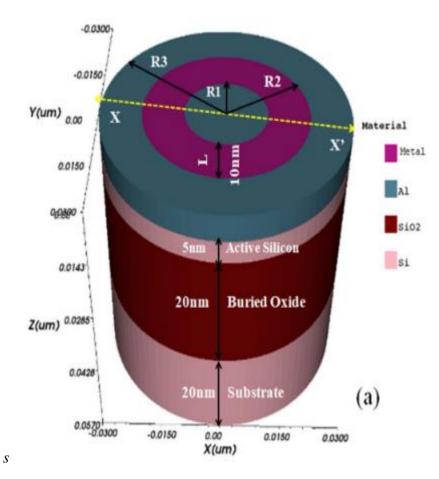

#### 2.2 Gate all around junctionless MOSFET having source/drain extension

F. Djeffal et al.[51] presented a gate-all-around junctionless MOSFET with source/drain extension for better analogue and RF performance, as illustrated in figure 2.2 [51]. The doping concentration of the source and drain extensions is higher in this architecture than the doping concentration of the channel. The doping concentration is indicated by the letters n++/n+/n++. Consider a lengthy channel with a silicon sheet thickness of less than 5nm. The doping concentration of the channel is  $10^{18} cm^{-3}$ , the concentration of both source and drain extension is  $10^{19} cm^{-3}$ , R is 5 nm, L is 100 nm,  $t_{ox}$  is 5nm. The drain current improves by addition of source /drain extension. The GAAJ MOSFET with extensions produces increased current compared to the conventional GAAJ. Therefore, Ion current magnitude increases by 70% with addition of the extensions.

Figure 2.2: GAAJ MOSFET with S/D extensions regions

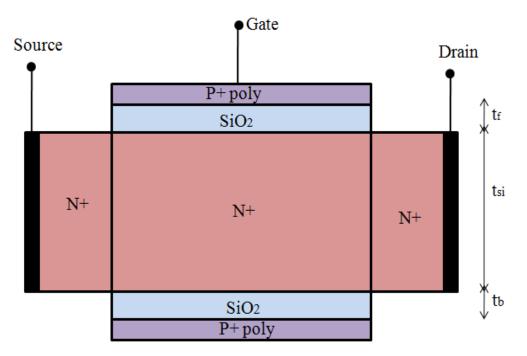

#### 2.3 Reliability of junctionless double gate (JLDG) MOSFET

Abhinav et al.[55] discussed the reliability concerns with junctionless double gate (JLDG) MOSFETs, as seen in figure 2.3. The effect of gate misalignment on the device's thermal stability between 200K and 500K is investigated. The current is reduced due to the gate misalignment, which deteriorates the JLDG MOSFET performance When the rear gate shifts towards the source or drain side, it causes misalignment. Non-ideal effects result from gate misalignment. The device's gate work function is 5.2 eV, the front and back gate oxide thicknesses are 1nm, the silicon substrate thickness is 5 nm, the channel, drain, and source doping concentrations are  $3 \times 10^{19} \text{ cm}^{-3}$  and the channel length L is 20 nm.

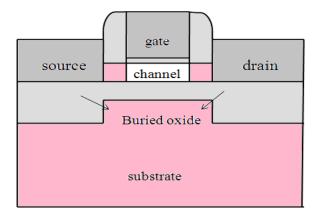

#### 2.4 A double step buried oxide (DSBO) SOI MOSFET

Figure 2.4 shows a DSBO SOI MOSFET developed by Ali A Ouruji et al. [57]. This design combines the benefits of both bulk MOSFETs and SOI MOSFETs. When the form of the buried oxide is modified to a double step shape, the self-heating effects are reduced, and the silicon dioxide thickness is reduced. Heat is easily transferred from the channel to the

substrate. As a result, despite the self-heating effects, the drain current increases. N + source & drain doping is  $10^{20} cm^{-3}$ , N+ source & drain extension doping is  $10^{19} cm^{-3}$ , silicon film doping for P type =  $10^{15} cm^{-3}$ , thickness of thin film = 10 nm, source & drain thickness = 50 nm, oxide thickness under the source/drain is 100 nm, oxide thickness under the channel = 20 nm, channel length = 30 nm, gate oxide thickness = 1.5 nm

Figure 2.3 :Schematic diagram of n-type JLDG MOSFET

Figure 2.4 :Schematic cross-sectional view of DSBO-SOI structures

# 2.5 Gate underlap junctionless double gate MOSFET (JL DG MOSFET)

Figures 2.6 and 2.7 show two types of gate underlap JL DG MOSFET suggested by Ajay et al.[58]. The gate underlap region, lying at the end of the source region, is the first example. The gate underlap area is located at the drain end of the JL DG MOSFETS channel region in the second scenario. Using the dielectric modulation approach, these types of structures are employed to detect bio molecules. The surface potential of the JL DG MOSFET is affected by the charged biomolecules. When biomolecules are charged positively, their surface potential rises, and when they are charged negatively, their surface potential falls.

# Figure 2.5 : The gate underlap region is considered at the source end of the channel region of JL DG MOSFET.

The gate length = 50 nm, the cavity length = 50 nm, the cavity thickness is = 19 nm, the channel thickness = 20 nm, the gate oxide thickness = 10 nm, the doping in the source & drain and channel is  $1 \times 10^{24}$  cm<sup>-3</sup>, and the oxide layer thickness in the open cavity area = 1 nm.

Figure 2.6 :When the gate underlap region is considered at the drain end of the channel region of JL DG MOSFET.

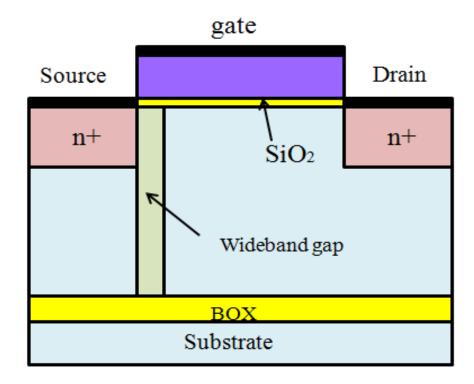

# 2.6 Silicon based MOSFET

Ikhyeon Kwon et al.[59] submitted a study on silicon-based MOSFETs to improve the device's operation at high temperatures, as illustrated in figure 2.8. This MOSFET is built to withstand the harshest of environments. Local insertion of large band gap material between the source and the channel area is done for high temperature operation. Furthermore, the suggested device is based on an SOI MOSFET structure with buried oxide (BOX) to prevent leakage current from passing through the substrate. The device features a gate length of 100 nanometers, a gate oxide thickness of 3 nanometers, a bottom oxide thickness of 10 nanometers, a barrier width of 10 nanometers, and a barrier depth of 75 nanometers. Source/drain and substrate doping concentrations are  $1 \times 10^{20}$  cm<sup>-3</sup> and  $1 \times 10^{17}$  cm<sup>-3</sup>, respectively.

Figure 2.8: Silicon based MOSFET for high temperature operation

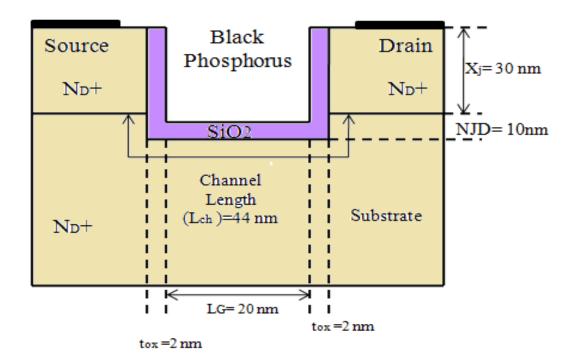

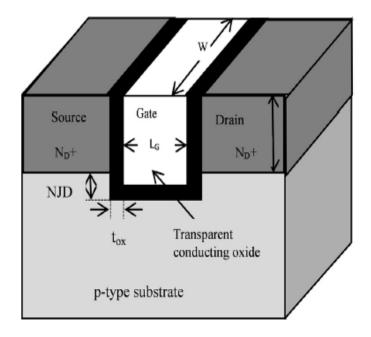

#### 2.7 Black phosphorus junctionless recessed channel MOSFET

Figure 2.9 shows a black phosphorus junctionless recessed channel MOSFET built by Ajay Kumar et al. [60] for use in RF applications using 45 nm technology. The junctionless recessed MOSFET is integrated with black phosphorus. The drain current may be increased by up to 0.3 mA using this arrangement. Off current is suppressed, and the SS improved . BP material has a strong ON current and a low OFF current. The gate length = 20 nm, the length of the drain and source region = 30 nm, the device width = 200 nm, the depth of the groove = 38 nm, the length of the channel is = 44 nm, the doping concentration of the drain & source is  $5x10^{16}cm^{-3}$ , the negative junction depth (NJD) = 10 nm, the voltage of the gate to source = 1.5 V, the thickness of physical oxide = 2 nm, the work

Figure 2.8: Design of BP JL RC MOSFET

# 2.8 Dual material surrounding gate (DMSG) MOSFET

Figure 2.10 shows the implementation of a 10 nm dual material surrounding gate (DMSG) MOSFET for digital applications by F. Djeffal et al.[51]. The benefits of 50 nm technology and the multi – objective genetic algorithms (MOGAs) optimization approach are merged in the DMSG MOSFET. The electrical behaviour of a 10 nm DMSG MOSFET is adjusted and enhanced using the MOGAs technique. The gadget, which is employed in nanoscale digital applications, has a low power consumption and a fast speed. The doping concentration  $N_A = 10^{15} \text{ cm}^{-3}$ , the drain and source doping concentrations =  $10^{20} \text{ cm}^{-3}$ , the channel length L = 10 nm, the oxide thickness = 2 nm, the silicon thickness = 10 nm, and the lengths L1 and L2 are L/2.

Figure 2.9: Structure of DMSG MOSFET

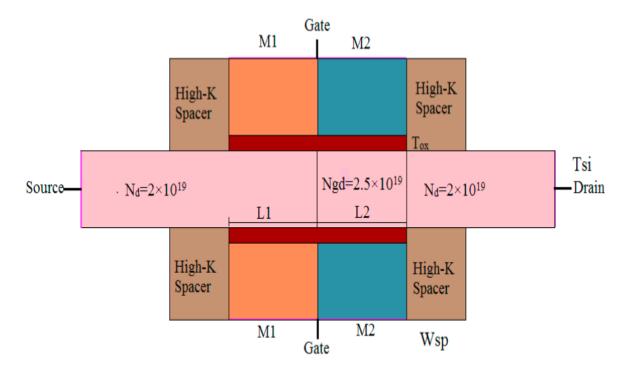

#### 2.9 Graded channel dual material gate junctionless (GC – DMGJL) MOSFET

Figure 2.11 shows the implementation of a graded channel dual material gate junctionless (GC – DMGJL) MOSFET for analogue applications by Varsha Pathak et al. [61]. The performance of GC – DMGJL and uniform channel dual material gate junctionless (UC – DMGJL) MOSFETs is compared. The GC – DMGJL MOSFET achieves a high drain current while simultaneously lowering SCEs. The device has a high doping concentration of  $N_{gd}$ = 2.5x10<sup>19</sup> cm<sup>-3</sup> near the channel's drain region, and a uniform doping concentration of  $N_{d}$ = 2x10<sup>19</sup> cm<sup>-3</sup> in the remaining regions . L (M1 ):L (M2)is a metal length ratio of 15:15. W (M1):W (M2) = 5.353:4.8 is the ratio of the metal's work function. The thickness of the oxide is estimated to be 2 *nm*.  $W_{sp}$ = 10 *nm* is the length of the spacer.  $T_{si}$ = 10 *nm* is the thickness of silicon.

Figure 2.10 : Structure of GC-DMGJL MOSFET

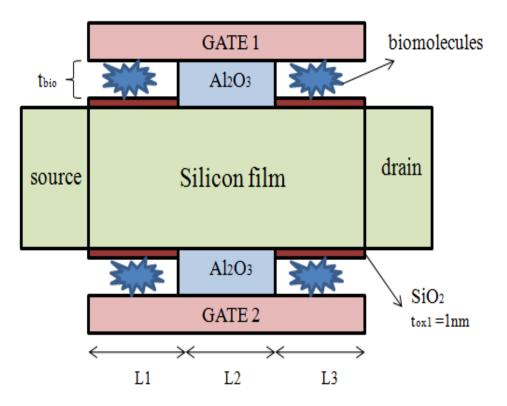

#### 2.10 Junctionless MOSFET structure for detecting biomolecules

Using the dielectric modulation approach illustrated in figure 2.12, Ajay et al.[62] constructed a junctionless metal oxide semiconductor field effective transistor structure that detects biomolecules such as DNA, enzymes, cells, and so on. A nanogap cavity is created by gate oxide etching from both the source & drain sides of the channel. The biomolecules that bonds to the SiO<sub>2</sub> layer present in the nanocavity impact the device's surface potential. The device's dimensions are  $t_{bio} = 9 nm$ ,  $t_{ox1} = 1 nm$ , and  $t_{si} = 10 nm$ , with a doping concentration of  $1 \times 10^{25} m^{-3}$  for the source, drain & channel. The lengths of the cavities L1 and L3 = 25 nm, while the length of the oxide Al<sub>2</sub> O<sub>3</sub> = 50 nm.

Figure 2.11: Junctionless MOSFET structure for detecting biomolecules

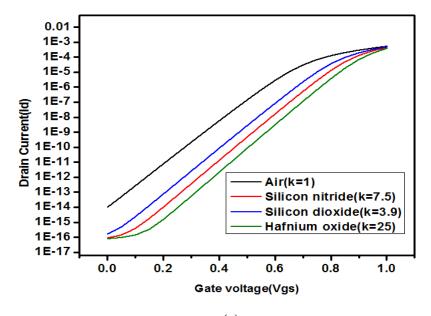

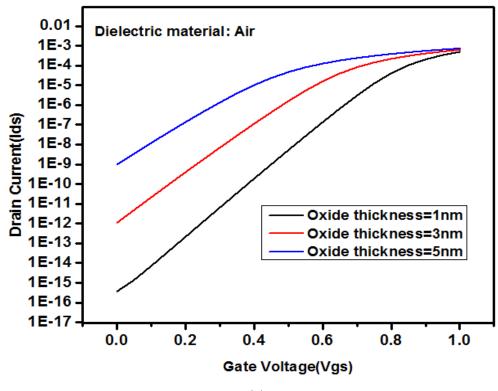

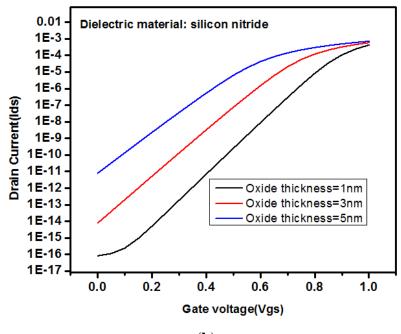

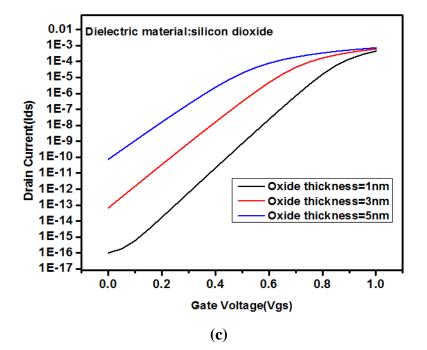

# 2.11 Pocket of n-MOSFET