# DESIGN AND OPTIMIZATION OF HETEROJUNCTION MULTIGATE FINFETS WITH PROCESS VARIATION.

Thesis Submitted For the Award of the Degree of

# **DOCTOR OF PHILOSOPHY**

in

Electronics and Communication Engineering

By

Shekhar Verma

41500192

Supervised By Dr. Suman Lata Tripathi

Transforming Education Transforming India

LOVELY PROFESSIONAL UNIVERSITY PUNJAB 2022

# DECLARATION

I declare that the thesis entitled "Design and Optimization of Heterojunction Multigate FinFETs with Process Variation" has been prepared by me under the guidance of Dr. Suman Lata Tripathi, Associate Professor, School of Electronics and Electrical Engineering at Lovely Professional University, Punjab, India. No part of this thesis has been included in or has formed the basis for the award of any Degree or Diploma or Fellowship of any institution or university anywhere previously.

I further declare that there is no falsification or manipulation in terms of research materials, equipment or processes, experiments, methods, models, modeling, data, data analysis, results or theoretical work.

I have checked the thesis using Turnitin for ensuring that there is no plagiarized material in my thesis and wherever any copyrighted material has been included, the same has been duly acknowledged.

Shekhar Verma School of Electronics and Electrical Engineering Lovely Faculty of Technology and Sciences Lovely Professional University Phagwara, -144411 (Punjab)

We endorse the above declaration of Ph.D. student

Date: 19<sup>th</sup> September 2022

(Signature of the Ph.D. Supervisor)

# CERTIFICATE

We certify that Shekhar Verma has prepared his thesis entitled "Design and Optimization of Heterojunction Multigate FinFETs with Process Variation", for the award of the Ph.D. degree of the Lovely Professional University, under our guidance. He has carried out the work at the School of Electronics and Electrical Engineering, Lovely Professional University.

Dr. Suman Lata Tripathi Associate Professor School of Electronics and Electrical Engineering Lovely Faculty of Technology and Sciences Lovely Professional University, Phagwara, Kapurthala-144411 (Punjab)

## ABSTRACT

Expeditious magnification and Inception of FinFET mechanization has inculcated new paradigms in the vertical of Nanotechnology. It can be defined through feigning for FinFET that it may be spanned down to almost 10 nm. Though the synthesis of ultrathin fin may trigger the short channel repercussions. FinFet introduces the ionization characteristics which depicts it as an inheritor to the Single gate MOSFET, further the simplicity of the process of formulation of FinFET in comparison with the MOSFET, it may become a highly usable product. All the modern-day technologies and industries based upon Silicon are foreseeing FinFET transistors as highly productive, usable, agile, robust, and due to which it can participate as one of the crucial members in the never ending new- developmental arena. The retardation and speed spins are an important aspect in ICs as both of them are complementary to each other. MOSFEST's gauging has given a new dimension to the size of the IC's. Short Channel Effects (SCEs) kicks-in with MOSFET, if we dig down to nanometer architecture which impacts the attainment and dependability which further can be addressed using FinFET as they have minimum efflux, less threshold voltage and perfect gate control. Although there are certain issues with them as well, like if we go beyond 10nm, leakage problem creeps in which gives rise to other important concerns such as threshold flattening, increase in power density and thermal dissipation. However, with the respect to the matter of heat dissipation, FinFET composition is less coherent as heat can be collected on the fins, thus resulting in the inception of altogether a naïve vertical of design rule – the design for thermal though there are other rules exists already such as design for manufacturability. All these devices are nearing their extinction, so one has to be ready with some new alternatives or inventions with respect to device structure so that the weaknesses can be addressed and also to see the possibility of using new material types instead of currently used materials like silicon. Among them, Carbon Nanotube (CNT) FET, Gate-All-Around Nanowire FET, or FinFETs with compound semiconductors may prove as promising solutions in future technology nodes.

# ACKNOWLEDGEMENT

*High achievement always takes place in the framework of high expectations.* The expectation was there and I begin with determined resolve and put in sustained hard work. It has been rightly said that every successful individual knows that his or her achievement depends on a community of persons working together but the satisfaction that accompanies the successful completion of any task would be incomplete without the mention of the people who made it possible.

This is to acknowledge with gratitude the guidance and ameliorating suggestions from my supervisor, Dr. Suman Lata Tripathi for their support and motivation throughout the thesis work.

I am grateful to the members of the School of Research Degree Programme (RDP) for being in my entire research progress review panel, and providing useful suggestions during the period. I am indeed thankful to all anonymous reviewers of my research papers submitted to various International journals and International conferences, due to which I was indeed able to improve upon the work contained herein.

I am indebted to the Honorable Chancellor, Worthy Pro-Chancellor, the Vice-Chancellor, and the successive Deans, LPU, for facilitating the administrative issues involved and encouraging me throughout.

I express my heartfelt gratitude to the Head of School, of the School of Electronics and Electrical Engineering, and the staff of the Electronics and Electrical Engineering School for their cooperation and support.

No words of thanks are enough to express my deepest gratitude and sincerest love to my parent and friends whose rock-solid faith in me kept me strong in all circumstances. Last but not least, I bow my head before the Almighty God for showering His mercy on me for every moment.

Shekhar Verma

# TABLE OF CONTENTS

|    | Declaration                                                      | i       |

|----|------------------------------------------------------------------|---------|

|    | Certificate                                                      | ii      |

|    | Abstract                                                         | iii     |

|    | Acknowledgment                                                   | iv      |

|    | Contents                                                         | v-vii   |

|    | Abbreviations                                                    | viii-ix |

|    | List of Tables                                                   | x-xi    |

|    | List of Figures                                                  | xii-xv  |

| 1. | Introduction                                                     | 1-13    |

|    | 1.1 Overview of metal-oxide field-effect transistor              | 1       |

|    | 1.2 Retrenchment of devices                                      | 1-2     |

|    | 1.3 Traditional metal-oxide-semiconductor technology             | 3-4     |

|    | 1.4 DG-MOSFET                                                    | 4-6     |

|    | 1.5 FinFETs                                                      | 7-8     |

|    | 1.6 Multigate FET                                                | 8       |

|    | 1.7 Need for lower power-based devices                           | 9       |

|    | 1.8 Motivation                                                   | 9-11    |

|    | 1.9 Research gap                                                 | 11      |

|    | 1.10 Objectives                                                  | 12      |

|    | 1.11 Thesis organization                                         | 12-13   |

| 2. | Literature Survey                                                | 14-22   |

|    | 2.1 Introduction                                                 | 14-15   |

|    | 2.2 Short channel effect                                         | 15-16   |

|    | 2.3 Scaling of metal oxide semiconductor field-effect transistor | 16-17   |

|    | 2.4 Challenges in bulk CMOS                                      | 17-18   |

|    | 2.5 FinFET structure                                             | 18-22   |

|    | 2.6 Summary                                                      | 22      |

| 3. | Design of Multigate Heterojunction FinFET                        | 23-47   |

|    | 3.1 Introduction                                                 | 23-24   |

|    |                                                                  |         |

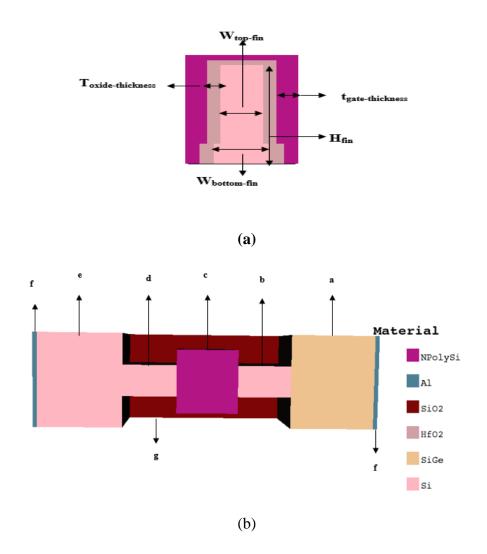

|    | 3.2 Material composition & structure design                     | 24-28 |

|----|-----------------------------------------------------------------|-------|

|    | 3.3 Physical simulation of proposed FinFET                      | 29-31 |

|    | 3.4 Transfer characteristics of 14-nm heterojunction N-FinFET   | 31-36 |

|    | 3.5 Process variation on performance parameter of 14-nm         | 36-44 |

|    | heterojunction N-FinFET                                         |       |

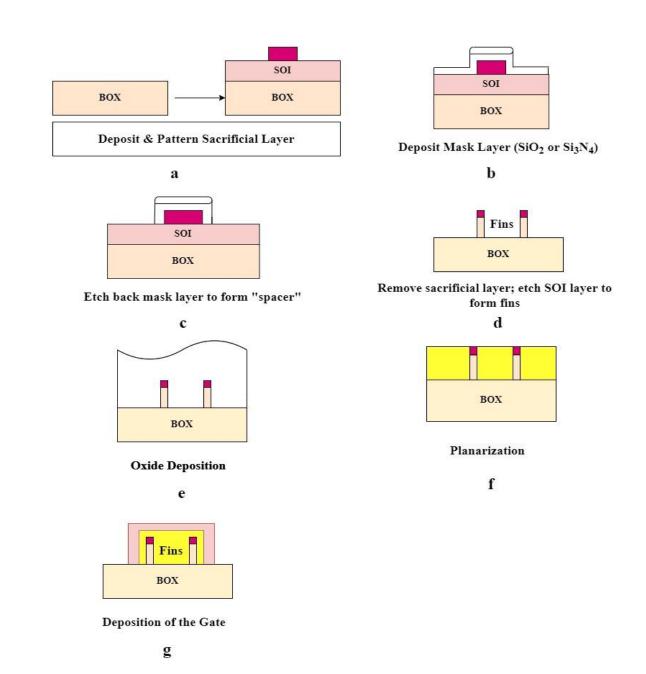

|    | 3.6 Fabrication steps for 14-nm heterojunction FinFET           | 45-46 |

|    | 3.7 Summary                                                     | 46-47 |

| 4. | Impact of Fin shape on Heterojunction FinFET                    | 48-74 |

|    | 4.1 Introduction                                                | 48-49 |

|    | 4.2 Structure design parameter and material composition         | 49-52 |

|    | 4.3 Physical simulation of t shaped fin                         | 52-53 |

|    | 4.4 Current characteristics of inverted T N-FinFET              | 54-56 |

|    | 4.5 Process variation on performance parameter of proposed      | 56-63 |

|    | FinFET                                                          |       |

|    | 4.6 Current flow inside the fin                                 | 63    |

|    | 4.7 Device design parameter & simulation of P-FinFET            | 64-66 |

|    | 4.8 Comparison of a performance parameter of N-FinFET & P-      | 66-69 |

|    | FinFET                                                          |       |

|    | 4.9 Process variation on performance parameter of proposed      | 69-74 |

|    | inverted T shaped 14-nm heterojunction P-FinFET                 |       |

|    | 4.10 Summary                                                    | 74    |

| 5. | Application as an invertor by using the rectangular shaped      | 75-85 |

|    | FinFET and T shaped FinFET                                      |       |

|    | 5.1 Introduction                                                | 75    |

|    | 5.1.1 Design of invertor by using the T shaped FinFET           | 75-77 |

|    | 5.1.2 Design of invertor by using the rectangular shaped        | 77-78 |

|    | FinFET                                                          |       |

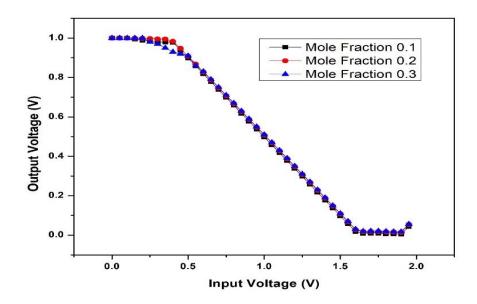

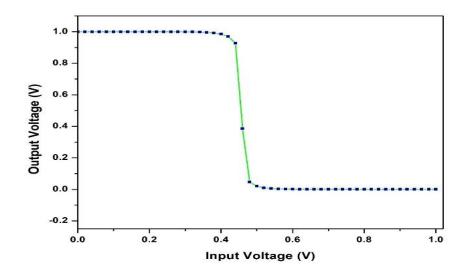

|    | 5.2 DC analysis for rectangular & T shaped fin of FinFET        | 78-81 |

|    | 5.3 Transient analysis for rectangular & T shaped fin of finfet | 82    |

|    | 5.3.1Transient analysis of rectangular-shaped FinFET            | 82-83 |

|    | 5.3.2 Transient analysis of T shaped FinFET                     | 83-84 |

|    | 5.4 Summary           | 85      |

|----|-----------------------|---------|

| 6. | Scope for Future Work | 86-88   |

|    | 6.1 Conclusions       | 86-87   |

|    | 6.2 Future works      | 87-88   |

|    | Tool Description      | 89-99   |

|    | List of Publications  | 100-101 |

|    | Bibliography          | 102-116 |

# **ABBREVIATIONS**

| 2D                          | Two Dimensional                                     |

|-----------------------------|-----------------------------------------------------|

| 3D                          | Three Dimensional                                   |

| BOX                         | Buried Oxide                                        |

| BTBT                        | Band-to-Band Tunneling                              |

| $C_{ds}$                    | Drain to Source Capacitance                         |

| Cg                          | Gate Capacitance                                    |

| CMOS                        | Complementary Metal Oxide Semiconductor             |

| CV                          | Characteristics Capacitance-Voltage Characteristics |

| CVD                         | Chemical Vapor Deposition                           |

| DIBL                        | Drain Induced Barrier Lowering                      |

| $E_{dyn}$                   | Dynamic Energy                                      |

| Eleak                       | Leakage Energy                                      |

| EOT                         | Effective Oxide Thickness                           |

| Etotal                      | Total Energy                                        |

| FET                         | Field Effect Transistor                             |

| FinFET                      | Fin based 3D Field Effect                           |

| GAA                         | Gate All Around                                     |

| GIDL                        | Gate Induced Drain Leakage                          |

| Ic                          | Integrated Circuits                                 |

| $\mathbf{I}_{\mathrm{off}}$ | Off Current                                         |

| Ion                         | On Current                                          |

| ITRS                        | International Technology Roadmap for Semiconductor  |

| IV                          | Characteristics Current-Voltage Characteristics     |

| MOS                         | Metal oxide Semiconductor                           |

| MOSFET                      | Metal Oxide Semiconductor Field Effect              |

| MOSFET                      | Metal-Oxide-Semiconductor Field Effect Transistor   |

| NMOS                        | N-channel MOSFET                                    |

| PMOS                        | P-channel MOSFET                                    |

| SCE                         | Short Channel Effect                                |

|                             |                                                     |

| TCAD             | Technology Computer Aided Design |

|------------------|----------------------------------|

| TEM              | Transmission Electron Microscopy |

| T <sub>ext</sub> | Extension Thickness              |

| Tox              | Oxide Thickness                  |

| $T_{si}$         | Fin Thickness                    |

| $T_{sp}$         | Spacer Thickness                 |

| VDD              | Supply voltage                   |

# LIST OF TABLES

| Table      | Title                                                     | Page       |

|------------|-----------------------------------------------------------|------------|

| No.        |                                                           | No.        |

| 1.1        | Scaling Trend                                             | 2-3        |

| 3.1        | Dimension of the Device Region of 14-nm Heterojunction N- | 25         |

|            | FinFET                                                    |            |

| 3.2        | Dimension of the Device Region of 14-nm Heterojunction P- | 27         |

|            | FinFET                                                    |            |

| 3.3        | Dimension of compared devices                             | 28         |

| 3.4        | Comparison of Performance Parameter                       | 33         |

| 3.5        | Comparison of Drain Current Vs Gate voltage for Different | 34         |

|            | FinFET                                                    |            |

| 3.6        | Comparison of transfer characteristics on different fin   | 37-38      |

|            | materials.                                                |            |

| 4.1        | Dimension of proposed -1 & 2 Heterojunction N-FinFET      | 51         |

| 4.2        | Dimension of the compared devices                         | 51         |

| 4.3        | Comparison of performance parameter                       | 55         |

|            |                                                           | <b>c</b> 1 |

| 4.4        | Variation of Fin Width on T shaped FinFET                 | 61         |

| 4.5        | Variation of Gate length on T shaped FinFET               | 63         |

|            | en e                  |            |

| 4.6        | Device design parameter of 14-nm heterojunction N-FinFET  | 64         |

|            | and P-FinFET of T shaped fin.                             |            |

| 4.7        | Performance Parameter Comparison of P-FinFET & N-         | 67         |

|            | FinFET                                                    |            |

| <b>-</b> 1 |                                                           | 00         |

| 5.1        | DC analysis of rectangular shaped fin of FinFET           | 80         |

| 5.2        | Comparison of DC Analysis for different inverter          | 81         |

| 5.3 | Comparison of transient analysis for the rectangular shaped fin |  |

|-----|-----------------------------------------------------------------|--|

|     | of inverter                                                     |  |

|     |                                                                 |  |

5.4Comparison of Transient Analysis for different inverter84

# LIST OF FIGURES

| Fig. No. | Caption                                                                                | Page No. |

|----------|----------------------------------------------------------------------------------------|----------|

| 1.1      | Generation of the depletion region                                                     | 3        |

| 1.2      | Cross-section of Double Gate FET                                                       | 5        |

| 1.3      | Energy band diagram of Symmetrical DG-FET                                              | 6        |

| 1.4      | Energy band diagram of Asymmetrical DG-FET                                             | 6        |

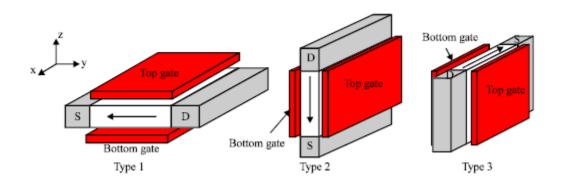

| 1.5      | Three possible realizations of DG-FETs                                                 | 6        |

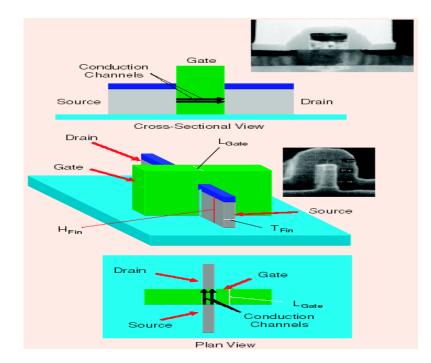

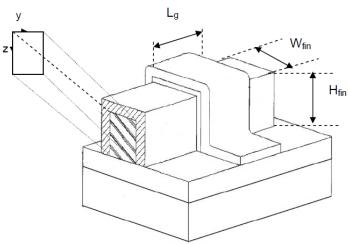

| 1.6      | FinFET structure                                                                       | 7        |

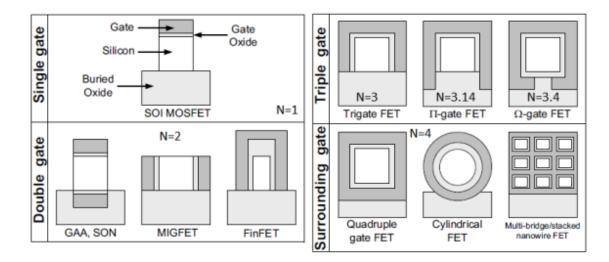

| 1.7      | Multigate device structures                                                            | 9        |

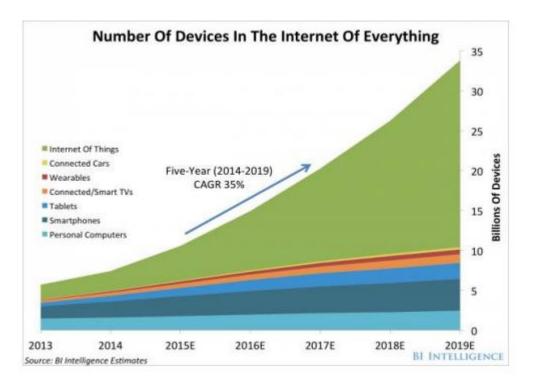

| 1.8      | IoT expansion in the market                                                            | 10       |

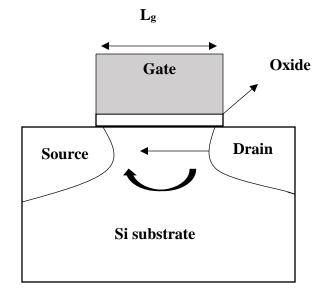

| 2.1      | MOSFET                                                                                 | 17       |

| 2.2      | DELTA                                                                                  | 18       |

| 2.3      | Three-dimensional structure of tri-gate FinFET.                                        | 19       |

| 3.1      | Basic design methodology for Heterojunction FinFET                                     | 24       |

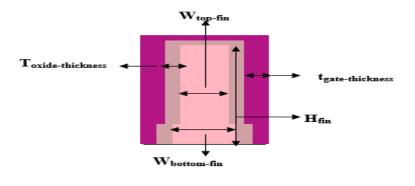

| 3.2      | Basic diagram of FinFET                                                                | 25       |

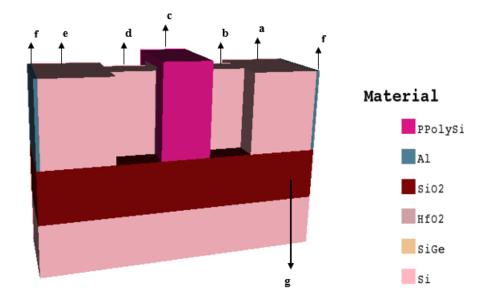

| 3.3      | 14-nm Heterojunction N-FinFET                                                          | 26       |

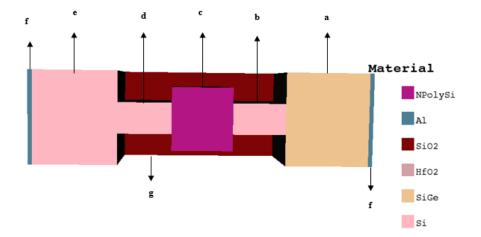

| 3.4      | 14-nm Heterojunction P-FinFET                                                          | 27       |

| 3.5      | Analytic description of 14-nm Heterojunction N-FinFET                                  | 28       |

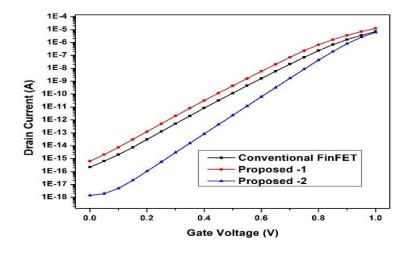

| 3.6      | Transfer Characteristics of Compared Devices.                                          | 33       |

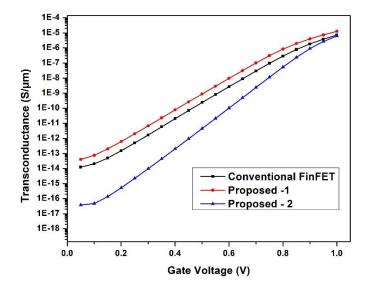

| 3.7      | Transconductance of Compared Devices                                                   | 35       |

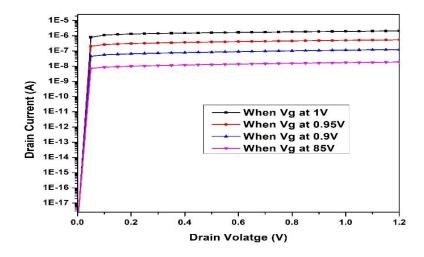

| 3.8      | Output characteristics of Proposed -2 14nm Heterojunction                              | 35       |

| 2.0      | FinFET                                                                                 | 27       |

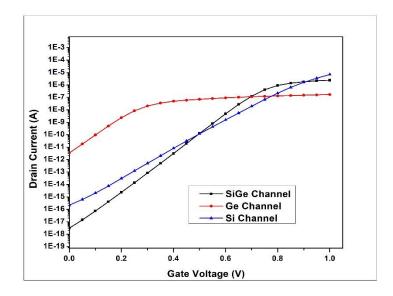

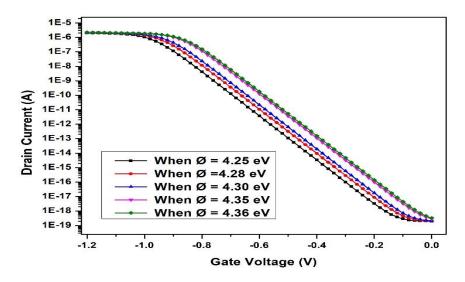

| 3.9      | Drain Current Vs gate voltage on different fin material                                | 37       |

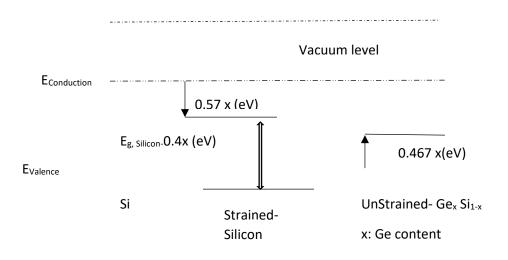

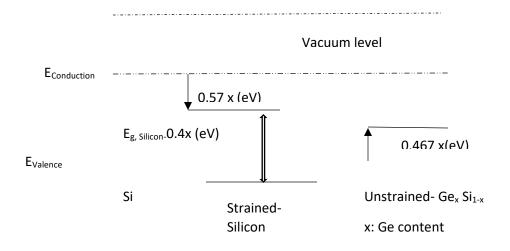

| 3.10     | Impact of strain on band structure of Silicon-Germanium<br>(Sil-xGex) and Silicon (Si) | 39       |

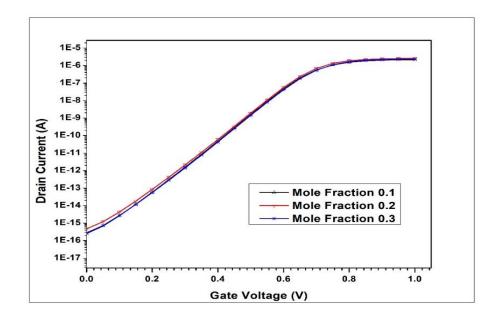

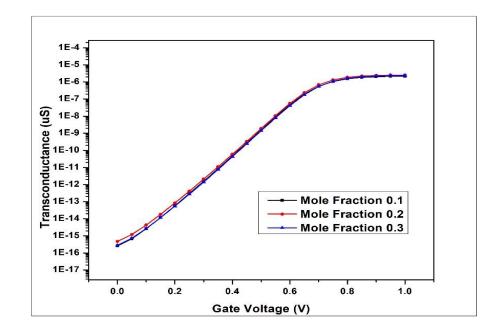

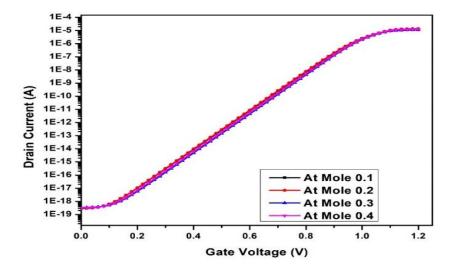

| 3.11     | Impact of Mole fraction on Proposed -2 14nm Heterojunction<br>FinFET                   | 40       |

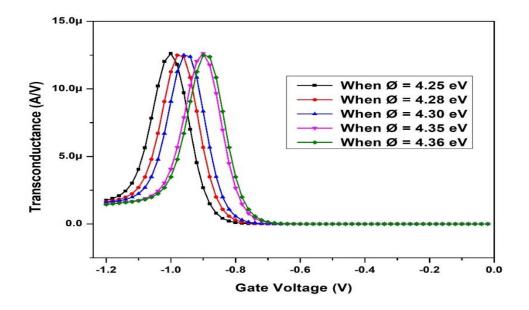

| 3.12     | Transconductance vs Mole fraction                                                      | 41       |

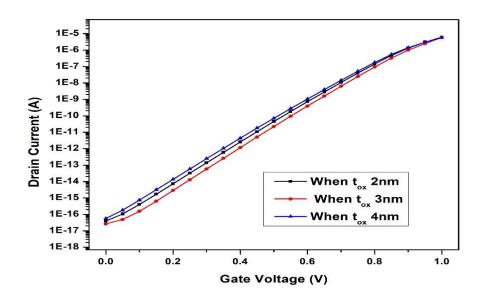

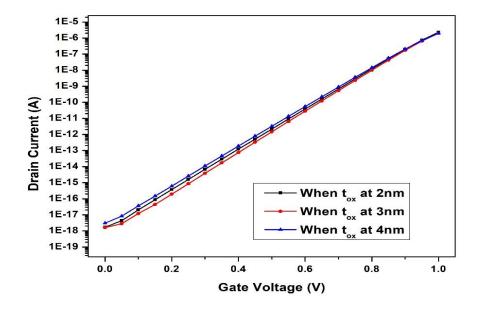

| 3.13     | Variation in oxide thickness when drain voltage at 1V                                  | 42       |

| 3.14 | Variation in oxide thickness when drain voltage at 0.1V                                                   | 43    |

|------|-----------------------------------------------------------------------------------------------------------|-------|

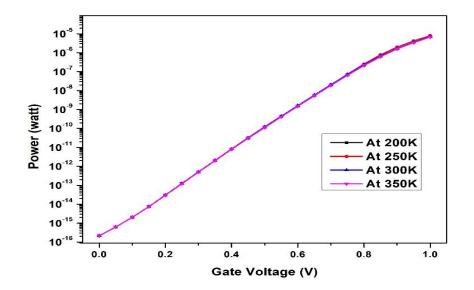

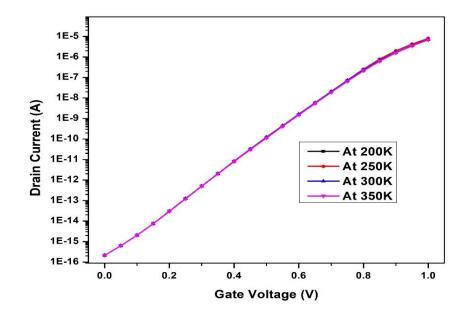

| 3.15 | Impact of temperature variation on power of Proposed -2                                                   | 43    |

|      | 14nm Heterojunction FinFET.                                                                               |       |

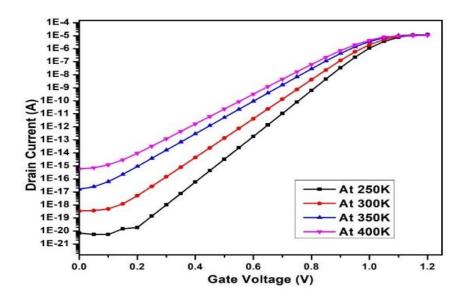

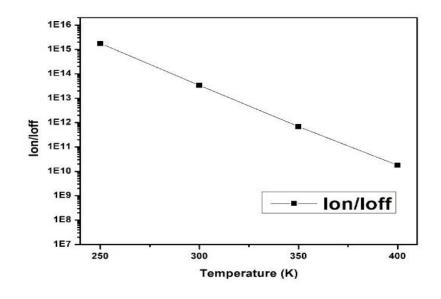

| 3.16 | Variation of temperature vs drain current                                                                 | 44    |

| 3.17 | Fabrications Step for FinFET                                                                              | 46    |

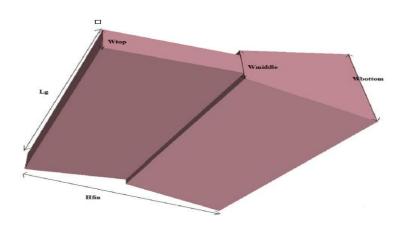

| 4.1  | (a) 14-nm heterojunction inverted-T P-FinFET (b) Three-                                                   | 49-50 |

|      | dimensional of 14-nm heterojunction inverted-T P-FinFET                                                   |       |

| 4.2  | Rectzoidal-fin shaped FinFET                                                                              | 50    |

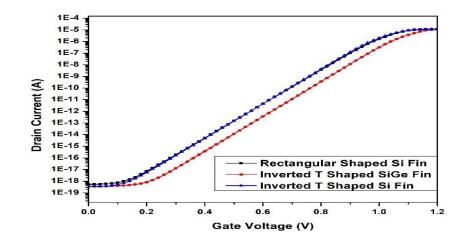

| 4.3  | Transfer characteristics comparison with different fin shaped                                             | 54    |

| 4.4  | Impact of strain on band structure of Silicon-Germanium                                                   | 57    |

|      | (Si <sub>1-x</sub> Ge <sub>x</sub> ) and Silicon (Si                                                      |       |

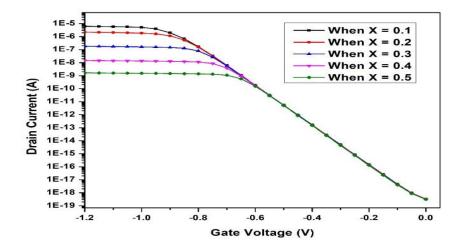

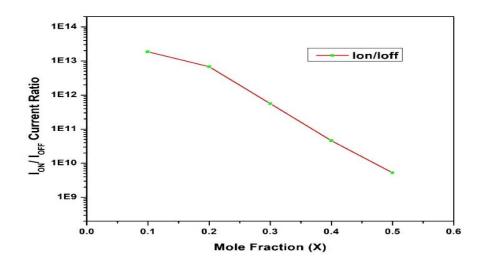

| 4.5  | Transfer characteristics on different mole values                                                         | 58    |

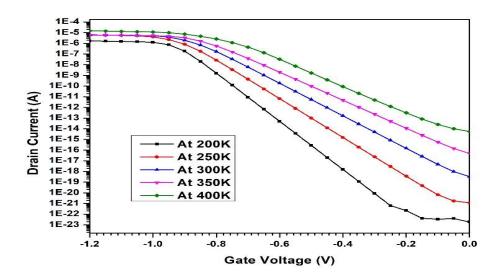

| 4.6  | a) Transfer characteristics at different temperature b) Current                                           | 59    |

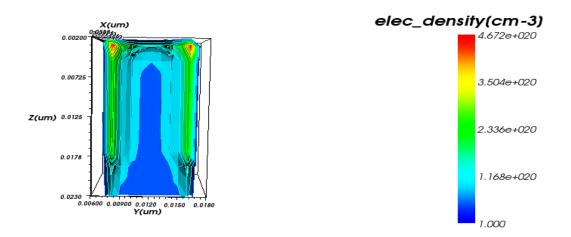

| 4.7  | ratio $(I_{on}/I_{off})$ at different temperature.<br>Electron density inside the fin of T shaped FinFET. | 59    |

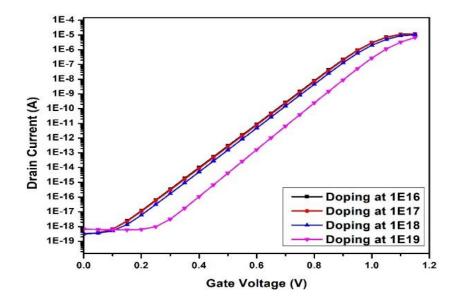

| 4.8  | Doping impact on T shaped FinFET                                                                          | 60    |

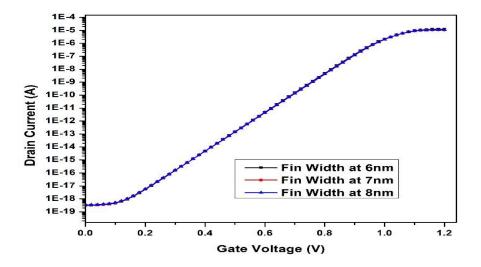

| 4.9  | Variation of Fin Width on T shaped FinFET.                                                                | 62    |

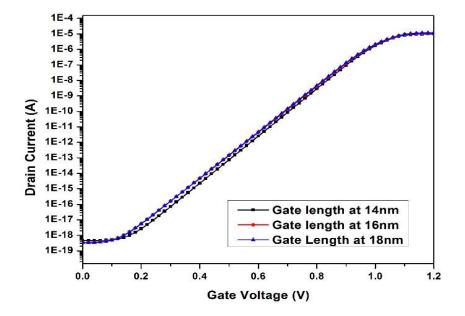

| 4.10 | Variation of gate length on T shaped FinFET                                                               | 62    |

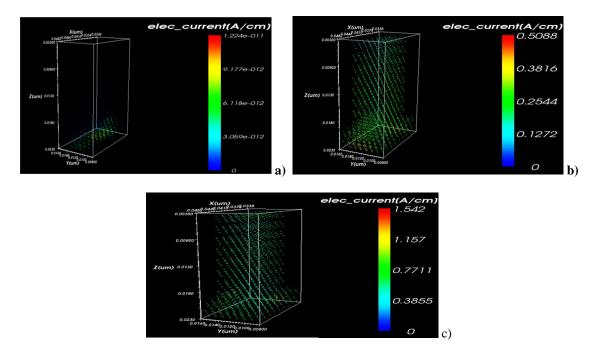

| 4.11 | Current Flow a) When Vgs is 0.18V b) When Vgs is 0.96V                                                    | 63    |

|      | c) When Vgs is 1V                                                                                         |       |

| 4.12 | (a) 14-nm heterojunction inverted-T P-FinFET (b) Three-                                                   | 65    |

|      | dimensional of 14-nm heterojunction inverted-T P-FinFET                                                   |       |

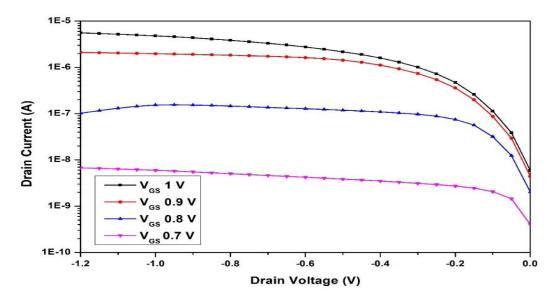

| 4.13 | Output characteristics of Inverted T shaped P-FinFET                                                      | 67    |

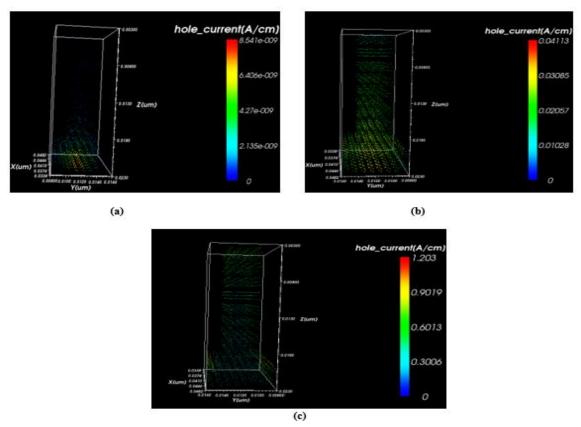

| 4.14 | Hole current Flow inside the T shaped P-FinFET a) When                                                    | 68    |

|      | Vgs at 0.3V b) When Vgs at 0.7V c) When Vgs at 1V                                                         |       |

| 4.15 | Id versus Vgs characteristics of heterojunction inverted-T P-                                             | 69    |

|      | FinFET with different gate contact work functions                                                         |       |

|      |                                                                                                           |       |

| 4.16 | Transconductance versus Gate Voltage of heterojunction                                        | 70 |

|------|-----------------------------------------------------------------------------------------------|----|

|      | inverted-T P-FinFET with different gate contact work functions                                |    |

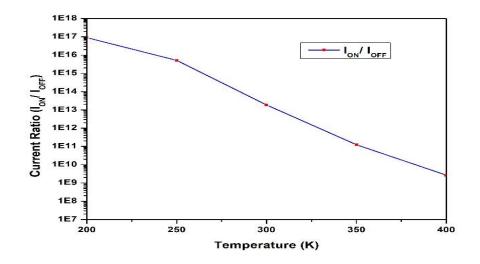

| 4.17 | Transfer characteristics of P-FinFET on the different Mole fraction                           | 72 |

| 4.18 | Current ratio versus mole fraction for P-FinFET                                               | 72 |

| 4.19 | Transfer characteristics of P-FinFET on different temperature                                 | 73 |

| 4.20 | Current Ratio Vs Temperature for P-FinFET                                                     | 74 |

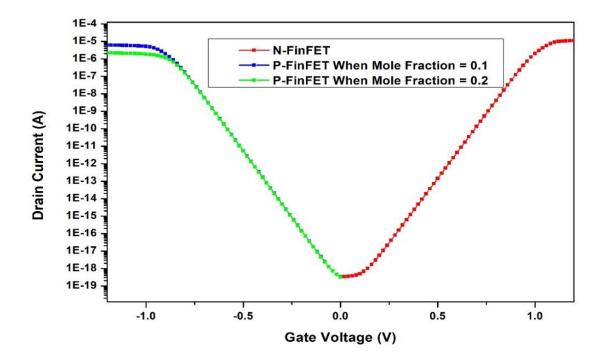

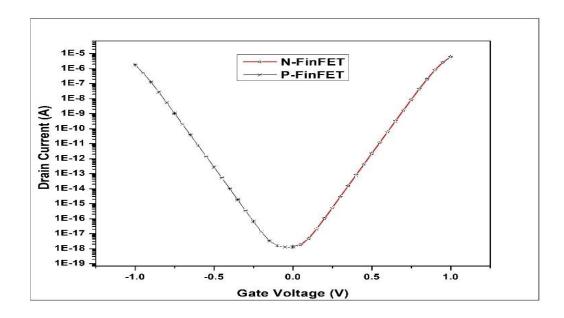

| 5.1  | Transfer characteristics of heterojunction P-FinFET & N-<br>FinFET of T-shaped fin.           | 76 |

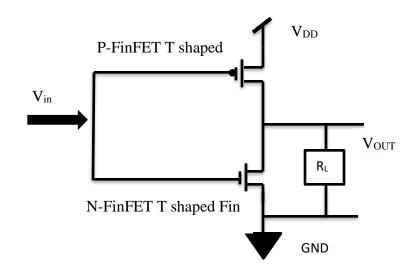

| 5.2  | Inverter Circuit by using the T-shaped P-FinFET & N-<br>FinFET.                               | 77 |

| 5.3  | Transfer characteristics of heterojunction P-FinFET & N-<br>FinFET of rectangular-shaped fin. | 78 |

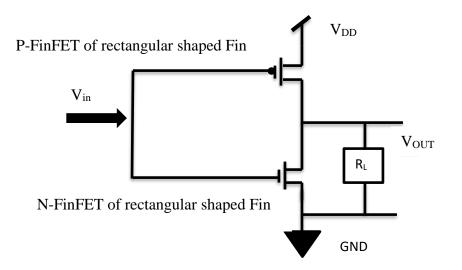

| 5.4  | Inverter Circuit by using the rectangular-shaped P-FinFET & N-FinFET.                         | 78 |

| 5.5  | VTC curve of the rectangular-shaped fin.                                                      | 79 |

| 5.6  | VTC curve of T -shaped fin                                                                    | 80 |

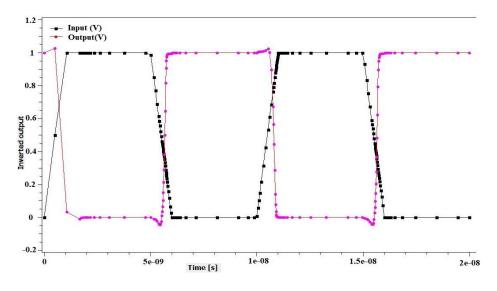

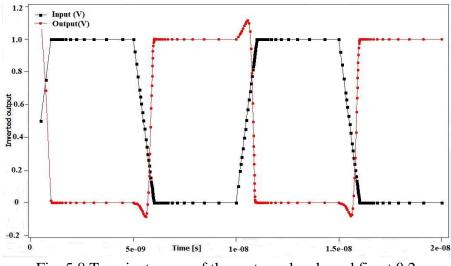

| 5.7  | Transient curve of the rectangular-shaped fin at 0.1                                          | 82 |

| 5.8  | Transient curve of the rectangular-shaped fin at 0.2                                          | 82 |

| 5.9  | Transient curve of the rectangular-shaped fin at 0.3                                          | 83 |

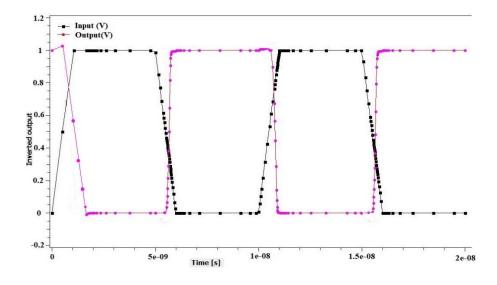

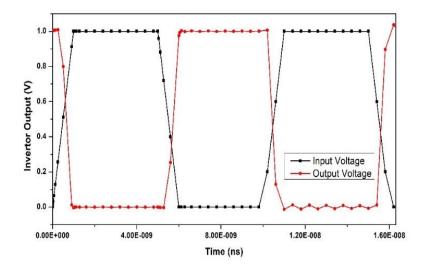

| 5.10 | Transient Curve of T shaped fin at 0.3 mole fraction                                          | 84 |

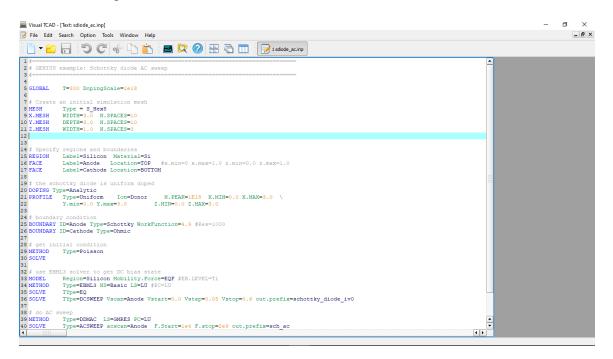

| 7.1  | Device drawing on the visual Tcad                                                             | 90 |

| 7.2  | Device programming on the visual Tcad.                                                        | 91 |

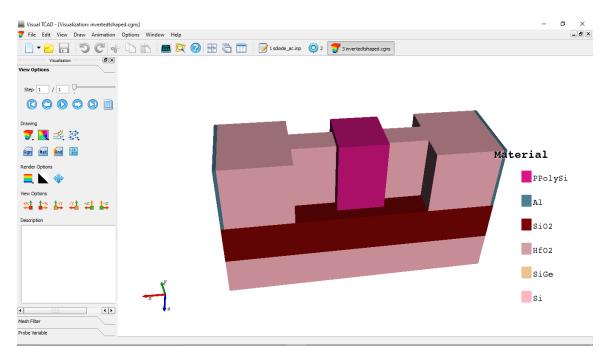

| 7.3  | Device visualization on the visual Tcad.                                                      | 92 |

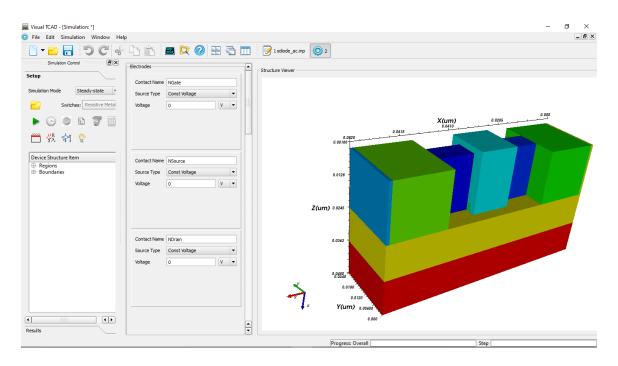

| 7.4  | Device simulation on the visual Tcad.      | 93 |

|------|--------------------------------------------|----|

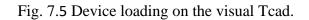

| 7.5  | Device loading on the visual Tcad          | 94 |

| 7.6  | Boundary condition of the device           | 94 |

| 7.7  | Interconnection of the device terminal     | 95 |

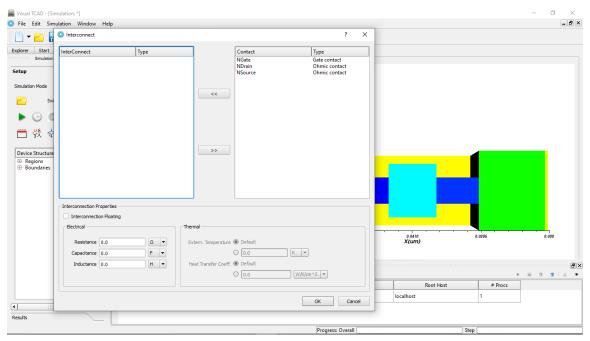

| 7.8  | Physical Model of the device terminal      | 96 |

| 7.9  | Physical Model of the device terminal      | 96 |

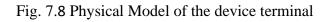

| 7.10 | Physical Model of the device terminal      | 97 |

| 7.11 | Result File of the device after simulation | 98 |

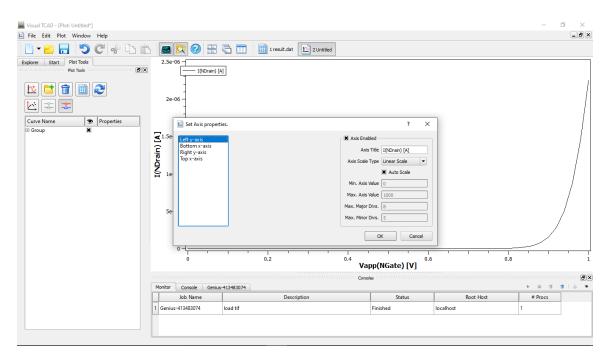

| 7.12 | Graph of the device                        | 98 |

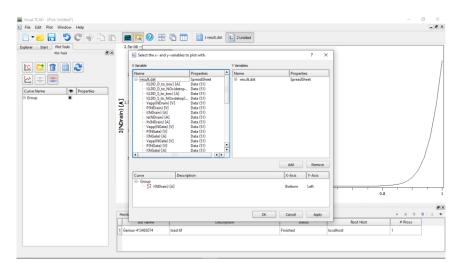

| 7.13 | Clubbing of the graph.                     | 99 |

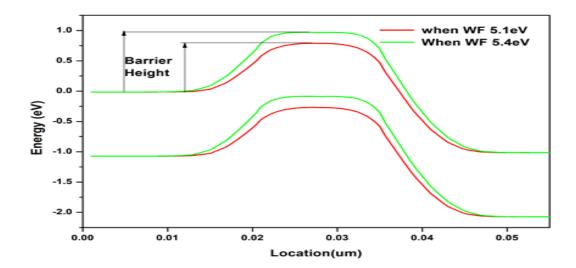

| 7.14 | Energy Diagram                             | 99 |

# **Chapter 1**

# Introduction

#### **1.1 OVERVIEW OF METAL-OXIDE FIELD-EFFECT TRANSISTOR**

Downscaling is a significant and effective approach to attaining semiconductor devices' highest performance regardless of technological challenges. The channel length is noticeably shortened due to the scaling of the devices. As per Moore's law, the size of the transistors will double every two years. These components must be scaled as the number of components on the chip grows while keeping the space constraint in mind. Moore's law is most likely responsible for the evolution of digital technology. This rule should be regarded as an observation rather than a physical rule. As devices become smaller, several limitations affect the devices' performance. When devices are scaled, short channel effects become visible. New transistor technologies that are free of junctions are known as junctionless technology [1], [2], [3] and are used to achieve the precise and optimal performance of devices during scaling.

There are seven sections in this chapter. Section I provides a high-level overview of the research topic. FinFETs and their importance in VLSI circuits are introduced in Sections II and III. The research's objective is described in Section IV, and the numerous research gaps are depicted in Section V. Finally, Sections VI and VII contain the work's aims and thesis organization.

#### **1.2 RETRENCHMENT OF DEVICES**

The speed, power consumption, and area of a digital system are the key impediments. All three pitfalls can't be fixed at the same time. There is no need to make concessions on any of these flaws. To boost the device's speed, we must reduce its physical dimensions, which reduces its area. However, SCE enters the scene and begins to increase power dissipation, increasing power consumption. Devices are scaled from 10um to 5nm in the International

Technology Roadmap for Semiconductors, with 5nm projected in 2020 [2], [3]. The scaling trend of devices is depicted in Table 1.1 from 1971 to 2022. The projected years for achieving the physical gate length of devices are listed in the table below. Etching, photolithography, metal deposition, and other procedures are used in the development of integrated circuits. When it comes to scaling, all of these procedures represent a roadblock for the fabrication business. There are many more parameters that must be scaled when scaling devices, such as the power supply [4], [5], [6], [7]. The change of physical channel length over time is shown in Table 1.1 [4].

| Channel length | Years     |

|----------------|-----------|

| 7 µm           | 1974      |

| 2 µm           | 1982      |

| 700 nm         | 1989      |

| 450 nm         | 1995      |

| 350nm          | 1997      |

| 280nm          | 1999      |

| 180nm          | 2001      |

| 90nm           | 2004      |

| 55nm           | 2006      |

| 45nm           | 2008      |

| 32nm           | 2010      |

| 20 nm          | 2012      |

| 10 nm          | 2016-2017 |

| 7 nm           | 2018-2019 |

**TABLE 1.1**: Scaling Trend [4]

| 5 nm | 2020-2021 |

|------|-----------|

|      |           |

#### **1.3 TRADITIONAL METAL-OXIDE-SEMICONDUCTOR TECHNOLOGY**

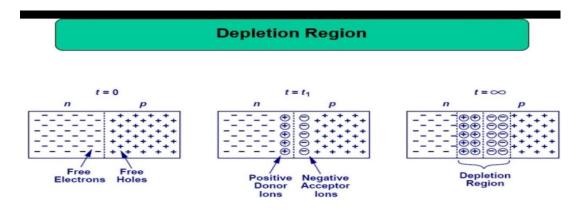

All transistors rely on the induction of various types of doping to produce junctions in the substrate. Metal oxide semiconductors are made with source and drain junctions (MOS). A P-N junction is formed when trivalent type impurity p-type and donor type impurity n-type semiconductors are joined. Diffusion is the movement of carriers from one concentration to another as a result of a concentration gradient [8]. Electrons begin to transition from n-type to p-type, while holes begin to transition from p-type to n-type during the diffusion process. When this happens, some electrons and holes along their path recombine, leaving positive and negative ions in their wake. As a result, a depletion zone develops where there are no mobile providers. The space charge area of the p-n junction is represented in fig 1.1.

Fig 1.1 Generation of the depletion region.[9]

A doping gradient is present in conventional transistors, resulting in the formation of P-N junctions. The current starts or stops flowing depending on the bias supplied to the junction. There are two junctions in a MOSFET. The physical length of the channel is measured by the space between drain and source. There are two gates coupled together in a traditional double gate MOS. The source and drain of an N channel transistor are n-type, while the

substrate is p-type. The device operates in three modes in conventional type MOS, called inversion, depletion, and accumulation. The majority of charge carriers are accumulated in the accumulation mode, removed in the depletion mode, and the n channel is formed from the p-substrate in the inversion model. When voltages are applied to the gate then, all of these modes are triggered. Two back-to-back diodes exist between the source and drain when the gate voltage is not applied. Between the drain (n+) and the substrate, one diode is made, and between the source (n+) and the p substrate, the other is formed. These diodes prevent conduction between the source and the drain even when the drain voltage is applied. As a result, conduction requires the gate voltage [10].

When a negative voltage is applied to the gate terminal of an N channel MOS, it begins to attract the holes in the channel area, which is known as the accumulation mode. When the gate voltage is set positive after accumulation, depletion-mode enters the scene. When the gate voltage reaches the point where the surface concentration of electrons equals the bulk concentration of holes, the threshold voltage is attained. At this voltage, the MOS begins to invert. When voltage is added to the gate, accumulation begins, and the direction of the electric field shifts to point towards the gate. The conduction band and the valence band are both bent upwards. A voltage is formed when both bands become flat, and this is referred to as flat band voltage. In an NPN transistor, if positive fixed charges are present in the oxide, these charges will suck the electron from the substrate even if no voltage is applied, resulting in the production of an inversion layer. While such devices are downscaled to channel lengths of 10nm or less, adding shallow junctions in the device becomes extremely difficult. Fabricating large-sized devices has become a significant issue for the semiconductor industry.

#### **1.4 DG-MOSFET**

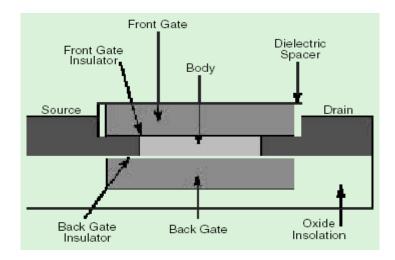

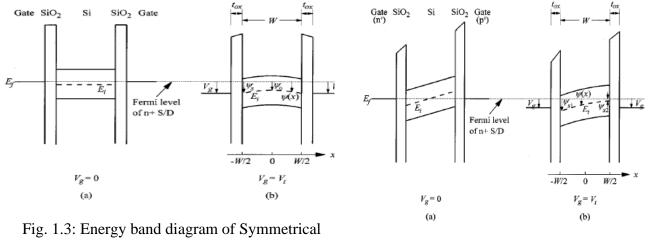

A MOSFET with two gates for controlling the channel is known as a double gate MOSFET (DG-FET). The DG-MOSFET is shown schematically in figure 1.2.

Fig. 1.2: Cross-section of Double Gate FET. [11]

Its main advantage is improved gate-channel control. Because all of the drain field lines are unable to reach the source, it also results in lower SCE when utilized in conjunction with ultrathin bodies in an SOI implementation (FDSOI DG-FET). This is owing to the lower dielectric constant of the gate oxide than Si (assuming SiO2), as well as the ultra-thinness of the body. Because it is more resistant to SCE and has superior gate-channel control, the physical gate thickness can be increased (compared to planar MOSFET). As a result, there are fewer leakage currents (D/S leakage and gate leakage).

There are two types of double-gate FETs:

- Asymmetric

- Symmetric

The front and rear gates of symmetric DG-FETs feature identical gate electrode materials (i.e. bottom and top gates). The channel has generated on both surfaces when symmetrically driven. The bottom gate and top gate electrode materials can differ in an asymmetric DG-FET (for example, p+ poly and n+ poly). When driven symmetrically, this will only build a channel on one of the surfaces. Both have their benefits and drawbacks. In a later section of this study, recent work on them will be discussed. Figures 1.3 and 1.4 show symmetrical and asymmetrical DG-FET energy band graphs.

Fig. 1.4: Energy band diagram of Asymmetrical DG-FET.[12]

The manufacture of DG-FETs is the major, and possibly only, stumbling block. There are three approaches [7, 4] to make a double gate FET, which are labeled with type 1, type 2, and type 3 in the figure. 1.5. Fabrication issues plague Types 1 and 2, making it difficult to construct both gates of the same size and precisely aligned to each other. It's also difficult to align the source/drain areas to the gate margins precisely. Furthermore, because the bottom gate is buried in Type 1 DG-FETs, it is difficult to produce an area-efficient contact and low resistance.

Fig 1.5: Three possible realizations of DG-FETs.[13]

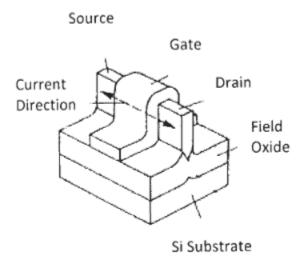

## **1.5 FINFETs**

FinFETs are DG-FETs of type 3. Even though current conduction occurs in the wafer's plane, it is not strictly a planar device. Instead, it's referred to as a quasi-planar device since its vertical geometry (i.e. fin height) has an impact on device behavior. The FinFET is the simplest of the DG-FET types to manufacture. Figure 1.6 illustrates its schematic.

Fig. 1.6: FinFET structure. [14]

It's called a fin because of the vertically narrow channel structure, which looks like a fin of fish, that's why called a FinFET. A gate can also be added to the top of the fin, resulting in a triple gate FET. Alternatively, the oxide above the fin can be thickened to the point where the gate is virtually non-existent.

While the gate length L of a FinFET is identical to that of a regular planar FET, the device width W is somewhat different. The width of the fin is defined as:

$$W = 2H_{fin} + T_{fin} \tag{1.1}$$

where  $T_{fin}$  is thickness and  $H_{fin}$  is the fin height. The rationale becomes clear when one realizes that W, as indicated above, is the breadth of the gate region in contact with (and

thus in control of) the channel in the fin (albeit with a dielectric in between). This is particularly noticeable when the gate is opened (i.e. unwraps it).

The width definition for a triple gate FinFET is shown above. If the gate above the fin is missing or ineffective, the  $T_{fin}$  term in the preceding definition is omitted. On the surface, this upward freedom (the ability to increase  $H_{fin}$ ) appears to be a highly desirable characteristic because it permits the device width W to be increased without expanding the planar layout area (Increasing W raises the Ion, which is a good thing.) However, because there is a certain range (in relation to Tfin) beyond which Hfin should not be increased, or else SCE will occur [15, 16], Hfin should not be increased beyond that range. FinFET scaling and greater drive current for future devices have been made achievable by gate work function engineering, thinner gate oxide, and more streamlined FinFET processes [17]. In 2011, Intel Corporation created a new transistor technology called "3D Trigate." [18]

#### **1.6 MULTIGATE FET**

A multi-gate device has numerous gates on multiple surfaces around the channel to effectively suppress "off-state" leakage current. Multi-gate devices also allow for higher current per region in the "on" state. These advantages equate to lower leakage power consumption and better device performance. Nonplanar transistors are also more compact than planar transistors, enabling higher transistor density and chip size reduction.

Furthermore, several gate layouts such as Tri-gate, Si nanowire FET, Fin FET, planar double-gate, and Gate-All-Around (GAA), and others have been proposed and proven. The multi-gate Si FinFETs are schematically illustrated in figure 1.7.

Fig. 1.7 Multigate device structures. [19]

## 1.7 NEED FOR LOWER POWER-BASED DEVICES.

The internet of things (IoT) has become an increasingly prominent topic of discussion in recent years. The goal of the Internet of Things is to connect any device to the Internet. This category includes cellphones, coffee makers, washing machines, wearable devices, and almost everything else we can think of. By 2020, Cisco and Ericson expect that there will be more than 50 billion connected devices. [20]

The evolution of personal electronics such as cell phones, computers, laptops, and tablets is depicted in figure 1.8. The world's population, on the other hand, limits its growth. The actual increase is being driven by all of these linked gadgets in areas like home automation, hospitals, and transportation. There will be a near-infinite number of gadgets available. All of these devices should be energy efficient and have a long battery life, but not at the expense of performance.

## **1.8 MOTIVATION**

The growth of microelectronic devices occurs rapidly in terms of cost, size, and performance. The scaling of the device dimensions acts as a kick point for the semiconductor industry that allows the manufacturing of the integrated circuit with reduced size, and the hat further leads to an increase in transistor density.

Fig. 1.8 IoT expansion in the market. [20]

As per the current scenario of International Technology Roadmap 2007, the physical gate length of the devices that are used in high-performance circuits are around 20 to 5nm by 2022 [21]. This shows a clear indication of the microelectronic industry entering into a new era of technology that is based on the nano dimension.

FinFET device scaling is a critical part of improving performance and achieving high performance and low power-based VLSI circuits. As a result, an accurate assessment of device performance and properties at the nanoscale is critical for understanding the FinFET device's limit and developing a new concept.

Short Channel Effects (SCEs) rise when the device's channel length decreases, causing the device's performance to suffer [22]. The most challenging aspect in the scaling of MOSFET is to control the SCEs. For better integrity on reduced channel length, the double gate

MOSFETs and FinFET play a vital role in it. FinFETs, on the other hand, have better electrostatics than single gate MOSFETs due to channel controllability [23].

Reducing supply voltage is one of the key parameters to keep the low switching power dissipation. But for attaining the high-performance device, however reduction in threshold voltage ( $V_{th}$ ) is required. The reduction in the threshold voltage ( $V_{th}$ ) in MOSFETs, leads to an increase exponentially in leakage current that degraded the static power of the device [24]. So, analysis of FinFETs device on the nanoscale is very important for attaining a high-performance circuit in VLSI.

## **1.9 RESEARCH GAPS**

Even though lots of work was carried out on the FinFET device. There are still a few issues that need to be worked out more thoroughly. A few studies show the process variation impact like temperature variation and oxide thickness variation on heterojunction multigate FinFETs on lower channel length (less than 20nm). Similarly, computational modeling was implemented in a few numbers. In the vast majority of cases, the existing mechanism is chosen for heterojunction multigate FinFETs either by an experimental approach or through the use of a hardware-based modeling environment. Because experimental procedures produce extremely trustworthy results, no research has examined computational complexity to date, making the methodology less relevant in real-time and large-scale commercial applications. The hardware-based approach makes use of a specific simulation environment, which limits the computational capability in this case. When the device gate length is scaled below 20nm, FinFETs have a weak subthreshold slope and a large leakage current, hence the primary concerns related to short channel effects persist. This option is critical for creating a low-power application. The impact of fin shape and fin material variation on the performance parameter of the FinFET device has been demonstrated in a few kinds of research.

## **1.10 OBJECTIVES**

The objectives of the work are as follows:

- 1. To design the heterojunction Multigate FinFET and its comparison with conventional FinFET.

- 2. To perform process variation on heterojunction Multigate FinFET.

- 3. To analyze the impact of the fin shape on the performance parameter of the heterojunction multigate FinFET.

- 4. To perform the verification for desired IOT based performance at different technology based on power and speed factor.

## **1.11 THESIS ORGANIZATION**

The following are the six chapters that comprise the thesis:

Chapter 1 provides the introduction and limitation of the planer MOSFET and the need for low power devices for future technology nodes followed by the introduction of FinFET. Further, the motivation, research gaps, objectives of the proposed work have been discussed in the same section.

Chapter 2 provided the review of existing literature for the proposed work. In this review, the different techniques for reducing the SCEs and fin shape impact on the performance parameter have been discussed. This chapter also discusses the obstacles, simulated and measured outcomes, and their applications.

Chapter 3 covers the models used in device modeling and describes the simulation approach for 14nm gate length Heterojunction FinFETs. The current-voltage characteristics of simulated models are compared to experimental results to calibrate the models.

Chapter 4 shows the simulation of the inverted T-shaped 14-nm heterojunction FinFET and its comparison with rectzoidal shaped FinFET and rectangular-shaped FinFET. In this chapter impact of the Mole fraction (Si<sub>1-x</sub> Ge<sub>x</sub>) in the fin, the material was also analyzed.

Chapter 5 shows the synthesis of the inverter circuit by using the proposed design and analyzing its performance as per transient and dc analysis.

The future scope of the suggested study is discussed in Chapter 6.

# **Chapter 2**

# Literature Survey

## **2.1 INTRODUCTION**

The dimension of the transistor has been reducing on a scale of nanometers with passing years. Scaling of the transistors acts as an advantageous step for attaining the higher packaging density and high performance with low power consumption [25]. In the future, microelectronic devices play a key role in the future of the VLSI circuits. Both microelectronic and nanoelectronics make a hybrid model that will boost up a powerful system and structures. Certain modifications in the traditional CMOS transistor will lay a foundation of some novel nanodevices like Double Gate (DG) Metal Oxide Semiconductor Field Effect Transistor (MOSFET, Silicon on Insulator (SOI), and FinFET [26]. For overcoming the limitation of the CMOS transistor, is very important to understand these new device operations and structures.

It's very easy to scaled-down the SOI devices with multigate like double-gate FinFET or Multi-Gate FinFET as compared to the conventional bulk-Si devices [27] [28]. The important feature of Multigate SOI MOSFET is good to hold on channel region through a gate that minimized the SCE effects in the device. Quantum Mechanical plays an important role in these devices due to its ultra-thin Si-body and gate dielectric [29]. Because of the high leakage current and short channel impact below 50nm, typical CMOS devices limit scaling. Minimizing the leakage current requires a thin gate dielectric with a heavily doped body that is not feasible in conventional CMOS. Multigate FinFET structures can easily overcome these and other scaling limitations. The multiple gates on the device, make the channel to gate capacitance is double that controls the channel potential in a better manner by the gate electrode that further limits the leakage current.

As compared to the bulk planner MOSFETs, FinFET shows the simple process and compatibility with the current flow. The property of self-alignment of the FinFET structure, makes it more advantageous in comparison to bulk MOSFETs or double gate MOSFET

due to the lower value of gate to drain capacitance and intrinsic gate to source, which is a result of high-speed operation. Due to the fast progress of the processing technique, the size of the MOSFET device is quite aggressive. But as the MOSFET device scaled down that led to an increase in the short channel effect [30]. A little modification in the import atom inside the limited area of the Si channel has a substantial impact on the effective doping density when the device is scaled down. As a result of the variation in doping density, managing threshold voltage is always a difficult task, as there is a typical link between threshold voltage and doping density. For regulating the threshold voltage (Vth), many studies have always concentrated on high doping density [31],[32],[33].

#### 2.2 EFFECT OF SHORT-CHANNEL

As the size of the device shrinks, the distance between the drain and the source shrinks, affecting the controllability of the gate electrode over the channel region, causing the shortchannel effect. This effect will be limiting the scaling of the MOSFETs [34]. With the help of the voltage-doping transformation, the technique can translate the effects of shrinking device parameters like drain voltage or gate length into the electrical parameter. Draininduced barrier lowering (DIBL) and short-channel effects (SCE) can be derived from the voltage doping transformation model [35].

$$SCE = 0.64 \frac{\varepsilon_{Si}}{\varepsilon_{ox}} \left[ 1 + \frac{x_j^2}{L_{el}^2} \right] \frac{t_{ox} t_{dep}}{L_{el}} V_{bi} = 0.64 \frac{\varepsilon_{Si}}{\varepsilon_{ox}} EI V_{bi}$$

(2.1)

and

$$\text{DIBL} = 0.80 \frac{\varepsilon_{\text{Si}}}{\varepsilon_{\text{ox}}} \left[ 1 + \frac{x_j^2}{L_{el}^2} \right] \frac{t_{\text{ox}}}{L_{el}} \frac{t_{\text{dep}}}{L_{el}} V_{\text{DS}} = 0.80 \frac{\varepsilon_{\text{Si}}}{\varepsilon_{\text{ox}}} \text{ EI } V_{\text{DS}}$$

(2.2)

Where  $V_{bi}$  is the drain or source built-in potential,  $x_j$  is the drain and source junction depth and  $L_{el}$  is the effective channel length,  $t_{dep}$  is the penetration depth of the electric field from gate to channel region. Here EI factor is known as the electrostatic integrity. This electrostatic integrity depends on the dimension of the device and it measures the influence of the electric field on the channel region that is lined up from the drain region. So, this factor caused the DIBL and SCE effects on the device [36]. So as per the above expressions 2.1 and 2.2, the threshold voltage of a MOSFET can be calculated fo a channel length L<sub>el</sub>.

$$V_{TH} = V_{TH\infty} - SCE - DIBL \tag{2.3}$$

Where  $V_{TH\infty}$  is represented here as a threshold voltage of a long channel device. If the gate length of the devices decreases then the threshold voltage is also decreasing and this concept is called threshold voltage roll-off [37]. For reducing the short-channel effects then as per equation 2.1, junction depth and thickness of the gate oxide need to be minimized by increasing the doping concentration.

# 2.3 SCALING OF METAL OXIDE SEMICONDUCTOR FIELD-EFFECT TRANSISTOR

The usage of bulk silicon MOSFET as shown in figure 2.1 in the semiconductor industry on large scale over the last 5 past decades. In nineteen, many other alternatives of bulk Sibased MOSFET have been proposed and invented. However, scaling down bulk Si MOSFETs below the 20nm node is challenging due to an increase in the capacitive coupling of the channel to the source as gate length decreases, which increases SCE effects. The main objective is to reduce the dimension of the device to increase the chip density and low cost per function with a high speed of operation. So, device scaling required a balance between the device's reliability and device performance. So, smaller devices required a uniformity scale for channel length. This is known as Drain Induced Barrier Lowering (DIBL) because it expresses itself as a) threshold voltage roll-off, b) increased off-state leakage current, and c) lowering of threshold voltage with higher drain bias [38].

Various technological advancements, such as ultra-thin gate dielectric [39], halo implant, ultra-shallow drain/source junction [40], and advanced channel dopant method [41], have been required to retain the relatively robust gate control of the channel potential device. Each of these technologies is approaching a basic physical limit, which will further limit the device's scalability [42].

In a MOSFET device, the thickness of the gate dielectric is one of the parameters for enabling

Fig. 2.1 MOSFET

the device scaling. But a thin gate increases the coupling capacitance from gate to channel that reduces the impact of source/drain on the channel region. However, larger gate capacitance increased the on-state current by increasing the inversion layer [43]. Because the capacitive coupling of the channel to the source increases as gate length decreases, scaling down bulk Si MOSFETs below the 20nm node is challenging due to increased SCE effects. [44]. To overcome this problem, another alternative solution of usage of high- k gate dielectric material has been proposed that provides an effective gate control for  $L_{el}$  scaling to control the leakage current [45].

## 2.4 CHALLENGES IN BULK CMOS

There are many challenges in CMOS technology to reduce the impact of the short channel effect, a high degree of dopant activation and ultra-shallow junctions with high doping are required [46]. Currently, many types of research are carried out on laser annealing and flash lamp annealing but these methods are not suitable for future technology nodes [47]. A polysilicon gate depletion effect hampers the threshold voltage and performance by contributing towards the effective oxide thickness. By using the metal gate technology, this effect can be eliminated. However, a separate gate material is required for PMOS and

NMOS devices to achieve the required work function which further leads to complexity in process integration. As polysilicon gates with a combination of silicon dioxide gate dielectric in bulk CMOS technology play the most suitable technology but the above challenges required a strong push for other alternative device structures and process techniques [48].

The major concern in bulk CMOS is static power consumption due to leakage current and short channel effect [49] and this leakage current is due to quantum mechanical tunneling, junction leakage, and subthreshold leakage. Using the high-k dielectric material in replace of Silicon dioxide insulator will sort out the leakage problem but not subthreshold leakage [50]. So new metal gate material is required along with high-k dielectric material to overcome this issue like strained silicon germanium or double gate MOSFET etc.

#### **2.5 FINFET STRUCTURE**

FinFET originally originated from the depleted lean channel transistor (DELTA) as shown in figure 2.2 [51].

Fig. 2.2 DELTA [51]

Both DELTA and FinFET transistors work on the same principle. In FinFET and DELTA, the thin structure of the body known as the fin is connected with large source/drain pads. The sides of the fin are covered with the gate material and it is masked with high- k

dielectric material. The current conduction always takes place at the center of the fin and device current can be increased by using the parallel fins. In FinFET, the channel width is always defined by the fin height and if it is compared with the conventional MOSFET it will be twice the fin height.

The concept of a novel scaling technique, such as high-k/metal-gate and channel strain, was introduced to increase the transistor's performance and achieve superior stability concerning speed, power, and cost in the VLSI Circuit [52]. Due to the invention of the FinFET, it is now possible to scale down the length of the channel from 24nm to 6nm, resulting in improved channel electrostatics. The double gate structure is based on the historical channel length scaling trend, with the addition of a new scaling parameter known as channel thickness. The three-dimensional nature of the FinFET is shown in figure 1.2, which overall lowered the footprint of the transistor, and a new performance parameter known as a 'Fin-Effect' (W/Fin-Pitch) that is not present in MOSFETs structure has been introduced. FinFET performance is affected by fin height ( $H_{fin}$ ), fin width (W), gate length ( $L_{gate}$ ), as well as oxide thickness. These settings can be changed to improve the performance of FinFET devices [53].

Fig. 2.3 Three-dimensional structure of tri-gate FinFET. [53]

However, to reduce the SCE, these parameters must be kept to a minimum, such as a fin thickness being equal to one-third of the length of the channel [54]. By adding a high-k dielectric material into the gate stack, leakage current can be reduced [55]. In general, the dielectric gate stack (typically high-k material) reduced oxide layer deterioration and enhanced capacitive coupling between gates and channels. FinFETs are difficult to construct a compact model for due to their reduced size and three-dimensional nature. By increasing the height of the fins, the Short Channel Effect in FinFETs can be mitigated, resulting in significant DIBL and a superior subthreshold slope.

When the Fins Effect is combined with the channel length, a superior result is achieved in terms of contact area reduction, which boosts contact resistance and device performance [56]. The two types of FinFETs available are SOI and Bulk FinFETs. The substrate fin is not attached to the substrate in the case of SOI; nevertheless, the substrate fin is directly linked to the substrate in the case of SOI. By minimizing direct contact between the fin and the substrate, SOI provides excellent insulation while also increasing the self-heating effect. Because of this self-heating, monitoring the temperature's impact on the FinFET device is crucial. The leakage current is reduced when the oxide material is replaced with hafnium oxide, although the temperature effect of this addition on the device is difficult to measure [57]. The off current can be reduced and the short channel effects can be reduced by using a spacer. To eliminate short channel effects in fin materials, metal gate contacts can be used instead of polysilicon [58], and GaAs can be used instead of silicon.

The fins in many FinFETs devices are constructed in a trapezoidal shape [60] to increase transistor performance at smaller sizes. When scaling down devices over a decade, the lowest value of subthreshold slope (SS) is limited to 60mV due to short channel effects (SCEs), and DIBL values should be as low as possible. Several scaling solutions, such as channel strain with diverse materials such as Ge, GaAs, and SiGe, high-k/metal-gate, can improve VLSI Circuit device performance in terms of cost, power, and speed [62].

When the VDD is lowered, the effect of the drain-induced field grows, forcing changes in overall transistor architecture from a single gate to many gates or gate overall around [63] to improve channel gate control by reducing subthreshold performance. The subthreshold slope of FinFETs can be increased by raising fin height, which minimizes oxide layer degradation and boosts capacitive coupling between channel and gates DIBL [64]. The contact area is reduced when the fins effect is paired with the channel length, increasing contact resistance and boosting device performance [65]. The SOI and bulk type structures that are available can be used to design the FinFET. In SOI, the substrate fin is not physically linked to the substrate, but in bulk, the substrate fin is physically attached to the substrate [66]. By minimizing direct contact between the fin and the substrate, SOI provides improved insulation, resulting in decreased leakage current and increased selfheating. Because of this self-heating, it's critical to keep an eye on the temperature's impact on the FinFET device [67]. By replacing the oxide material with hafnium oxide, the leakage current is reduced, albeit the temperature effect of this addition on the device is difficult to measure [68]. If the channel material is strained SiGe, fluctuations in the strained SiGe channel can cause a shift in transconductance and threshold voltage [69]. Modeling Challenges: As the size of electronic gadgets decreases, they become increasingly complex in terms of processing power [70]. This makes it very difficult to analyze and forecast the appearance of the gadget in its ultimate state. It consequently provides a considerable modeling difficulty for bodily processes. The field-level transistors (FINFET) that have the potential to replace the majority of MOS in nanotechnology. This is because FINFET fabrication process is nearly equivalent to that of a normal MOS transistor [71].

Due to its resistance to Short Channel Effects as well as conventional design, nanowires and FINFET have attracted a great deal of attention. Silicon NW FinFET (SNWFT) will be evaluated as a contender for CMOS nomination at 32 nm node because to its excellent performance, strong gate control, and travel improvements [72]. The compact controlled body and several gates give FINFET with strong short-term control, electrostatic protection against body inclusions, and relaxing drug or pocket-packing channels, which are crucial in planetary technology for preventing threshold voltage ( $V_{th}$ ) emissions. Metal gates with High-k (HKMG) dielectric Stacks give the Vth required for performance adjustment and minimizing gate leakage, making it possible to use gate engineering to produce devices with enough  $V_{th}$ . The three-dimensional nature of FINFET provides several advantages, such as the ability to increase the driving current while maintaining the same footprint. By using a channel switch that utilizes characteristics like carbon nanotubes (CNTs) or graphene, device performance on the micro scale may be enhanced via increased Ion/Ioff ratios and decreased leaks, resulting in lower power consumption. [73].

#### 2.6 SUMMARY

Semiconductor industry research is driven by the incessant desire for miniaturization and improvement in semiconductor electronic devices. As traditional devices were shrunk to sizes below 50 nm in SCE, the necessity arose for the creation of new FETs. The electrical properties of the device, such as the threshold voltage, DIBL, SS, etc., are negatively impacted by SCE. The channel of multigate transistors may be controlled more precisely, and SCE is automatically muted. Studies on various multigate transistors are being conducted with an eye toward their eventual commercialization. It is generally agreed that FinFETs are the transistors of the future because of the sub-20 nanometer domain into which they may be scaled. However, it introduces new parasitic that degrade FinFET functionality. In this chapter, we have gone over the fundamentals of a FinFET and how it works, with special emphasis on two variations: the shorted gate and independent gate FinFETs. Different varieties benefit from different features. FinFET devices, like other MOSFET devices, are susceptible to device variability. Due to the nanoscale nature of FinFET production, several process variances cannot be avoided. The following chapter will concentrate on these FinFET device characteristics.

## **Chapter 3**

# **Design of Multigate Heterojunction FinFET**

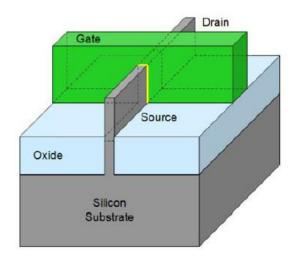

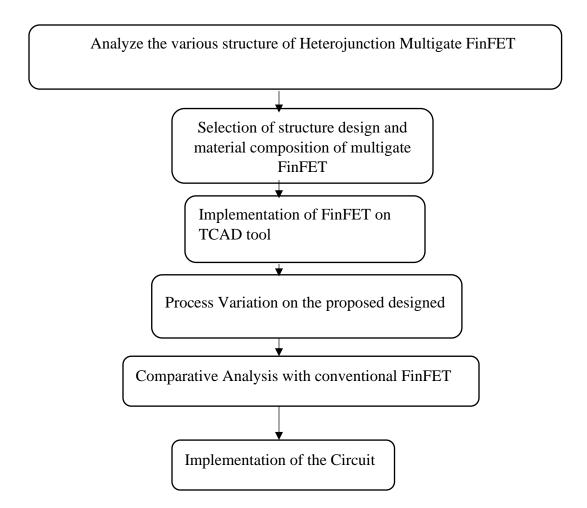

### **3.1 INTRODUCTION**

The main focus of this chapter is to study and describe the basic design procedure of Heterojunction FinFET and its comparison with conventional FinFET. As discussed in chapter 2, multiple techniques have been employed by the researchers to achieve the FinFET for lower applications. However, the initial step of all the mentioned designs is to achieve the Low power-based high-performance device for the VLSI circuit.

A basic FinFET device needs to possess certain characteristics such as minimum short channel effect, minimum off current, and high on current as stated in earlier chapters. The design process of the multigate Heterojunction FinFET device contains a few steps that are mentioned below:

- Selection of the structure design of FinFET i.e. SOI-based structure or Bulk-based structure.

- Finding the channel length, fin height, fin width and oxide thickness, and gate length of the device.

- Selection of the dielectric material for gate oxide.

- Selection of material composition for creating the Heterojunction

- Selection of the doping level for fin, source, and drain

- Parametric study of the device for optimal results

Based on these steps Fig. 3.1 demonstrates the basic design methodology used to design the multigate Heterojunction FinFET for low power applications. The purpose is to understand the basic simulation of the multigate Heterojunction FinFET. In this chapter, we have designed the 14-nm Heterojunction FinFET by using the SOI-based structure.

Fig. 3.1 Basic design methodology for Heterojunction FinFET

This chapter is organized into four sections. Section I represents the basic structural design and material composition of FinFET. Further, section II shows the comparisons of the proposed design with conventional FinFET and section III shows the process variation on the proposed design.

### **3.2 MATERIAL COMPOSITION & STRUCTURE DESIGN**

The Bulk type and the SOI type are the two different structure kinds for designing FinFETs [74-76]. The fin of the FinFET is not directly attached to the substrate in the SOI type structure, but the fin is directly attached to the substrate in the Bulk type. As a result of the lack of direct contact between the fin and the substrate, the SOI type structure provides

better insulation and reduces the short channel effect in the device. As a result, we employed the SOI type structure in the suggested device, and figure 3.2 depicts the

FinFETs basic diagram.

Fig. 3.2 Basic diagram of FinFET

| Table 3.1: Dimension of the l | Device Region of 14-nm | Heterojunction N-FinFET |

|-------------------------------|------------------------|-------------------------|

|                               |                        |                         |

| Region of     | Material         | Region | Region | Region | Doping               |

|---------------|------------------|--------|--------|--------|----------------------|

| device        |                  | Length | Width  | Height | Level                |

| Extended      | Silicon          | 13nm   | 10nm   | 20nm   | $1 x 10^{20} / cm^3$ |

| Source -1 (a) |                  |        |        |        |                      |

| Extended      | Silicon          | 20nm   | 24nm   | 20nm   | $1 x 10^{20} / cm^3$ |

| Source-2 (b)  |                  |        |        |        |                      |

| Extended      | Silicon          | 13nm   | 10nm   | 20nm   | $1 x 10^{18} / cm^3$ |

| Drain-1 (d)   |                  |        |        |        |                      |

| Extended      | Silicon          | 20nm   | 24nm   | 20nm   | $1 x 10^{18} / cm^3$ |

| Drain-2 (e)   |                  |        |        |        |                      |

| Fin           | Silicon-         | 14nm   | 10nm   | 20nm   | $1 x 10^{18} / cm^3$ |

| (Channel)     | Germanium        |        |        |        |                      |

|               | $(Si_{1-x}Ge_x)$ |        |        |        |                      |

| Gate (c)      | PPolySi          | 14nm   | 2nm    | 23nm   | -                    |

| Oxide         | HFO <sub>2</sub> | 14nm   | 2nm    | 21nm   | -                    |

| Contact Of    | Aluminum         | 20nm   | 1nm    | 20nm   | -                    |

| source &      |                  |        |        |        |                      |

| drain (f)     |                  |        |        |        |                      |

Table 3.1, shows the dimension of the different regions of the 14nm Heterojunction N-FinFET and figure 3.3, shows the 3 D view of the 14-nm Heterojunction N-FinFET.

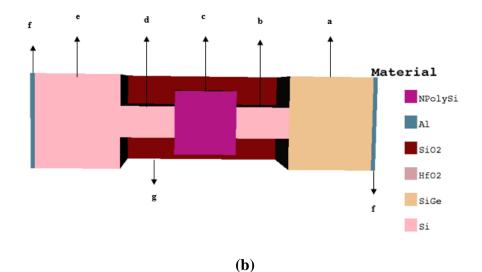

Fig 3.3 14-nm Heterojunction N-FinFET

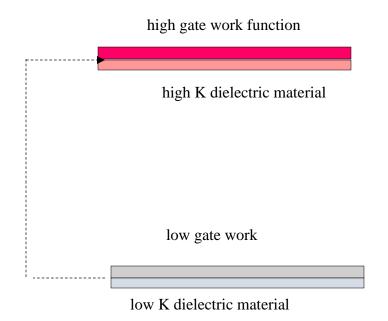

In the above device, we mainly focus on designing a FinFET structure that can show good performance in terms of reduction in short-channel effects and improved on current/off current ratio in comparison with the existing structure for smaller gate length. For the proposed design, hafnium oxide (HFO<sub>2</sub>) is used as an oxide material and has a higher value of dielectric and polysilicon material ( $\Phi_m = 4.25 \text{ eV}$ ) for a gate. As aluminum material ( $\Phi_m = 4.1 \text{ eV}$ ) used for making the contact of a substrate, source, and drain. In the same design, we covered the fin from three sides (top, right side, and left side) with oxide material then by gate material and work function value set at 4.17eV.

For designing the P-FinFET, we used the same dimension structure as used for the N-FinFET. Table 3.2 and figure 3.4 show the dimension and 3D view of the 14-nm Heterojunction P-FinFET. In the same design, we change the gate material with Npoly Silicon and the doping level of the source, drain, and channel region. Variation in the work function value in P-FinFET was done to match the features of both the devices P-FinFET and N-FinFET.

For both devices, a rectangular-shaped fin was used that was covered by the three sides of the oxide layer of  $HFO_2$  and then further covered by the gate material. This leads to control the short effect in the device and figure 3.5 represents the analytic expression of high-k dielectric with high work function for the same.

| Region of     | Material         | Region | Region | Region | Doping               |

|---------------|------------------|--------|--------|--------|----------------------|

| device        |                  | Length | Width  | Height | Level                |

| Extended      | Silicon-         | 13nm   | 10nm   | 20nm   | $1 x 10^{20} / cm^3$ |

| Source -1 (a) | Germanium        |        |        |        |                      |

|               | $(Si_{1-x}Ge_x)$ |        |        |        |                      |

| Extended      | Silicon          | 20nm   | 24nm   | 20nm   | $1 x 10^{20} / cm^3$ |

| Source-2 (b)  |                  |        |        |        |                      |

| Extended      | Silicon          | 13nm   | 10nm   | 20nm   | $1 x 10^{18} / cm^3$ |

| Drain-1 (e)   |                  |        |        |        |                      |

| Extended      | Silicon          | 20nm   | 24nm   | 20nm   | $1 x 10^{18} / cm^3$ |

| Drain-2 (d)   |                  |        |        |        |                      |

| Fin           | Silicon          | 14nm   | 10nm   | 20nm   | $1 x 10^{17} / cm^3$ |

| (Channel)     |                  |        |        |        |                      |

| Gate (c)      | NPolySi          | 14nm   | 2nm    | 23nm   | -                    |

| Oxide         | HFO <sub>2</sub> | 14nm   | 2nm    | 21nm   | -                    |

| Source &      | Aluminum         | 20nm   | 1nm    | 20nm   | -                    |

| Drain Contact |                  |        |        |        |                      |

| (f0           |                  |        |        |        |                      |

**Table 3.2**: Dimension of the Device Region of 14-nm Heterojunction P-FinFET

Fig 3.4 14-nm Heterojunction P-FinFET

In both designs, Heterojunction was created between the fin and extended source-2 by using the two different materials silicon and Silicon-Germanium  $(Si_{1-x} Ge_x)$ .

Fig 3.5 Analytic description of 14-nm Heterojunction N-FinFET

| Parameter of the Device  | Channel<br>Length (Lg)<br>(nm) | Fin Width<br>(W <sub>fin</sub> ) (nm) | Height of<br>Fin (H <sub>fin</sub> )<br>(nm) | Gate Oxide<br>thickness<br>(T <sub>ox</sub> ) (nm) |

|--------------------------|--------------------------------|---------------------------------------|----------------------------------------------|----------------------------------------------------|

| Proposed 14-nm           | 14                             | 10                                    | 20                                           | 2                                                  |

| Heterojunction FinFET    |                                |                                       |                                              |                                                    |

| Conventional FinFET [78] | 14                             | 10                                    | 20                                           | 2                                                  |

| Source Step-FinFET [77]  | 40                             | 14                                    | 40                                           | 1.5                                                |

| FinFET-1 [79]            | 20                             | 15                                    | 25                                           | 1                                                  |

| FinFET-2 [79]            | 5                              | 1                                     | 8                                            | 1                                                  |

Table 3.3:

Dimension of Compared Devices

The dimensions of various parameters for the standard FinFET, Source Step-FinFET, and the proposed 14-nm Heterojunction FinFET are listed in Table 3.3.

#### **3.3 PHYSICAL SIMULATION OF PROPOSED FINFET**

The Cogenda tool and the Lombard equation for device modeling [80] were used to generate all of the results and simulations. The doping-dependent mobility model was also utilized to investigate the impact of carrier mobility in the 14nm Heterojunction N-FinFET. The drift-diffusion model and Boltzmann statistics were utilized in this simulation [81]. The recombination rate is calculated using the sum of direct recombination and Shockley read hall recombination. While simulating the proposed design, Boltzmann statistics and the drift-diffusion model were used. The recombination rate is calculated by adding the results of Shockley read hall recombination and direct combination. Drift-diffusion equations, high field mobility dependency, doping dependent mobility degradations, Lombardi as a mobility model, and high field mobility dependency were all enabled during the simulation of the proposed device. We used a global command on the device to set the external temperature to 300K. Electron and hole concentrations were introduced to the simulation as shown in equations 3.1 [82].

$$\nabla_{n} = -((h^{2}\gamma n)/(6qm_{n}^{*})) * ((\nabla^{2}\sqrt{n})/(\sqrt{n}))$$

(3.1)

$$\nabla_{p} = -((h^{2}\gamma n)/(6qm_{p}^{*})) * ((\nabla^{2}\sqrt{p})/(\sqrt{p}))$$

(3.2)

Where p and n indicate electron concentration, hole concentration, and valance band in the conduction band, h and q represent Planck's constant and electron charge, while mn\* and mp\* represent hole and electron effective mass.

The relationship between the temperature and energy bandgap can be represented by equation 3 [83-84].

$$E_g(T) = E_g(0) - \alpha E T^2 / (T + \beta_E)$$

(3.3)

Where,  $\alpha$  for Si = 5.41×10-4 eV/K and Eg = 1.42 eV,  $\beta_E$  = 206 K

The term electrical width of FinFET is defined as

$$W = 2H_{fin} + T_{fin} \qquad (3.4)$$

Where  $H_{\text{fin}}$  represents fin-height and  $T_{\text{fin}}$  represents the fin-thickness.

Following the model was used while simulating the device.

a) Auger-Auger recombination has a three-particle transition in which the mobile carrier is either released or trapped. When an electron recombines, energy is transferred to the conduction band's third electron, which thermalizes near the conduction band's edge. Auger recombination was modeled using the following expression (3.5) [85].

$$R_{Auger} = C_n n(np - n_{ie}^2) + C_p p(np - n_{ie}^2)$$

(3.5)

Where p, n represent the concentration of hole and electron respectively and  $n_{ie}$  is intrinsic concentration,  $C_p$ ,  $C_n$  are constant. In the proposed design we used the standard model of auger recombination for both devices.

- b) Shockley Recombination (SRH) Recombination through defects is also known as Shockley Recombination. It's a two-part procedure.

- An electron or hole is caught by an energy level present in a forbidden gap due to crystal defects.

- The SRH recombination rate [86] happens when the hole reaches the same energy level as the electron before being thermally heated to the conduction band.

$$R_{SRH} = \frac{n_p - n_{ie}^2}{\tau_p (n + n_{ie} \, e^{(+ETRP/kT_L)}) + \tau_n (p + n_{ie} \, e^{(-ETRP/kT_L)})} \tag{3.6}$$

p and n are the electron and hole life cycles, n and p are the electron and hole concentrations,  $n_{ie}$  is the effective intrinsic concentration, and TL is the lattice temperature. ETRAP stands for the difference between the trap energy level and the intrinsic fermi level. The concentration-dependent SRH lifetime model calculates carrier lifetime as a function of impurity concentration.

c) Model of Lombardi mobility - The Lombardi models used in this work are a hybrid model that considers both low field and transverse field influences on mobility. The

effects of doping, temperature, and the inversion layer are also taken into account [86]. The mobilities of electrons and holes are represented as

$$\frac{1}{\mu} = \frac{1}{\mu_{\rm i}} + \frac{1}{\mu_{\rm s}} + \frac{1}{\mu_{\rm p}} \tag{3.7}$$

Carrier Mobility ( $\mu$ ) depend on the phonon scattering ( $\mu_p$ ), surface roughness scattering ( $\mu_s$ ) and ionized impurity scattering ( $\mu_i$ ). Equation 3.7 shows the mathematic formula of carrier mobility ( $\mu$ ).

## 3.4 TRANSFER CHARACTERISTICS OF 14-nm HETEROJUNCTION N-FINFET.

Different performance parameters of the device were analyzed for the 14-nm Heterojunction N-FinFET.

a) Drain current of the device calculated as per equation 3.8

$$I_{d} = \emptyset + \mu C_{ox} \left(\frac{W_{g}}{L_{g}}\right) \left(\frac{(V_{gs} - V_{th})}{2m}\right)$$

(3.8)