## MODELLING, SIMULATION AND VALIDATION OF ACTIVE SEMICONDUCTOR DEVICES USING FLOATING ADMITTANCE TECHNIQUE

A Thesis

Submitted in partial fulfilment of the requirements for the award

of the degree of

### **DOCTOR OF PHILOSOPHY**

in

**Electronics and Communication Engineering**

By

SANJAY KUMAR ROY (41900208)

Transforming Education Transforming India

**Supervised By**

### Dr. KAMAL KUMAR SHARMA

# LOVELY PROFESSIONAL UNIVERSITY PUNJAB 2022

## DECLARATION

I declare that the thesis entitled, "Modelling, Simulation and Validation of Active Semiconductor Devices using Floating Admittance Technique" under the guidance of Dr. Kamal Kumar Sharma, Professor, School of Electronics and Communication Engineering, Lovely Professional University, Punjab, India, No part of this thesis has formed the basis for the award of a degree or fellowship previously.

I further declare that there is no falsification or manipulation in terms of research materials, equipment or process, experiments, methods, modelling, data, data analysis, results, or theoretical work.

I have checked the thesis using Turnitin for ensuring that there is no plagiarised material in my thesis and whenever any copyrighted material has been included, the same been duly acknowledged.

Sanjay Kumar Roy School of Electronics and Electrical Engineering Lovely Professional University Phagwara, Punjab Date: 05/08/2022

## CERTIFICATE

It is to certify that **Sanjay Kumar Roy** (**41900208**) has completed the scientific formulation of the thesis entitled, "**Modelling, Simulation and Validation of Active Semiconductor Devices using Floating Admittance Technique**" under my guidance and supervision. To the best of my knowledge, the present work is the result of their original investigation and study. No part of the thesis has ever been submitted for any other degree at any University.

Dr. Kamal Kumar Sharma Professor School of Electronics and Electrical Engineering Lovely Professional University, Phagwara, Punjab

## ACKNOWLEDGMENT

First, I would like to express my gratitude to my supervisor, Dr Kamal Kumar Sharma, for his supervision, advice, and guidance, as well as for giving me extraordinary suggestions throughout the work. Special thanks to my previous supervisors, Dr Cherry Bhargava, and Dr Manwinder Singh. I am very fortunate to have the opportunity to work with them. I found that their guidance is precious. It is our pleasure to be indebted to various people who directly or indirectly contributed to this work's development and influenced our thinking, behaviour, and acts during the study. I am great full to my friend and colleague for their constructive suggestion. I want to thank the School of Electronics and Electrical Engineering, Lovely Professional University, for providing me with a suitable research environment to carry out the research work. I want to thank my wife Rita, my son and daughter-in-law Kaushik & Poonam and Kinshuk, and my father and mother-in-law for their moral support.

Sanjay Kumar Roy School of Electronics and Electrical Engineering Lovely Professional University Phagwara, Punjab Date: 05/08/2022

|                                                                                  | Page N0. |

|----------------------------------------------------------------------------------|----------|

| TABLE OF CONTENTS                                                                | i        |

| I. List of Figures                                                               | iii-v    |

| II. List of Abbreviation                                                         | vi       |

| III. List of Table-Table 1.1 Time Constants of RC Integrator                     | 39       |

| Abstract                                                                         | 1-3      |

| Organisation of the Thesis                                                       | 4        |

| Chapter 1 Modelling: Review of the Literature                                    | 5        |

| 1.1 Introduction                                                                 | 5        |

| 1.2 Objectives                                                                   | 6        |

| 1.3 Mathematics in modelling                                                     | 10       |

| 1.4 Modelling of physical Environment                                            | 10       |

| 1.5 Advantages of modelling                                                      | 12       |

| 1.6 Background of modelling                                                      | 20       |

| 1.7 Building blocks of modelling                                                 | 20       |

| 1.8 Classification of mathematical models                                        | 20       |

| 1.9 Priori information of models                                                 | 22       |

| 1.10 Subjective Information of models                                            | 23       |

| 1.11 Complexity of models                                                        | 24       |

| 1.12Training of models                                                           | 25       |

| 1.13 Model Evaluation                                                            | 25       |

| <ul><li>1.14 Model Fitting of empirical data</li><li>1.15 Models Scope</li></ul> | 25<br>26 |

| 1.16 Philosophical considerations of models                                      | 20<br>26 |

| 1.17 Conclusion                                                                  | 20       |

| Reference                                                                        | 28       |

| Chapter 2 Generation of Transfer Function (Two-Port Model)                       | 20<br>30 |

| 2.1 Introduction                                                                 | 30       |

| 2.2 Two-port Network Model                                                       | 31       |

| 2.3 Two-port Network Model Parameters                                            | 32       |

| 2.4 Model development of Two-Port Network                                        | 35       |

| 2.5 Model specifications                                                         | 37       |

| 2.6 Large signal model                                                           | 39       |

| 2.7 Small-signal model                                                           | 40       |

| 2.8 Low frequency model                                                          | 42       |

| 2.9 High frequency model                                                         | 43       |

| 2.10 Floating admittance model                                                   | 44       |

| 2.11 First Order Cofactor of Matrix Model                                        | 54       |

| 2.12 Second Order Cofactor of Matrix Model                                       | 55       |

| 2.13 Transfer function model of two port Network                                 | 56       |

| 2.14 Self-admittance model of two port Network                                   | 60       |

| 2.15 conclusion                                                                  | 63       |

| References                                                                       | 64       |

| Chapter 3 Modelling of the BJT Amplifiers                                        | 66       |

| 3.1 Introduction                                                                 | 66       |

| 3.2 Small-signal model development of the BJT                                    | 67       |

| 3.3 Circuit Model of CE for Input Resistance                                     | 70       |

| 3.4 Circuit Model of CB for Input Resistance                                     | 71       |

| 3.5 T-model of the BJT                                                 | 72      |

|------------------------------------------------------------------------|---------|

| 3.6 Hybrid- $\pi$ Circuit model of the BJT                             | 73      |

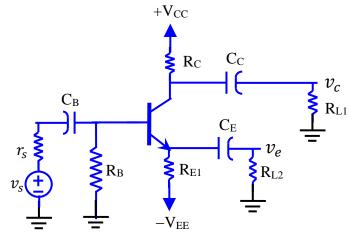

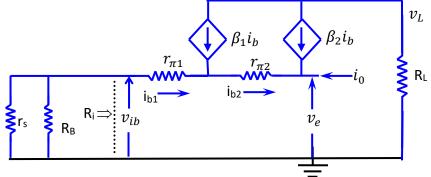

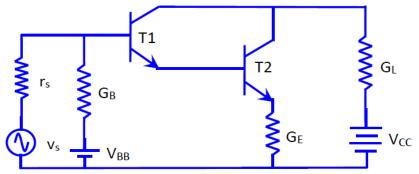

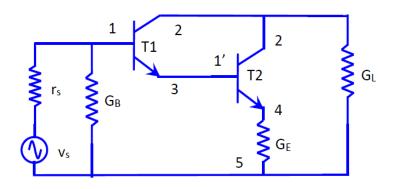

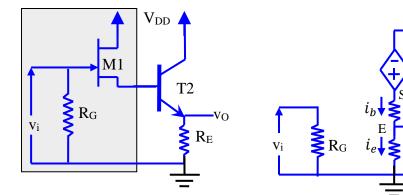

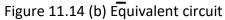

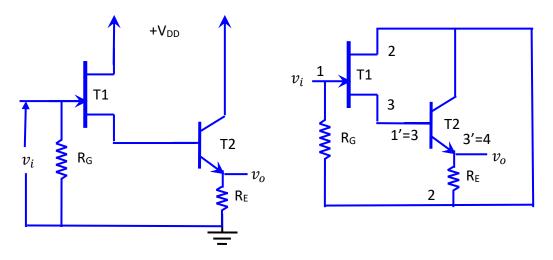

| 3.7 Circuit Model of the BJT Phase-splitter amplifier                  | 74      |

| 3.8 Circuit Model of Common-Emitter amplifier                          | 78      |

| 3.9 Circuit Model of Common-collector amplifier                        | 80      |

| 3.10 Circuit Model of Common-base amplifier                            | 84      |

| 3.11 Circuit Model of BJT phase-splitter amplifier (complete analysis) | 87      |

| 3.12 Simulation and Validation of Common Emitter Amplifier             | 91      |

| 3.13 Conclusion                                                        | 92      |

| References                                                             | 92      |

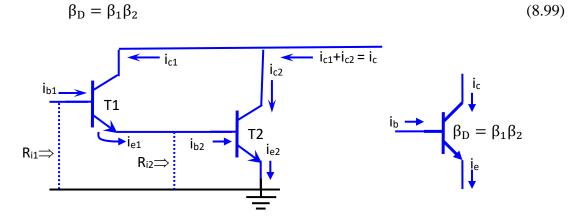

| Chapter 4 Modelling of the FET Amplifiers                              | 95      |

| 4.1 Introduction                                                       | 95      |

| 4.2 FET Small-Signal Equivalent model                                  | 100     |

| 4.3 Circuit Model of FET Common-source amplifier                       | 103     |

| 4.4 Circuit Model of FET Common-Drain Amplifier                        | 106     |

| 4.5 Circuit Model of FET Common-Gate Amplifier                         | 110     |

| 4.6 Circuit Model of FET Phase-splitter amplifier (complete analysis)  | 113     |

| 4.7 Conclusions                                                        | 119     |

| References                                                             | 119     |

| Chapter 5 Modelling of the Four Terminal MOSFET Amplifiers             | 121     |

| 5.1 Introduction                                                       | 121     |

| 5.2 Development of FAM Model for 4-terminal MOSFET                     | 122     |

| 5.3 Small-Signal model development of the MOSFET                       | 127     |

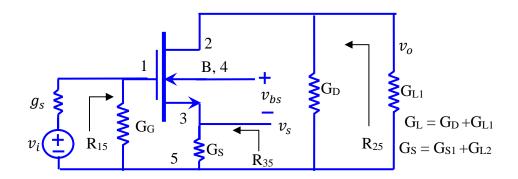

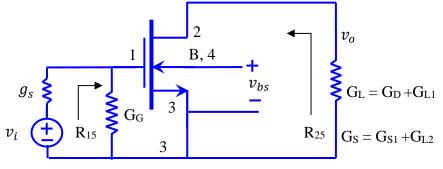

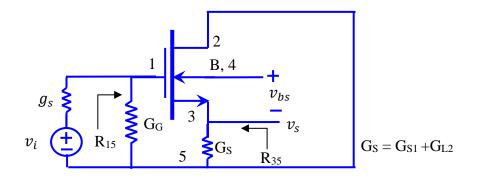

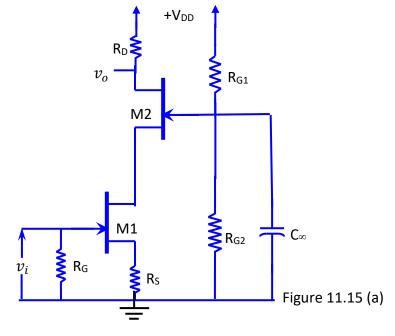

| 5.4 Circuit Model of a 4- terminal MOSFET phase-splitter amplifier     | 127     |

| 5.5 Circuit Model of a 4-Terminal MOSFET CS Amplifier                  | 129     |

| 5.6 Circuit Model of a 4-Terminal MOSFET CD amplifier                  | 132     |

| 5.7 Circuit Model of a 4-Terminal MOSFET CG amplifier                  | 135     |

| 5.8 Circuit Model of a 4-Terminal MOSFET Phase-Splitter amplifier      | 138     |

| 5.9 Conclusion                                                         | 142     |

| References                                                             | 143     |

| Chapter-6 Conclusions                                                  | 145-148 |

| Future Scope of Work                                                   | 148     |

| Annexure 2(All Published Papers in pdf)                                | 149     |

| Annexure 3(comparison of Conventional and FAM Method)                  | 150-166 |

## Table 1 List of Figures:

| S.N. | Figures Name                                                                 | page  |  |  |  |

|------|------------------------------------------------------------------------------|-------|--|--|--|

| 1.   | Fig. 1.1 An Effective Engineering Program model                              | 11    |  |  |  |

| 2.   | Fig. 1.2 Model of a RC Integrator                                            |       |  |  |  |

| 3.   | Fig. 1.3 Model of RC Integrator Response with step Input                     |       |  |  |  |

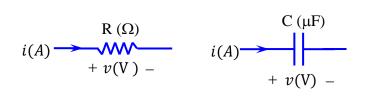

| 4.   | Fig. 1.4 Model of Resistor, Capacitor, and Inductor                          |       |  |  |  |

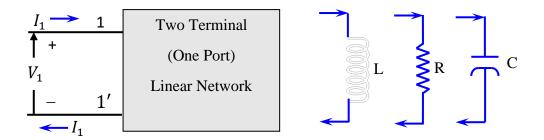

| 5.   | Fig. 2.1 Model of Two Terminal Network                                       | 31    |  |  |  |

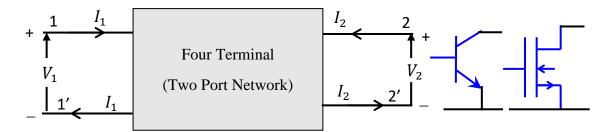

| 6.   | Fig. 2.2(a) Model of Two-port Network                                        | 31    |  |  |  |

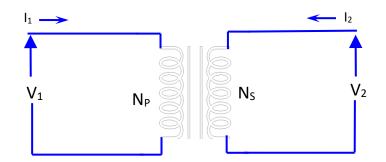

| 7.   | Fig. 2.2(b) Model of Single-Phase Transformer                                | 32    |  |  |  |

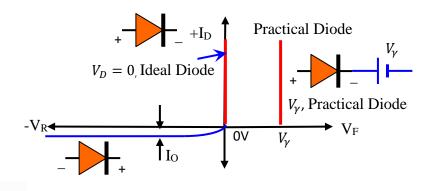

| 8.   | Fig. 2.3 Large-Signal Models of Semiconductor Diode                          | 39    |  |  |  |

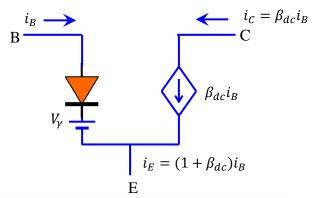

| 9.   | Fig. 2.4 Large Signal Model of the BJT                                       | 40    |  |  |  |

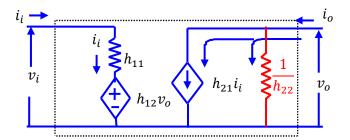

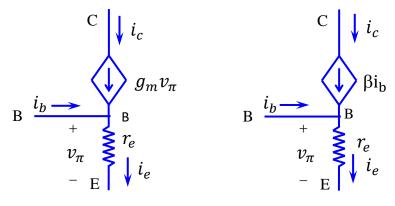

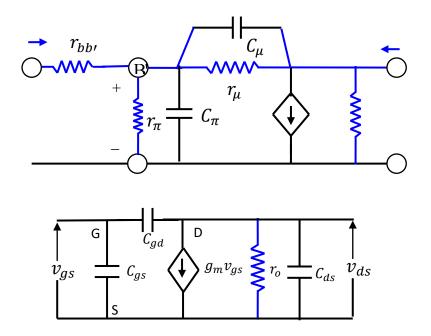

| 10.  | Fig. 2.5 Small-signal models of the BJT & FET                                | 41-42 |  |  |  |

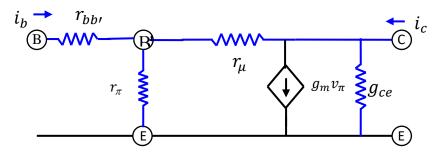

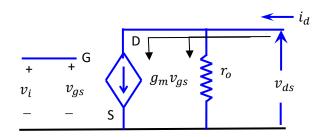

| 11.  | Fig. 2.6 Low-Frequency symbolic Models of the BJT & MOSFET                   |       |  |  |  |

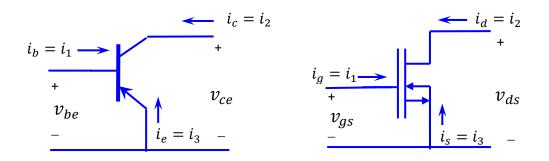

| 12.  | Fig. 2.7 High-Frequency Circuit Models of the BJT & MOSFET                   |       |  |  |  |

| 13.  | Fig. 2.8 High-Frequency models of the BJT and FETs/ MOSFETs                  |       |  |  |  |

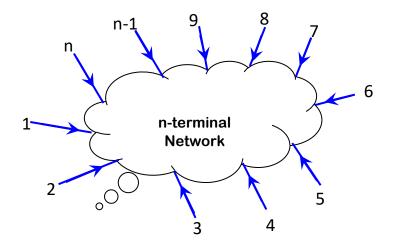

| 14.  | Fig. 2.9 n-Terminal Network Model                                            | 45    |  |  |  |

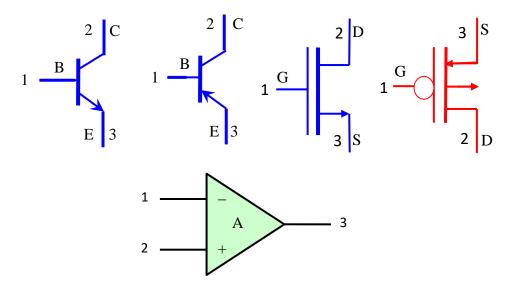

| 15.  | Fig. 2.10 Physical Model of the BJT, MOSFET, Op-Amp                          | 51    |  |  |  |

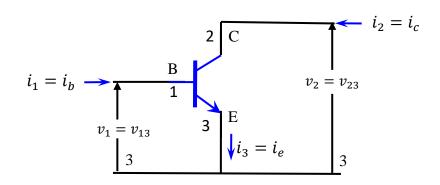

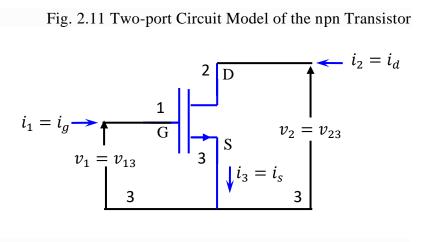

| 16.  | Fig. 2.11 Two-Port Circuit Model of npn Transistor                           | 52    |  |  |  |

| 17.  | Fig. 2.12 Two-Port Circuit Model of a n-channel MOSFET                       | 52    |  |  |  |

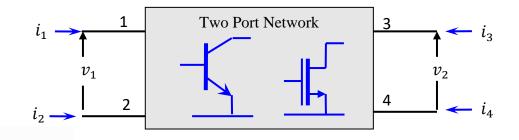

| 18.  | Fig. 2.13 Generalized 2-Port Network Model                                   | 52    |  |  |  |

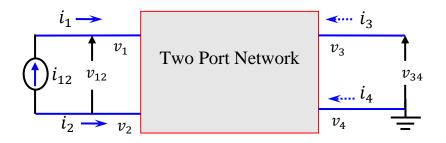

| 19.  | Fig. 2.14 Two-Port Network Model with $V_4 = 0$                              | 56    |  |  |  |

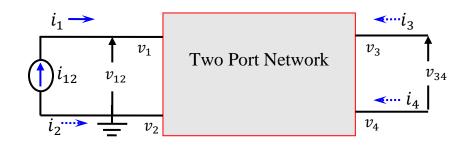

| 20.  | Fig. 2.15 Two-Port Network Model with $V_2 = 0$                              | 60    |  |  |  |

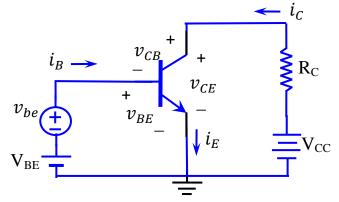

| 21.  | Fig. 3.1 Circuit Model of the BJT Amplifier with DC and AC Superimposed      | 67    |  |  |  |

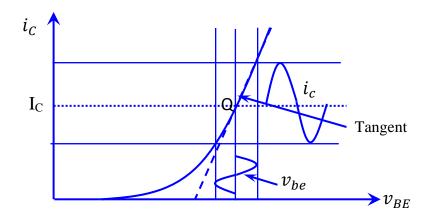

| 22.  | Fig. 3.2 Graphical Model Representation of $I_c VS V_{BE}$                   | 69    |  |  |  |

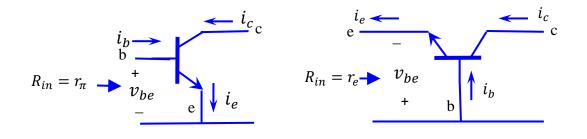

| 23.  | Fig. 3.3 Circuit Symbol Model of the BJT in (a) CE and (b) CB Configurations | 70    |  |  |  |

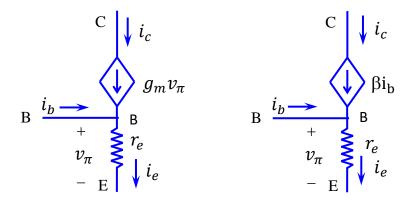

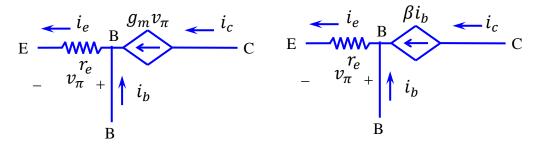

| 24.  | Fig. 3.4 (a) Vertical and (b) Horizontal Circuit Model of The BJT            | 72    |  |  |  |

| 25.  | Fig. 3.4 (c) Vertical T-model Circuit of the BJT including $r_o$             | 73    |  |  |  |

| 26.  | Fig. 3.4 (d) hybrid- $\pi$ circuit model of the BJT including $r_o$          | 73    |  |  |  |

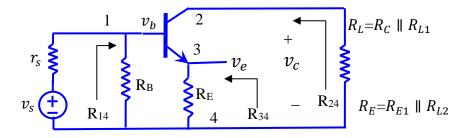

| 27.  | Fig. 3.5 Circuit Model of BJT phase-splitter Amplifier                       | 75    |  |  |  |

| 28. | Fig. 3.6 AC Circuit model of the BJT Phase-Splitter Amplifier                                                                                         | 75    |  |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|

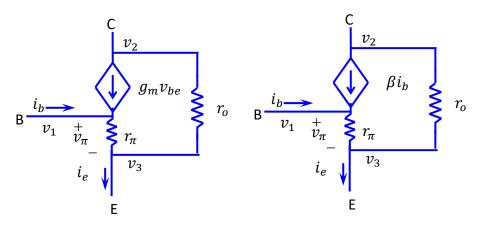

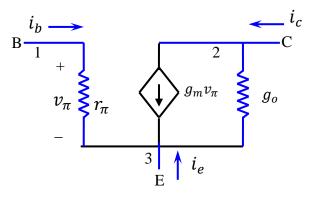

| 29. | Fig. 3.7 AC Circuit Model of common-emitter amplifier                                                                                                 | 78    |  |  |  |

| 30. | Fig. 3.8 AC Circuit Model of Common-Collector Amplifier                                                                                               | 82    |  |  |  |

| 31. | Fig. 3.9 AC Circuit Model of Common-Base Amplifier                                                                                                    | 85    |  |  |  |

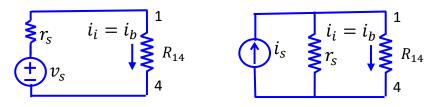

| 32. | Fig. 3.10 Model of Voltage Source Conversion to Current Source                                                                                        | 89    |  |  |  |

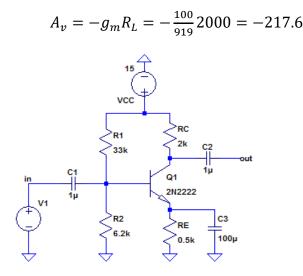

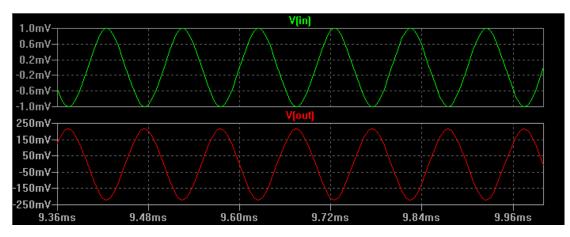

| 33. | Fig. 3.11 LTSpice Circuit Model for Common Emitter Amp.                                                                                               | 91    |  |  |  |

| 34. | Fig. 3.12 LTSpice Response of Common Emitter Amplifier                                                                                                | 92    |  |  |  |

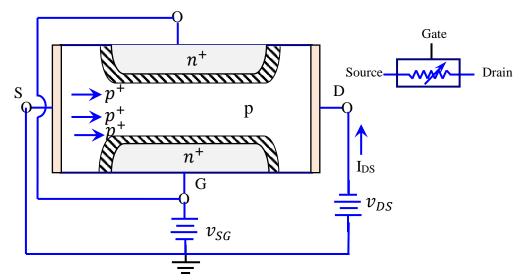

| 35. | Fig. 4.1 Cross-Section of a symmetrical n-channel JFET Model                                                                                          | 95    |  |  |  |

| 36. | Fig. 4.2 Cross-section of a symmetrical p-channel JFET Model                                                                                          | 96    |  |  |  |

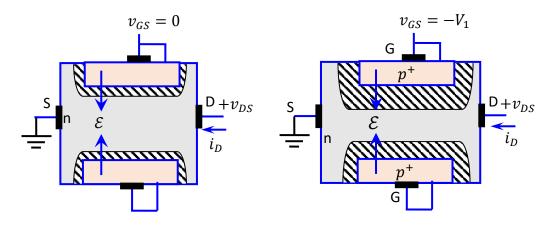

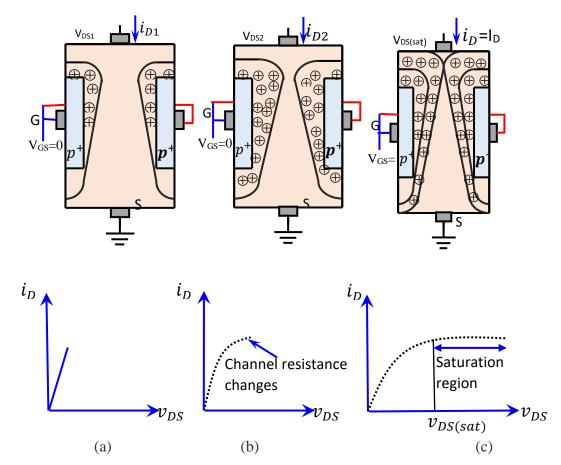

| 37. | Fig. 4.3 Space-Charge Model of FET for a Small $v_{DS}$ with (a) Zero Gate Voltage, (b) Small Gate Voltage, and (c) Pinch-Off Gate Voltage.           | 96-97 |  |  |  |

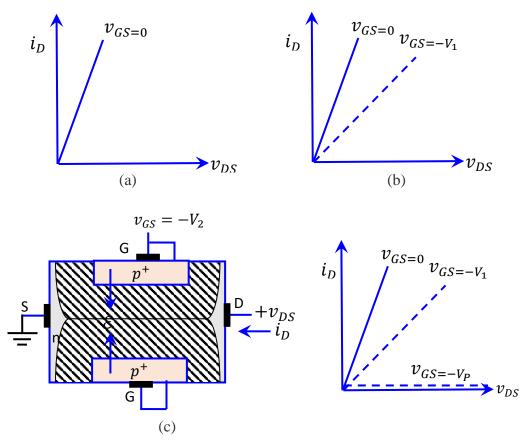

| 38. | Fig. 4.4 Illustration of physical pinch-off Model of JFET                                                                                             | 98    |  |  |  |

| 39. | Fig. 4.5 Space-Charge Model of JFET With Zero Gate Voltage for<br>(a) Small Drain Voltage (b) Large Drain Voltage and (c) Pinch-Off<br>Drain Voltage. | 99    |  |  |  |

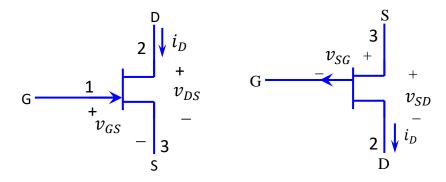

| 40. | Fig. 4.6 Circuit Symbol Model of a <i>three</i> -terminal FETs                                                                                        |       |  |  |  |

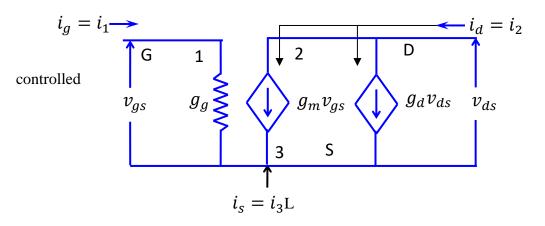

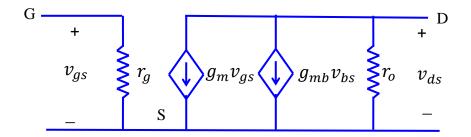

| 41. | Fig. 4.7 Current Source small signal model of a three-terminal FET                                                                                    | 101   |  |  |  |

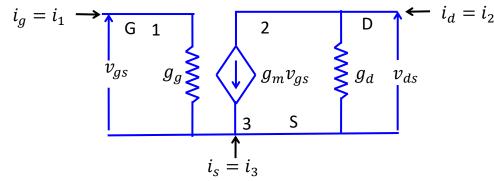

| 42. | Fig. 4.8 Modified small-signal model of a three-terminal JFET                                                                                         | 101   |  |  |  |

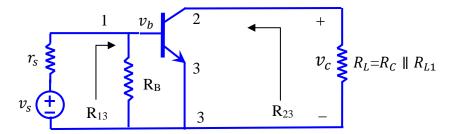

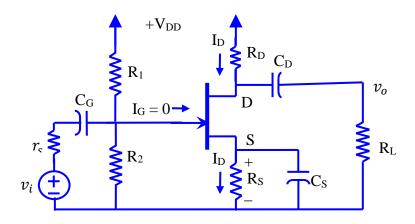

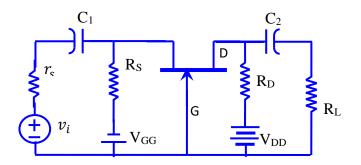

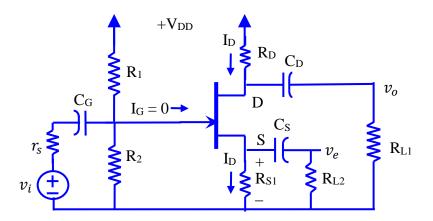

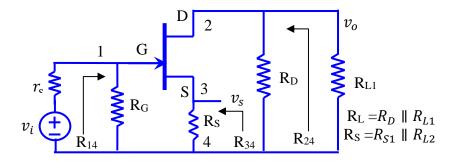

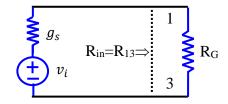

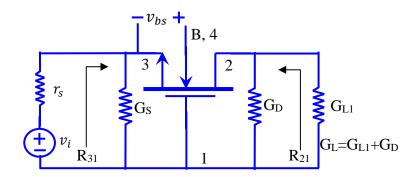

| 43. | Fig. 4.9 Circuit Model of Common-source FET Amplifier                                                                                                 | 103   |  |  |  |

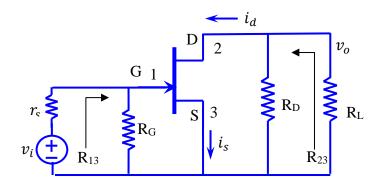

| 44. | Fig. 4.10 AC Circuit Model of CS Amplifier                                                                                                            | 104   |  |  |  |

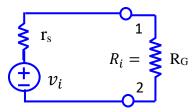

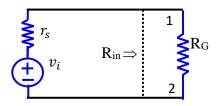

| 45. | Fig. 4.11 Effective Voltage Gain Model with $R_i = R_{13} = R_G$                                                                                      | 105   |  |  |  |

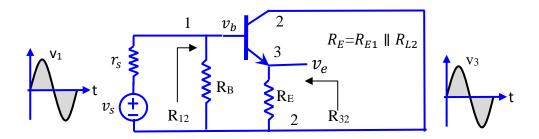

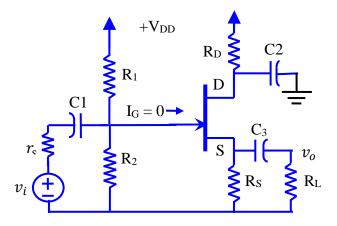

| 46. | Fig. 4.12 Circuit Model of Source Follower Amplifier                                                                                                  | 107   |  |  |  |

| 47. | Fig. 4.13 AC Circuit Model of Source Follower Amplifier                                                                                               | 107   |  |  |  |

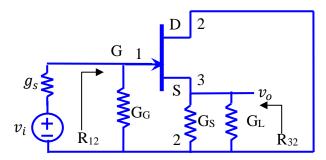

| 48. | Fig. 4.14 Effective Voltage Gain Model with $R_i = R_{12} = R_G$                                                                                      | 109   |  |  |  |

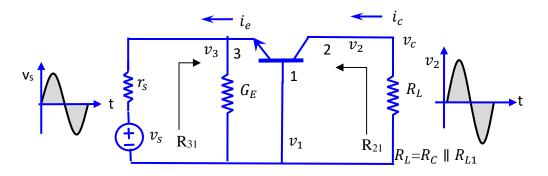

| 49. | Fig. 4.15 Circuit Model of Common-gate FET Amplifier                                                                                                  | 110   |  |  |  |

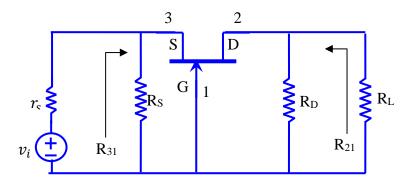

| 50. | Fig. 4.16 AC Circuit Model of CG FET Amplifier                                                                                                        | 110   |  |  |  |

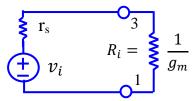

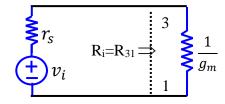

| 51. | Fig. 4.17 Effective Voltage Gain Model with $R_i = R_{31} = \frac{1}{g_m}$                                                                            | 112   |  |  |  |

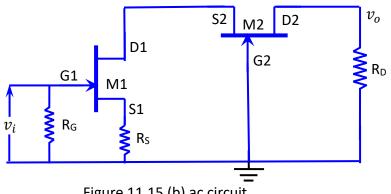

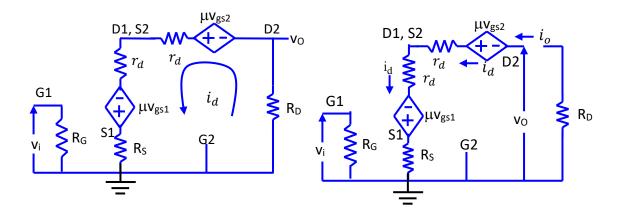

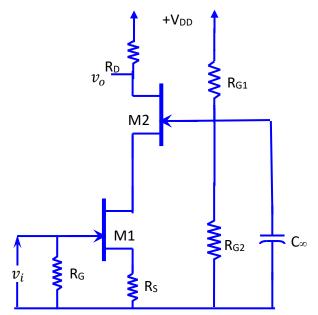

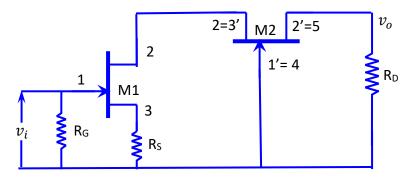

| 52. | Fig. 4.18 Circuit Model of FET Phase-Splitter amplifier                                                                                               | 114   |  |  |  |

| 53. | Fig. 4.19 AC Circuit Model of FET Phase-Splitter amplifier                                                                                            | 114   |  |  |  |

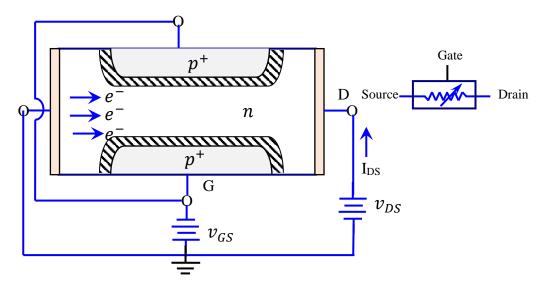

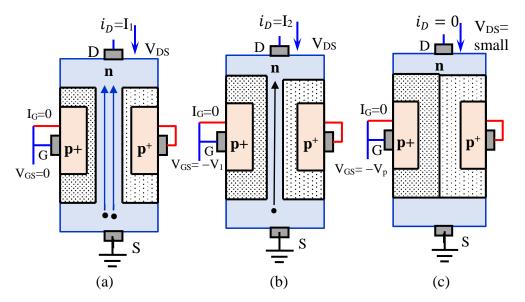

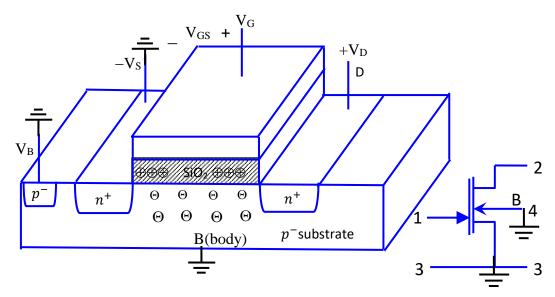

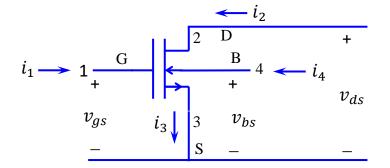

| 54. | Fig. 5.1 Physical Model of The nMOSFET                                                                                                                | 122   |  |  |  |

|     |                                                                                                                                                       |       |  |  |  |

| 55. | Fig. 5.2 Circuit Symbol Model of 4-Terminal nMOSFET with (a)                                                  | 123 |  |  |

|-----|---------------------------------------------------------------------------------------------------------------|-----|--|--|

|     | DC and (b) AC Voltages                                                                                        |     |  |  |

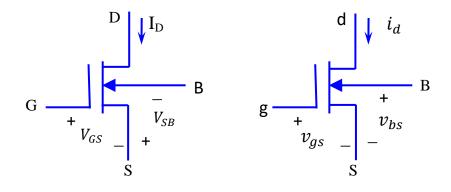

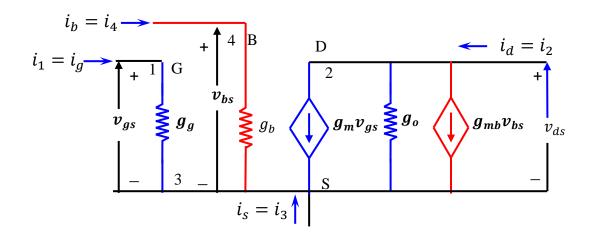

| 56. | Fig. 5.3 Small-signal model of the nMOSFET with the body effect.                                              | 124 |  |  |

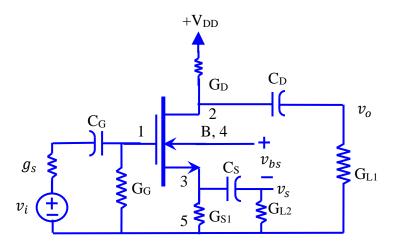

| 57. | Fig. 5.4 Circuit Model of a 4-Terminal CS MOSFET Amplifier                                                    | 125 |  |  |

| 58. | Fig. 5.5 Small-signal model of 4-Terminal MOSFET with $V_{SB} \neq 0$                                         |     |  |  |

| 59. | Fig. 5.6 Circuit Model of a 4-Termanal MOSFET Phase-splitter Amp                                              | 128 |  |  |

| 60. | Fig. 5.7 AC Circuit Model of MOSFET phase-splitter Amplifier                                                  | 128 |  |  |

| 61. | Fig. 5.8 AC Circuit Model of a 4-TERMAINAL MOSFET CS Amp                                                      | 130 |  |  |

| 62. | Fig. 5.9 Effective Voltage Gain Model with Source Voltage and Resistance of a 4-Termianal MOSFET CS Amplifier | 131 |  |  |

| 63. | Fig. 5.10 AC Circuit Model of a 4-Terminal MOSFET CD Amp.                                                     | 133 |  |  |

| 64. | Fig. 5.11 Effective Voltage Gain Model with Source Voltage and Resistance of a 4-Terminal MOSFET CD Amplifier |     |  |  |

| 65. | Fig. 5.12 Circuit Model of a 4-Termanal CG MOSFET Amplifier                                                   | 136 |  |  |

| 66. | Fig. 5.13 Effective Voltage Gain Model with Source Voltage and Resistance of a 4-terminal MOSFET CG Amplifier | 137 |  |  |

| S.N. | Abbreviations                                 | Stands for                                        |  |  |

|------|-----------------------------------------------|---------------------------------------------------|--|--|

| 1    | FAM                                           | Floating Admittance Matrix                        |  |  |

| 2    | BJT                                           | Bipolar Transistor                                |  |  |

| 3    | FET                                           | Field Effect Transistor                           |  |  |

| 4    | MOSFET                                        | Metal Oxide Semiconductor Field Effect Transistor |  |  |

| 5    | $A_v$                                         | Voltage gain without source resistance            |  |  |

| 6    | $A_{vs}$                                      | Voltage gain with source resistance               |  |  |

| 7    | $A_i$                                         | Current gain                                      |  |  |

| 8    | $A_P$                                         | Power gain                                        |  |  |

| 9    | R <sub>in</sub>                               | Input resistance                                  |  |  |

| 10   | R <sub>o</sub>                                | Output resistance                                 |  |  |

| 11   | CE                                            | Common Emitter                                    |  |  |

| 12   | CB                                            | Common Base                                       |  |  |

| 13   | CC                                            | Common Collector                                  |  |  |

| 14   | CS                                            | Common Source                                     |  |  |

| 15   | CD                                            | Common Drain                                      |  |  |

| 16   | CG                                            | Common Gate                                       |  |  |

| 17   | $I_B, i_b$                                    | DC and AC base currents                           |  |  |

| 18   | <i>I</i> <sub>C</sub> , <i>i</i> <sub>c</sub> | DC and AC collector currents                      |  |  |

| 19   | I <sub>E</sub> , i <sub>e</sub>               | DC and AC emitter currents                        |  |  |

| 20   | $V_B$ , $v_b$                                 | DC and AC base voltages                           |  |  |

| 21   | $V_c, v_c$                                    | DC and AC collector voltages                      |  |  |

| 22   | $V_E$ , $v_e$                                 | DC and AC emitter voltages                        |  |  |

| 23   | V <sub>CC</sub> , V <sub>DD</sub>             | DC collector and Drain supply voltages            |  |  |

| 24   | $\pm V_{BB}$                                  | Base supply voltage                               |  |  |

| 25   | $-V_{EE}, V_{SS}$                             | Emitter and Source supply voltages.               |  |  |

| 26   | Int. J.                                       | International Journal                             |  |  |

Table 2 List of Abbreviations

## Abstract

The dynamics of any system, whether *mechanical, electrical, thermal, economical, biological* and so on, may be described in terms of difference or differential or integral equations. Such equations may be obtained by using physical laws governing a particular system, for example, Newton's laws for mechanical systems, Kirchhoff's laws for electrical systems, etc. We should continually keep in mind that deriving a reasonable, if not the best, mathematical model is an essential part of the complete analysis of any system.

The modelling assumes many different forms. Depending on the particular system and circumstances, one model may be better suited than others in given conditions. For example, using the state-space model in the optical control modelling is advantageous. On the other hand, the transfer function representation may be more convenient than any other for a transient response or the frequency response analysis of single-inputsingle-output, linear time-invariant systems. After developing the mathematical model of a system, various analytical and computational tools can be used for analysis and synthesis purposes.

Models of any system in science come in a wide variety of forms. The well-known modelling expert, Babour G. Ian, lists four types of models in his extensive discussion of models. According to him, different modelling types are categorised under one of the following methods: *material model, mathematical models, logical models, theoretical models*. The simplified scaled-down or up miniatures, e.g., the wind tunnels, hydrodynamic models or analogue models, e.g., an electric circuit having the same behaviour as a mechanical system of springs & dampers, are available in the literature. They are helpful when it is too difficult to experiment on the actual system or when the mathematical equations are unknown or too complex to solve. Some models can be better than others, but that model also gives an idea of the functioning of the physical behaviour of any system.

A set of equations describes the mathematical model of a system's behaviour's functioning. We focus on developing dynamic models that will ultimately result in

differential equations. How to represent such differential equations in the form of a block diagram? It is not possible to develop a precise model of any Physical system. Many processes cannot be modelled even. So Model error or model **uncertainties** occur. Even if a model describes a part of the reality, it can be very useful for analysis and design if it describes the dominating dynamic properties of the system. Some models are based on the physical principles of the system. Models can also be developed from experimental (historical) data. This way of mathematical modelling is called system identification.

Most of the books on electronic circuits deal with the analysis of various types of passive and active circuits (containing BJTs, FETs, MOSFETs, and Operational Amplifiers) in the conventional way of replacing the BJTS, FETs, MOSFETs, and Operational Amplifiers by its small-signal equivalent circuits. Then the well-known tools of KCL, KVL, Thevenin's, Norton's etc., are taken to advantage for the solution of the given network. Chirlian. P. "Electronic Circuits-Physical Principles Analysis and Design" proposed a generalised network analysis method containing the BJTs, FET, MOSFETs, and Operational Amplifiers.

The model proposed by Chirlian was so general that this method seemed to be very cumbersome. The proposed work defines different functions of electronic circuits, the active ones, to solve them elegantly using the Floating Admittance Matrix (*FAM*) approach. This matrix is called floating as because the reference terminal (ground) for the potential is arbitrary and lies outside the selected multi-pole network. For any network solution, the floating admittance matrixes of active and passive networks are written separately and then merged according to the node numbers. Once the overall floating admittance matrix of the complete amplifier or any circuit (active device and passive components) is obtained, its various transfer and self-port functions such as the input impedance (resistance), the output impedance (resistance), the voltage gain, the current gain and the power gains are obtained in terms of the co-factors of the derived floating admittance matrix. The voltage-current relationship for even complicated passive networks is usually linear, and hence, the solution of such a network is simple, using well-known tools like the KCL, the KVL, the Thevenin's, the Norton's etc.

On the contrary, electronic devices such as the BJT, FET, MOSFET, and Operational Amplifier are governed by current-voltage relationships that are typically nonlinear and somewhat complex. In general, it is not easy to analyse devices that obey nonlinear equations because there are much less developed design methods for circuits that include these devices. The basic concept of modelling of an electronic device is to replace the device as the circuit with linear components that approximate the voltagecurrent characteristics of the device as the *piecewise linear* models. A model can then be defined as a collection of simple components or elements used to represent a more complex electronic device. Once the device is replaced in the circuit by the model, wellknown tools for the circuit analysis can be applied.

The necessity of modelling for engineering lies in the very nature of technology and its advancement. As technology approaches its limit, i.e. fundamental changes do not occur as used to occur previously, and the engineers have to find a suitable substitute.

Our aim is to simplification of the analog circuit combining BJT, FET, MOSFET, and their combinations along with resisters and capacitors using properties of the Floating Admittance Matrix (FAM) technique. The gist of the development of the Thesis reviles as following.

- We have developed formulae for the Voltage gain, Current gain, Input Impedance, Output Impedance, and Power Gain using our technique (FAM) for all types of Circuit using BJT, FET/MOSFET, Op-Amp including resistances and Capacitances in the form of its cofactors.

- 2) Solving Complicated Circuits such as Twin-T and Bridge T Networks is a very good example of applying our technique for achieving a simple solution.

- The Zero-Sum Property of all elements of any Row or any Column of FAM satisfies the superposition theorem.

- Once the FAM of any network is written, it is easy to find out transfer or self-port functions between as many ports as possible.

- We have shown that the FAM technique to solve cascaded or cascoded circuits become very easy with respect to conventional Methods.

### **Organization of the Thesis**

The thesis has been divided in six chapters. The first chapter deals with the modelling technique vis-à-vis literature survey. All types of transfer (voltage gain, current gain, power gain) or self-port functions (input and output resistances) have been derived in Chapter-2 in the form of cofactors of the floating admittance matrix of any circuit. Chapters-3 and 4 show the beauty of the FAM to obtain all types of transfer and self-node functions easily in the form of cofactors only of the BJT and the FET/MOSFET amplifiers. Chapter-5 discusses the drawback of the four terminal MOSFET, if its body is not connected to the source terminal and this effect is included on its small-signal model. Thus, all the four terminals of a MOSFET play active role in functioning of the MOSFET. The sixth chapter is devoted the discussion and conclusion derived from Chapter-1 to Chapter-5.

## **Chapter 1**

### **Modelling: Review of Literature**

### **1.1 Introduction**

We start with the question 'what is modelling'? Modelling is the process of making models. Its most straightforward answer would be that models are often simplified versions of a complicated one. We might have played with a small toy car during our childhood. It can be called a model of an actual car. They gave us a unique idea of what a real car looks like, but they are much smaller and oversimplified. A model cannot always be accurate. We must realize this so that we do not build up an incorrect idea about something.

One way of defining the model is that it is the essential theoretical construct of anything. It exists in our brain, and we use it to explain how the phenomena of any object work. What is gravity? It is almost like a black box or an abstract. We cannot touch it, but we get to develop models that help us to predict it. What was the gravity for Einstein? What was he doing when the model was already developed by Sir Isaac Newton? He was looking at the construct of the model. He was able to improve on that model based on the data he had received. So why does an apple fall to the Earth? It is not that there is some magical force pulling it there. What did Einstein say that they are wrapping time and these objects are travelling through the shortest path? Was he able to confirm that using data? Yes.

The model of any system might be of different in nature. It is important to note that a model is not the real world but merely a human construct to understand realworld systems better. In general, all models include information input, an information processor, and the output of expected results.

The models are inherently inexact as they only approximate natural phenomena. The mathematical description may be imperfect, and/or our understanding of the phenomenon may or may not be complete. The mathematical input parameters used in models to represent real processes might be uncertain as these input parameters are empirically determined or represent multiple input/output. Additionally, the initial conditions and/or the boundary conditions in a model may not be exactly known.

Despite the above-stated weaknesses, models are effective tools for describing natural processes. Often, models are the only means to extrapolate to large spatial scales. Because of their importance in the earth sciences, we assess model accuracy by calibrating and validating models. To quantify the model's uncertainty, we correlate the result's sensitivity to the model parameters.

It is well known that an atom is the smallest part of the element that can further be divided by nuclear reactions only. An atom is an ensemble of the smallest particles of energy that make up everything on the Earth. A variety of models have been used over the past decades to speculate on how an atom works and what particles it contains.

Before more discussion here, we describe first, the 4-research objectives to formulate the problem statement for the thesis. The third and the fourth objectives have been implemented in the papers published, which forms the basis of the problem statements.

#### **1.2 Objectives**

# **Objective 1:** *Design to formulate the mathematical model for active semiconductor devices.*

The proposed technique of the floating admittance matrix is an elegant mathematical modelling approach for both active and passive circuits. The fundamental benefit of the floating admittance matrix approach is that the algebraic sum of all elements in any row or column producing zero serves as a preliminary check that the circuit analysis and design process is going in the right direction. The remaining entries in the floating admittance matrix whole circuit incorporating passive components can be written by inspection without much difficulty once the floating admittance matrix of the active device is understood. This technique can be used to avoid performing a rigorous equivalent circuit analysis with more active devices in any circuit. Mathematical modelling should be the foundation of every educational system, especially engineering

education, because it shows where to put the right tools to get the job done. It is needless to say that stakeholders are students, guardians, faculty positions, management groups, and, very importantly, the industrialist as employers and others. These variables are correctly set in the mathematical model to achieve the desired outcome. If the desired result is not reached for a given set of inputs from all stakeholders, the mathematical modelling is revisited, with fine-tuning of one or more variables increased or decreased to get the desired result. As a result, mathematical modelling variables should be finetuned so that the desired result is attained quickly and elegantly. (A paper as presented on "Mathematical modelling of semiconductor devices and circuits: A review," 3rd International Conference on Intelligent Circuits and Systems (ICICS 2020) held on June 26-27th, 2020, organised by "The School of Electronics and Electrical Engineering" Lovely Professional University, Punjab (India) at DOI:10.1201/9781003129103-14).

## **Objective 2:** *Performance validation of the developed models using the floating admittance technique.*

**Problem Statement:** Using the floating admittance matrix approach, all forms of transfer and self-port functions such as voltage gain, current gain, input resistance (impedance), output resistance (impedance), and power gains of any complicated circuit may be easily generated. The superposition theorem is nicely satisfied by this FAM approach. Because the method only uses co-factors from the created FAM, the computer can be used for complex networks.

**Work Explanation:** The conventional approach to a mathematical model of the actives devices such as BJT, FET, MOSFET, and Op. Amp uses its equivalent circuit as per the requirement of (a) either large signal or small-signal models, (b) low frequency or high-frequency models, so and so forth. The typical way of equivalent circuit approach becomes quite onerous for cascaded or cascoded connections of several devices (BJTs. FETs, MOSFETs, and Op Amps) or combinations of BJTs & FETs, MOSFETs, and Op Amps) or combinations of BJTs & FETs, MOSFETs, and Op Amps in any circuit. "Mathematical Modelling of Simple Passive RC Filters Using (FAM) Floating Admittance Technique" (*2020 IEEE International Conference for Innovation in Technology (INOCON) Technically Cosponsored by IEEE Bangalore*

# *Section 06th - 08th November 2020 DOI:* 978-1-7281-9744-9/20/\$31.00 ©2020 IEEE) was presented (IEEE, SCOPUS).

In this article, the problems relating to modelling simple electrical circuits consisting of resistors, capacitors, voltage sources, and current sources were taken up. Generally, we avoid using passive inductors because the planar spiral inductors are heavy, take more space, and dissipate considerable power with respect to resistors and capacitors. On the other hand, simulated inductances are frequently utilised in filters to achieve good performance, but that is the realm of active filters. Mesh equations, node equations, or Thevenin or Norton equivalent methods are used to solve fundamental networks consisting of resistances (R), capacitances (C), voltage sources, and current sources. These techniques do not conform to the state-space form of the mathematical model or, even later, cannot be converted by any means to the state space form.

The fundamental understanding of transfer function characterisation provides sufficient information to determine whether proper functioning has been attained. The circuit structure's input impedance and output impedances, power supply coupling and uncoupling, circuit component change, and other dynamic behaviour are all significant elements.

### **Objective 3:** Simulation and analysis of developed models using MATLAB/ SIMULINK/LTSpice.

**Problem Statement:** The analysis becomes lucid and corroborates the transfer functions obtained in the literature. These transfer functions are solely dependent on the co-factors of FAM of any circuit, whether active, passive or a combination of both. The floating admittance matrix has the distinct advantage of being able to be written by inspection for basic circuits.

**Work Explanation:** The modelling and simulation of bridge -T network has been carried out using MATLAB's Simulink system environment. This paper provides simulated and numerical validation of two forms of bridge -T network used for band pass filter. The MATLAB program developed for the transfer function for both types of the RC bridge-T network are plotted in the form of magnitude and phase w.r.t. frequency. The input and output impedances are derived and drawn using the FAM technique.

"Mathematical Modelling and Simulation of Band Pass Filters using the Floating Admittance Matrix Method" (WSEAS TRANSACTIONS on CIRCUITS and SYSTEMS E-ISSN: 2224-266X DOI: 10.37394/23201.2021.20.24) was another paper published (SCOPUS).

# **Objective 4:** Comparative analysis of floating-point admittance technique with existing methods for active semiconductor devices

**Problem Statement**: The traditional analysis approach employs one of the widely used tools, such as KCL, KVL, Thevenin's, Norton's, and others, depending on the circuit's suitability, whether active or passive. The floating admittance matrix technique proposed here is unique, and it may be used to any type of circuit. The matrix partitioning method is used to benefit the difficult network. The fact that all elements of any row or column add up to zero gives you the confidence to go deeper into analysis or re-observe the circuit at the first equation to save time and energy. Work **Explanation**: The floating admittance mathematical model presented here is so simple that anybody with slight knowledge of electronic devices, but an understanding of matrix maneuvering, can analyse the circuits to derive all types of transfer functions provided the parameters of devices are known to them. The floating admittance matrix model is used to analyse and subsequently build any circuit. It is based on pure mathematical maneuvering of matrix elements of the circuit. All transfer or self-port functions are defined as the ratios of co-factors of the first and or second order of the FAM. The FAM approach's mathematical modelling allows the designer to adjust their design style at any analysis stage comfortably.

"Unique Analysis Approach to Bridge-T Network using Floating Admittance Matrix Method" (INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING Volume 15, 2021 DOI: 10.46300/9106.2021.15.140) was published (SCOPUS).

Another paper, "Unique Analysis Technique for 4-Terminal MOSFET Amplifiers using Floating Admittance Matrix Approach" 2022 International Conference for Advancement in Technology (ICONAT) Goa, India. Jan 21-22, 2022, DOI: 978-1-6654-2577-3/22/\$31.00 ©2022 IEE was published (IEEE, SCOPUS). The paper presents an elegant technique of analysing the 4-terminal MOSFET amplifier circuit. The proposed technique helps in writing the floating admittance matrix (FAM) of any circuits by inspection once the FAM of electronic devices (BJT/FET/ MOSFET) is known. The matrix partitioning technique suits an extensive network well using the proposed technique. The proposed floating admittance matrix technique does not assume any reference terminal. For this reason, it is called the floating admittance matrix approach.

#### **1.3 Mathematics in modelling**

Mathematics helps engineers form, analyse, and optimize the functionality of the phenomena to design and develop a system. Mathematics enhances teachers' and students' ability to engage in abstract thinking and arouses their imagination. Innovative engineers and scientists are creative, and creativity is essential for strong imagination and abstract thinking. As a result, a successful innovative engineer is likely to have a solid understanding of mathematics.

### **1.4 Modelling of physical environment**

Modelling also refers to the study of processes and items in one physical environment utilising processes and objects from another physical environment as models to replicate the system's behaviour. Collins, Brown, and Newman [1] believe modelling shows how and why an expert does a task. It is one method that is critical to expert teaching regarding any procedure or process.

The complexity of the processes in modern engineering, economics, and other systems is so powerful that they expect to have useful information and the characteristics of the complete systems and predictions of the consequences of their behaviours.

Modelling is a powerful technique that may be used in various fields. It's "a natural requirement of practically any engineering course," according to the author Crawley et al. [2]. *Massoud Moussavi* [3] in 1998 submitted a Ph.D. dissertation on Mathematics, Modelling, and Modular Curriculum. Grinter [4] proposed retraining programs in Engineering for *Johnson & Wales University and School of Technology* to emphasize the maneuverability of *mathematical models* in the curriculum.

Modelling is part of the management process nowadays at every stage of human involvement. Engineering colleges/institutes should, for example, investigate the efficiency and efficacy of an engineering curriculum by:

- Predict the program performance of the proposed curriculum.

- Evaluate and assess the proposed curriculum.

- Identify the points of deficiencies.

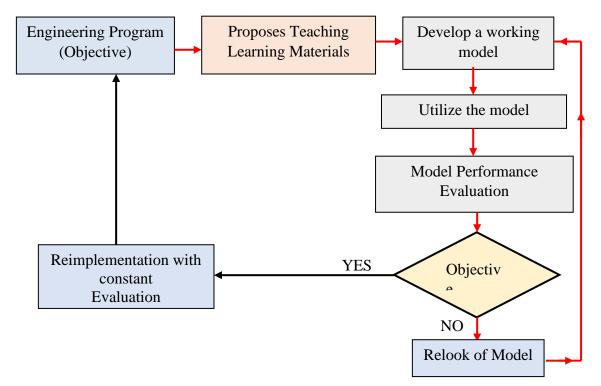

Modelling becomes a powerful tool to accomplish these tasks for them. Fig. 1.1 shows a typical model for an effective engineering education program.

Fig. 1.1 Model of an Effective Engineering Education Program

This model helps engineering education to continuously evaluate their proposed program, identify its deficiencies, and improve and modify it in a timely manner.

To model an effective engineering program, as an example, for Electronics Engineering students, we have first to define the Program's Educational Objectives as;

- (a) To enrol students having a basic knowledge of *mathematics* and science.

- (b) To train students so that they will be able to maintain and handle electronics systems, equipment, and component parts with creativity and critical spirit in

the technological development as per necessity and viability, globally, and especially for our country.

- (c) To enable the student to achieve employment in Electronics, Communication, and IT-related industries with appropriate title and compensation.

- (d) To enable the student to innovate, design, and develop hardware and software components and equip the student with technical and communication skills to function in national/international/multi-cultural corporations and organizations.

- (e) To build strong fundamental knowledge amongst students to pursue higher education and continue professional development in Electronics and other related fields.

The syllabi's design comes into the picture as per the stated objectives with the target set. The working model defines the mechanism to meet the targeted objective. The working model is divided into many subheadings: Assignments, Quizzes, mid-term examinations, end-term examinations, seminars, projects, etc. The marks distribution is as per the weightage of all such subheadings assigned. The students go through this process, and their performance is analysed to suit the stated objectives. If the *working model* matches 75% to 80% of the objective set, then we assume the working model is successful. Even if the desired model results in acceptable limits, we try to input components from all stakeholders, such as students, alumni, guardians, industrialists, etc., to improve the model management. If the model does not result in an acceptable limit, we do in-house brainstorming, inviting experts to strengthen the program objectives to match the desired result.

### **1.5 Advantages of Modelling**

Modelling provides several advantages for engineers at the design and development stage. The modelling helps engineers to evaluate the unknown properties of objects. Modelling may become the sole viable approach for engineers to design, develop, and optimise new systems due to limited resources and options. Modelling is a valuable tool for engineers to avoid the consequences of bad technical decisions. Let us take another example of the automated manufacturing of an automobile. The decision of optimum weight, speed, fuel consumption, etc., are designed and tested on the computer, and then only the industrialists go to manufacture the automobile. What should be the weight of the automobile if the break is suddenly applied when it is running at a certain speed so that it does not overturn? Many more iterations are performed on the computer before the final design is accepted for manufacturing.

Engineers may proceed in the following ways with regard to methods and methodology. They aim to acquire as much relevant information as possible for each challenge. Then they look for connections between the various themes to create a workable model. They then propose solutions that must be optimised for a variety of factors such as time, cost, size, and performance. According to Rodencker [5], the designing process is "a transition of knowledge, leading from the abstract to the concrete." He proposed eight rules for developing a technical system that starts by defining and abstracting the requirements.

Rodencker's rules are:

- (a) Clarify the task (the required relationship)

- (b) Establish the function structure (the logical relationship)

- (c) Choose the physical process (the physical relationship)

- (d) Determine the embodiment (the constructional relationship)

- (e) The appropriate calculation can check the logical, physical, and constructional relationships.

- (f) Eliminate disturbing factors and errors.

- (g) Finalize the overall design.

- (h) Review the chosen design.

What Rodencker tried to establish is a model that employs *mathematics* to design a technical system. Rules' 'd', 'e,' and 'f' are nothing but formalizing the system using mathematics. In fact, these three rules are the heart of the design process. They show that a scientific, efficient, and cost-effective design would be possible only by the employment of *modelling*.

*Electronic processes* and *objects*, in general, are used as *models* because electronic systems have an unusual combination of properties and characteristics. The electronic process parameters and the structure of the connection between individual

elements can also be changed easily, explicitly, or implicitly. Along with rapid progress in the field of electronics, the calculation and designing of electrical devices and networks have become a much more sophisticated and challenging task than ever been taken.

Consequently, Electronic engineers must continuously improve the mathematical description, numerical analysis, and computer-aided design of electronic devices and systems. *Modelling* is the only effective technique that responds to the current marketplace, demanding fast and inexpensive design and production methods.

Mathematical *modelling* helps electronic engineers extensively to study and investigate the dynamic behaviour of electrical networks. Verlan [6] has developed a mathematical model called an integral equation. This is essentially the procedure which finds the integral mathematical relationships between the known source of data and unknown network parameters. The following brief description of Verlan's work depicts how *mathematical modelling* helps engineers study a system's behaviour to further develop a more accurate system.

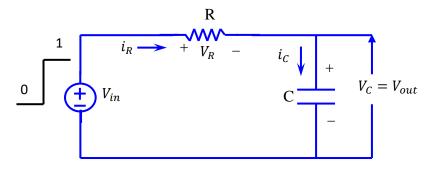

The RC circuit can act as a simple integrator or a first-order low-pass filter. The signals of low frequencies pass approximately unchanged through the filter, while signals of high frequencies are filtered out (stopped). We will find the *mathematical model* to analyze it relating  $V_{in}$  and  $V_{out} = V_C$ . We start by considering the following RC circuit of Fig. 1.2.

Fig. 1.2 Circuit Model of a passive RC Integrator

We apply Kirchhoff's voltage law (KVL) in the circuit, which contains the input voltage terminals, the resistor, and the capacitor, considering the voltage drop positive in the clockwise direction. The non-homogeneous equation delineates the RC circuit's

response to a step input to the register's interconnected terminals and capacitance. If a step voltage  $(V_{in})$  is applied at t = 0, what is the form of the output?

Writing the KVL yields

$$-V_i + V_R + V_C = 0 (1.5)$$

If a step voltage  $(V_{in})$  is applied at t = 0, what is the form of the output?

For a capacitor

$$i_c = C \frac{dV_c}{dt}$$

(1.6)

Current through the resistor

$$= i_R = \frac{V_R}{R}$$

(1.7)

Since there is a single path for the current through the resistor and the capacitor, we can write

$$i_R = i_C \tag{1.8}$$

Then,

$$i_R = \frac{V_R}{R} = i_C = C \frac{dV_C}{dt}$$

(1.9)

$$V_R = RC \frac{dV_C}{dt} \tag{1.10}$$

Substituting  $V_R = V_{in} - V_C$  and rearranging yields

$$RC\frac{dV_C}{dt} = V_R = V_{in} - V_C \tag{1.11}$$

Now separating the variables as

$$dt = RC \frac{dV_C}{V_{in} - V_C} \tag{1.12}$$

Integrating

$$\int dt = RC \int \frac{dV_C}{V_{in} - V_C}$$

(1.13)

Thus,

$$t = -RC \ln\{V_{in} - V_C\} + k(constant)$$

(1.14)

For

$$t = 0, V_C = 0$$

(1.15)

Slowly the charge builds up across the capacitor from zero value.

$$0 = -RC \ln\{V_{in} - 0\} + k$$

$$k = RC \ln V_{in}$$

(1.16)

Now,

$$t = -RC \ln\{V_{in} - V_C\} + RC \ln V_{in} = RC \left[\ln\{V_{in} - (V_{in} - V_C)\}\right]$$

(1.17)

$$\frac{t}{RC} = ln \{V_{in} - (V_{in} - V_C)\} = ln \frac{V_{in}}{V_{in} - V_C}$$

$$exp\left(\frac{t}{RC}\right) = \frac{V_{in}}{V_{in} - V_C}$$

$$\{V_{in} - V_C\} = \frac{V_{in}}{exp\left(\frac{t}{RC}\right)}$$

$$(1.18)$$

$$V_C = V_{in} - \frac{V_{in}}{exp\left(\frac{t}{RC}\right)} \tag{1.19}$$

$$V_{C} = V_{in} \left[ 1 - \frac{1}{exp\left(\frac{t}{RC}\right)} \right] = V_{in} \left[ 1 - exp\left(-\frac{t}{RC}\right) \right]$$

(1.20)

If we substitute t = 0 in Eq. (1.20),  $V_C = V_{in}[1 - exp(-0)] = 0$  (1.21)

This condition verifies that at the moment t = 0, the capacitor was fully discharged.

At

$$t = \infty, V_C = V_{in}[1 - exp(-\infty)] = V_{in}$$

(1.22)

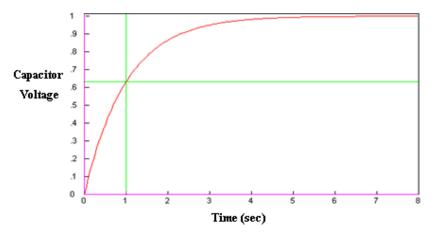

Equation (1.22) reveals that the capacitor is charged to the input voltage's full value after a considerable time. The plot of this response for unit values of capacitor C, resistor R, and input step voltage  $V_{in}$  is given as in Fig. 1.3.

The RC is the product of resistance R (Ohms), and capacitance C (Farads) has the unit of seconds and is always constant. The Greek letter  $\tau$  (tau) is usually used to denote this variable.

The output voltage ( $V_c$ ) reaches 63.2% of its final value in 1 time constant (1 second in this case). The time taken to reach a particular value is related to the number of time constants given in Table 1.1.

Fig. 1.3 Response of RC Integrator for input step

| Table 1.1 Required number of time constants to reach a proportion of the final value |       |       |       |       |       |       |

|--------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| τ                                                                                    | 2τ    | 3τ    | 4τ    | 5τ    | 6τ    | 7τ    |

| 63.2%                                                                                | 86.5% | 95.0% | 98.2% | 99.3% | 99.7% | 99.9% |

Reducing the value of  $\tau$  (i.e., reducing R or C) means that the output will change faster, and any given voltage will be reached sooner.

Thus, the integral equations provide a most common and convenient means to examine and determine the inherent and the induced part of the components of processes that may take place in linear circuits. The use of integral equations for describing electrical networks' dynamic behaviour results in several specific methods for their quantitative and numerical analysis.

Another straightforward example of mathematical modelling is the relationship between the voltage across and current through a resistor. The relationship between current and voltage for the resistor, capacitor, and inductor is depicted in Fig. 1.4.

If the current through the component is I (A) and the voltage drop across the component is v (V). The current and voltage are then related as follows.

$$\text{Resistor} \rightarrow Ri(t) \rightarrow Ohm's \ Law \tag{1.23}$$

Capacitor

$$\rightarrow i(t) = C \frac{dv(t)}{dt}$$

(1.24)

Inductor  $\rightarrow v(t) = L \frac{di(t)}{dt}$  (1.25)

Inductor  $i(A) \longrightarrow (H)$ + v(V) -

Fig. 1.4 Circuit symbol Model of Resistor, Capacitor, and Inductor Power →Instantaneous Power:

When current i(t) flows through the resistor (R), the power delivered to the resistor is given as;

$$P(t) = v(t)i(t) \tag{1.26}$$

Mean Power: When an alternating (sinusoidal) current of amplitude I flows through a resistor R (for example, a heating element), the mean or average power delivered to the resistor is written as;

$$\hat{P} = \frac{1}{2}RI^2 = \frac{1}{2}\frac{V^2}{R}$$

(1.27)

A resistor is a two-terminal component described by the mathematical model in terms of voltage and current as;

$$R (Ohm) = \frac{V(volt)}{I (amp)}$$

(1.28)

Where V and I are the voltage across and current through the resistor, the large signal Model of the resistor is described by Eq. (1.28). However, a resistor dissipates power, and as it dissipates power, it gets heated. Depending upon the material of the resistor, the heat can change the value of the resistor. Hence, considering the effect of heat, the large-signal model of the resistor could be written as;

$$R(t) = R(t_o)f_1(t - t_o)$$

(1.29)

Where  $R(t_o)$  is the resistance at the reference temperature  $t_o$  and  $f(t - t_o)$  is a suitable function that represents the variation in the value of the resistor. This function is dependent on the power dissipation in the resistor and its thermal properties. So, we can write the value of the resistor at any terminal voltage as

$$R(V) = R(V_o)f_2(V - V_o)$$

(1.30)

Where R(V) is the value of resistance at a reference voltage  $V_o$  and  $f_2$  is a function of terminal voltage V and the reference voltage  $V_o$ . It is possible to interrelate the function  $f_1$  and  $f_2$  through the physics of heating and thermal properties of the material. The nature of these functions also depends upon the nature of variation of resistance with temperature. The resistance of metal film resistors increases linearly with temperature. On the contrary, the resistance of a Thermistor made of semiconducting material decreases linearly with temperature. Therefore, we may have a simple or a complex large-signal model of the resistor depending on the resistor's material.

The small-signal model of a resistor is simply a dynamic resistance that changes with respect to the change in the operating points that can be represented by

$$\Delta R(V) = \frac{\Delta V}{\Delta I} \tag{1.31}$$

Where  $\Delta R(V)$  is the ratio of  $\frac{\Delta V}{\Delta I}$  and  $\Delta I$  and  $\Delta V$  are small signal variations.

Modelling is one of the most important means for accelerating scientific and technological progress.

The modelling also intensifies the development of science and the economy, but unfortunately, it is given the least priority in Indian engineering education, mainly at the Undergraduate College Level. Several factors play a role in de-emphasizing modelling in engineering education globally. The Grinter [4] report supports converting engineering colleges to research institutes and takes away the engineering curriculum design. The Grinter report is one of the essential documents followed in engineering education in the United States.

The U.S. had much better resources and options after World War II than any other well-developed nation. The defence budget and military spending were very high, and engineering colleges were funded by the armed forces and Government. "Only research that helped to war-making was rewarded," presumably, "to keep alive the expectations of a perpetual war economy." by Ferguson [7]. Almost unlimited resources left no room for modelling instead, a philosophy of "trial-and-error" became popular in engineering development and design.

As global marketplaces got more intensive in their pursuit of re-engineering, American companies have adapted to the concepts of re-engineering, continuous design, just-in-time strategy, and product cost reduction. Consequently, *modelling* is getting attention among engineers and engineering schools.

A mathematical model uses mathematical language to explain a system. Mathematical models area unit used not solely within the natural sciences and engineering disciplines (such as physics, biology, natural science, meteorology, and electrical engineering) however conjointly within the social sciences (such as political economy, sociology, and political science); physicists, engineers, pc scientists, and economists use mathematical models most extensively. Eykhoff [8] outlined a mathematical model as an illustration of the essential aspects of the Associate in Nursing existing system (or a system to be constructed) that presents information of that system in usable form'. However, mathematical models will take several forms, not restricted to resurgent systems, applied math models, differential equations, or game-theoretic models. These different kinds of models will overlap with a given model involving a range of abstract structures.

#### **1.6 Background of Modelling**

Often, once engineers analyze a controlled or optimized system, they use a mathematical model. Within the analysis, engineers will build a descriptive model of the system as a hypothesis; however, the system might work or try {an} estimate. However, an unpredictable event might affect the system. Similarly, engineers will try totally different management approaches in simulations on top of things of a system.

The mathematical model typically describes a system by a collection of variables and a collection of equations that establish relationships between the variables. The values of the variables are often anything; real or numbers, Boolean values, or strings, for instance. The variables are some properties of the system; as an example, the measured system outputs typically within the variety of signals, temporal arrangement knowledge, counters, and event prevalence (yes/no). The particular model is the set of functions describing the various variables' relations.

### **1.7 Building Blocks of Modelling**

There are six basic groups of variables; input variables, state variables, exogenous variables, random variables, and output variables. Since there may be several variables of every sort, the variables are typically denoted by vectors, call variables, or are typically referred to as freelance variables. Exogenous variables are typically referred to as parameters or constants. The variables do not seem to be freelance of every alternative because the state variables are captivated by the choice, input, random, and exogenous variables. Moreover, the output variables are captivated by the state of the system. The system's objectives and constraints are represented as functions of the output variables or state variables. The target functions can depend upon the angle of the model's user. Counting on the context, the Associate in Nursing objective operates additionally referred to as the Associate in Nursing index of performance because it is a few life of interest to the user. Though there is no limit to the number of objective functions and constraints a model will have, mistreatment or optimizing it becomes an additional concern (computationally).

### **1.8 Classification of Mathematical Models**

Mathematical models may be classified in some of the following ways;

(a) *Linear vs nonlinear* $\rightarrow$ the linear systems are of two types, namely,

- Linear time-invariant, and

- Linear time-varying systems.

A differential equation is linear if its coefficients are constants or functions of the only independent variable. Dynamic systems composed of linear time-invariant lumped-parameter may be described by a linear time-invariant (or linear constant-coefficient) system. Systems that are represented by differential equations with their coefficients as functions of time are called linear time-varying systems. An example of a time-varying control system is a spacecraft control system—the mass of the aircraft changes due to fuel consumption.

*Nonlinear Systems*: A nonlinear system where the principle of superposition does not hold well. The response to two inputs cannot be calculated by treating the one input at a time and adding the result for a nonlinear system. Examples of nonlinear differential equations are;

$$\frac{d^2x}{dt^2} + \left(\frac{dx}{dt}\right)^2 + x = A \sin\omega t$$

(1.32)

$$\frac{d^2x}{dt^2} + (x^2 - 1)\frac{dx}{dt} + x = \mathbf{0}$$

(1.33)

$$\frac{d^2x}{dt^2} + \frac{dx}{dt} + x + x^3 = \mathbf{0}$$

(1.34)

If operators in a mathematical model are linear, the resulting mathematical model of the linear system suggested by Olof Staffans [9] is linear; otherwise, a model is considered nonlinear.

The question of linearity and nonlinearity depends on the context. A linear model might have nonlinear expressions. For instance, a linear statistical model assumes a linear relationship in parameters, but it might be nonlinear among predictor variables.

Similarly, a differential equation is alleged to be linear if it is often written with linear differential operators. However, it will still have nonlinear expressions in it. In an exceedingly mathematical programming model, if the target functions and constraints square measure diagrammatic entirely by linear equations, then the model is thought to be a linear model. If one or a lot of the target functions or constraints square measure diagrammatic with a nonlinear equation, then the model is thought of as a nonlinear model. Even in relatively simple systems, nonlinearity is usually related to phenomena like chaos and un-changeableness. Though there square measure exceptions, nonlinear systems and models tend to be tougher to check than linear ones. a typical approach to nonlinear issues is linearization. However, this could be problematic if one attempts to check aspects like un-changeableness, that square measure powerfully tied to nonlinearity.

- (b) Deterministic vs probabilistic (stochastic)→ A deterministic model of Lin and Segel [10] is one within which variable states are unambiguously determined by parameters within the model and by sets of previous states of those variables. Therefore, settled models perform a similar method for a given set of initial conditions. Conversely, randomness is a gift in an exceedingly random model, and variable states don't seem to be delineated by distinctive values but rather by likelihood distributions.

- (c) Static vs dynamic→ the static model does not account for the time of elements, but a dynamic model does. Dynamic models are represented either in the form of difference or differential expressions.

- (d) Lumped versus distributed parameters→ if the model is homogeneous, the parameters are lumped. If the model is heterogeneous (a varying state within the system), then the System's parameters are distributed. Distributed parameters are represented with partial differential equations and in many more ways.

#### **1.9 Priori Information of Models**

According to how much *a priori* information suggested by Jason and Jenkins [11,12] is available, Black box and white box models are commonly used to classify mathematical modelling difficulties. A *black-box* model is a system in which there is no a priori information available. A *white-box* model is known as a system where all necessary information required is available for use. In practice, all systems fall inbetween *black-box* and *white-box* models. So, this concept works as an intuitive guide only.

It is desirable to use the maximum amount of a priori data to make the model a lot of correct predictions. The white-box models are typically thought of as softer due to acquired knowledge correctly; the model can behave appropriately. Often, a priori data comes within the type of knowing the kind of functions regarding totally different variables. For Associate Nursing instance, if we tend to create a model of how a drug works in a human system, we all know that the number of drugs within the blood is associated with Nursing exponentially decaying performance. However, our tendency is still to live with many unknown parameters. How speedily will the medication quantity decay, and what is the initial quantity of drugs in the blood? In this instance, it is not a very simple white-box model. These parameters have to be calculable through some suggestions before using the model.

In black-box models, one tries to estimate each useful type of relationship between variables and, therefore, the numerical parameters in those functions. Employing a priori data, we tend to find ourselves, for instance, with a group of functions that most likely may describe the system adequately. If there is no a priori data, we will try to use functions as general as possible to hide all different models. In Nursing's often-used approach for black-box models, associates are neural networks that generally do not assume nearly one thing regarding the incoming information. Using a vast set of functions to elucidate a system estimates the parameters becomes increasingly powerful once the number of parameters (and different types of functions) increases.

### **1.10 Subjective Information of Models**

Many a time, incorporating subjective information into a mathematical model is useful. This may be done based on *intuition, experience, expert opinion,* or mathematical convenience.

*Bayesian statistics* suggest a theoretical framework for incorporating a subjective approach in rigorous analysis. One specifies a prior subjective probability distribution and then updates it based on empirical data. An example of one such Associate in Nursing approach would be a necessary scenario within which an Associate in Nursing experimenter bends a coin slightly and tosses it once, recording whether or not the head comes up gives a chance of predictions that the following flip comes up heads. The probability of the coin coming up with a head after tossing is unknown. So, the experimenter makes an arbitrary decision (perhaps by looking at the shape of the coin) about what prior distribution to use. Incorporating subjective information is necessary to predict the next flip accurately; being head would lead to wrong predictions.

MacKay's contribution to machine learning and information theory is based on the development of Bayesian methods for neural networks, called the rediscovery (with Radford M. Neal Shahbaba, B. and Neal, R. M. (2005). Improving classification when a class hierarchy is available using a hierarchy-based prior (Technical Report No. 0510, Dept. of Statistics, 11 pages.) of low-density parity-check codes and the invention of *Dasher*. This software application for communication was most popular with those who cannot use a traditional keyboard. MacKay [13] in 2003 he published a book on Information Theory, Inference, and Learning Algorithms based on the above statements.

### **1.11 Complexity of Models**

Usually, the model complexity involves a trade-off between the simplicity and accuracy of the model. *Occam Razor's* [14] principle is particularly relevant to modelling; the essential idea is that the simplest one is the most desirable among models with roughly equal predictive power. On the one hand, adding complexity usually improves the fit of a model; it may make the model too difficult to understand and work with and pose computational problems, including *Numerical instability*. *Thomas Kuhn* [15] argues that explanations become more complex as science progresses before a *Paradigm shift* offers radical simplification. For example, when modelling an aircraft's flight, we embed each mechanical part of the aircraft into our model to acquire an almost *white-box* model of the system. Moreover, the computational cost of adding such a massive amount of details would not allow the use of such a complicated model.

Additionally, the uncertainty would increase thanks to a very sophisticated system due to every separate half induces some quantity of variance in the model. It is, therefore, typically acceptable to create some approximations to scale back the model to an acceptable size. Engineers typically will settle for some approximations to get a lot of sturdy and easy models. As an example, Newton's classical mechanics is an approximate model of the real world. Still, Newton's model is comfortable for many ordinary-life things, that is, as long as particle speeds are well below the sunshine's speed and we solely study macro-particles.

### **1.12 Training of Models**

Any model which is not a pure white box contains some parameters that may be accustomed to match the model of the system it describes. If a neural network completes the modelling, the optimization of parameters is named coaching. In addition, standard modelling through expressly given mathematical functions determines parameters by curve fitting.

### **1.13 Model Evaluation**

A crucial part of the modelling method is evaluating whether a given mathematical model accurately describes a system. This question will be challenging to answer because it involves many different kinds of analysis.

### **1.14 Model Fitting of Empirical Data**

Usually, the best part of the model analysis checks whether or not a model fits experimental measurements or different empirical information. A typical approach to check this work is to separate {the information} into 2 disjoint subsets in models with parameters: coaching information and verification data. The coaching information measure would not estimate the model parameters. The correct associate model can closely match the verification information even though it did not set the model's parameters. The cross-validation of the regression model by Richard and Dennis [16] was presented in statistics.

Defining a metric to live the deviation between ascertained and foretold knowledge could be an excellent tool for assessing model work. A loss performs a similar role in statistics, call theory, and a few economic models. It is very tough to check the validity of a model's general mathematical kind when it is comparatively simple to check the parameters' appropriateness. In general, additional mathematical tools are developed to check applied math models' work than models involving Differential equations. Tools from statistic statistics will typically not measure; however, good knowledge fits a known distribution or comes back up with a general model that creates marginal assumptions regarding the model's mathematical kind.

### **1.15 Model's Scope**

Assessing the model's scope is crucial. What things the model applies to may be less straightforward. If the model was created supported by a collection of information, one should confirm what systems or things could be a typical set of information. Whether or not the model describes well the properties of the system between knowledge points is named interpolation and it was suggested by Crochiere and Rabiner [17], and therefore the same question for events or knowledge points outside the determined knowledge is named extrapolation That was the suggestion of Brezinski and Zaglia [18]. Likewise, he did not include molecules' movements and different tiny particles. However, macroparticles were solely considered. It is then not stunning that his model does not extrapolate well into these domains, although his model is entirely decent for standard life physics.

### **1.16 Philosophical Considerations of Models**

Many types of modelling implicitly involve claims concerning relation. This is often typically (but not always) true of models involving differential equations because modelling aims to extend our understanding of the globe. However, the validity of a model rests not solely on its acceptable empirical observations but also on its ability to extrapolate to things or information on the far side that was originally delineated within the model. One argues that a model is nugatory unless it provides some insight that goes on the far side of what's already notable from the development's direct investigation.

An example of such criticism is that the mathematical models of the optimum forage theory projected by Graham H. Pyke [19] do not supply insight that goes on the far side of the common-sense conclusions of evolution and alternative basic principles of ecology. We would discuss the general topic of deriving equivalent circuits from the differential equations that determine a given system's response. This is the procedure usually followed in modelling solid-state devices, where the distributed parameters of the equivalent circuits are derived from the solutions to Laplace or Poisson equations. The circuital visualization of this process provides insights that are extremely helpful in understanding the system response.

Mathematical modelling is the process of representing a physical system (structure, automobiles, graphs, diagrams, scattered plots, tree diagrams, circuits, etc.)