# ALGORITHM BASED OPTIMIZATION OF FRACTIONAL PLL FOR COMMUNICATION BASED APPLICATIONS

Thesis Submitted for the Award of the Degree of

# **DOCTOR OF PHILOSOPHY**

in

**Electronics and Communication Engineering**

By

Mohammad Abdul Muqueem

**Registration Number: 41800742**

**Supervised By**

Dr. Shanky Saxena (25061)

**School of Electronics & Electrical**

**Engineering, Assistant Professor**

Lovely Professional University Phagwara, Punjab, India Co-Supervised by

Dr. Govind Singh Patel (100)

ECE Department,

Professor

SITCOE, Ichalkaranji, MH,India

Transforming Education Transforming India

LOVELY PROFESSIONAL UNIVERSITY, PUNJAB

2024

# DECLARATION

I hereby declare that the thesis entitled "Algorithm based Optimization of Fractional PLL for Communication based Applications" has been prepared and submitted by me under the guidance of Supervisor Dr. Shanky Saxena, Assistant Professor, School of Electronics & Electrical Engineering, Lovely Professional University, Phagwara, Punjab and Co-Supervisor Dr. Govind Singh Patel, Professor, Department of Electronics & Computer Engineering, SITCOE, Ichalkaranji, Maharashtra the requirement for the award of the degree of Doctor of Philosophy (Ph.D.) in Electronics & Communication Engineering is entirely my original work and ideas, references are duly acknowledged. It does not contain any work that has been submitted for the award of any other degree or diploma from any University.

Mr. Mohammad Abdul Muqueem Reg.No-41800742 Lovely Professional University, Phagwara, Punjab, India.

# CERTIFICATE

This is to certify that **Md Abdul Muqueem** has completed his Doctor of Philosophy (Ph.D.) in Electronics & Communication Engineering thesis entitled "Algorithm based Optimization of Fractional PLL for Communication based Applications" is a bonafide work carried out by him under my supervision and guidance. To the best of my knowledge, the present work is the result of his original investigation and study. No part of the thesis has ever been submitted to any other University or Institute for the award of any degree or diploma.

| Dr. Shanky Saxena                              | Dr. Govind Singh Patel |

|------------------------------------------------|------------------------|

| Supervisor                                     | Co-Supervisor          |

| Assistant Professor,                           | Professor,             |

| School of Electrical & Electronics Engineering | ECE Department         |

| Lovely Professional University                 | SITCOE,                |

| Phagwara,Punjab,India                          | Ichalkaranji,MH,India  |

#### ABSTRACT

A Phase-Lock Loop (PLL) is a control system-equipped device that produces an output signal which stage is correlated with the stage of input signal. The fundamental electrical circuit consists of a phase detector and variable frequency oscillator with a feedback loop. The only difference between the fractional-N PLL and the integer-N PLL is the fractional outcome of the divider ratio is produced, and extra electric circuits must be included the feedback loop to keep the optimistic bandwidth and further decrease noise. The primary idea behind fractional-N PLL is to switch among two different divider ratios in order to obtain the appropriate fractional value. The pulse swallowing technique can be used to do this, which replaces the divider value for the first half of time period and then moves the value to next neighboring integer for the second half of the time period. A resolution multielement divider (fractional) is available and utilized to reduce noise that occurs in FNPLL and is known as quantization noise. Grouping of frequencies by a fraction of reference is possible using FNPLL. Both digital and analog PLLs can use it. It provides a higher frequency and a broader band width, which speed up the settling process. FNPLL has additional noise from the Delta Sigma modulator's quantization error that is used to produce the division ratio. With this suggested method, noise is systematically decreased across the full frequency range. It is difficult to simulate and Delta Sigma f-NPLL frequency synthesis. In order to create a quick simulation environment, MATLAB is used for Delta-Sigma based FNPLL frequency synthesis. In order to achieve improved reduction of noise, quick simulation environment, and various methods to lower phase noise in FNPLL, a FNPLL with a Delta-Sigma modulator is created in this study. And also The primary purpose of the PLL, which is a structural circuit design for a closed loop control system, is to make it easier for the supplied input signal to be phase and frequency synchronized. The frequency synthesizer, which takes the form of PLL, is one of the most crucial components of integrated transceivers. The explanation that follows provides an example of the 3rd order Delta-Sigma modulator design model. Changing your approach can help with this creating a new PLL architecture that is suitable for wireless applications and has low noise. The PLL overcomes several obstacles by reducing power, taking up less space, and increasing frequency. This comparison includes a diagram that illustrates various PLL. The fundamental loop transfer function, noise sources dividers, phase detectors, and fractional-N operation are all covered in this first study.

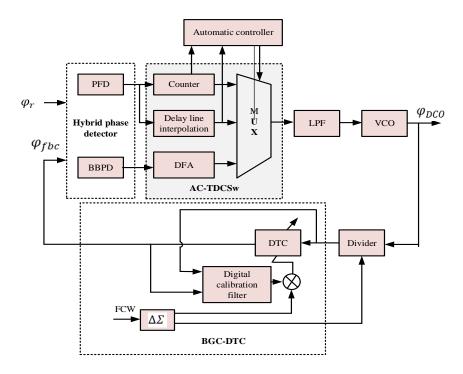

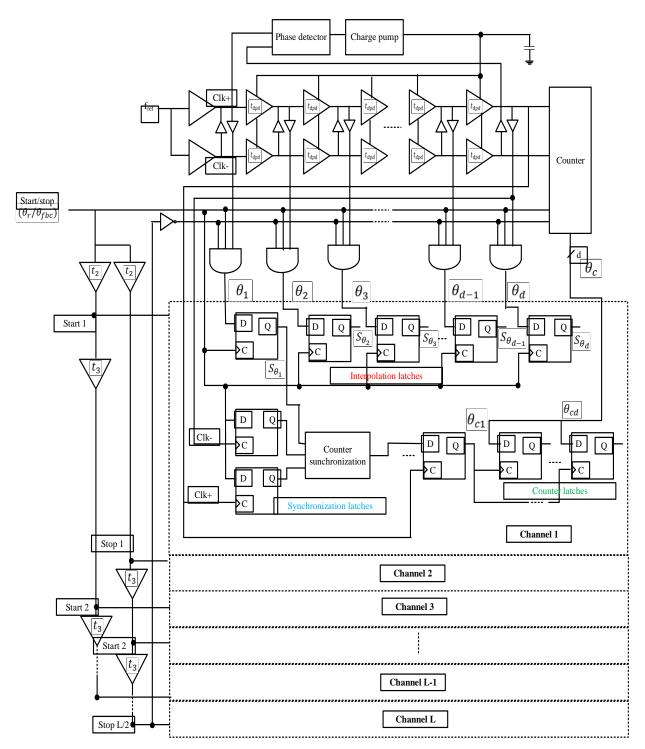

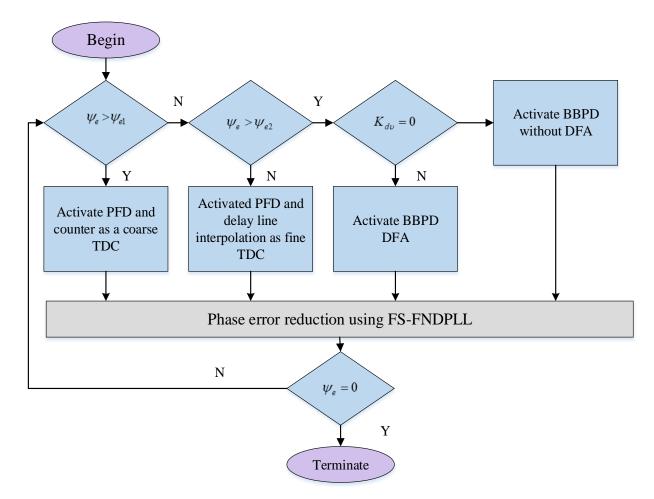

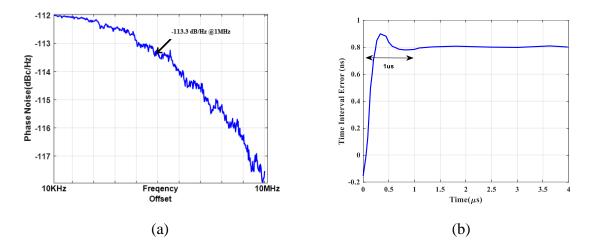

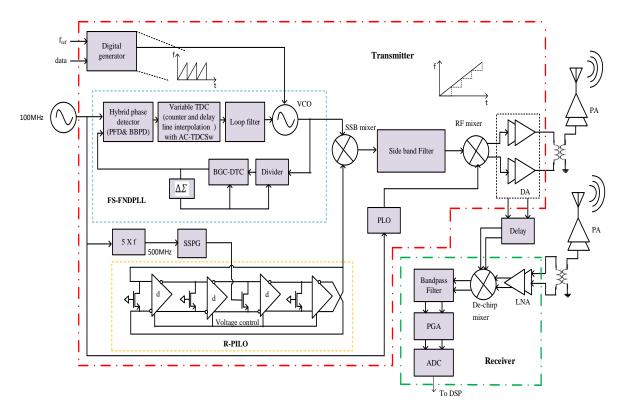

In the second work specifies low light and bad weather, radar systems according to the Frequency-Modulated Continuous-Wave (FMCW) transmissions can outrun optical and ultrasonic sensors. A quick settling frequency synthesizer is necessary for FMCW radar systems to decrease signal of chirp modulation and inactive times. Through the use of Ring-Based Pulse Injection Locking Oscillator (R-PILO) and Fast Settling Fractional-N DPLL (FS-FNDPLL), a new C-Band FMCW Transmitter is proposed. The suggested FS-FNDPLL implements an Automatic Controller-based TDC switching (AC-TDCSw) technique in the forward loop of FNDPLL to provide ultra-fast lownoise smooth narrowband chirp. A new Background Gain Calibrated Digital-to-Time Converter (BGC-DTC) is also used in the proposed FS-FNDPLL as a fractional divider in the feedback loop for the Quantization Noise Cancellation (QNC). After creating a narrowband chirp with FS-FNDPLL, recommended FMCW Transmitter provides an R-PILO to provide fast switching adjacent carriers. Ultra-fast chirps with lower spur levels and phase noise are made possible by the key characteristics of suggested FMCW to speed settling time with BGC-DTC, AC-TDCS, and combination of spur suppressing pulse generator in R-PILO. A 2-GHz chirp at the C-band is obtained by proposed emitter by up converting a 500-MHz narrowband chirp signal in four nearby carriers. According to simulation results, the suggested FMCW Transmitter uses 79 mW of power. Additionally, the suggested FS-FNDPLL's phase noise is decreased to 113 dBc/Hz at 1-MHz With the added AC-TDCSw system, the suggested, FS-FNDPLL decreases settling time to 1µs.

# ACKNOWLEDGEMENT

The successful completion of any task would be incomplete without complementing those who made it possible, under whose guidance and encouragement, the efforts are made successful. First of all, I acknowledge without hesitation, the grace of god the Almighty, in this arduous journey, it is he alone who deserves all the credit for this work. I owe my sincere gratitude to my project supervisor **Dr. Shanky Saxena**, Assistant Professor, Lovely Professional University, Punjab, India for his valuable guidance, direction, and persistent encouragement. He has always motivated me and supported me in the constructive and creative process of the entire research journey. Its really a matter of pride and joy for me to work under his guidance. I hope to seek his guidance for my future endeavors also. I owe my sincere gratitude to my project Co-supervisor Dr. Govind Singh Patel, Professor, SITCOE, Ichalkaranji, Maharashtra, India for his vital guidance, direction, and persistent encouragement. He has always motivated me and supported me in the constructive and creative process of the entire research journey. It is really a matter of pride and joy for me to work under his guidance. I hope to seek his guidance for my future endeavors also. I would also like to express my deeply felt gratitude to the Department of Research Program. I would also like to express my deeply felt gratitude to the Lovely Professional University, Punjab, India for providing me with an opportunity to work in the best academic environment.

I also would like to thank **Dr.Gaurav Sethi**, Professor & Dean, School of Electrical & Electronics Engineering, Lovely Professional University, Punjab for his kind support.

I also would like to thank **Dr. Sanjeet K. Sinha**, Associate Professor, HoD School of Electrical & Electronics Engineering, Lovely Professional University, Punjab, India for his kind support.

I would also like to express my deeply felt gratitude to **Capt.V.Lakshmikantha Rao Sir**, **Ex MP (Rajyasabha), Chairman** of Kakatiya Institute of Technology and Science, Warangal, for providing unconditional support during this journey .I also would like to thank **Prof. K. Ashoka Reddy Sir, Principal,** Kakatiya Institute of Technology and Science, Warangal, for his kind support. I also would like to thank **Prof. G. Raghotham**  **Reddy Sir**, for his kind support. I also would like to thank **Dr M.Raju Sir**, HoD ECE for his kind support. I also would like to thank all staff members of Kakatiya Institute of Technology and Science, Warangal, for their kind support. I am really thankful to **Dr. B. Arun Kumar** Assistant Professor, Lovely Professional University, Punjab, India for his kind support.

I am really happy to be blessed and encouraged by, My father **Md Abdul Aleem**, My Mother **Qursheeda Begum**. I also express sincere gratitude to all my family members. I really have no words to express my feelings for them. It is a great privilege to express my profound thankfulness, and fondness to my wife, and my dearest Sons, who stood like a rock in my difficult times. Their love, patience, persistent encouragement, and good virtuous understanding enabled me to complete the research work successfully. Finally, I express my sincere thanks to Almighty and his beautiful nature for allowing me an opportunity to complete this research work

•

Mohammad Abdul Muqueem

**RegNo: 41800742**

| TABLE OF CONTENTS                                        |    |

|----------------------------------------------------------|----|

| Title Page                                               |    |

| Declaration                                              |    |

| Certificate                                              |    |

| Acknowledgment                                           |    |

| Table of Contents                                        |    |

| List of Tables                                           |    |

| List of Figures                                          |    |

| List of Abbreviations                                    |    |

| Abstract                                                 |    |

| CHAPTER 1: INTRODUCTION                                  | 1  |

| 1.1 Overview                                             | 1  |

| 1.2 Background information of Phase Locked Loop          | 2  |

| 1.3 Fractional-N modulation methods                      | 3  |

| 1.3.1 Fractional-N PLLs (Closed Loop)                    | 4  |

| 1.3.2 Multi-Phase Switching (Open Loop)                  | 5  |

| 1.4 Fractional-N Frequency Synthesis                     | 6  |

| 1.4.1 Fractional-N PLL                                   | 7  |

| 1.4.1.1 DAC Cancellation Method                          | 8  |

| 1.4.1.2 Phase Interpolation Method                       | 8  |

| 1.4.1.3 Random Jittering Method                          | 9  |

| 1.4.2 Frequency synthesis with $\Delta\Sigma$ modulation | 10 |

| 1.5 Applications of PLL                                  | 11 |

| 1.6 Advantages of PLL                                    | 13 |

| 1.7 Disadvantages of PLL                                 | 15 |

| 1.8 Motivation                                           | 17 |

| 1.9 Problem Statement                                    | 18 |

| 1.10 Research Objectives                                 | 19 |

| 1.11 Thesis Organization                                 | 19 |

| 1.12 Summary                                             | 20 |

| CHAPTER 2: LITERATURE REVIEW                                                         | 21 |

|--------------------------------------------------------------------------------------|----|

| 2.1 Overview                                                                         | 22 |

| 2.2 Related Works                                                                    | 22 |

| 2.3 Research Gap                                                                     | 52 |

| 2.4 Summary                                                                          | 52 |

| CHAPTER 3 : PRELIMINARIES OF PLL AND DSS                                             | 54 |

| 3.1 Overview                                                                         | 52 |

| 3.2 Different existing PPL algorithms                                                | 56 |

| 3.2.2 Digital Phase-locked loop (DPLL)                                               | 58 |

| 3.2.3 ADPLL Architecture                                                             | 59 |

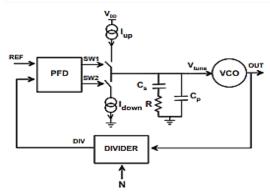

| 3.2.4 CP-PLL                                                                         | 60 |

| 3.2.5 Fast lock DPLL                                                                 | 60 |

| 3.3.6 SRF-PLL Algorithm                                                              | 61 |

| 3.3.7 DDSRF-PLL Algorithm                                                            | 62 |

| 3.3.8 Second-Order Generalized Integrators PLL (SOGI PLL)                            | 63 |

| 3.3.9 Proportional Integral Derivative (PID)-based PLL                               | 64 |

| 3.3.10 Adaptive or Notch Filtering Techniques                                        | 64 |

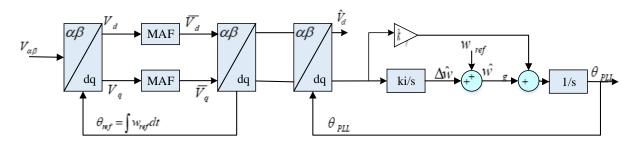

| 3.3.11 Pre-filtering Moving Average Filter (PMAFPLL)                                 | 65 |

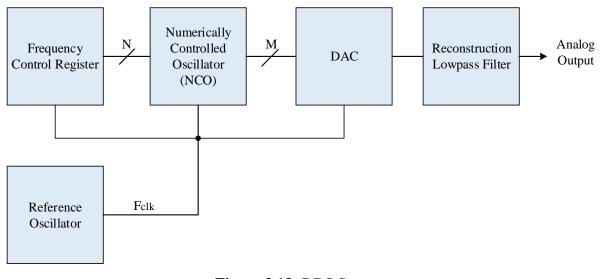

| 3.3 DDS: Concept and various types                                                   | 66 |

| 3.3.1 Pulse Output DDS                                                               | 67 |

| 3.3.2 Fractional Divider DDS                                                         | 68 |

| 3.4 Comparison Analysis                                                              | 69 |

| 3.4.1 Comparison of PLL and DDS                                                      | 71 |

| 3.5 Summary                                                                          | 73 |

| CHAPTER 4 : OPTIMIZED ALGORITHM TO ACHIEVE IMPROVED<br>PERFORMANCE OF FRACTIONAL PLL | 74 |

| 4.1 Overview                                                                         | 74 |

| 4.2 Proposed Methodology                                                             | 75 |

| 4.2.1 Design of Fractional-NPLL for Low Phase Noise                                  | 76 |

| 4.2.2 An Intensified Fractional-NPLL for Deepened low Phase Noise                    | 78 |

|                                                                                                                       | Result and discussion                                                                                                                                                                                                                                                                                                     | 8                |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 4.                                                                                                                    | 3.1 Results of Fractional-NPLL                                                                                                                                                                                                                                                                                            | 8                |

| 4.                                                                                                                    | 3.2 Results of Intensified Fractional-NPLL                                                                                                                                                                                                                                                                                | 8                |

| 4.4 \$                                                                                                                | Summary                                                                                                                                                                                                                                                                                                                   | 8                |

| CHAP                                                                                                                  | FER 5 : FAST-SETTLING FNDPLL SYNTHESIZER                                                                                                                                                                                                                                                                                  | ç                |

| 5.1 0                                                                                                                 | Dverview                                                                                                                                                                                                                                                                                                                  | 9                |

| 5.2 F                                                                                                                 | S-FNDPLL synthesizers with AC-TDCSw scheme                                                                                                                                                                                                                                                                                | ç                |

| 5                                                                                                                     | 2.2.1.Counter and delay line interpolation-based TDC                                                                                                                                                                                                                                                                      | ç                |

| :                                                                                                                     | 5.2.1.1 AC-TDCSw scheme                                                                                                                                                                                                                                                                                                   | ç                |

|                                                                                                                       | 5.2.1.2 Background gain calibrated digital-to-time converter (BGC-DTC)                                                                                                                                                                                                                                                    | ]                |

| 5.3.                                                                                                                  | Results and Discussion                                                                                                                                                                                                                                                                                                    | ]                |

| 5                                                                                                                     | 3.1 Evaluation of FS-FNDPLL                                                                                                                                                                                                                                                                                               | ]                |

| 5.4 \$                                                                                                                | bummary                                                                                                                                                                                                                                                                                                                   | ]                |

|                                                                                                                       |                                                                                                                                                                                                                                                                                                                           |                  |

| CHAP                                                                                                                  | FER 6: FMCW TRANSMITTER WITH THE UTILIZATION OF R-                                                                                                                                                                                                                                                                        | ]                |

| _                                                                                                                     | TER 6: FMCW TRANSMITTER WITH THE UTILIZATION OF R-<br>TO PRODUCE FAST SWITCHING ADJACENT CARRIERS                                                                                                                                                                                                                         | ]                |

| PILO 7                                                                                                                |                                                                                                                                                                                                                                                                                                                           |                  |

| <b>PILO</b> 7                                                                                                         | TO PRODUCE FAST SWITCHING ADJACENT CARRIERS                                                                                                                                                                                                                                                                               | ]                |

| PILO 7       6.1 0       6.2 F                                                                                        | TO PRODUCE FAST SWITCHING ADJACENT CARRIERS Overview                                                                                                                                                                                                                                                                      | ]                |

| PILO 7       6.1 0       6.2 F       6.1                                                                              | TO PRODUCE FAST SWITCHING ADJACENT CARRIERS<br>Overview<br>Proposed C-BAND FMCW SAR Transmitter                                                                                                                                                                                                                           | 1                |

| PILO 7         6.1 0         6.2 F         6.3 F                                                                      | <b>FO PRODUCE FAST SWITCHING ADJACENT CARRIERS</b> Overview         Proposed C-BAND FMCW SAR Transmitter         2.1 Ring-based pulse injection locking oscillator (R-PILO)                                                                                                                                               | ]                |

| PILO 7         6.1 0         6.2 F         6.3 F         6.3 F                                                        | <b>FO PRODUCE FAST SWITCHING ADJACENT CARRIERS</b> Overview         Proposed C-BAND FMCW SAR Transmitter         2.1 Ring-based pulse injection locking oscillator (R-PILO)         Result and discussion                                                                                                                 | 1<br>1<br>1<br>1 |

| PILO 7         6.1 0         6.2 F         6.3 F         6.3 S                                                        | <b>FO PRODUCE FAST SWITCHING ADJACENT CARRIERS</b> Overview         Proposed C-BAND FMCW SAR Transmitter         2.1 Ring-based pulse injection locking oscillator (R-PILO)         Result and discussion         3.1 Evaluation of FMCW Transmitter                                                                      | 1                |

| PILO T         6.1 C         6.2 F         6.3 F         6.3 S         CHAP                                           | <b>FO PRODUCE FAST SWITCHING ADJACENT CARRIERS</b> Overview         Proposed C-BAND FMCW SAR Transmitter         2.1 Ring-based pulse injection locking oscillator (R-PILO)         Result and discussion         3.1 Evaluation of FMCW Transmitter         Summary                                                      |                  |

| PILO 7         6.1 0         6.2 F         6.2 F         6.3 F         6.3 S         CHAP         7.1 0               | <b>FO PRODUCE FAST SWITCHING ADJACENT CARRIERS</b> Overview         Proposed C-BAND FMCW SAR Transmitter         2.1 Ring-based pulse injection locking oscillator (R-PILO)         Result and discussion         3.1 Evaluation of FMCW Transmitter         Summary <b>FER 7: CONCLUSION AND FUTURE SCOPE</b>            |                  |

| PILO 7         6.1 0         6.2 F         6.2 F         6.3 F         6.3 S         CHAP         7.1 0         7.2 F | <b>FO PRODUCE FAST SWITCHING ADJACENT CARRIERS</b> Overview         Proposed C-BAND FMCW SAR Transmitter         2.1 Ring-based pulse injection locking oscillator (R-PILO)         Result and discussion         3.1 Evaluation of FMCW Transmitter         Summary <b>FER 7: CONCLUSION AND FUTURE SCOPE</b> Conclusion |                  |

# List of Tables

| Table 2.1 | Comparison of different existing works                     | 38  |

|-----------|------------------------------------------------------------|-----|

| Table 3.1 | Summary and Comparison                                     | 70  |

| Table 3.2 | Summary and Comparison of various DDS researches           | 71  |

| Table 3.3 | Advantages and Disadvantages of PLL and DDS                | 73  |

| Table 4.1 | Represent charge pump operation with different frequencies | 85  |

| Table 5.1 | Comparison table of the state-of-the-art FNDPLL            | 107 |

| Table 6.1 | Comparison table of the state-of-the-art FMCW transmitter  | 113 |

# **List of Figures**

| Figure 1.1  | Block Diagram of Digital Phase Locked Loop                                      | 3  |

|-------------|---------------------------------------------------------------------------------|----|

| Figure 1.2  | Block diagram of conventional fractional-N synthesizers using $\Delta \Sigma$ - | 4  |

|             | digital FNPLL                                                                   |    |

| Figure 1.3  | Block diagram of conventional fractional-N synthesizers using $\Delta \Sigma$ - | 5  |

|             | based phase switching                                                           |    |

| Figure 1.4  | Frequency synthesis example with integer-N PLL                                  | 6  |

| Figure. 1.5 | Block Diagram of Fractional-N PLL                                               | 7  |

| Figure. 1.6 | Fundamental Block Diagram of DAC Cancellation                                   | 8  |

| Figure. 1.7 | Block Diagram of Phase interpolation method                                     | 9  |

| Figure. 1.8 | Block Diagram of Random jittering method                                        | 10 |

| Figure. 1.9 | Block Diagram of $\Delta\Sigma$ fractional-N PLLs                               | 11 |

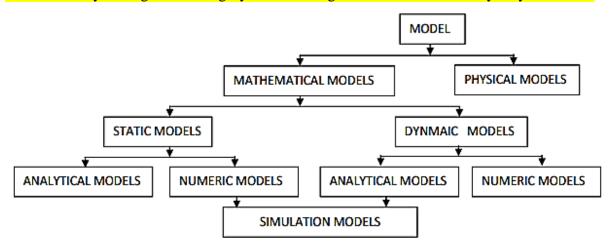

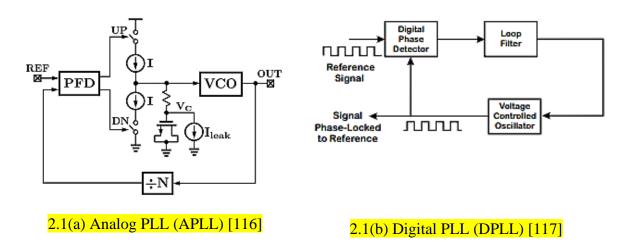

| Figure. 2.1 | Classification of PLL model                                                     | 22 |

| Figure. 2.2 | Different types of PLLs                                                         | 23 |

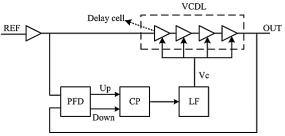

| Figure 3.1  | Conventional MDLL                                                               | 55 |

| Figure. 3.2 | Block diagram of the fundamental ILPLL                                          | 56 |

| Figure. 3.3 | Structure of APLL                                                               | 57 |

| Figure. 3.4 | Structure of DPLL                                                               | 58 |

| Figure 3.5  | ADPLL structure                                                                 | 59 |

| Figure 3.6  | Structure CP-PLL                                                                | 60 |

| Figure 3.7  | FL-DPLL Structure                                                               | 61 |

| Figure 3.8  | SRF-PLL Structure                                                               | 62 |

| Figure 3.9  | Structure of SRF-PLL                                                            | 63 |

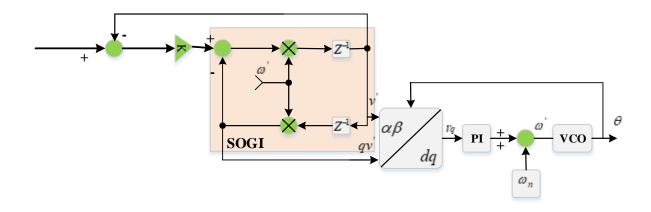

| Figure 3.10 | Structure of SOGI-PLL                                                           | 64 |

| Figure 3.11 | Adaptive or Notch Filtering based PLL                                           | 65 |

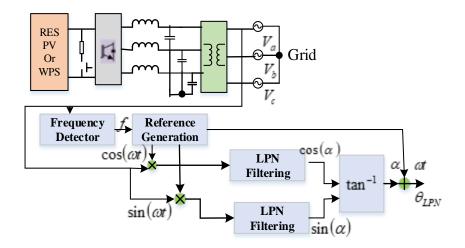

| Figure 3.12 | PMAFPLL Structure                                                               | 66 |

| Figure 3.13 | DDS Structure                                                                   | 66 |

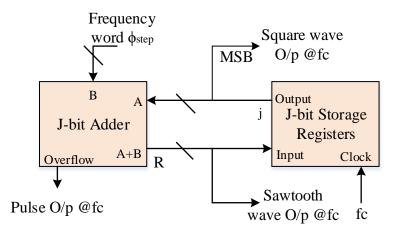

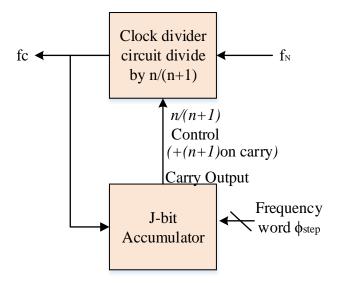

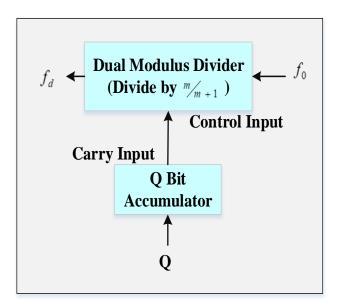

| Figure 3.14 | Pulse Output DDS                                                                | 68 |

| Figure 3.15 | Fractional Divider DDS                                                                                | 69  |

|-------------|-------------------------------------------------------------------------------------------------------|-----|

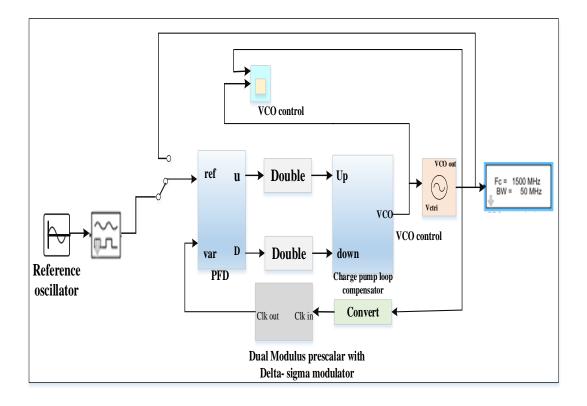

| Figure 4.1  | Block diagram                                                                                         | 77  |

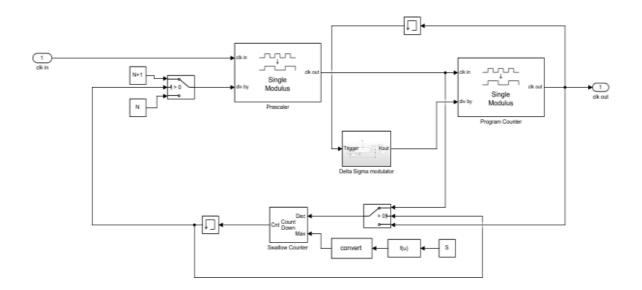

| Figure 4.2  | Pulse swallowing technique                                                                            | 81  |

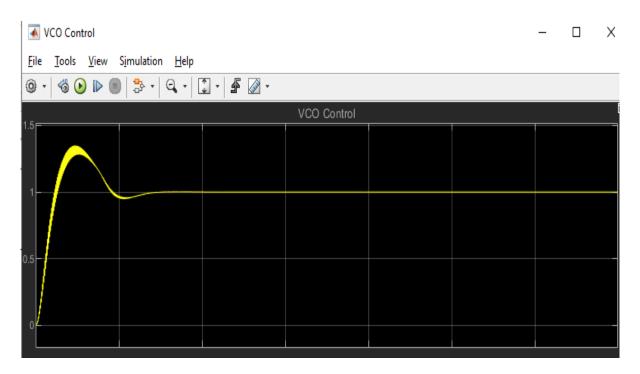

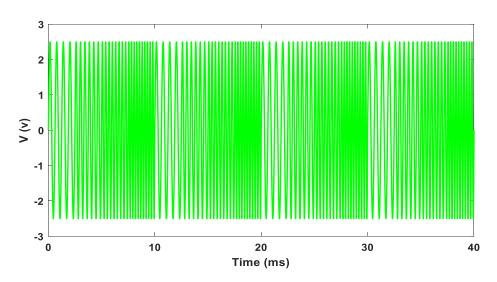

| Figure 4.3  | Wave form of VCO                                                                                      | 82  |

| Figure 4.4  | Feedback network through pulse swalloer circuit                                                       | 84  |

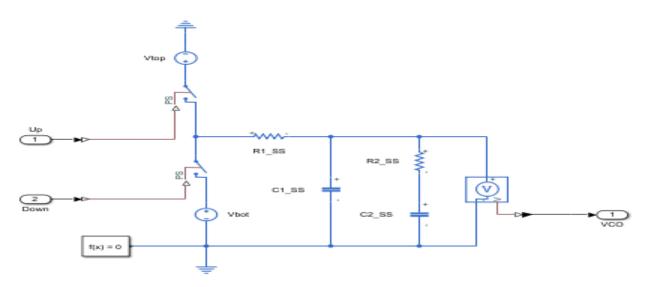

| Figure 4.5  | Charge Pump and low pass filter design                                                                | 84  |

| Figure 4.6  | Wave form of VCO                                                                                      | 86  |

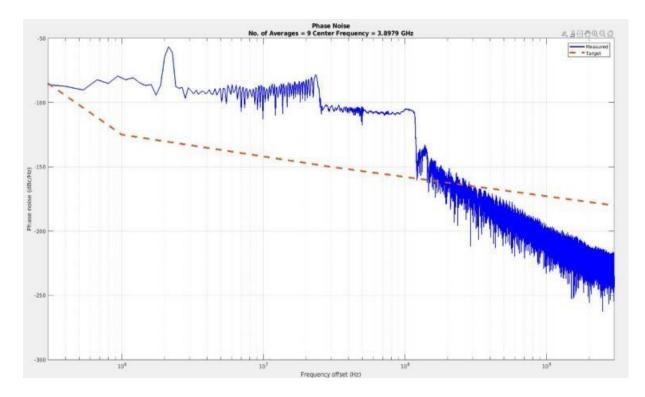

| Figure 4.7  | Phase Noise Plot                                                                                      | 87  |

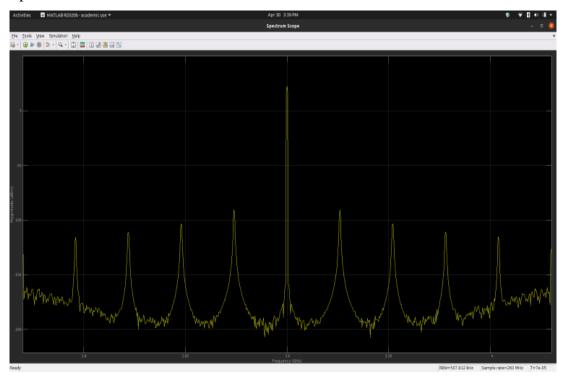

| Figure 4.8  | Frequency Spectrum plot of the Design                                                                 | 88  |

| Figure 5.1  | Architecture of the proposed FS-FNDPLL synthesizer                                                    | 92  |

| Figure 5.2  | Structure of proposed variable TDC                                                                    | 94  |

| Figure 5.3  | Switching rule of AC-TDCSw scheme                                                                     | 97  |

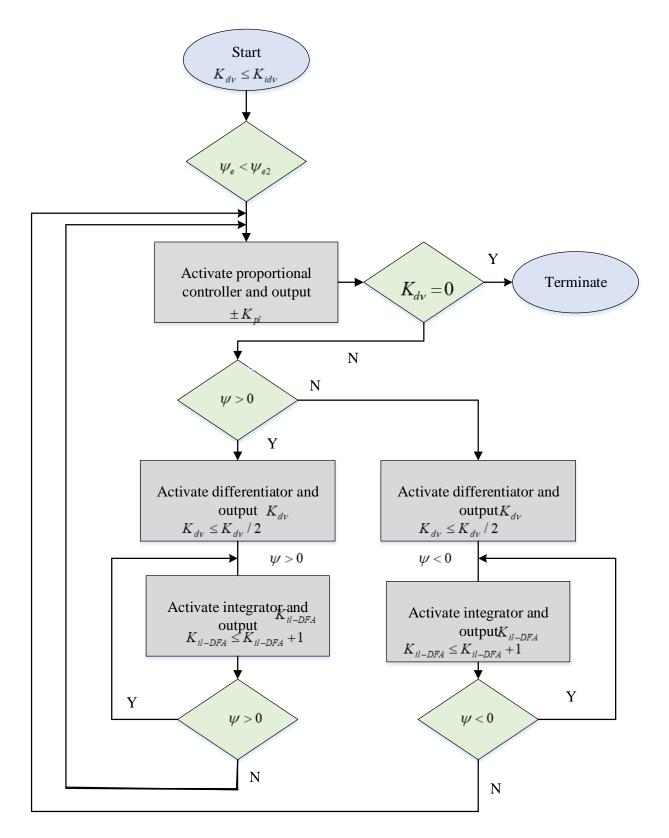

| Figure 5.4  | Process flow of DFA algorithm activated with a BBPD mode                                              | 98  |

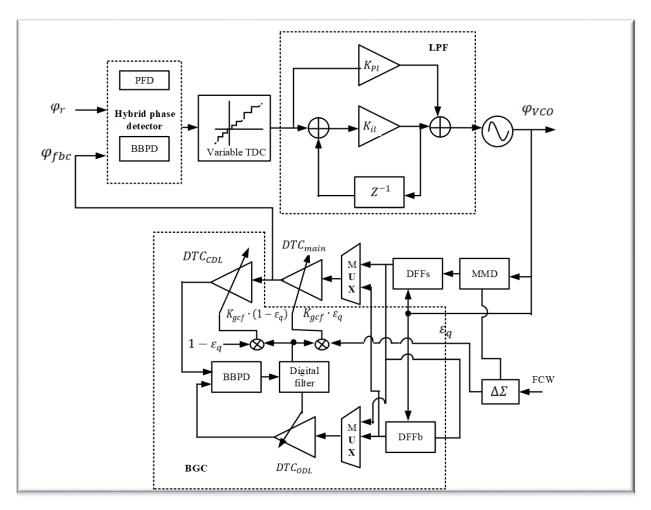

| Figure 5.5  | Architecture of FS-FNDPLL with BGC-DTC                                                                | 101 |

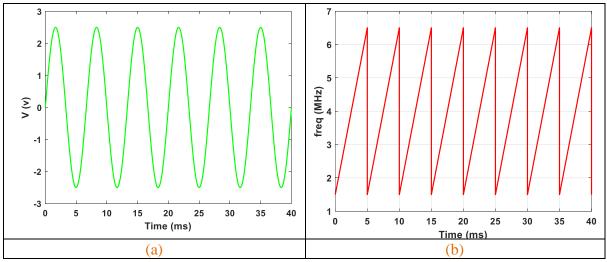

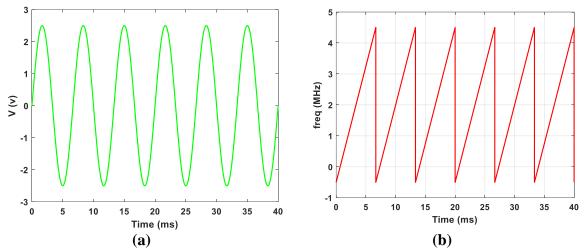

| Figure 5.6  | Input sinsoidal signal of 100MHz and (b) time-frequency plot of input signal for FS-FNDPLL            | 102 |

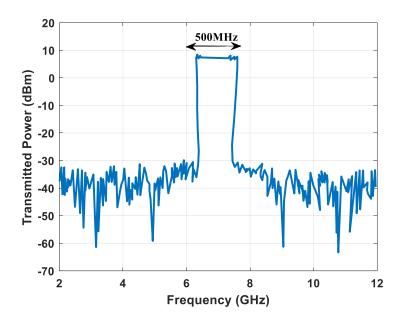

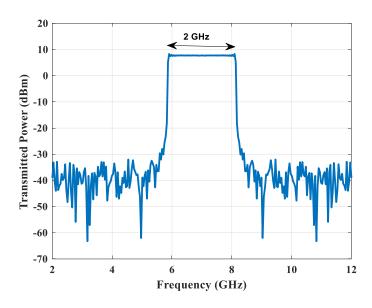

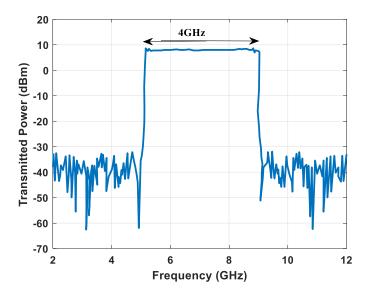

| Figure 5.7  | Transmitted output power                                                                              | 103 |

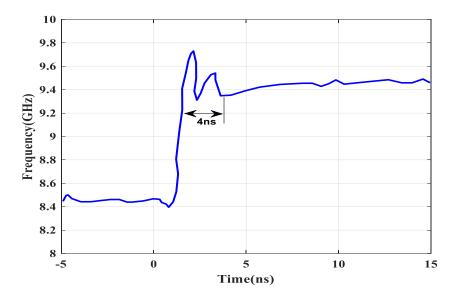

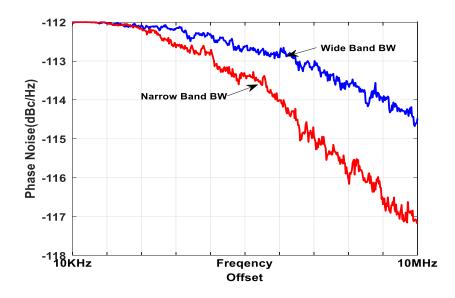

| Figure 5.8  | Evaluation of FS-FNDPLL (a) phase noise (b) settling time                                             | 103 |

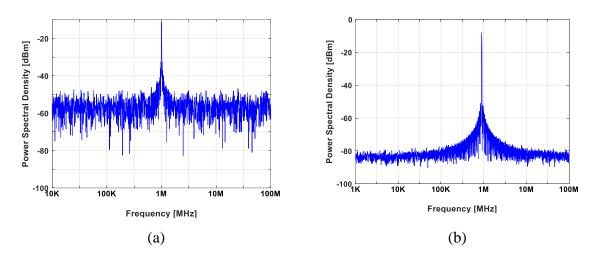

| Figure 5.9  | Output spectrum of FS-FNDPLL (a) without BGC in DTC (b) with BGC in DTC                               | 104 |

| Figure 6.1  | Diagram of the proposed FMCW transmitter                                                              | 107 |

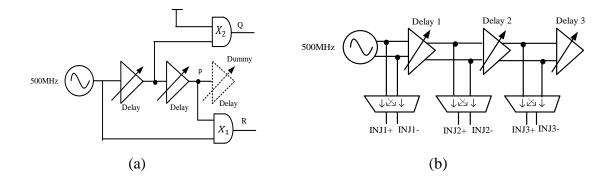

| Figure 6.2  | Injection pulse generator (a) conceptional diagram for pulse<br>generator (b) SSPG                    | 107 |

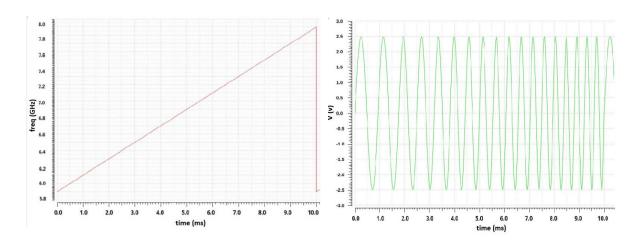

| Figure 6.3  | (a) Input sinsoidal signal of 100MHz and (b) time-frequency plot of input signal for FMCW transmitter | 109 |

| Figure 6.4  | Time-frequency plot of FMCW signal for one sweep period and   | 109 |

|-------------|---------------------------------------------------------------|-----|

|             | Time-amplitude plot of FMCW signal for one sweep period       |     |

| Figure 6.5  | Measured output spectrum                                      | 110 |

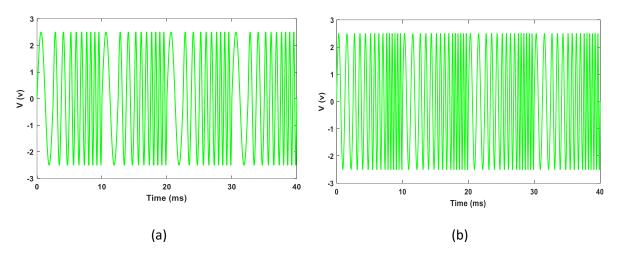

| Figure 6.6  | (a) SSB mixer output for 1GHzand (b) RF mixer output for 2GHz | 110 |

| Figure 6.7  | Output signal with 4 GHz have signal                          | 111 |

| Figure 6.8  | Output signal with 4 GHz have spectrum                        | 111 |

| Figure 6.9  | Switching time analysis of R-PILO                             | 112 |

| Figure 6.10 | Phase analysis of the proposed FMCW transmitter               | 113 |

# **ABBREVIATIONS**

| PLL  | Phase-Lock Loop                     |

|------|-------------------------------------|

| VCO  | Voltage Controlled Oscillator       |

| LPF  | Low-Pass Filter                     |

| СР   | Charge Pump                         |

| PFD  | Phase/Frequency Detector            |

| FMCW | Frequency-Modulated Continuous-Wave |

| DPLL | Digital Phase Locked Loop           |

| RF   | Radio Frequency                     |

| FS   | Frequency Synthesizer               |

| PFD  | Phase Frequency Detector            |

| SoCs | System-On-Chips                     |

| SSC  | Spread Spectrum Clocking            |

| EMI  | Electromagnetic Interference        |

| DTC  | Digital-To-Time Converter           |

| TDC  | Time-To-Digital Converter           |

| DCO  | Digitally Controlled Oscillator     |

| QNC  | Quantization Noise Cancellation     |

| AFC  | Automatic Frequency Control         |

| ICs  | Integrated Circuits                 |

| FMCW | Frequency-Modulated Continuous-Wave |

| BLE  | Bluetooth Low Energy                |

| FHSS | Frequency-Hopped Spread Spectrum    |

| PI   | Phase Interpolation                 |

| SSC  | Spread Spectrum Clocking            |

| DJ   | Deterministic Jitter                |

| ILCM | Injection Locked Clock Multiplier   |

| TP-FPSC      | Triple-Point Frequency/Phase/Slope Calibrator      |

|--------------|----------------------------------------------------|

| SIL          | Self-Injection Locking                             |

| ADDLL        | All-Digital Delay-Locked-Loop                      |

| NCO          | Numerically Controlled Oscillator                  |

| NOCs         | Network On Chips                                   |

| PCS          | Personal Communication System                      |

| FPGA         | Field Programmable Gate Array                      |

| GDI          | Gate Diffusion Input                               |

| MOSFETs      | Metal-Oxide Semiconductor Field-Effect Transistors |

| ТА           | Temporal Amplifier                                 |

| DMRO         | Dual-Mode Ring Oscillator                          |

| PVAPF        | Photovoltaic-Active Power Filter                   |

| CDAC         | Capacitor-Based Digital-To-Analog Converter        |

| RSPD         | Reference Sampling Phase Detector                  |

| MDLL         | Multiplying Delay-Locked Loop                      |

| SPO          | Static Phase Offsets                               |

| BBPD         | Bang-Bang Phase Detector                           |

| DPO          | Dynamic Phase Offsets                              |

| ТРМ          | Two-Point Modulation                               |

| FFD          | Fractional Frequency Dividing                      |

| DPI          | Digital Phase Interpolator                         |

| LSB          | Least Significant Bit                              |

| GEO-SA-BiSAR | Geosynchronous Spaceborne-Airborne Bistatic        |

|              | Synthetic Aperture Radar                           |

| SRR          | Short-Range Radar                                  |

| LRR          | Long-Range Radar                                   |

| EA           | Error Amplifier                                    |

| ADA          | Azimuth Doppler Ambiguity                          |

| VSAR         | Velocity SAR                                       |

| RCMC         | Range Cell Migration Correction                    |

| MIMO  | Multiple Input Multiple Output       |

|-------|--------------------------------------|

| TBS   | Time Domain Bandwidth Synthesis      |

| MDLL  | Multiplying Delay Locked Loop        |

| SSPLL | Sub-Sampling-Based PLL               |

| S-PLL | Sampling PLL                         |

| СР    | Charge Pump's                        |

| NPS   | Narrow Pulse Shielding               |

| PG    | Pulse Generator                      |

| SOGI  | Second-Order Generalized Integrators |

| PID   | Proportional Derivative Integral     |

| FFT   | Fast Fourier Transform               |

| PMAF  | Pre-Filtering Moving Average Filter  |

#### **CHAPTER 1**

#### **INTRODUCTION**

#### **1.1 Overview**

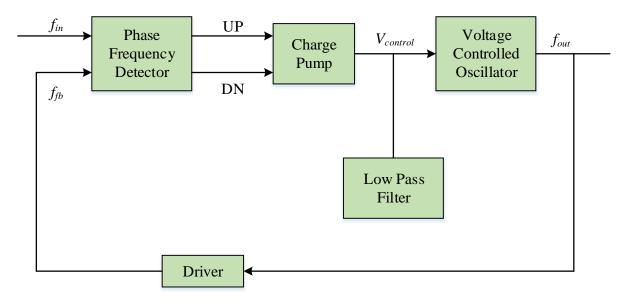

PLLs are necessary to synchronize and retime the input data on the receiver side. A Phase/Frequency Detector (PFD), Voltage-Controlled Oscillator (VCO), Charge Pump (CP), Low-Pass Filter (LPF), and frequency divider make up a typical single-loop PLL [1]. A fractional PLL is designed by choosing the PLL's constituent parts, such as the Phase Detector (PD), loop filter, fractional divider, and VCO, and then fine-tuning their parameters to attain the desired frequency constancy, phase noise, and stability achievement. Steps needed in creating a fractional PLL in general [2] identify the required input and output frequency. The output frequency is the preferred value of the output clock signal, and the input frequency is the reference frequency signal. To detect phase differences among reference and output signals. To produce an error of signal proportionate to that phase difference, choose the phase detector. There are various different types of phase detectors, each with advantages and limitations, including XOR, mixer-based, and D-type flip-flops. The most important part of PLL is the design of the loop filter, which stabilizes the PLL by removing noise from the error signal [3]. The fractional-N PLL synthesizers based on Delta-Sigma are commonly used as local oscillators for creating precisely specified frequencies in wireless communication applications. The approach-based FNPLL has many benefits that have led to its widespread application in electronic devices like mobile phones and wireless LANs, including high shift speediness, little phase noise (PN), and compact space between channels. Determine the outcome frequency of a  $\Delta \Sigma$  f-N PLL and an integer-N PLL [4]. To integer multiples of reference frequency, loop some degree. Integer NPLL and FNPLL share many fundamental properties; however, different circuits are employed. Introduce the frequency accurately between a single or nonnegative integer multiple. Fast-settling frequency synthesizers are becoming increasingly popular in Frequency-Modulated Continuous-Wave (FMCW) in the radar system because of their capacity to shorten the chirp signal's idle modulation and time period [5]–[7]. The quick response time of clock generators is crucial for supporting power management strategies like frequency scaling and dynamic voltage [8] as well as in digital SoCs. The Digital PPL (DPLL) is created as a switched scheme with a novel loop-order switching device included in its feedforward channel in order to achieve a quick settling reaction [9]. The high-order integrator and differentiator are called upon by this adaptive mechanism to escalate error tracking responses in the loop. A system that alternates among various loop orders and loop gains would be more likely to deviate from equilibrium or oscillate among various states. This chapter covered the history of phase-locked loops, fractional-n modulation techniques, fractional-n frequency synthesis, and applications of PLLs, as well as their benefits and drawbacks. This chapter also includes motivation, a problem description, research objectives, and a thesis organization.

#### 1.2 Background information of Phase Locked Loop

The phase-locked loops (PLLs) were operated at high frequency and speed. Therefore, it is necessary to possess in-depth knowledge of the theory's foundational ideas on PLLs, dynamic behavioural traits, and transistor size scaling. Some performance measurement characteristics, such as speed, settling time, and hold time, and decreased jitter with minimal power consumption, are highlighted and elaborated for high-frequency operation based on the simulation findings attained. The fundamental need for charge pump phase-locked loops with very high clock frequencies in the range of GHz is growing quickly as high-data-rate transmission technologies. PLLs are usually used in radio frequency (RF) [10], digital, and analog communication systems. PLLs can produce low-jitter, high-frequency clocks with little temporal skew. To successfully recover the data broadcast from the transmitter, PLLs are also utilized in clock and data recovery [11] circuits. PLL refers to a system that locks to a specific phase or frequency signal when processing or synchronizing data. Software PLL, analog PLL, all-digital PLL, and digital PLL (DPLL) are some of the different types of PLL. These are categorized based on their analog and digital blocks.

These current system applications drive the designs of PLL, and as a result, the specifications required vary. A low power, completely integrated, low cost, and high performance Integer-N digital PLL frequency synthesizer is required by applications including frequency multipliers, radar, cell phones, data synchronization, and telecommunications. Research has confirmed the CP in the integer-N digital PLL [12]. In an indirect frequency synthesizer, the PLL is a crucial component. The frequency division and/or multiplication can be carried out by a PLL in conjunction with divider components. The majority of the frequency synthesizers sector is still held by a number of PLL design variants today. In addition to enhancing portability across coming CMOS technologies, a solid understanding of PLL frequency synthesizer (FS) design can save development costs and shorten time to market.

An essential component of an indirect frequency synthesizer is the PLL. A PLL in conjunction with divider elements can be used to multiply and/or divide frequencies. Today, a number of

PLL design variants continue to dominate the market for frequency synthesizers. In addition to enhancing portability across forthcoming CMOS technologies, a solid understanding of PLL frequency synthesizer (FS) design can save development costs and shorten time-to-market.

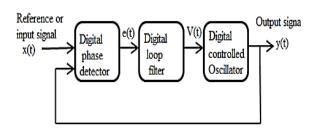

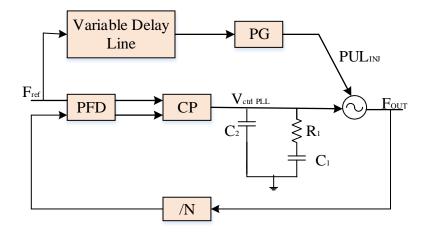

Figure 1.1: Block Diagram of Digital Phase Locked Loop [13]

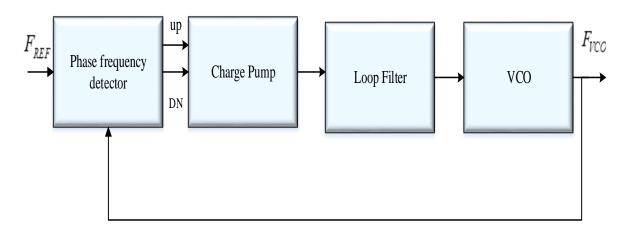

The illustration of digital PLL is displayed in the Figure 1.1. The VCO, LPF, CP, and phase frequency detector (PFD) are the main components of these DPLLs [13]. PFD and divider in this case are digital in nature.

#### **1.3 Fractional-N modulation methods**

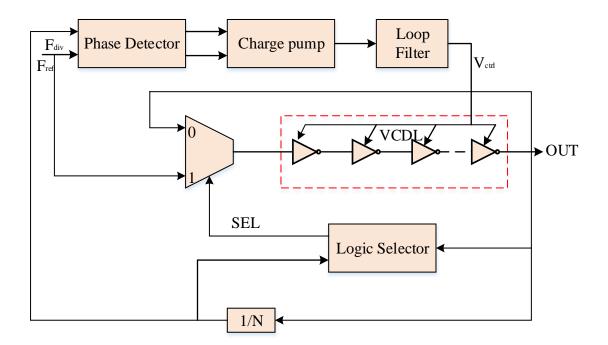

Modern system-on-chips (SoCs) are capable of performing a wide range of analog, mixedsignal, digital, and radio frequency tasks. A SoC often consists of a wide range of things, including wireless transceivers, modules, I/O interfaces, memory, and multicore processors [14]. These modules each operate in a separate clock domain tailored to their preferred outcome. In contrast, a CPU may need Spread Spectrum Clocking (SSC) to decrease Electro-Magnetic Interference (EMI) or quick frequency switching to provide power-saving strategies like Dynamic Frequency Scaling (DFS) [15]. For instance, I/O interfaces need low-jitter highfrequency clocks. Additionally, dynamically adjustable per-core clock generators are needed for today's multicore processors because they must offer quick frequency switching without frequency overrun and adhere to strict settling time, power, and area limits. SoC clock producers were commonly designed as Fractional-N Phase-Locked Loops (FNPLLs) to satisfy these various criteria. However, PLL bandwidth (BW) restricts the degree of EMI reduction and the shortest attainable settling time during frequency switching [16]. The BW restriction can be bypassed using a two-point modulation approach and calibrated modulation routes [17]. However, its use in the dynamically variable SoC clock generators is constrained by the calibration's extremely sluggish settling time. Open-loop modulation of digital delay lines or multi-phase switching, on the other hand, can provide a great decrease in EMI and accurate depth of the modulation [18], but they have a significant deterministic jitter (DJ) issue. Multiple independent output clocks are produced between the frequencies of 20 to 1000 MHz using a digital PLL's low-jitter high-frequency clock.

The BW restriction of FNPLLs is overridden by the open loop architecture, which also achieves almost infinite modulation of the spread spectrum as well as instantaneous frequency switching without any frequency overshoot. A high-resolution Digital-to-Time Converter (DTC) is used to implement the suggested background calibrated quantization error cancellation approach, which results in outstanding jitter performance.

#### 1.3.1 Fractional-N PLLs (Closed Loop)

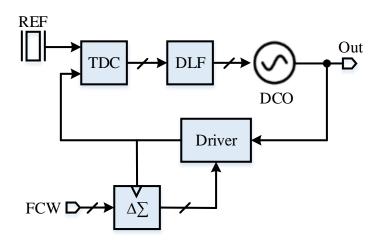

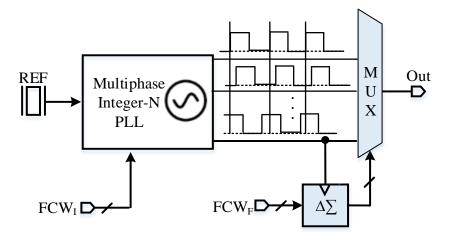

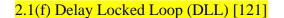

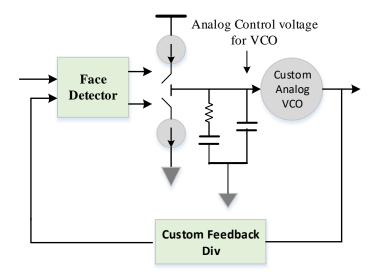

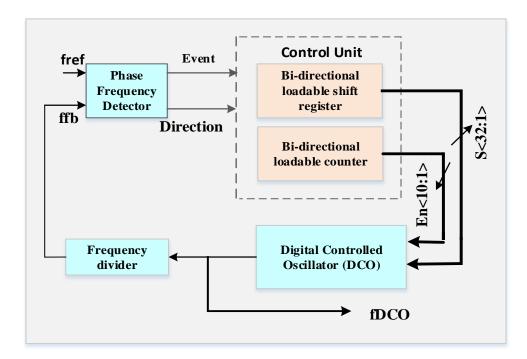

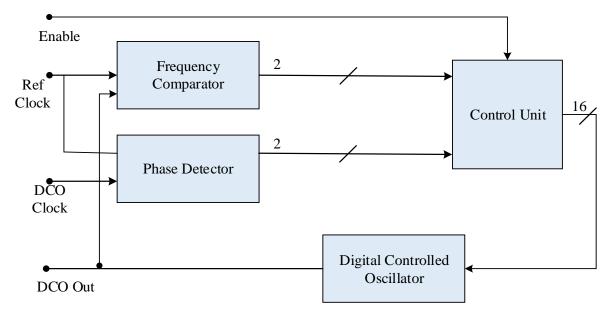

The feedback divider is dithered using D modulator to operate in the fractional-N mode. Phase errors among reference and dithered feedback clocks are found using Time-to-Digital Converter (TDC) [19]. The diagram of typical Digital FNPLL is displayed Figure 1.2.

Figure 1.2: Block diagram of conventional fractional-N synthesizers using  $\Delta \Sigma$ -digital FNPLL [16]

In order to adjust the frequency of the Digitally Controlled Oscillator (DCO), TDC output is filtered by a digital loop filter. The PLL-BW controls jitter performance and is difficult to optimize under opposing demands. Low-pass filtering of shaped quantization noise is aided by a narrow PLL-BW, but the modulation BW is constrained, and oscillator phase noise is

insufficiently filtered as an outcome [20]. In order to avoid this tradeoff and achieve excellent jitter performance, Quantization Noise Cancellation (QNC) methods [21] might be used. However, they are prone to mismatches between the two modulation pathways. Two-point processes and modulation approaches can expand modulation BW [22]. In order to accurate path mismatches across voltage and temperature differences, background gain calibration [23] can be used. However, because of the calibration's slow convergence, this method is not suitable for SoC clock generators where the modulation parameters and output frequency must be changed automatically.

#### 1.3.2 Multi-Phase Switching (Open Loop)

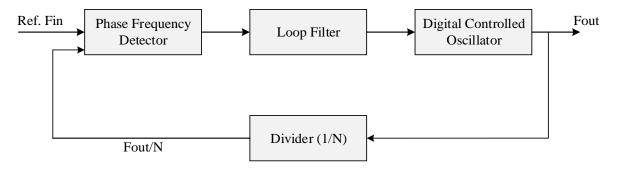

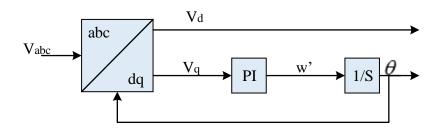

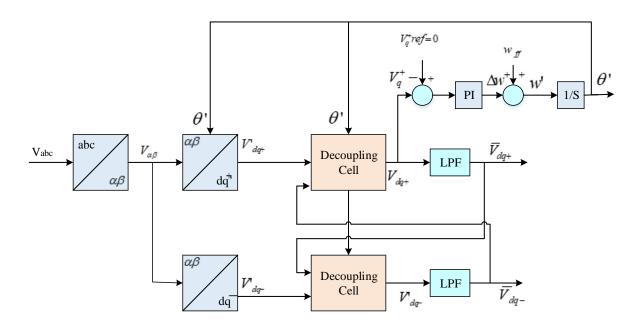

The modulation BW constraint of FNPLLs was addressed by the proposal of open-loop frequency synthesis-based phase switching. Rotating M evenly spaced clock signals with similar phase and frequency gap between adjacent signals was used to accomplish fractional-N synthesis, as given in Figure 1.3.

Figure 1.3: Block diagram of conventional fractional-N synthesizers using  $\Delta \Sigma$ -based phase switching [16]

Ring oscillators built into integer-N PLLs or conventional quadrature generating methods are frequently used to create these clock phases. A digital phase accumulator incorporates fractional frequency control words, or FCWF, and produces the phase multiplexor's control sequence. Phase interpolators are employed to increase resolution due to the output frequency resolution being determined by the very low phase separation [24]. By driving the phase accumulator with a digital modulator, it is possible to attain finer frequency resolution. In order to eliminate the shaped quantization error, a QNC technique is put forth that involves directly modifying the VCO of a multi-phase clock generator. This resulted in the simultaneous

achievement of low-phase noise and open-loop modulation performance. Perfect QNC is sensitive to PVT changes because it involves reasonably accurate knowledge of KVCO in VCO gain. Additionally, the multi-phase clock generator is not shared, so this solution is unable to produce several independent outputs. The performance of spurious and phase noise is diminished by digital-to-phase conversion's nonlinearity. To reduce performance degradation, routing pathways and VCO delay cells must be exactly matched [16]. The requirement for the determination of numerous high-frequency clocks dramatically raises the power consumption of strategy. An open loop FDIV method that can attain fine resolution and low jitter in light of the shortcomings of current open loop modulators.

#### **1.4 Fractional-N Frequency Synthesis**

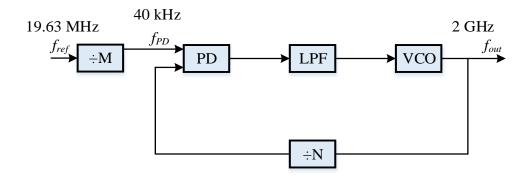

In multi-standard transceiver systems, PLL-based frequency synthesizers are essential. When the frequency division ratio must be particularly high, the integer-N PLL struggles to meet design trade-offs. The block diagram for the device that produces 2 GHz output at a stable crystal frequency of 19.68 MHz is shown in Figure 1.4.

Figure 1.4: Frequency synthesis example with integer-N PLL [25]

In order to achieve the 200 kHz frequency resolution for channel rasters, such as WCDMA systems, the phase detector frequency must be set to 40 kHz and the frequency division ratio must be 50,000. In that situation, phase detectors and reference sources's in-band noise contributions are increased by 114 dB at VCO output. Additionally, PLL BW can only a few kHz for stability with a phase detector frequency of 40 kHz, causing VCO noise suppression and a protracted settling time. The fractional-N PLL provides the number of benefits over the integer-N PLL due to PD frequency being greater than resolution frequency. Unwanted spur production, which is brought on by the dual modulus divider's periodic operation, is the fractional-N PLL's special difficulty. If the fractional spurs are not suppressed, the fractional-

N frequency synthesis is useless for real-world applications. Therefore, more circuitry is required to reduce those fractional spurs.

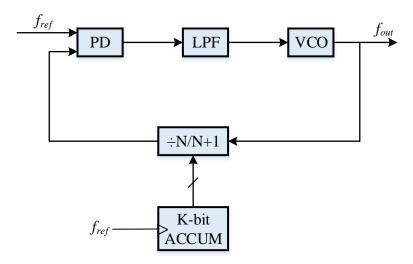

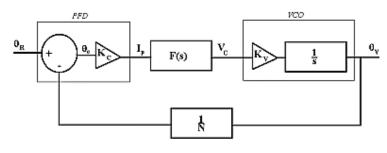

#### **1.4.1 Fractional-N PLL**

The PD frequency cannot match the fine-resolution frequency of fractional-N PLL. The Digiphase methodology, which uses digital control of the phase to interpolate the frequency, is where the fractional-N method first emerged [26]. The illustration of conventional fractional-N PLL is provided in Figure 1.5.

Figure 1.5: Block Diagram of Fractional-N PLL [26]

The dual modulus divider's control input is regularly modulated to produce a fractional division ratio. Such periodic modulation produces an undesirable spur.

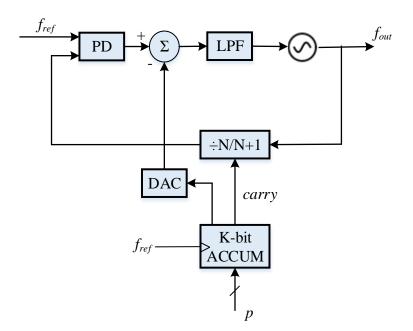

#### 1.4.1.1 DAC Cancellation Method

A common surge reduction technique is phase cancellation utilizing a Digital-to-Analog Converter (DAC). Figure 1.6 depicts the fundamental design and how it functions.

Figure 1.6: Fundamental Block Diagram of DAC Cancellation [27]

This method has analog flaws since phase error is corrected in the voltage field. The DAC resolution and accuracy limitations are the main causes of the discrepancy. The DAC only requires to match dc voltage for one reference clock period; this technique is highly efficient when an S/H phase detector rather than a phase/frequency detector (P/FD) is utilized.

## 1.4.1.2 Phase Interpolation Method

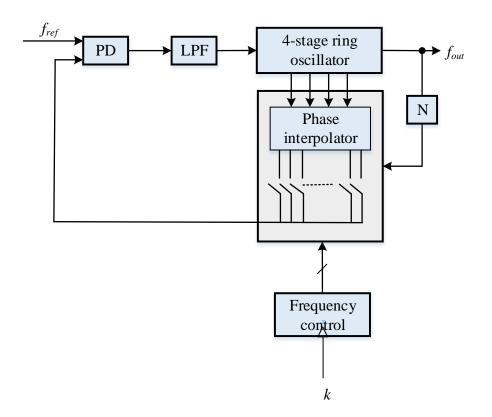

A fractional divider is implemented as shown in Figure 1.7 by taking use of the N distinct phases that N-stage ring oscillator creates.

Figure 1.7: Block Diagram of Phase interpolation method [28]

The phase interpolator is provided to create finer phases using obtainable stages from multiphase ring VCO because the ring oscillator's number of inverters is constrained. A fractional division is accomplished by picking the ideal interpolated phase from the available phases. Any mistake in interval of timing was inserted phase edges produce secure tones since phase edges provided for fractional division ratio are chosen frequently.

#### 1.4.1.3 Random Jittering Method

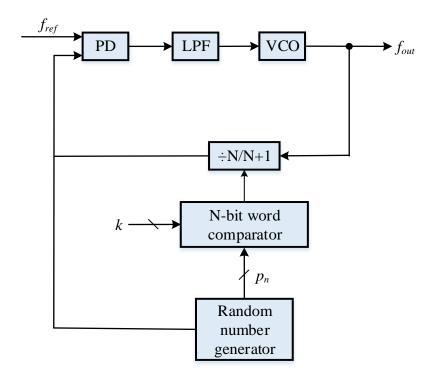

The conventional fractional-N synthesizers perform poorly for fractional spurs when analog matching is not properly managed. In addition, the VCO output frequency affects design complexity. The section of the VCO time, which is as low as 10<sup>-3</sup> rad, is the instantaneous phase error that must be negated at PD outcome. By digitally randomizing the sequence of dual-modulus divider control bits, a random jittering solution resolves the spur issue in the digital realm [28]. The illustration of a fractional-N divider with random jittering is shown in Figure 1.8.

Figure 1.8: Block Diagram of Random jittering method [28]

The random number producer yields a new random word  $P_n$  at each outcome of the divider, which is associated with the frequency word K. The dual-modulus divider is controlled by the frequency word K so that the average value tracks the required fractional division ratio. The white noise injection in the frequency domain causes  $1/f^2$  noise in the phase domain, which causes frequency jitter in this method.

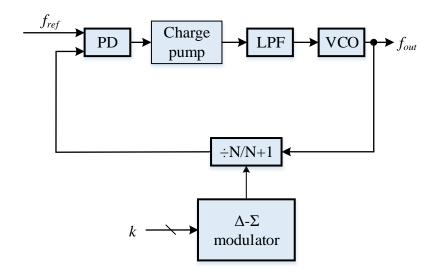

### 1.4.2 Frequency synthesis with $\Delta\Sigma$ modulation

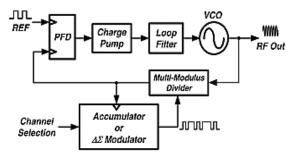

An essential component of contemporary transceiver systems, the  $\Delta\Sigma$  fractional-N frequency synthesizer provides direct digital frequency modulation for low-budget transmitter construction. The fundamental method is to interpolate fractional frequency using a coarse integer divider and an oversampling  $\Delta\Sigma$  modulator, as shown in Figure 1.9.

**Figure 1.9:** Block Diagram of  $\Delta\Sigma$  fractional-N PLLs [29]

Higher VCO frequency causes greater spur reduction challenges for conventional finitemodulo  $\Delta\Sigma$  fractional-N PLLs, although the resolution of these PLLs is independent of VCO frequency. One can easily achieve an extremely fine frequency resolution, such as 1 Hz, by simply increasing the modulation bit count. This technique is related to the random jittering technique; however, due to the shaping of the noise ability of the  $\Delta\Sigma$  modulator, it does not produce a frequency jitter.

#### **1.5 Applications of PLL**

A PLL is flexible electronic circuit that finds applications in a different industries due to its capability to synchronize signals, regulate frequencies, and retrieve timing information. PLLs are used in the following typical applications:

#### > Clock Recovery

PLLs are frequently provided in communication schemes to recover the clock signal from a stream of incoming data for clock recovery. For accurate data demodulation, this is essential.

#### Frequency Synthesis

PLLs are capable of producing precise and consistent output frequencies by securing with a source of reference frequency. This is necessary for many applications, such as RF transmission, the creation of local oscillators for transceivers, and the manufacture of clocks for microprocessors.

#### Frequency Modulation and Demodulation

PLLs can be used to demodulate a modulated signal (frequency demodulation) or to modulate a carrier signal with information (frequency modulation). This is used, for instance, in FM radio receivers.

#### > Phase noise reduction

PLLs are capable of helping oscillators in reducing phase noise, producing clearer and more stable signals. RF and microwave applications need to take this into consideration.

#### > Data Synchronization

In digital communication, PLLs are used to accurately recover data by synchronizing the receiver's clock with the incoming data stream.

#### Frequency Tracking and Control

PLLs are capable of tracking and controlling a signal's frequency within a specific range. This is applied in radar systems and automatic frequency control (AFC) circuits.

#### Signal locking and tracking

PLLs are employed in tracking systems to lock onto and follow a signal source's phase or frequency. This is typical in satellite communication, radar systems, and GPS receivers.

### Frequency Divider and Multiplier

PLLs have the ability to divide or multiple the frequency of an input signal, which is advantageous for both clock distribution and signal processing.

### Phase-Locked Loop Detectors

PLLs are used to monitor phase differences and retrieve signals buried in noise in a variety of detectors, including phase detectors and lock-in amplifiers.

#### Spread Spectrum Communication

In spread spectrum systems, the dispreading spreading code is synchronized with the received signal using PLLs. Both GPS and wireless communication employ this technology.

#### > Motor Control

PLLs can be used in motor control systems to precisely manage the speed and position of motors in a variety of applications, such as industrial automation and robotics.

#### Audio and Video Processing

PLLs are utilized in consumer electronics like DVD players and HDTVs for audio and video synchronization, jitter reduction, and clock generation.

# Frequency Hopping

To increase communication security and dependability, frequency-hopping spread spectrum systems use PLLs to quickly switch between various carrier frequencies.

# > Test and Measurement Equipment

To reliably create, modulate, and demodulate signals, PLLs are used in signal generators, spectrum analyzers, and other test and measurement instruments.

# Wireless Communication

PLLs are essential parts of wireless transceivers for the generation and synchronization of carrier frequencies as well as for the establishment of reliable communication links.

PLLs are essential in a variety of applications where accurate timing, synchronization, and frequency control are essential because to their flexibility and adaptability.

## 1.6 Advantages of PLL

PLLs are generally utilized in electronics and communications because of their many benefits, which include:

## Frequency Stability

PLLs can produce output frequencies that are extremely stable and accurate by locking onto a reference signal. Applications like frequency synthesis and clock generation depend on this stability.

# Frequency Control

PLLs are the best choice for applications that call for modulation or fine-tuning of the output frequency since they provide precise control over this parameter.

# > Frequency Multiplication and Division

PLLs have the ability to be programmed to multiply or divide the input frequency, giving them flexibility in the creation and manipulation of signals.

# Clock Recovery

To ensure precise data reception and synchronization, PLLs are employed to recover clock signals from data streams.

# > Noise reduction

PLLs can lower jitter and phase noise in signals, making communication clearer and more dependable.

#### > Synchronization

PLLs are used for synchronization to make sure that various signals or systems function in unison and at the same frequency.

# > Signal Regeneration

PLLs may restore and correct weak or distorted signals, enhancing the quality of the signal in a variety of applications.

# > Phase and Frequency Tracking

PLLs are capable of keeping track of changes in phase or frequency, which makes them helpful in systems like frequency hopping and radar.

# Data Demodulation

To enable data recovery, PLLs are used to demodulate analog and digital signals, including frequency and phase modulation.

# > Phase Detection

Phase-locked loop detectors are useful in phase-sensitive applications such as phaselocked amplifiers and phase-locked detectors because they can precisely monitor phase differences.

# Wide Range of Applications

PLLs have a wide range of uses, including in telecommunications, wireless communication, audio and video processing, radar systems, GPS, motor control, and test and measurement equipment.

# > Versatility

PLLs are flexible electronic system components that can be modified and designed to perform a variety of tasks.

# **Real-Time Tracking**

PLLs have the ability to modify their output in real-time to stay in sync with an altering input signal.

# > Energy Efficiency

A significant number of contemporary PLL implementations are made with low power consumption in mind, which makes them appropriate for battery-operated gadgets and mobile applications.

# Reduced Component Count

A PLL can replace several discrete components in some applications, simplifying circuit design and cutting costs.

# > Improved Signal Quality

PLLs improve the quality and dependability of signals in applications like communication and data transmission by minimizing phase noise and jitter.

# > Ease of Integration

Contemporary PLLs are frequently offered as integrated circuits (ICs), which make them simple to integrate into electrical systems.

Security and encryption

PLLs synchronize spreading codes and improve security in spread spectrum communication systems, which contribute to secure communication.

# Efficient Signal Processing

PLLs can be employed in signal processing applications for effective frequency and phase alignment.

## > Environmental Change Adaptation

Some PLLs can adjust to environmental changes, including temperature variations, to preserve frequency stability.

Due to these benefits, PLLs have become a crucial and adaptable part of contemporary electronics, enabling accurate frequency control, synchronization, and signal processing for a variety of applications.

## 1.7 Disadvantages of PLL

Although phase-locked loops (PLLs) have many benefits in a variety of electronic and communication applications, they also have several drawbacks and difficulties. PLL drawbacks include the following points:

# > Phase Noise

Phase noise, or random and unwelcome fluctuations in the output signal's phase, can be introduced by PLLs. In RF communication and radar, for example, where low phase noise is essential, this may had effect on signal quality.

> Jitter

Jitter is the signal's departure from real periodicity, which is frequently brought on by phase noise. An excessive amount of jitter can cause data transmission mistakes in high-speed data transfer.

> Locking Time

PLLs may require some time to lock onto the reference frequency or input signal. In applications that need quick synchronization, this lock-in time can present a drawback.

# > Spurious Signals

When running close to the loop's bandwidth limit, PLLs are more likely to emit undesirable spurious signals or harmonics. Other nearby frequencies may be hampered by these erroneous transmissions.

# Design of the Loop Filter

To obtain the desired performance, a PLL's loop filter design, which might be intricate, needs to be carefully tuned. The performance or instability of a loop filter might be affected by improper loop filter design.

# Sensitivity to Reference Signal

PLLs are sensitive to the strength and consistency of the reference signal. The performance of the PLL might be impacted by any alterations or errors in the reference signal.

# Frequency Pulling

PLLs are susceptible to frequency tugging, in which the output frequency is affected by outside signals or noise. This may result in frequency variations from the desired value.

# > Nonlinear Behavior

PLLs may display nonlinear behavior under specific operating situations, which can make their performance unpredictable and difficult to manage.

# > Operating Frequency Range Limitations

The operating frequency range of PLLs may have several restrictions. Operating outside of this range could lead to performance degradation or lock loss.

# > Power Consumption

PLLs have the potential to use an enormous amount of power, which could be problematic for battery-powered devices depending on implementation and operating conditions.

# > Complexity

The design and implementation of PLLs, particularly in high-frequency and highprecision applications, can be challenging. They could need careful parameter adjustment and component selection.

# > Cost

High-performance PLL components can be costly, which may be a factor in applications with tight budgets.

# > Trade-offs

Phase noise, lock time, power consumption, and frequency range are some of the tradeoffs that are frequently made while designing a PLL. Finding the right balance can be difficult.

#### > Compatibility

Considering compatibility is important when integrating PLLs into existing systems since frequency output and phase of PLL must correspond to those of system.

Vulnerability to External Interference

In sensitive applications like RF transmission, external electromagnetic interference (EMI) can impair PLL performance.

#### Limited Bandwidth

Since a PLL has a limited bandwidth, it could not be appropriate for applications using wideband or rapidly changing signals.

PLLs continue to be a useful tool in many applications despite these drawbacks, and engineers frequently employ a variety of strategies to reduce these restrictions and enhance their performance for certain work.

#### **1.8 Motivation**

Periodic spurious tones at integer multiples of frequency orientation can be produced using  $\Delta \Sigma$ -fractional-N PLL with certain divider modulus. Although a small PLL bandwidth minimize the PLL's total performance is reduced, which can counteract the advantages of  $\Delta \Sigma$ -fractional-N approach. The delta-sigma modulator's high oversampling rate makes sure quantization noise produced by modulation is dispersed over a wide frequency range, with the majority of its power in a band that is above PLL's ideal BW. Because they are dispersed in large frequency range and it can be eliminated with a low-pass filter in PLL loop, spurious tones brought by the periodicity of divider modulus are no longer concern. Also, the current synthetic bandwidth-based FMCW SAR Transmitter is complicated due to the use of numerous PLLs, high-speed RF switches, as well as filter banks. Because of this, a fast-switching injectionlocked oscillator (ILO) should be used to simplify the design of a FMCW SAR transmitter of synthetic bandwidth. The current SHILO, takes up more space, decreases power efficiency, and causes crosstalk. These arguments stimulate to produce a new FMCW SAR transmitter by refining the FNDPLL and ILO configurations to improve overall performance while lowering power and space requirements. The minimum settling time that may be achieved is constrained by PLL bandwidth of frequency switching. The FMCW chirp's bandwidth is also expanded using a synthetic bandwidth technique. This method up converts narrowband chirp to other carrier frequencies. Additionally, it makes use of several PLLs, high-speed RF switches, as well as filter banks to facilitate rapid carrier frequency switching. Therefore, overall synthetic bandwidth structure becomes more complex. Therefore, the FMCW SAR Transmitter's architecture needs to be updated in order to decrease complexity and settling time.

#### **1.9 Problem Statement**

Modifying divider modulus resolves the issue of achieving non-integer multiples of reference frequency, cost is incurred as enlarged segment noise. The fractional-N-PLL technique is prepared to improve segment noise performance. Inaccuracies that are introduced into PLL and result in compounded section noise occur at some point during each reference period when actual divider modulus differs from common, or ideal divider modulus. The characteristics of the series of the divider are what determine how much the section noise is increased. There was the use of dual modulus and then the pulse swallowing technique, each of which had their own input limitations, so a new technique was introduced where the divider values will assume the fractional values also to reduce the addition of 20 dB noise in the procedure of frequency multiplication. Pre-scaler networks are used with integer N-PLLs to increase the upper frequency of the counter. Pre-scaler networks hinder the n value to the integers. The random noise group, along with periodic noise and phase noise, are the types of noise that have an effect on PLL performance. The PLL overcomes various challenges by reducing power, taking up less space, and increasing frequency. This comparison includes several PLL.

In order to achieve a quick PLL settling, previous techniques required a very wide PLL bandwidth, significantly raised spur levels and phase noise. Additionally, the phase detectors in the previous FNPLLs were either BBPD or PFD. The settling period of the FNPLL is lengthened by nonlinear Phase Error Detector unit like BBPD, despite its low power consumption. In contrast, PFD uses more power but has a longer settling period. Therefore, a different FMCW SAR transmitter with a quick settling time FNPLL is required. Additionally, for fractional division in low-noise Application, Existing FNDPLL Structures Frequently Rely On DTCs or TDCs. Due of its intricate structure, the DTC uses more energy and is constrained.

#### 1.10 Research Objectives

The main research objectives is given below,

- To achieve improved noise reduction, quick simulation environment, and various methods to lower the phase noise in FNPLL, a FNPLL with a modulator is created in this study.

- To achieve power reduction, reduced area, and high frequency, this work describes the fundamental loop transfer function, noise sources dividers, phase detectors, and fractional-N operation.

- To implement an AC-TDCSw device in forward loop of the FNDPLL to produce an ultra-fast low-noise smooth saw-tooth wideband chirp.

- To design on-chip averaging strategy to lower measurement error and add a mutable TDC by a timing signal interpolation and counter.

- To increase settling time of FNDPLL excluding the need for reference clock, remove quantization noise, and create new DTC-based fractional divider with background gain calibration in feedback path.

#### 1.11 Thesis Organization

The thesis is organized in following way, there are:

#### **Chapter 1: Introduction**

This chapter discussed about Background information of phase locked loop, fractional-n modulation methods, fractional-n frequency synthesis, applications of PLL, advantages of PLL and disadvantages of PLL. Additionally, motivation, problem statement, research objectives and thesis organization are provided in this chapter. And finally concluded with summary.

#### **Chapter 2: Literature Review**

This chapter discussed about the reviews of studies related to PLL based method. Additionally, the comparison of advantages and disadvantages of reviews are provided in tabular representation.

#### **Chapter 3: Preliminaries of PLL and DDS**

This chapter discussed about Preliminaries of PLL and DDS. This chapter includes different existing PPL algorithms, DDS various approaches, comparison analysis among PLL and DDS. Finally the chapter concluded with summary.

#### **Chapter 4: Fractional PLL Performance Improvement through an Optimized Algorithm**

This chapter discussed based on the optimized algorithm to achieve improved performance of fractional PLL. This chapter includes about proposed method and result analysis. Finally this chapter concluded with summary.

## **Chapter 5: Fast-Settling FNDPLL Synthesizer**

This chapter discussed about proposed Fast Settling Fractional-N DPLL synthesizer. This chapter includes about proposed scheme and result analysis. Finally this chapter concluded with summary.

# Chapter 6: FMCW Transmitter with the utilization of R-PILO to produce fast switching adjacent carriers

This chapter discussed about ultra-low-power C-Band FMCW Transmitter utilizing a Fast Settling Fractional-N DPLL as well as ring-based pulse injection locking oscillator approach. This chapter includes about proposed scheme and result analysis. Finally this chapter concluded with summary.

## **Chapter 7: Conclusion and Future scope**

This chapter discussed about the conclusion of the entire research and the direction for future enhancement in the area of PLL based technology.

## 1.12 Summary

A PLL is control system-equipped device that produces an outcome signal which phase is correlated with phase of input signal. A variable frequency oscillator and PD with a feedback loop make up the fundamental electric circuit. It is a closed loop control system structural circuit design whose primary goal is to make it easier for the fed input signal to be phase and frequency synchronized. Nowadays, radar/ranging applications require a transceiver engine with an ultra-low power limitation. Different radars, FMCW radar, pulse, and a including UWB, are used for the range applications. FMCW is a pulsed waveform that has become widely employed in SAR recently to increase transmit power and sensor range. Modern CMOS technological advancements have made it possible to manufacture FMCW radar sensors on a single chip. This chapter covered the background information of phase locked loops, fractional-n modulation techniques, fractional-n frequency synthesis, applications of PLLs, as well as its benefits and drawbacks. This chapter also includes motivation, a problem description, research objectives, and a thesis organization.

#### **CHAPTER 2**

## LITERATURE REVIEW

## 2.1 Overview

The development of low-power, low-jitter frequency synthesizers for transceivers that adhere to the IEEE802.15.4 & Bluetooth low-energy (BLE) specifications has been the subject of numerous studies [29]. Nonetheless, fractional-N PLLs with a quick settling reaction are necessary for certain applications. For instance, the channel-switching period was a crucial part of frequency-hopped spectrum dispersion (FHSS) devices and needed for vital security applications as well as commercial standards like wireless USB with ultra-wideband (UWB). Quick settling frequency synthesizers were being used more often in frequency-modulated continuous-wave (FMCW) sensors because they could lessen the idle time and modulation length of the chirp signal. [30].

Wide chirp bandwidth busing narrowband chirp capability of an FMCW transmitter based on synthetic bandwidth approach had the potential to decouple the aforementioned PLL tradeoff [31]. Only discrete solutions using DDFS, which consumes a lot of power, were exhibited. The SoC project was defined using such a technique. The problem of substituting DDFS with PLL is addressed in this letter, along with suggestions for enhanced efficiency [32]. Ultimately, this leads to the suggested fractional-N PLL including randomised interpolation of phase and a wide loop filter bandwidth (BW).

A wide variety of digital, analog, mixed-signal, and radio frequency jobs can be performed by modern system-on-chips (SoCs) [33]. A SoC frequently comprises of a variety of modules, including memory, I/O interfaces, wireless transceivers, multicore CPUs, and memory. Each of these components runs in a unique clock domain which was developed to satisfy its unique performance needs. For instance, I/O interfaces need low-jitter, high-frequency clocks, whereas a CPU would need EMI (electromagnetic interference) to allow power-saving strategies like dynamic frequency scaling or spread spectrum clocking (SSC) to decrease frequent frequency switching. The amount of EMI decrease and the quickest attainable time to settle during frequencies switching are, nevertheless, constrained by PLL bandwidth (BW). BW restriction can be bypassed using a two-point modulation approach and calibrated modulation routes. However, because to the calibration's incredibly slow settling period, its application in the dynamic adjustable SoC clock generator was limited. [34].