## TESTING AND FAULT ANALYSIS OF EMBEDDED SRAM IN LOW POWER TECHNOLOGIES USING PARASITIC R AND C EXTRACTION METHOD

Thesis Submitted for the Award of the Degree of

## DOCTOR OF PHILOSOPHY in Electronics and Communication Engineering

By

Venkatesham Maddela

**Registration Number: 41900665**

Supervised By Dr.Sanjeet K Sinha (22690) SEEE (Professor) Lovely Professional University Co-Supervised by Dr. Muddapu Parvathi ECE (Professor) BVRIT HYDERABAD College of Engineering for Women

LOVELY PROFESSIONAL UNIVERSITY, PUNJAB 2024

### **DECLARATION**

I, hereby declared that the presented work in the thesis entitled "**Testing and Fault Analysis of Embedded SRAM in Low Power Technologies using Parasitic R and C Extraction Method**" in fulfilment of degree of **Doctor of Philosophy** (**Ph. D.**) is outcome of research work carried out by me under the supervision of Dr.Sanjeet K Sinha, working as Professor, in the School of Electrical and Electronics Engineering of Lovely Professional University, Punjab, India. In keeping with general practice of reporting scientific observations, due acknowledgements have been made whenever work described here has been based on findings of other investigator. This work has not been submitted in part or full to any other University or Institute for the award of any degree.

Joi 10124

(Signature of Scholar)

Name of the scholar: Venkatesham Maddela

Registration No.: 41900665

Department/school: ECE

Lovely Professional University,

Punjab, India

### **CERTIFICATE**

This is to certify that the work reported in the Ph. D. thesis entitled "**Testing and Fault Analysis of Embedded SRAM in Low Power Technologies using Parasitic R and C Extraction Method**" submitted in fulfillment of the requirement for the award of degree of **Doctor of Philosophy (Ph.D.)** in School of Electrical and Electronics Engineering is a research work carried out by Venkatesham Maddela, 41900665, is bonafide record of his original work carried out under my supervision and that no part of thesis has been submitted for any other degree, diploma or equivalent course.

(Signature of Supervisor)(5)Name of supervisor: Dr. Sanjeet K SinhaNameDesignation: ProfessorDesignation: ProfessorDepartment/school: SEEEDesignation: Designation: Versity: Lovely Professional UniversityUniversity: Lovely Professional UniversityUniversity

(Signature of Co-Supervisor) Name of Co-Supervisor: Dr.M.Parvathi Designation: Professor Department/school: ECE University: BVRIT HYDERABAD College of Engg. For Women

## ABSTRACT

According to the International Technology Roadmap for Semiconductors (ITRS), memory occupied up to 94 percent of a SOC space. As a result, memory components dominate the fundamental logic of the SoC and take up greater space in Systems-on-Chip (SoCs). As process technology continues to scale, the test quality, yield, and dependability of current System-on-Chips increasingly rely on their embedded SRAM blocks. Their high integration density, along with a complex manufacturing process, results in minor lithographic flaws that necessitate increasingly effective test solutions to ensure low DPPM (defective parts per million) rates while keeping test costs low. So memories become the key distractor on SoC. As a result, in order to attain the best density and access speed possible, memories must be built independently of technological variance. The majority of existing fault approaches do not address manufacturing-related flaws. Because of its great density and fabrication using very deep submicron (VDSM) technology, testing embedded memory in a chip can be extremely difficult.

SRAMs, which can be utilized with SoCs or as a separate device, have become an essential component of memory in recent years. Because memories are employed in a variety of applications, the number of SRAM cores on SoCs is rapidly expanding. This results in increased density and die size. As with any other type of memory device, technology scaling reduces the size of integrated circuits and increases the density of transistors, resulting in undiscovered flaws. As a result, identifying and troubleshooting SRAM problems is challenging, and efficient test procedures are required. The difficulties in testing SRAMs include test time and fault coverage.

Prior to 1990, fault models like as AC parametric testing and DC parametric testing were utilized to test memory. Static faults are simple flaws that occur in SRAM cells. With a single read or write action, static defects can be exposed. March tests are novel fault models developed based on computational procedures. Electrical fault models are utilized

at the cell level, while Inductive Fault Analysis (IFA) is used at the layout level.

Because testing the memory for all faults is impractical, testing is limited to a subset of defects. This type of fault is referred to as a fault model. Physical spot flaws, which are represented as local irregularities in an SRAM's layout, are utilized to create a fault model for SRAMs. Many errors occur during the production process. Later, based on the sequence of read and write operations, additional test models called as March tests were established. The majority of existing fault models were assessed in terms of well-known March tests, which only provide fault detection information. March testing are effective for checking that SRAMs work properly. With these methodologies, as the fault coverage improves, so does the testing complexity and time. Other faults, termed as dynamic faults, take repeated read and write operations to sensitize. Resistive Dynamic faults are caused by open or bridges. These failures occur in the SRAM cell's address decoder, sense amplifiers, and pre charge circuits (bit lines). These defects are mostly responsible for the cell's electrical failure.

The linked faults occur in two or more cells. It was discovered that there are extremely few studies on coupling problems accessible. The fundamental reason for this is that when more than one cell is examined, the fault number is either doubled or tripled when compared to single cell faults. Because of this flaw magnification, utilizing march algorithms necessitates higher number primitive compositions, which takes a long time. Scaled-down technologies have an impact on parasitic effects, resulting in an extra source of defective behavior and making current test algorithms vulnerable to them. Traditional testing methods do not cover all flaws. To detect undefined defects, a fault model that takes the parasitic effect into account must be developed.

In order to accomplish this, the author developed a layout dependent Extraction of Parasitic R and C approach for fault detection and location identification. A new fault model for SRAM is provided, in which the defective model manifests as local disruptions in the SRAM cell layout. Three technologies are being considered: 45nm, 32nm, and 7

nm. The proposed test approach yielded 100% fault coverage. The test findings for variation levels ranging from Deep submicron (120nm) to Very deep submicron (7nm) are tabulated and examined. The parasitic variations are compared to the parasitic variations of fault-free SRAM. The proposed parasitic extraction method determines the type of fault as well as its position regardless of the specified technology (45nm, 32nm, or 7nm).

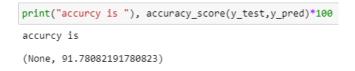

Machine learning has now become an essential method for assessing Embedded Memory. Machine learning improves overall performance and power economy. Machine Learning techniques can also automate the defect identification process. The author employs multiple linear regression to forecast parasite R and C values, with different technologies and lengths serving as independent variables and parasitic R and C serving as dependent variables. The results demonstrate that the parasitic R and C values may be predicted with an accuracy of 88.62%. The decision tree machine learning approach was utilized by the researcher to forecast fault detection and placement. regardless of technology variation, an excellent accuracy score of 91.78% in separating defective memory cells and locating the position of the problem.

Finally, a fault model dictionary that can be used for testing was developed for 45nm, 32nm and 7nm technologies for a single 6T-SRAM cell and multiple 6T-SRAM cells considering all open and short defects. Faults like Stuck at faults (SAF), Write Before Access Fault(WBAF), Undefine Write Fault(UWF), Undefined Read Fault(URF), Unstabilized Write Fault(USWF), Unstabilized Read Fault (USRF), No Access Fault(NAF), Transition Faults(TF), State Coupling faults(CFst), Inversion Coupling Fault(CFin), Fault Masking observed by this method and also we have observed an Undefined faults named as Undefined Short Fault(USF)

#### **OBJECTIVES OF THE PROPOSED WORK**

- 1. Analyze faults due to open defects in Embedded SRAM cell for submicron to deep submicron technologies

- 2. Design a parasitic R and C extraction method for short/bridge defects in SRAM cell using nano meter technologies.

- 3. Develop a fault detection method for open and Short defects in multi cell SRAM architecture

- 4. Design Novel Fault detection and test methods using Machine Learning Algorithms in embedded SRAM architecture

## ACKNOWLEDGEMENT

During the pleasant journey of this thesis work, I have come across many people who have supported and motivated me all throughout my research work and thesis preparation.

First of all, I would like to express my gratitude to my supervisor **Dr. Sanjeet Kumar Sinha** Associate Professor, School of Electronics & Electrical Engineering, Lovely Professional University (Phagwara, Punjab) for his constant support, encouragements, constructive discussions and critical analysis of the research topics. His positive attitude and belief have always motivated me to carry forward my research even during the days of my struggle. I am truly very fortunate to have the opportunity to work with him.

I would also like to thank **Dr. Parvathi Muddapu**, Professor, Electronics & Communication Engineering, BVRIT HYDERABAD College of Engineering for Women (Hyderabad, Telangana) for her guidance and support. I had many fruitful discussions about my work with her. Her scholastic discussions have encouraged me to work on my limitations and constantly improve my work.

I am highly thankful to **Mr. Vinay Sharma**, Director at ni2designs (Pune) for making all the necessary research related licensed softwares available at my disposal.

I am also thankful to all my colleagues of Electronics and Communication Engineering Department and my friends who contributed directly or indirectly through their constructive criticism in my research work.

I extend my deepest gratitude to my family members for their love, affection, encouragement and support during this whole journey.

Venkatesham Maddela

# **TABLE OF CONTENTS**

| ABSTRACTi                                                   |

|-------------------------------------------------------------|

| ACKNOWLEDGEMENT v                                           |

| TABLE OF CONTENTS vii                                       |

| LIST OF TABLES xi                                           |

| LIST OF FIGURES xiii                                        |

| LIST OF ABBREVIATIONS xvi                                   |

| CHAPTER 1: INTRODUCTION                                     |

| 1.1 Semiconductor Memories Challenges                       |

| 1.1.1 Embedded Memories4                                    |

| 1.1.2 External Memory Devices                               |

| 1.1.3 Embedded Memories Vs External (Stand Alone) Memories5 |

| 1.2 Need of Memory Testing                                  |

| 1.3 SRAM Core Cell Operation                                |

| 1.4 Faults and Fault Models 10                              |

| 1.4.1. Assertion Faults10                                   |

| 1.4.2. Behavioural Faults10                                 |

| 1.4.3. Branch Faults11                                      |

| 1.4.4. Bridging Faults11                                    |

| 1.4.5. Cross point Faults11                                 |

| 1.4.6. Defect Oriented Faults                               |

| 1.4.7. Delay Faults12                                       |

| 1.4.8. Pattern Sensitive Faults12                           |

| 1.4.9. Physical Faults13                                    |

| 1.4.10. PLA Faults                                                   | 13 |

|----------------------------------------------------------------------|----|

| 1.4.11. Redundant Fault                                              | 13 |

| 1.4.12. Memory Faults                                                | 13 |

| 1.4.13. Stuck at faults                                              | 14 |

| 1.4.14. Transition fault                                             | 15 |

| 1.4.15. Coupling Faults                                              | 15 |

| 1.4.16. Bridging Faults                                              | 16 |

| 1.4.17. Address Decoder Faults                                       | 18 |

| 1.4.18. Neighborhood Pattern Sensitive Faults                        |    |

| 1.4.19. Data Retention faults                                        |    |

| 1.5 Concept of Fault Primitives                                      | 19 |

| 1.5.1. Single cell static FFMs                                       | 19 |

| 1.5.2. Double cell static FFMs                                       | 20 |

| 1.6 Motivation                                                       | 22 |

| 1.7 Objectives and Scope of the Work                                 | 23 |

| 1.7.1 Objective of the proposed work                                 | 24 |

| 1.7.2 Tools used for the proposed work                               | 25 |

| 1.7.2 Organization of the thesis                                     | 25 |

| CHAPTER 2: LITERATURE REVIEW                                         | 26 |

| CHAPTER 3: PROPOSED PARASITIC EXTRACTION METHOD                      | 47 |

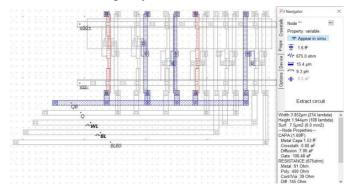

| 3.1 Method of Parasitic Extraction and Test Approach Using Microwind |    |

| 3.2 Proposed Fault Model with Open Defects in Single Cell SRAM       | 52 |

| 3.3 Faults Identified for Open Defects for different technologies    | 53 |

| 3.3.1 No Access Fault                                                | 55 |

| 3.3.2 .Undefined Read Fault                                            | 56  |

|------------------------------------------------------------------------|-----|

| 3.3.3 .Undefined Write Fault                                           | 57  |

| 3.3.4 .Transition Fault                                                | 58  |

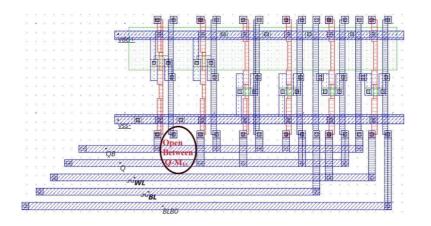

| 3.4 Extraction of Parasitic R, C at 6T-SRAM node points                | 59  |

| 3.5 Fault Detection Using Parasitic R, C Extraction Method             | 61  |

| 3.5.1. Open Fault Detection for 32nm Technology                        |     |

| 3.5.2. Open Fault Detection for 45nm Technology                        |     |

| 3.6 6T SRAM Cell analysis for short Defects                            |     |

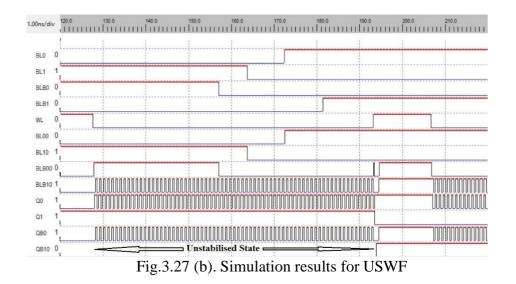

| 3.6.1 . Unstabilized Write Fault (USWF)                                | 73  |

| 3.6.2 . Unstabilized Read Fault (USRF)                                 | 74  |

| 3.6.3 . Write Before Access Fault(WBAF)                                | 74  |

| 3.6.4. Initialization Order Fault (IOF)                                | 76  |

| 3.6.5. Read Destructive Retention Fault                                | 77  |

| 3.7 Fault Detection Using Parasitic R, C Method for short faults       | 79  |

| 3.7.1. Short Fault Detection for 45nm Technology                       |     |

| 3.7.2. Short Fault Detection for 32nm Technology                       | 83  |

| 3.7.3. Short Fault Detection for 7nm Technology                        | 86  |

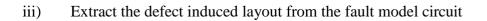

| 3.8 Fault Models In Two-Cell SRAM Architecture                         | 89  |

| 3.8.1 Analysis of Coupling Faults                                      | 89  |

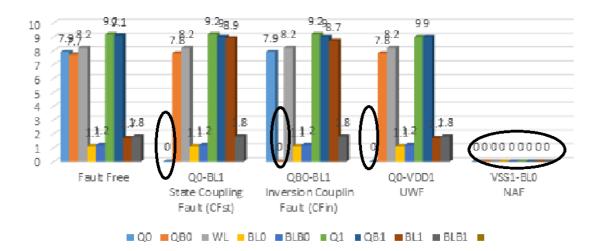

| 3.8.2 Linked Fault Detection using Extraction of Parasitic R, C Method |     |

| CHAPTER 4: MACHINE LEARNING BASED PARASITIC EXTRACTION<br>METHOD       |     |

| 4.1 Need of Machine Learning in VLSI Design                            | 105 |

| 4.2 Machine Learning Applications in VLSI                              | 105 |

| 4.3 Improving VLSI Design with Machine Learning Algorithms             | 105 |

|   | 4.4 Machine Learning Techniques for VLSI Layout Optimization                   | .107 |

|---|--------------------------------------------------------------------------------|------|

|   | 4.5 Machine Learning-Based Fault Detection and Diagnosis in VLSI Circuits      | .107 |

|   | 4.6 Challenges and Limitations of Machine Learning in VLSI                     | .108 |

|   | 4.7 Machine Learning Techniques in embedded Memory                             | .109 |

|   | 4.8 Machine Learning Design Methodology                                        | .112 |

|   | 4.9 Determination of Parasitic R, C values by using Multiple Linear Regression | .114 |

|   | 4.10Building a Decision Tree for fault detection in SRAM Cell                  | .121 |

| ( | CHAPTER 5: CONCLUSION FUTURE SCOPE                                             | 123  |

# LIST OF TABLES

| Table 1.1 Single Cell Static Functional Fault Models    20                                              |

|---------------------------------------------------------------------------------------------------------|

| Table 1.2 Double cell static FFMs    21                                                                 |

| Table 2.1 Comparison of Literature Review                                                               |

| Table 3.1 Technological Evaluation                                                                      |

| Table 3.2 Comparison of Transistor Parameter for different technologies       51                        |

| Table 3.3 Open Fault Dictionary for Single Cell 6T SRAM.                                                |

| Table 3.4 Parasitic R, C values of Fault Free SRAM Cell for different technologies60                    |

| Table 3.5 Fault Models for all open faults                                                              |

| Table 3.6 Parasitic R, C at affected nodes for chosen open fault models using 32nm         Technology   |

| Table 3.7 Extracted R, C Values Single 6T-SRAM cell for all open defects using 32nm         Technology  |

| Table 3.8 Parasitic R, C at affected nodes for chosen open fault models for 45nm         Technology     |

| Table 3.9 Extracted R, C Values Single 6T-SRAM cell for all open defects using 45nmTechnology           |

| Table 3.10 Node equivalence corresponding to main nodes                                                 |

| Table-3.11: Complete Fault Model Dictionary for short defects for different technologies                |

| Table 3.12 Parasitic R, C at affected nodes for chosen short fault models using 45nm         Technology |

| Table 3.13 Complete fault model dictionary for all short faults using 45nm technology82                 |

| Table 3.14 Parasitic R, C at affected nodes for chosen short fault models using 32nm      Technology    |

| Table 3.15 Extracted parasitic R,C values for all Short defects(32nm)    85                             |

| Table3.16. Variation of parasitic C values for SRAM short defect model (7nm)                            |

| Table 3.17. Variation of parasitic R, C values for SRAM short defect model (7nm)86                      |

| Table:3.18: Extracted R,C values for all Short defects(7nm)                                                 |

|-------------------------------------------------------------------------------------------------------------|

| Table3.19: Fault Dictionary for two Cell 6T SRAM for coupling short faults92                                |

| Table.3.20 Fault Detection with Parasitic R, C in Two Cell Fault Models                                     |

| Table 4.1 Extracted R, C values for fault free single 6T-SRAM cell using different technologies         115 |

| Table 4.2. Extracted R and C values for faulty and fault free SRAM at different nodes120                    |

| Table 4.3. Fault Coverage Comparison of different methods                                                   |

| Table 4.4. Comparison between different Machine Learning algorithms                                         |

# LIST OF FIGURES

| Figure 1.1. Types of Semiconductor Memories                                   |

|-------------------------------------------------------------------------------|

| Figure 1.2 6T SRAM memory cell 8                                              |

| Figure 1.3a Read Operation of SRAM Cell9                                      |

| Figure 1.3b Write Operation of SRAM Cell                                      |

| Figure 1.4(a) State Diagram of a Fault-free Circuit                           |

| Figure 1.4(b) Stuck at Zero and Stuck at One Fault State Diagrams             |

| Figure 1.5 State Diagram of Transition Fault15                                |

| Figure 1.6(a) State Diagram of Two Cell Transitions, Fault-free16             |

| Figure 1.6(b) State Diagram of Two Cells with Coupling Fault16                |

| Figure 1.7(a) State Diagram of AND Bridging Fault17                           |

| Figure 1.7(b) State Diagram of OR Bridging Fault18                            |

| Figure 1.8. Coupled cells21                                                   |

| Figure 3.1. Proposed Fault Model for open defects                             |

| Figure 3.2(a). Fault Model for open defect between Q and M3GM4G55             |

| Figure.3.2 (b). Simulation results for No Access Faults                       |

| Figure 3.3(a) Fault Model for open defect between M6D and BLB56               |

| Figure 3.3(b). Simulation results for Undefined Read Fault at OD356           |

| Figure 3.4(a). Fault Model for open defect between M1G and M2G57              |

| Figure 3.4(b). Simulation results for Undefined Write Fault at OD2157         |

| Figure 3.5(a). Fault Model for open defect between VDD and M <sub>3</sub> S58 |

| Figure 3.5(b). Simulation results for Transition Fault                        |

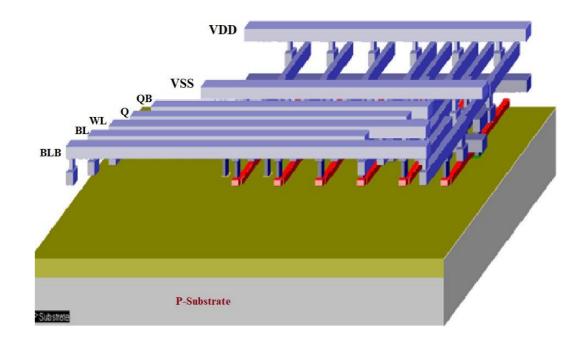

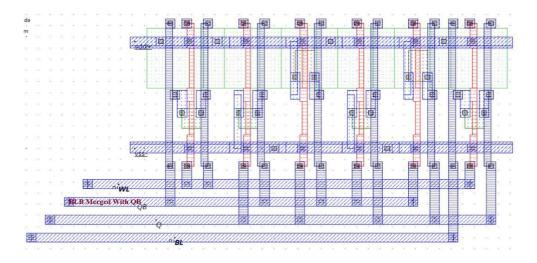

| Figure 3.6(a).3D View of Layout diagram for fault free 6T SRAM                |

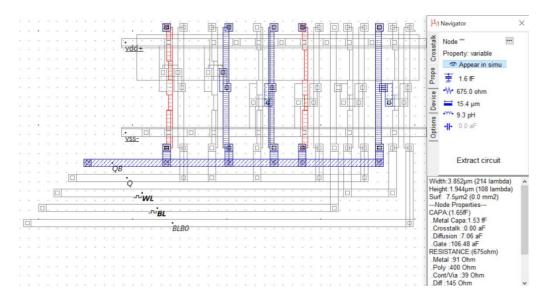

| Figure 3.6(b) Parasitic Extraction at node QB for fault free SRAM Cell60      |

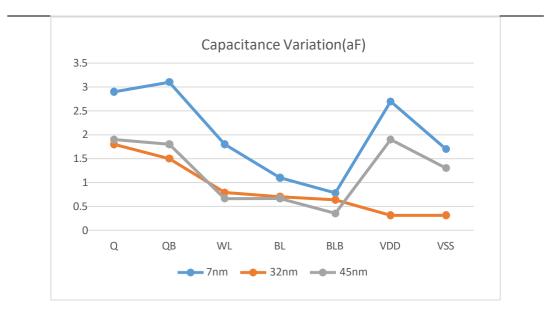

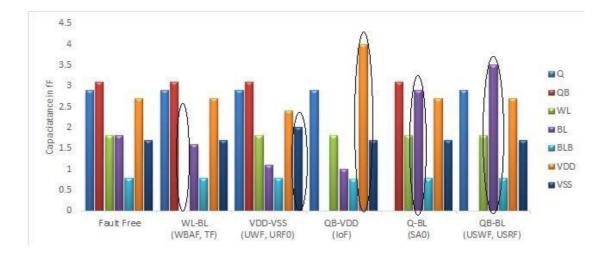

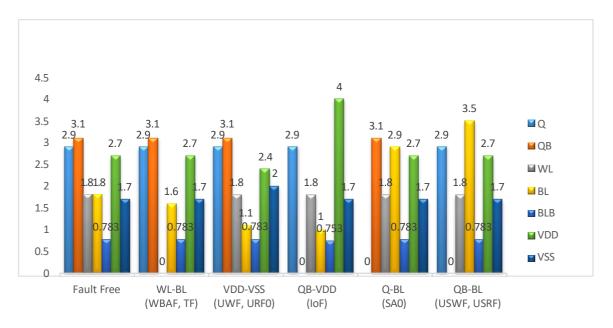

| Figure 3.7(a). Parasitic capacitance variation for different technologies for fault free SRAM Cell |

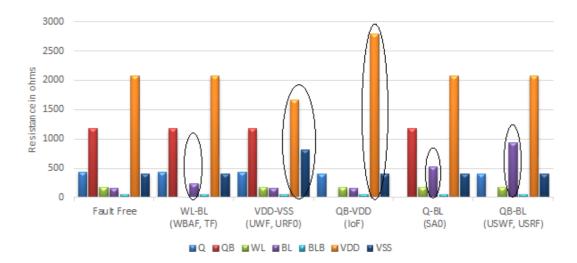

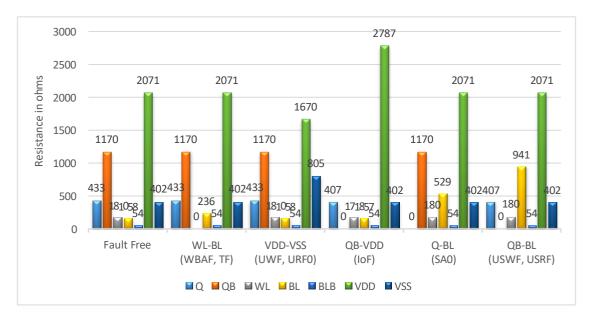

|----------------------------------------------------------------------------------------------------|

| Figure 3.7(b) Parasitic Resistance values for different technologies for fault free SRAM<br>Cell   |

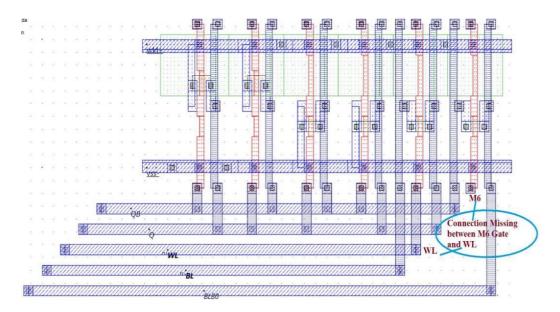

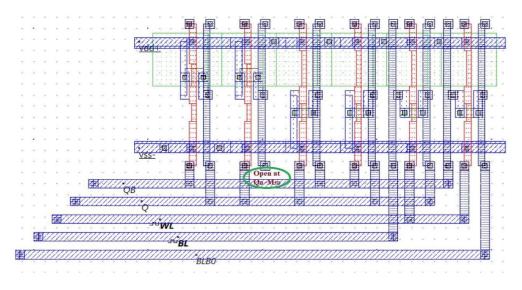

| Figure 3.8a. Layout diagram for URF fault with open defect at WL-M6G62                             |

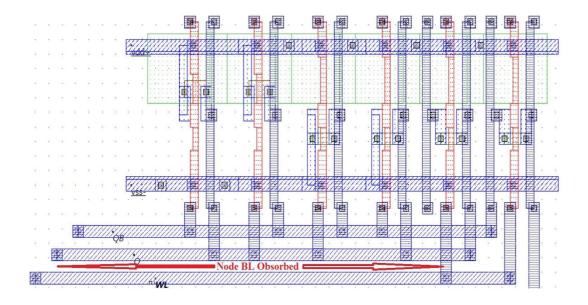

| Figure 3.8b. Layout diagram for NAF fault with open defect at BL-M5S63                             |

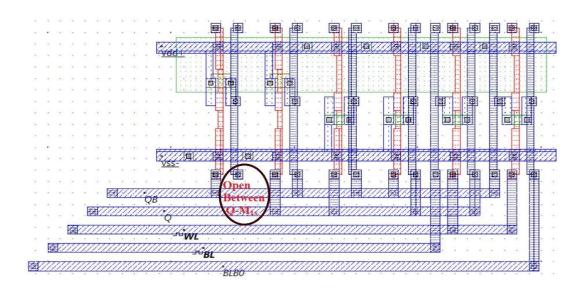

| Figure 3.8c. Layout diagram for URF& UWF fault with open defect at $Q-M_{1D}$ 63                   |

| Figure 3.8d. Layout diagram for TF fault with open defect at QB-M3D64                              |

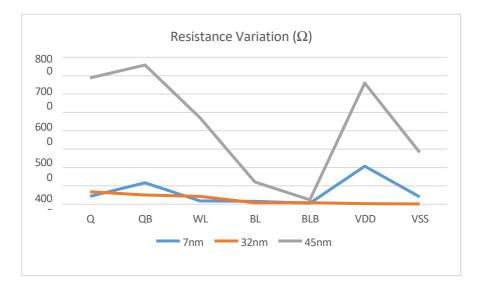

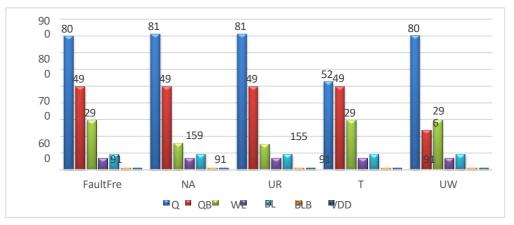

| Figure 3.9a. Variation in Resistance for different faults                                          |

| Figure 3.9b. Variation in Capacitance for different fault                                          |

| Figure 3.10a. Variation in Capacitance for different faults                                        |

| Figure 3.10b. Variation in Resistance for different faults                                         |

| Figure 3.11. Proposed Fault Model for short Defects71                                              |

| Figure 3.12a. Fault Model for short defect between Q and QB73                                      |

| Figure 3.12b. Layout diagram for USWF fault with Short defect at Q-QB73                            |

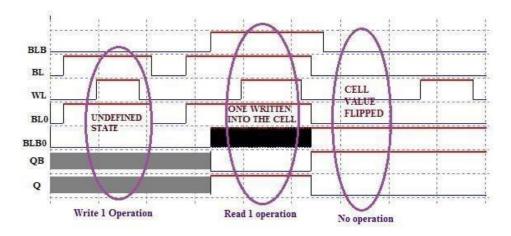

| Figure 3.12c Simulation results for Unstabilized Write Fault                                       |

| Figure 3.13a. Fault Model for short defect between QB and BLB74                                    |

| Figure 3.13b. Layout diagram for WBAF fault with Short defect at QB-BLB75                          |

| Figure 3.13c Simulation Results for Write Before Access Fault75                                    |

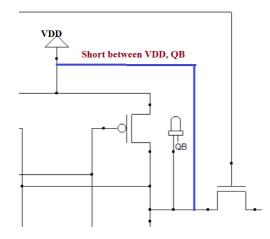

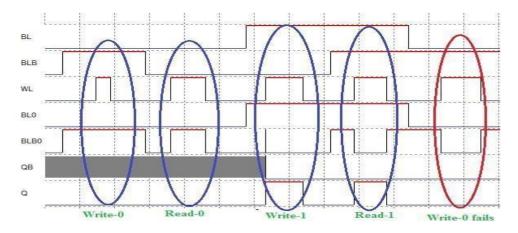

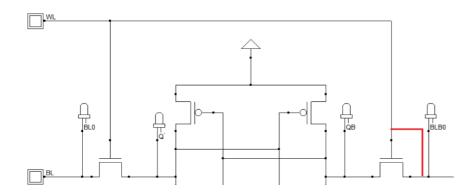

| Figure 3.14a. Fault Model for short defect between VDD and QB76                                    |

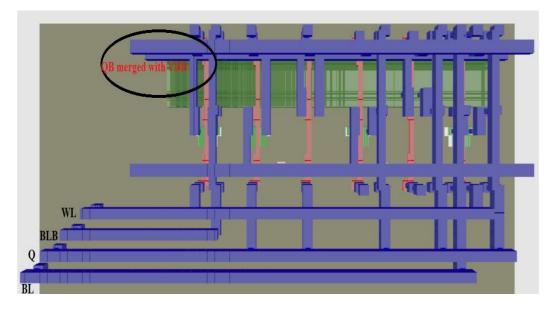

| Figure 3.14b. Layout diagram for IOF fault with Short defect at VDD-QB76                           |

| Figure 3.14c. Simulation Results for Initialization Order Fault77                                  |

| Figure 3.15a. Fault Model for short defect between WL and BLB78                                    |

| Figure 3.15b. Layout diagram for IOF fault with Short defect at VDD-QB78                           |

| Figure.3.15c. Undefined Short Fault at nodes WL-BLB                                                |

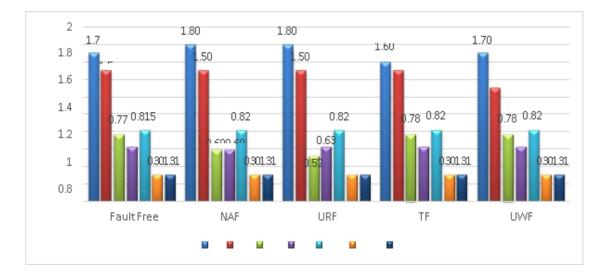

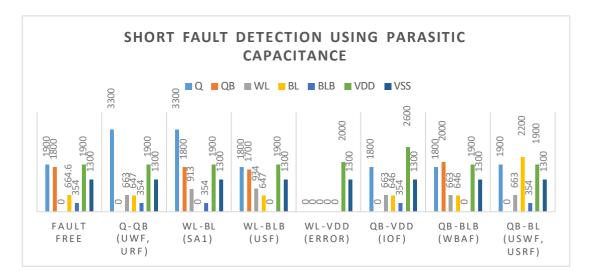

| Figure 3.16a. Variation in Capacitance for different short faults (45nm)81                   |

|----------------------------------------------------------------------------------------------|

| Figure 3.16b. Variation in Resistance for different short faults (45nm)81                    |

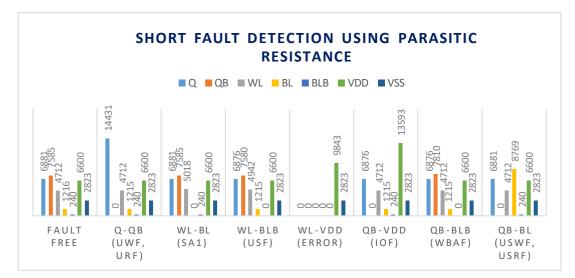

| Figure 3.17a Fault detection based on parasitic capacitance variation for short defects84    |

| Figure 3.17b Fault detection based on parasitic resistance variation for short faults84      |

| Figure 3.18a Fault detection based on parasitic capacitance variation for short faults (7nm) |

| Figure 3.18b Fault detection based on parasitic capacitance variation for short faults (7nm) |

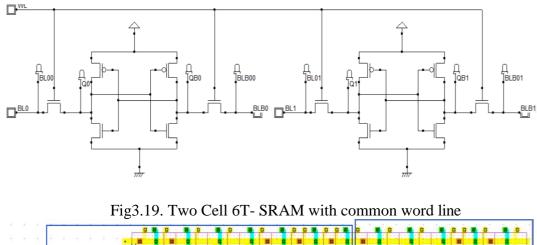

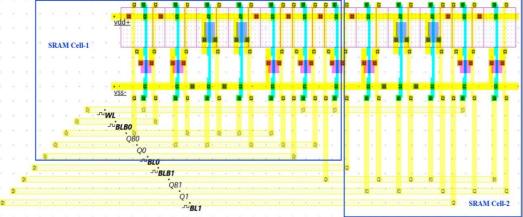

| Figure 3.19. Two Cell 6T- SRAM with common word line91                                       |

| Figure 3.20. Layout Diagram for two cell 6T SRAM Cell91                                      |

| Figure 3.21: Proposed Two Cell SRAM Fault Model for short defects92                          |

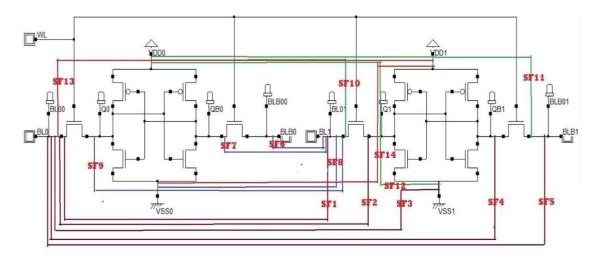

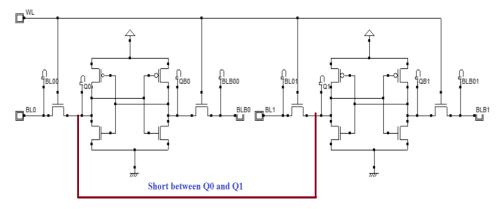

| Figure 3.22(a). Fault Model for short defect between Q0 and Q195                             |

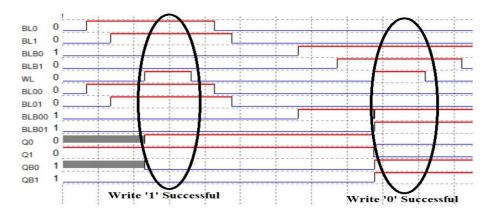

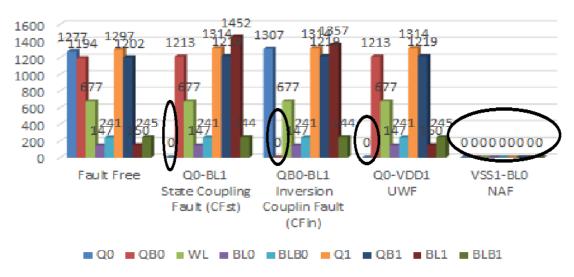

| Figure 3.22(b) Simulation results for State Coupling Faults                                  |

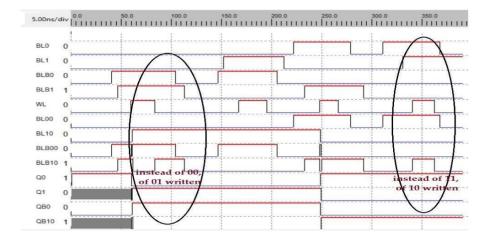

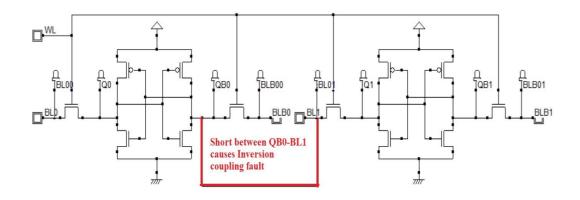

| Figure 3.23(a): QB0 and BL1 short defect Fault Model96                                       |

| Figure 3.23(b). Simulation results for inversion Coupling Faults                             |

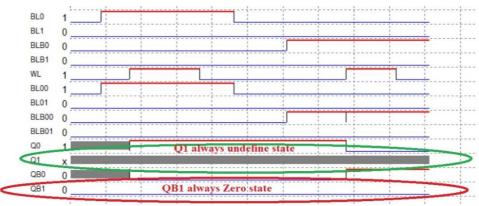

| Figure 3.24(a). Fault Model for short defect between VSS0 and Q197                           |

| Figure. 3.24(b). Simulation results for inversion Coupling Faults97                          |

| Figure 3.25(a). Fault Model for short defect between QB1 and BLB1098                         |

| Figure 3.25(b): Simulation results for short fault QB1-BLB1098                               |

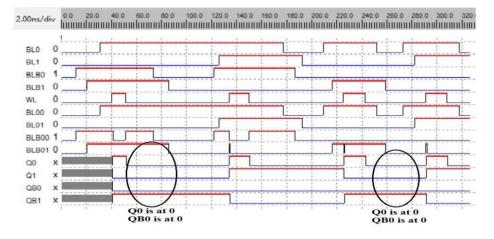

| Fig 3.26(a). Fault Model for short defect between VSS0 and Q199                              |

| Fig.3.26 (b). Simulation results for Undefined Write Fault                                   |

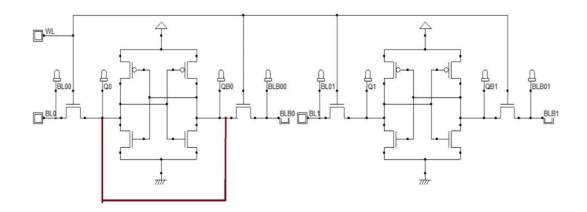

| Fig 3.27(a). Fault Model for short defect between Q0 and QB0100                              |

| Figure 3.27(b). Simulation results for USWF100                                               |

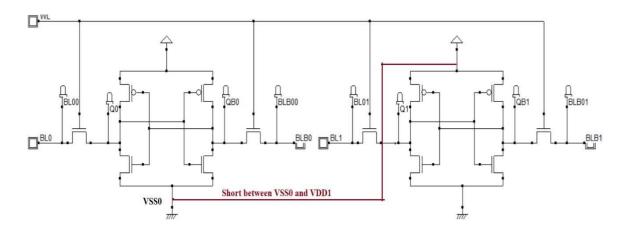

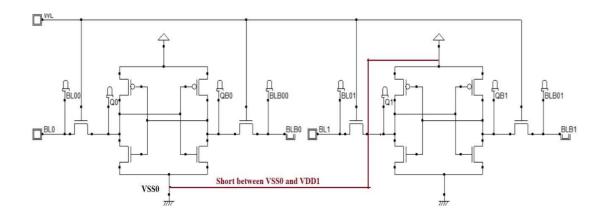

| Figure 3.28(a): Fault Model for short defect between VSS0 and VDD1101                        |

| Figure 3.28(b) Simulation results for short fault VSS0-VDD1101                               |

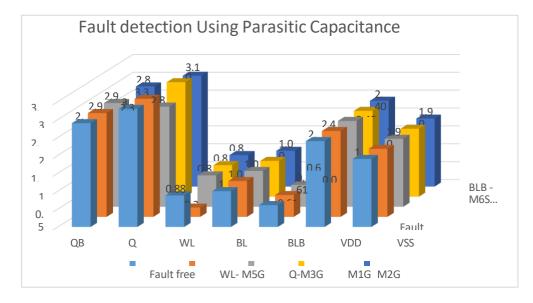

| Figure 3.29a. Variation in Capacitance for different linked faults103                        |

| Figure 3.29b. Variation in Resistance for different linked faults | 103 |

|-------------------------------------------------------------------|-----|

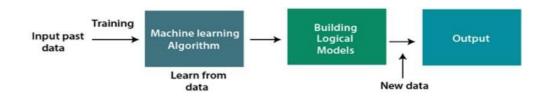

| Figure 4.1. Working model of Machine Learning algorithm           | 112 |

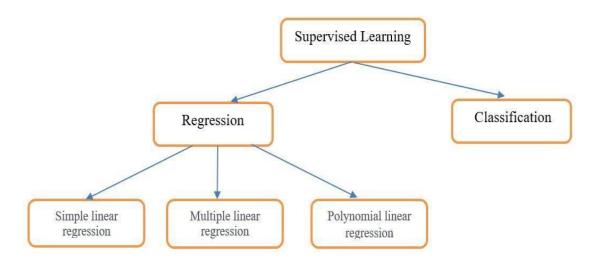

| Figure 4.2. Types of Supervised Learning                          | 113 |

# LIST OF ABBREVIATIONS

| ITRS  | International Technology Roadmap for Semiconductor |

|-------|----------------------------------------------------|

| SoC   | System on Chip                                     |

| VLSI  | Very large Scale Integration                       |

| SRAM  | Static Random Access Memory                        |

| eSRAM | embedded SRAM                                      |

| DRAM  | Dynamic Random Access Memory                       |

| MW    | Microwind                                          |

| DRC   | Design Rule Check                                  |

| DFT   | Design For Testability                             |

| NAF   | No Access Fault                                    |

| BIST  | Built In Self Test                                 |

| MBIST | Memory BIST                                        |

| VDSM  | Very Deep Sub Micron                               |

| RAM   | Random Access memory                               |

| ROM   | Read Only Memory                                   |

| SAF   | Stuck at Faults                                    |

| TF    | Transition Faults                                  |

| BF    | Bridging Faults                                    |

| ADF   | Address Decoder Faults                             |

| NPSF  | Neighborhood Pattern Sensitive Faults              |

| DRF   | Data Retention faults                              |

| FP    | Fault Primitives                                   |

| FFM   | Functional Fault Model                             |

| SOF   | Stuck Open Fault                                   |

| RDF   | Read Destructive Fault                             |

| L     |                                                    |

| DRDF  | Deceptive Read Destructive Fault        |

|-------|-----------------------------------------|

| IRF   | Incorrect Read Faul                     |

| RRF   | Random Read Fault                       |

| USF   | Undefined Short Fault                   |

| CFst  | State Coupling Fault                    |

| CFds  | Disturb Coupling Fault                  |

| CFrd  | Read Disturb Coupling Fault             |

| CFdrd | Deceptive Read Disturb Coupling Fault   |

| CFir  | Incorrect Read Disturb Coupling Fault   |

| CFrr  | Random Read Coupling Fault              |

| CFtr  | Transition Coupling Fault               |

| CFin  | Inversion Coupling Fault                |

| CUT   | Circuit Under Test                      |

| BITE  | Built in Test Equipment                 |

| ML    | Machine learning                        |

| AI    | Artificial Intelligence                 |

| CNN   | Convolutional Neural Networks           |

| DL    | Deep Learning                           |

| EDA   | Electronic Design Automation            |

| CMOS  | Complementary Metal Oxide Semiconductor |

| IFA   | Inductive Fault Analysis                |

| URF   | Undefined Read Fault                    |

| UWF   | Undefined Write Faults                  |

| SF    | State Fault                             |

| SD    | Short Defect                            |

| OD    | Open Defect                             |

| USWF  | Unstabilized Write Fault                |

| USRF  | Unstabilized Read Fault                 |

| WBAF  | Write Before Access Fault               |

| IOF   | Initialization Order Fault              |

## **CHAPTER 1**

## **INTRODUCTION**

Integrated circuits (ICs) are main components of an electronic product. In integrated circuit fabrication channel length has been rapidly decreased. These reduced channel length devices circuits face many challenges during manufacturing and during functional working. The manufacturing with reduced channel length for reduce integrated circuit size, reduce power dissipation and low cost, create various defects in SRAM's core cell. These defects create various faults in SoC's main part SRAM. So, testing is necessary parts during manufacturing of integrated circuit for improve reliability for customer satisfaction and error free operation of SRAM in very sensitive and security system.

In the last few decades, size of circuits has decreased enormously and transistors on a System on-Chip (SoC) have increased from few thousands to billions in the time frame of three decades. Exponential increase in transistor count on a silicon chip is possible due to technology scaling. Density of a SoC increased beyond billions of gates which have resulted in extensive complex very dense integrated circuits. Due to this complexity of VLSI circuits, testing is also very complex, formidable, time and power consuming task. Eventually, test time and power consumption is increasing day by day and so, now the testing cost is very high and testing is an important factor in SoC or embedded system fabrication. Efficiency, test time and power consumption are main factors of testing. Efficiency increases the customer satisfaction, low test time and low power requirement reduces the cost of product. Therefore, in highly competitive and volatile market testing is key factor for survival of manufacturer, supplier and distributer.

The semiconductor part of integrated circuit used for fabrication of memory is regularly increases in latest nanometer technologies. A memory density will approach more than 90 per cent of System on Chip (SoC) semiconductor area in the duration of next decade [1] having its own field of applications. Static Random Access Memories (SRAMs) have wide use in embedded system and processor for fast processing with very low power consumption. SRAMs are very low power consumption volatile memories. SRAM stored data in core cell is accessed with same and high speed. SRAM losses the data when power is off but with continuous power supply stored data remain saved and any time core cell can be accessed for functional operation. The term 'static' refers to the structure of six transistor storage core cell. Various resistive open defects and other variations during the manufacturing effect the operation or accuracy of SRAMs. So, memories have to be tested correctly or with zero error. SRAM testing challenges are represent fault model, high fault coverage, low power consumption and low time consumption test solution. . Different test methodologies have been evolved to identify the memory defects. Traditional test methods are zero/one, checker board, GALPAT, walking 1/0, sliding diagonal and butterfly to name a few. Among the traditional test methods, few methods are simple (zero/one, checkerboard) and few methods are complex (GALPAT, walking 1/0, sliding diagonal and butterfly). However, simple methods have poor fault coverage and the complex methods exhibit slow performance in spite of better fault coverage [2, 3 and 4]. Now in latest nanometer technologies these test solutions are not sufficient for new faults known as dynamic faults [5, 6 and 7]. These dynamic faults can be detected or sensitized by more than one read or write operations or Read Equivalent Stress (RES). Hence March algorithm with large operations element, enhanced addressing sequence and power constrained test schedule with low power test architecture will detect these faults with low power and minimal application time [8]. The complexity of the March algorithms increases as the fault coverage increases. This is the main disadvantage of the March Algorithms.

## **1.1 Semiconductor Memories Challenges**

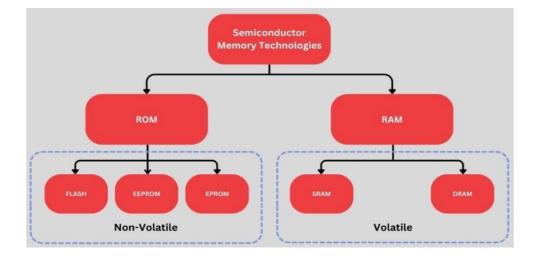

### Figure. 1.1 Types of Semiconductor Memories

Semiconductor memories uses the semiconductor devices to store the data. There are two types of semiconductor memories volatile and non-volatile memories. Volatile memory refer to the device that loose the stored information when the supply voltage is turned off, while the non-volatile memories, or Read Only Memories(ROM) able to maintain the stored information even without an external power source. Volatile memories can be classified into two types based on the technology used to store the information Ex: SRAM and DRAM

Static Random Access Memory is a volatile memory, commonly used with embedded systems. In SRAM flip flops are used to store the data, SRAM can hold the data as long as power is ON. SRAM memory provides high-speed access and consumes little power, making it excellent for quick data access and temporary storage. The main disadvantages of SRAM are its complexity and high manufacturing expenses.

Another type of volatile memory that is often utilized in embedded systems is dynamic random access memory (DRAM). Unlike SRAM, DRAM use capacitors to store the data. Therefore DRAM must be refreshed regularly to keep their charge. DRAM has a lesser data lifetime and slower access time than SRAM due to the refresh required. The fundamental disadvantage of DRAM is its slow access time and periodic refreshing. Depends on the application, memories classified into two types. i) Embedded Memories ii) External (Standalone) Memories.

### **1.1.1 Embedded Memories:**

The memory integrated with core logic is known as embedded memory. This type of memory used to perform specific functions. Embedded memory enables the logic core to perform its functions without requiring inter-chip communication. Because of high speed and wide bus capabilities of embedded memory become an important component in VLSI. The capability to integrate memory and logic on the same chip, as well as advances in manufacturing technology, have made developing embedded memory devices easier.

Memory types for embedded systems are critical components in the design of efficient and effective systems. Memory selection can have an impact on performance, cost, and power usage. Each memory type has distinct features that make it appropriate for specific applications.

Because of its quick access time, SRAM is frequently employed in embedded systems for essential data pathways and cache memory. SRAM is also frequently used in conjunction with other memory types, to achieve a maximum performance and cost. Microcontrollers, digital signal processors, and high-speed data buffers are examples of embedded memories.

Factors to Consider to choose the memory in Embedded System

1. High access Time of the embedded system, time taken to read or write the data into the memory is known as access time

2. Cost of the memory should be low, because it will affect the total cost of the embedded system

3. Data Retention: the ability to hold the data, when the power is turned off known as data retention. Non-volatile memories keep the data even after power is turned off.

4. Density and Capacity

Memory density and capacity are critical for embedded systems that need to store significant volumes of data. Flash memory is an appealing alternative for such systems because it offers high-density storage at a low cost. Because of its greater cost-per-byte, SRAM delivers lesser density.

In conclusion, while choosing the memory for Embedded System, designer should have the knowledge on how to optimize the performance, reduction of power consumption and cost

#### **1.1.2 External Memory Devices**

Memory devices located external of the logic core are referred to as external memory devices. Embedded SRAM (Static Random Access Memory) and ROM (Read Only Memory) are currently commonly used. External memory devices, on the other hand, are freestanding memory devices such as hard disks and RAM that are not included on the chip.

External memory devices are memory devices that are not built inside a chip. These are devices like as hard drives, CD/DVD ROM, RAM, and ROM that are not built into the chip. Historically, external memory refers to devices used for permanent storing of huge amounts of data, such as magnetic disks, CD ROM, and so on. The most common external memory device is the hard disk, which can often store a huge quantity of data.

#### **1.1.3 Embedded Memories Vs External (Stand Alone) Memories**

Embedded memory devices are those that are integrated with the logic core on the semiconductor, and external memory devices are those that are located outside the chip. Outside or stand-alone SRAM and ROM are used less frequently than embedded SRAM and ROM. The use of embedded memory devices reduces the number of chips and the device's space requirements. Furthermore, on-chip memory delivers faster response time and reduced power consumption than external memory devices. Creating embedded memory devices, on the other hand, demands a more complex design and manufacturing process than creating external memory devices. Combining many types of memory on the same chip would also complicate the manufacturing process.

Memory size, density, speed, stored data accuracy and efficiency in 'read', 'write' operations in present VDSM (Very Deep Sub Micron) technology completely affects the working performance of various embedded systems and System on Chips related to the 'audio', 'video', data processing applications. Semiconductor Industry Association analysis forecasts that memory will cover more than 98 % semiconductor

area of a SoC or in a system's Integrated Circuit. Basis on these reasons technology limits are used to achieve maximum density, highest speed and accuracy in operations of the system.

The testing of SRAM is one of the manufacturing steps that ensure that the SRAM, manufactured has no manufacturing defect. The testing of SRAM's core cell working is very important step because it detects faults and cause of these faults due to various defects with electrical equivalent is resistance. Therefore efficient test operation improves the quality and reliability of integrated circuit products with maximum customer satisfaction [9, 10, 11 and 12]. Physical testing will help to eliminate errors, so working performance will enhance afterward. Fault free device efficiency is maximum and improved performance. Testing detects faults generated by defects and also gets results by analysis for reason of faults and defects in core cell during manufacturing. Testing improves the performance at all stages such as designer, production, test, manufacturer and end-user [13]. Memory core cell array bit line capacitance and other lumped capacitances are high and significant during process of read and write operations on which this study will be focusing.

### **1.2 Need of Memory Testing**

Gordon Moore, predicted in 1965 that for every, one and half year it can be possible to integrate double the number of transistors. The term VLSI was used in 1980's for the ICs integrated with more than one lakh transistors. Now we are able, to integrate millions and billions of transistors in an integrated circuit. As a result, transistors are scaled down and interconnects are scaled down up to Nano meters. The scale down of transistors lead to high clock speeds [14]. There by high speed systems are designed. The result of scaling down of transistors lead to manufacturing defects in SoC [15]. Defects in the manufacturing process lead to faults in the chip. These VLSI chips used to construct an embedded system also behaves unexpectedly. A fault in the chip may lead to malfunctioning of the system. So, testing of memory cells is very much required. The expense of detecting a fault becomes ten times in the ratio when it is ignored from component stage to chip stage, chip stage to circuit board stage, circuit board stage to system stage and finally from system stage to the field of work stage. This rule is called as rule of ten.

A circuit deformity is treated as a fault, the effect of a fault is the malfunctioning of

the circuit, and a circuit malfunctioning can bring about a system failure. Two noteworthy deformity systems may be responsible to SOC configuration to breakdown. First are the manufacturing errors and the second are soft errors. During assembling, the manufacturing faults are observed. They are physical in nature that reasons the outline to neglect to work appropriately in the device, on the PCB, or in the complete logic block. Static faults are because of these manufacturing defects in the system. Stuck at faults and timing issues are come under this category. The rule of ten depicts that the cost of distinguishing a faulty device increments by a factor of size as we move through each phase of assembling, from scrap level, to board level, to system level, lastly to device assembled in the field.

### **1.3 SRAM Core Cell Operation**

VLSI memory design began when the IBM and Intel Corporation came up with their invention, semiconductor memory in 1970. Till then magnetic thin films are used for storage purpose. Semiconductor memories replaced magnetic thin films. A drastic shift has taken place within no time. Semiconductor memories can be broadly differentiated as Random-Access Memory (RAM) and Read Only Memory (ROM).

Despite of its high cost, SRAM has many features like its high speed, very easy to use. So, it is used in almost all personal computers, super computers, main frame computers, embedded systems and handheld devices. Figure 1.1 illustrates the schematic diagram of a standard SRAM circuit. SRAM circuit constructed using a flip flop placed in between power supply lines, and two switching transistors.

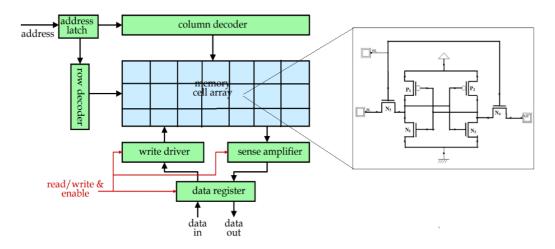

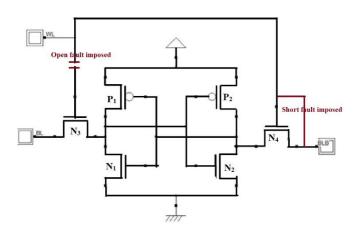

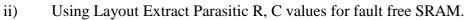

Data is written into also read from the memory by using BL and BL\_B lines as shown in figure. A write operation is carried out by supplying two inverting inputs al BL and BL\_B. If it is a logic '1' write operation. HIGH logic is supplied at BL and LOW logic is supplied at BL\_B. If it is a logic '0' write operation logic LOW is supplied at BL and logic HIGH is supplied at BL\_B. A read operation is carried by retrieving information from BL and BL\_B. There is no continuous refresh is required in the case of SRAM. A standard SRAM memory cell is shown in Figure 1.1. Two NMOS and two PMOS transistors shapes the basic flipflop to store the information and word line (WL) is used to control, two NMOS pass transistors to excite bit line (BL) and bit line complement (BL\_B) into the memory block. A compose activity is done by charging the bit line (BL) and bit line complement (BL\_B) to which the logic level needs to be stored in to the SRAM cell. Making the word line (WL) at logic high plays out the memory write task, and the new information is written in the SRAM. In the same way, read task is started by bit line (BL) and bit line complement (BL\_B) pre-charged to logic high level. The Word line (WL) put at logic high level to short NMOS pass transistors to set the value written in the cell on the bit line (BL) and bit line complement (BL\_B).

Figure 1.2: 6T SRAM memory cell

In Figure 1.2 a column single core cell of SRAM using six transistors with lines 'BL', 'BLB' and 'WL'. It consists of a bi-stable multi-vibrator unit made from two cross coupled CMOS inverters and two 'nMOS' pass transistor. These 'nMOS' pass transistors connects 'bit line' (BL) and 'bit line bar' (BLB) according to control signal 'word line' (WL) instruction. The level if bit line and bit lines bar is changes according to operation performing. During 'read' operation voltage difference in bit line and bit line bar gives the information about saved data.

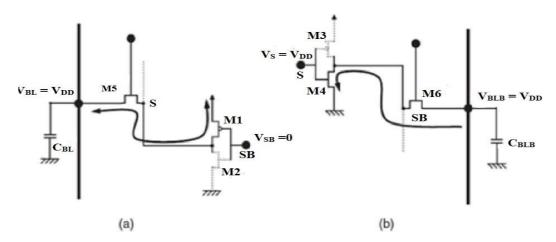

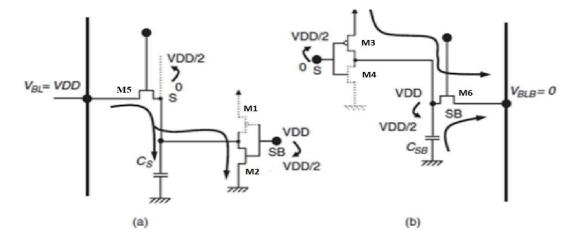

To furnish the details for the read operation of SRAM cell, let consider a memory cell storing a logic value '1" with logic node S at supply voltage  $V_{DD}$  as well as logic node SB at 0V. In read operation, the BL and BLB pins are pre-charged with certain supply voltage value  $V_{DD}$ . If the word line signal WL is connected to  $V_{DD}$ , then access transistors  $M_5$  and  $M_6$  are turned into ON state. Then there S node and bit line BL are in at the same potential i.e.  $V_{DD}$ , and there is no current flow takes place. There is a current flow from BLB (precharged to  $V_{DD}$ ) through transistor  $M_6$  and transistor  $M_4$  by evoking the discharge of BLB. The charging and discharging path of the SRAM circuit during a read operation given in the Figure 1.3(a), where the bit line capacitor  $C_{BL}$  and bit line\_bar capacitor  $C_{BLB}$  are equivalent capacitances of BL and BLB pins

Figure 1.3(a): Read Operation of SRAM Cell

Figure 1.3(b): Write Operation of SRAM Cell

In the Figure 1.3(b), the capacitors connected at output nodes S and SB of two inverters CS as well as CSB were the parasitic capacitances. The regenerative feedback that causes the Flip-Flop to switch when either VS or VSB reaches to the value VDD/2. If this condition was satisfied, the positive feedback in this SRAM immediately takes place. This positive feedback establish a path to charge and discharge VDD in capacitors  $C_S$  and  $C_{SB}$ .

It is important to test the fabricated IC thoroughly. ITRS demonstrates that as size of memory increases, yield decreases which points out the significance of memory testing. Moreover, memory testing must have diagnostic capability to identify the defective locations. The circuit design and the manufacturing process can be improved significantly by unravelling the defective location. The results of fault diagnosis can further be used to examine the defect and the mechanism of failure. Hence memory testing plays a crucial role in semiconductor manufacturing process as it analyses and isolates many of the defects in order to obtain an efficient yield.

The main applications of the eSRAM is i) Automotive, mobile devices, consumer devices, media processors, and analog and mixed signal designs. ii) used to store firmware or security code iii) media applications iv) space craft applications

### **1.4 Faults and Fault Models**

**1.4.1 Assertion Faults:** Wang et al. presented these assertion faults to depict the faults in embedded processors [20]. Test generation and validation of embedded array blocks are represented with the faults occurring in those circuits. Test generation from the abnormal state declaration determination gives a perfect answer for the issue of both test and verification. On the off chance that tests can be derived specifically from assertions, DFT on the gate level test point of view is never again required and consequently, dispose of the diagnosis needs connected with it. This additionally stays away from the inconveniences of experiencing the ATPG development tools. Hence, rather than making complex gate level perspectives for microprocessor arrays with the goal that they can be tested through ATPG tools, the new stream uses the high-level assertion.

1.4.2 Behavioural Faults: At the point where a computer programming language is

used to depict an electronic system, which is for the most part described by any programming language, just like C or java or any Hardware Description Language (HDL) that takes after a programming language, for example, VHDL or Verilog HDL. At the behavioural level, refered as practical or functional level state, the descriptions depicted are not the representing the electrical nodes and their interconnections but rather they simply define the functional behaviour of the system. Behavioural faults refer the inaccurate compilation of the statements and builds utilized as a part of the description. Cases of behavioural faults may come under declaration faults, instruction command faults and branch faults. In behavioural level of description, programming test strategies, statement scope and branch scope and toggle scope, are additionally utilized in spite of the fact that these don't fit in with a particular fault model.

**1.4.3 Branch Faults:** Branch faults are displayed in the behavioural level where a system is depicted with a programming language or hardware description language. Branch faults may occur because of a circuit branching to an unintended branch [21-22].

**1.4.4 Bridging Faults:** This type of faults mainly because of some of the circuit wires may be short circuited. In bridging fault with respect to memories, one cell alters another cell, there is no question of one cell dominating other. Generally demonstrated a bridging fault is because of the short between two or more wires in a circuit. The logic estimation of the shorted net might be displayed as OR bridging fault or AND bridging fault or Indeterminate. Combinational bridging faults and the scope of occurrence is generally more when appeared along with stuck at faults. That isn't generally appeared in feedback bridging faults which deliver stored values in the combinational logic [23-24]. These bridging faults are generally because of defects in the circuit construction.

**1.4.5 Cross point Faults:** Cross point faults generally displayed in Programmable Logic Devices (PLD). While designing a PLD, general input wires and output wires are crossing the product signals. Intersection flag lines either frame shorts of connections or stay open at intersection nodes, contingent upon the logic which is implemented. These cross-point discrepancies can be broad classified in two ways.

First is the missing cross point implying a disconnected association at an intersection where an association was expected. Second is the additional cross point implies a defective association at an intersection where no association was expected [25-26]. In view of their effect in the behavioural capacity of the PLD, the cross-point faults are additionally named shrinkage faults, development faults, appearance faults and disappearance faults.

**1.4.6 Defect Oriented Faults:** Unintended contrast between the fabricated system and the proposed structure of the system is called a defect. [3] in their research work mentioned about this type of defect-oriented flaws. Issues in the physical manufactured chip that for the most part happen during construction are called as defects. Physical deformities may create the electrical or logic level faults. Faults because of these physical deformities are called as defect oriented faults. Cases of physical deformities may be some open circuited wires, short circuits, bridging between adjacent wires, inappropriate semiconductor doping, and wrong components. Bridging faults, stuck-open faults are some examples of defect oriented faults.

**1.4.7 Delay Faults:** Delay faults in a system are because of combinational delay. If the combinational delay exceeded by the clock period, the system functionality may be changed. Different delay faults noted are gate delay faults, transition faults, segment delay faults, line delay faults and path delay faults[9].

**1.4.8. Pattern Sensitive Faults:** Since memory is firmly coupled neighboring cells influence the conduct of a cell. The example that is put away in the influencing cells modifies the conduct of influenced cell. This is called Pattern Sensitive Fault[13]. There are two kinds of pattern sensitive faults. One is Active PSF and the other Passive PSF. Dynamic PSF is the point at which an adjustment in any four contiguous cells supplements the incentive in the influenced cell. Passive fault is the point at which a cell is encompassed by four neighbouring cells and all the four cells at logic 0 level then the influenced cell stuck at logic zero level. Similarly, when a cell at logic 1 encompassed by four cells at logic 1 then the influenced cell stuck at logic 1. This kind of fault is called passive PSF.

1.4.9 Physical Faults: Physical faults in the circuits are because of the defects in

physical implementation of the circuits[31]. Cases of physical deficiencies are open circuited connections, short circuits between transmitters conveying detached flags, shorted or open transistors, and so forth. These deficiencies may be sometimes called as defect oriented faults.

**1.4.10 PLA Faults:** Faults observed in Programmable Logic Arrays (PLAs) are called as PLA faults. In PLA design, primary input and output lines are crossing the OR input lines. Convergence input lines and product lines may be outline required sorts of associations or may be open, dependent upon the executed digital logic. These Cross point discrepancies are classified in two ways. First one is the open circuited cross point where a cross point short is expected. Second one is the extra cross point suggests a faulty relationship at a convergence where no affiliation was expected. In perspective of their impact of the cross- point fault on the system functionality limit of the PLA, these faults are moreover named PLA faults.

**1.4.11 Redundant Fault:** A fault which is not changing the functionality of the circuit is known a redundant fault[120]. In a redundant fault the input and output relationship is not changing. So, it is difficult to identify the redundant fault by any test method. These types of faults are expelled by the circuits where the outputs are affected by fault inside. Multiple faults in a circuit may compensate the faulty behaviour of the outputs. Be that as it may, recognizable proof and expulsion of excess issues is a more unpredictable process. These faults can be observed in both combinational and sequential circuits. Generally, the issues in sequential circuits which any test related to sequential circuit testing, not able to detect the faulty behaviour of the circuit is called a redundant fault.

**1.4.12 Memory Faults:** Faults observed in memories are called as memory faults. Cell stuck at faults, coupling faults, address decoding faults are examples of memory faults[116]. Memories available in various structures and sizes. It is difficult to arrange fault model for each kind. For the most part by the basic structure of reading and writing of memory arrays, a memory can be all around depicted. Faults memories can be displayed, and algorithms to find faults in memories can be made by considering these read and write cycles. Memory arrays comprises of Analog and digital parts. Basic fault testing of memories may impractical. As a result of the

substantial number of cells and basic components. So functional testing model is conceivable as for memory testing.

Memories accessible in numerous structures and sizes. It is hard to configuration fault model for each type. Generally, by the common structure of reading and writing in to memory locations, a memory can be well described. Faults in memories can be modelled, and algorithms to discover faults in memories can be created by considering these read and write cycles. Fault can be characterized as the abstracted functional level of a defect in a digital system. Memory blocks may have analog circuit blocks and digital circuit blocks. Structural fault testing of memories may not possible as memories have large number of storage cells and other logic components. So functional testing model is possible with respect to memory testing. Functional modelling of memory faults consists of Stuck at faults, Transition faults, Bridging faults, Coupling faults, Data retention faults, Address decoding faults and Intermittent faults [27].

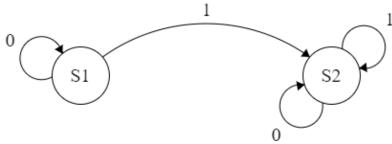

**1.4.13 Stuck at faults (SAF)**: There are two types of stuck-at- faults. Stuck-at-zero (SA- 0) and Stuck-at-one (SA-1) fault. A SA-0 fault occurs when a cell is 'stuck at logic-0' and does not change in response to any logical input pattern presented. Similarly, when a cell is SA-1 and does not change for any logical input pattern presented, that form of problem is referred to as a stuck at one fault [28].

Figure 1.4(a) State Diagram of a Fault-free Circuit

Source: embedded.com

Figure 1.4(b) Stuck at Zero and Stuck at One Fault State Diagrams

Source: embedded.com

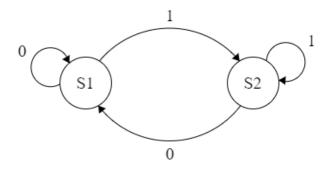

**1.4.14 Transition fault (TF):** A transition error occurs when a signal or line fails to toggle from 'logic 1' to 'logic 0' or from 'logic 0' to 'logic '1' [29]. In the case of memories, a cell fails to toggle. A rising transition error occurs when a cell fails to flip from logic '0' to logic '1'. A falling transition fault occurs when a cell fails to flip from logic '1' to logic '0'.

Source: embedded.com

Figure 1.5 State Diagram of Transition Fault

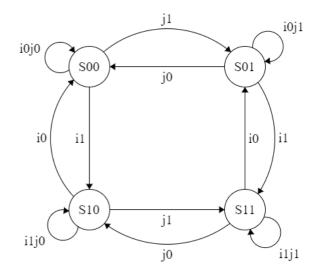

**1.4.15 Coupling Faults (CF):** When a cell is purposely transformed, the other cell changes, which is not supposed to alter. This is referred to as a coupling fault[22]. In general, when a cell is written with a logic value ranging from 0 to 1 or 1 to 0, the next cell is affected and its logic value changes. Different sorts of coupling defects have been identified in memories. A cell can only store a logic value if it contains a specific logic value, either 0 or 1. State coupling faults are the name given to this sort of fault. When a cell switches its state, the adjacent cell's value changes, which is known as an idempotent coupling defect.

Figure 1.6(a) State Diagram of Two Cell Transitions, Fault-free

Source: embedded.com

Figure 1.6(b) State Diagram of Two Cells with Coupling Fault

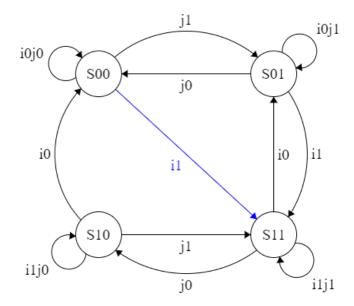

**1.4.16 Bridging Faults (BF):** These faults occur because of a short between some memory cells[36-45]. In bridging fault one cell alters another cell, there is no question of one cell dominating other. If there are two cells, namely cell\_A and cell\_B are affected in bridging fault. Either cell\_A may influence cell\_B or cell\_B may

influence cell\_A. Bridging faults are of two types. AND bridging fault and OR bridging fault. And bridging fault involved in two cells, namely cell\_A and cell\_B, when one cell is at logic zero then it pulls other cell also to logic zero.

When cell\_A at logic 0 and cell\_B supposed to be a logic 1 but cell\_A pulls cell\_B also at logic 0. In the same way cell\_B when it is at logic zero it doesn't allow cell\_A to go logic 1. This type of bridging fault is called AND bridging fault. OR bridging fault is when any one of the two cells at logic 1 then it pulls other cell also to logic 1. This type of fault is called OR bridging fault. When cell\_A is at logic 1 and cell\_B if supposed to be at logic 0, cell\_A pulls cell\_B also logic 1 level. In the same way when cell\_B is at logic 1 and cell\_A if supposed to be at logic 0, then cell\_B pulls, cell\_A to logic 1 level. This type of fault is called as OR bridging fault.

Figure 1.7(a) State Diagram of AND Bridging Fault

Source: embedded.com

Source: embedded.com

Figure 1.7(b) State Diagram of OR Bridging Fault

**1.4.17** Address Decoder Faults: Address decoder failures are caused by incorrect address decoding in the address decoder. In general, four types of address decoder defects have been reported in memory[86]. No address can ever be used to access a cell array. The second condition occurs when no memory array is accessed with an address. Third, a memory array can have numerous addresses. Finally, numerous addresses are attempting to access the same cell array.

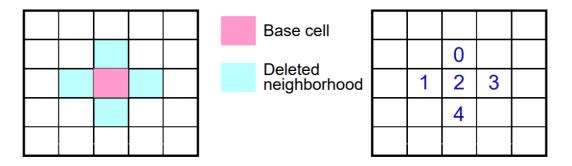

**1.4.18 Neighborhood Pattern Sensitive Faults (NPSF):** NPSF faults are due to influence of neighbouring cells of a call in an array. Because memory is closely coupled neighbouring cells affect the behaviour of a cell[100]. The pattern that is stored in the affecting cells alters the behaviour of affected cell. This is called Neighbouring Pattern Sensitive Fault. NPSF faults can be broadly classified in to two ways. One is Active NPSF and the other is Passive NPSF. Active NPSF is when a change in the any four adjacent cells complements the value in the affected cell. Passive fault is when a cell is surrounded by four neighbouring cells and all the four cells at logic 0 level then the affected cell stuck at logic 2 reo level. In the same way when a cell at logic 1 surrounded by four cells at logic 1 then the affected cell stuck at logic 1 then the affected cell stuck at logic 1. This type of fault is called passive NPSF.

**1.4.19 Data Retention faults:** When a stored logic value in a memory array is not updated during a specific time interval, the cell that is unable to preserve its logic value is referred to as a Data retention error[115]. After a time lapse, the cell is unable to recover its previously stored cell content. These types of defects are common in SRAMs.

#### **1.5 Concept of Fault Primitives**

The fault primitive space is defined by Hamdioui [30]. An operation sequence that can be done in a memory cell. The FP is a precise, concise mathematical description that explains the operation done in the memory cell, the cell contents after sensitization, and the sense amplifier response. Using the concept of fault primitives, one may deduce all forms of faulty behavior, and it offers a framework for all errors in the memory cell. The two basic components of a fault model are: 1) A list of memory operations completed 2) A collection of corresponding variations in observed behavior from expected behavior. An operation sequence is a collection of memory cell actions. A sensitizing operation sequence (S) is one that produces a discrepancy between expected and observed behavior. Faulty behavior (F) is observable behavior that differs from the predicted one. FP that include a single cell is indicated as  $\langle S/F/R \rangle$ >, where 'S' indicates the sequence of sensitization operations carried out in the memory cell, 'F' indicates the response of faulty cell, and If the sensitization operation performed on the cell is a read operation, 'R' denotes the logical value that appears at the sense amplifier's output. '-' represents any operation. ' $R \in \{0,1,2,-\}$ '. Here, '?' represents random or undefined logical value. A '-' in R represents that the output is not applicable in that case and the sensitizing operation does not contain a read operation.

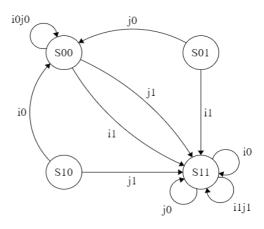

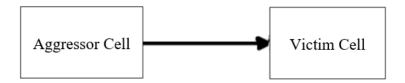

Two cell functional fault models consist of fault primitives sensitized by performing utmost one operation while considering the effects of two cells have on each other. ' $\langle$ Sa,Sv/F/R $\rangle$  or  $\langle$ Sa,Sv/F/R $\rangle$ ' the subscripts a,v indicates the fault primitive of two cells. The sensitization operation or state of the aggressor cell is denoted by Sa, while the sensitization operation or state of the victim cell is denoted by Sv. The set of Si is given as 'Si  $\mathcal{E}$  {0, 1, X, w0, w1, w $\uparrow$ , w $\downarrow$ , r0, r1, 0w1, 1w0}', where I  $\in$  a, v and X represents the don't care value X $\in$ {0,1}.

## 1.5.1 Single cell static FFMs

Single cell errors arises in the same cell,. This section summarizes many forms of single cell fault models and fault notations. Table1.1 summarizes the behavior of various forms of single cell static faults, as well as their acronyms and FPs.

| Type of fault | FPM                                       | FPs                                                |

|---------------|-------------------------------------------|----------------------------------------------------|

|               | Stuck-at-Fault (SAF)                      | $< \Box/1/->, < \Box/0/->$                         |

|               | Stuck-Open-Fault(SOF)                     | $\{<0w1/0/->, <1w0/1/->, \}$                       |

|               | Transition Fault(TF)                      | < 0w1/0/->, < 1w0/1/->                             |

|               | Read-Destructive-                         | $<$ r0/ $\uparrow$ /1 >, $<$ r1/ $\downarrow$ /0 > |

|               | Fault (RDF)                               |                                                    |

| Single        | Deceptive-Read-<br>Destructive-Fault (DRD | $<$ r0/ $\uparrow$ /0 >, $<$ r1/ $\downarrow$ /1 > |

| cell static   | F)                                        |                                                    |

| faults        | Incorrect-Read-Fault<br>(IRF)             | < r0/0/1 >, < r1/1/0 >                             |

|               | Random-Read-Fault (RR<br>F)               | < r0/0/? >, < r1/1/? >                             |

|               | Undefined-State-                          | $< w_0/?/->, < w_1/?/->,$                          |

|               | Fault (USF)                               | <r0 ?="">, <r1 ?=""></r1></r0>                     |

Table1.1Single cell static Functional Fault Models

# **1.5.2 Double cell static FFMs**

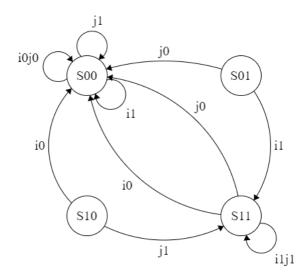

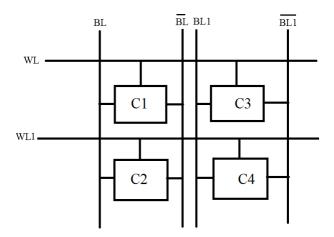

In a coupled fault, two or more cells are coupled with each other. When two cells are involved, it is known as double cell fault. A two-cell coupling fault manifests itself if the contents of the victim cell is changed by a transition in the aggressor cell. LetC2, C3 and C4 be the neighboring cells of cell C1 (Figure 1.8).

A coupling fault occurs mainly due to shorts in interconnections between adjacent cells. Shorts between neighboring cells can occur row wise, column wise, or diagonal. For example, between cells C1 and C3 in Figure 1.8.

Fig 1.8. Coupled cells

• Static double cell errors are those that involve two cell actions. This section describes the classification of static coupled FFMs. Table 1.2 shows the behavior of numerous forms of double cell static faults, as well as their acronyms and FPs.

Table 1.2 Double cell static FFM

| FFM                                                   | FPs                                                                                                                           |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| State-Coupling-Fault<br>(CFst)                        | <0;0/1/->,<1;0/1/->,<0;1/0/->,<1;1/0/->                                                                                       |

|                                                       | $< 0w1;0/\uparrow/->,< 1w0;0/\uparrow/->,< 0w0;0/\uparrow/->,< 1w1;0/\uparrow/->$                                             |

| Disturb-Coupling-                                     | $<0w1;1/{\downarrow}/->,<1w0;1/{\downarrow}/->,<0w0;1/{\downarrow}/->,<1w1;1/{\downarrow}/->,$                                |

| Fault (CFds)                                          | $<$ r0;0/ $\uparrow$ /->, $<$ r1;0/ $\uparrow$ /->, $<$ r0;1/ $\downarrow$ /->, $<$ r1;1/ $\downarrow$ /->                    |

| Read-Disturb-<br>Coupling-Fault(CFrd)                 | $<\!\!0;\!r0/\!\uparrow/1\!\!>,<\!\!1;\!r0/\!\uparrow/1\!\!>,<\!\!0;\!r1/\!\downarrow/0\!\!>,<\!\!1;\!r1/\!\downarrow/0\!\!>$ |

| Deceptive-Read-<br>Disturb-Coupling-<br>Fault (CFdrd) | <0;r0/^/0>, <1;r0/^/0>, <0;r1/↓/1>,<1;r1/↓/1>                                                                                 |

| Incorrect-Read-<br>Disturb-Coupling-<br>Fault (CFir)  | <0;r0/0/1>, <1;r0/0/1>, <0;r1/1/0>,<1;r1/1/0>                                                                                 |

| Random-Read-<br>Coupling-Fault<br>(CFrr)              | <0;r0/0/?>,<1;r0/0/?>,<0;r1/1/?>,<1;r1/1/?>                                                                                   |

| Transition-Coupling-<br>Fault(CFtr)                   | <0;0w1/0/->, <1;0w1/0/->,<0;1w0/1/->, <1;1w0/1/->                                                                             |

## **1.6 Motivation:**

From the literature review, the following points are noticed for testing of embedded memory. There are numerous testing methodologies available, but there are just a few strategies known for memory testing. All of these memory testing approaches are based on memory read and write activities. March memory test designs are popular memory test approaches. There are numerous March-based algorithms for testing SRAMs. Memory testing is becoming more difficult as technology continues to diminish. As technology advances, more and more faults develop in memories. Traditional memory test procedures may not meet today's low power test circuit's needs. Low power memory test approaches are required to overcome all of these disturbances. Memory is tested using built-in Self-Test procedures. March algorithms are commonly used to test memory, such as Static Random-Access Memory (SRAM). There are various March test strategies accessible to test memories. Each test approach has a distinct feature for testing various faults detected in memories at various levels of testing. March algorithms used a low power strategy to generate low power consumption Memory Built in Test structures.

Design engineers treat the Circuit Under Test (CUT) as a black box, as they see external input signals that can be controlled and the output signals that can be observed. As the complexity of the digital circuit increasing the testability of the circuit decreases. The design of a good Design for Testability (DFT) circuit is difficult as the circuit complexity increases. When a circuit became more controllable and more observable then it is more testable circuit. Test methods to enhance controllability and observability leading to enhance Testability of the digital circuit. By adding extra test hardware Controllability and observability can be improved. This extra hardware results extra control pins and output lines. More control pins and output lines results circuit complexity, high power consumption, high delay, less reliability and high cost. Effective test structures are needed to overcome all these trade-offs.

Built in Self-Test (BIST) is a hardware logic constructed along with the circuit to test itself. BIST is for generating test data to test Circuit under Test and observe the response and compares the output with expected results. BIST circuitry designed for testing memories is called Memory Built in Self-Test (MBIST). Since almost all the

systems uses memories, system behaviour completely depends on memories. It is mandatory to construct effective test methods for memories. Fault analysis and fault location are of prime significance in semiconductor Random-Access Memories (RAM) regarding the expanding memory utilization and commanding segment of installed memories in recent embedded processors. Manufacturing faults ought to be recognized, analysed and situated for additionally repair keeping in mind the end goal to enhance the item quality, dependability and yield.

BIST is the ability of a circuit or a chip or a board or system to test itself [16]. Built in Self-Test speaks to a collection of the ideas of Built in Test and Self-Test. The more equivalent term Built in Test Equipment (BITE) alludes to the equipment and additionally programming consolidated into a unit to give design for testability or BIST capacity. Now a day's low power advanced circuit configuration has risen as a key subject in hardware industry. Till now the VLSI industry builds more focus on chip area, product cost and performance. Now the VLSI architects focusing more on portable digital circuits.

In conclusion, the existing test methods are not considering all aspects of SARM parameters. This has motivated in developing a test method for single cell faults based on parasitic extraction method considering all aspects of SRAM parameters. The proposed parasitic extraction test method uses defect induced layout, which is extracted from known electrical model.

Due to complexity in representing coupling faults, research was done at low rate compared to single cell faults. This problem directed the researcher to extend towards analysis of coupling faults too. In this process, a fault model dictionary was developed by the researcher for detecting existing, detectable and undetectable single cell and multi cell SRAM faults, in 45nm, 32nm and 7nm technologies.

## 1.7 Objectives and Scope of the Work

It is necessary to thoroughly evaluate memories using effective algorithms and realistic defect models. By developing a fault model dictionary at three technology levels and employing the parasitic extraction method, the investigation tackles the issue of test time complexity in the development identification of a variety of faults in the new technological era while taking parasitic memory effects into consideration.

With the continuous downscaling of silicon-based technologies, it is felt that there is a growing need for mechanisms to detect the manufacturing faults. Bridging/short and open faults are very common manufacturing faults. The researcher analyzed the open and short faults for single cell SRAM. The proposed parasitic extraction method has been implemented using MicroWind tool for three technologies 45nm, 32nm and 7nm technology.

With technological advancement, AI and Machine Learning are playing a very key role in every industry. Machine learning (ML) has benefited the VLSI industry by optimizing the use of EDA tools, resulting in reduced design times and manufacturing costs. Machine learning in VLSI design helps EDA tools find the best solution for use case scenarios and minimizes production loss by recognizing chip faults. Therefore the researcher used the machine learning algorithms to predict the faults.

With the continuous downscaling of silicon-based technologies, it is felt that there is a growing need for mechanisms to detect the faults. In this scenario, an outcome based analysis carried out using parasitic extraction method will be necessary to guarantee an accurate testing method. The proposed methods are envisaging the future needs.

## 1.7.1 Objectives of the proposed work

- Analyze faults due to open defects in Embedded SRAM cell for submicron to deep submicron technologies

- Design a parasitic R and C extraction method for short/bridge defects in SRAM cell using nano meter technologies.

- Develop a fault detection method for open and Short defects in multi cell SRAM architecture

- Design Novel Fault detection and test methods using Machine Learning Algorithms in embedded SRAM architecture

## **1.7.2** Tools Used for the proposed work

- 1. Microwind Tool (3.9 licensed Version)

- 2. Multiple Linear Regression

- 3. Decision Tree algorithm

## **1.7.3 Organization of the thesis**

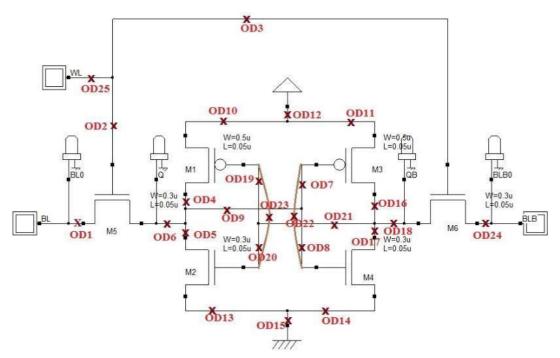

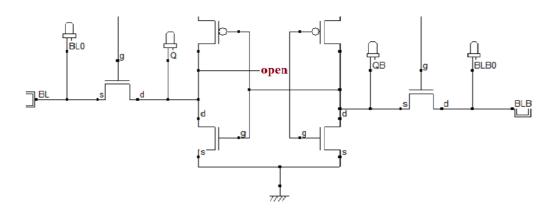

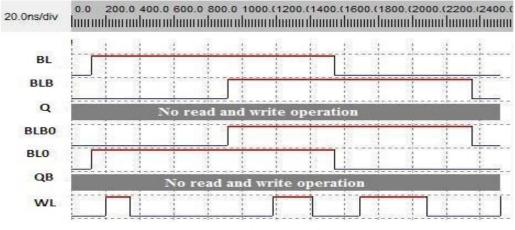

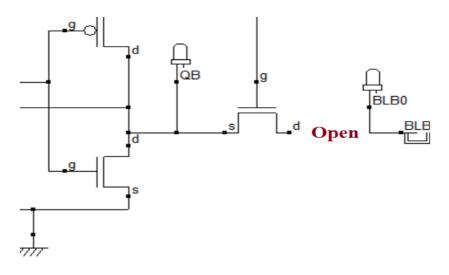

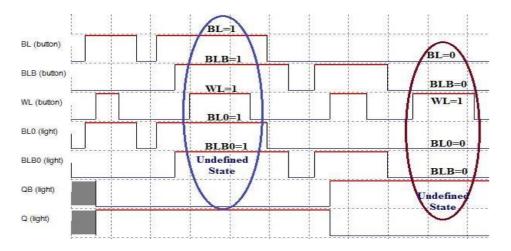

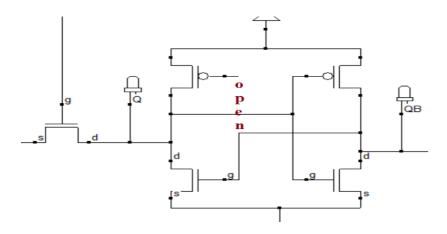

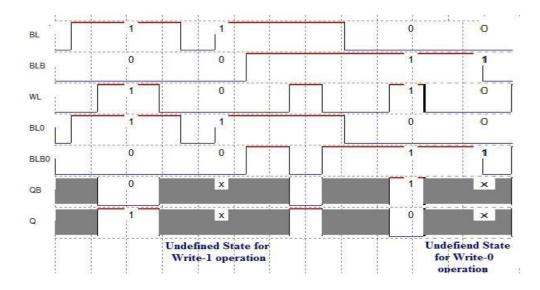

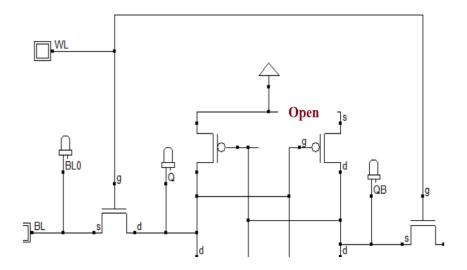

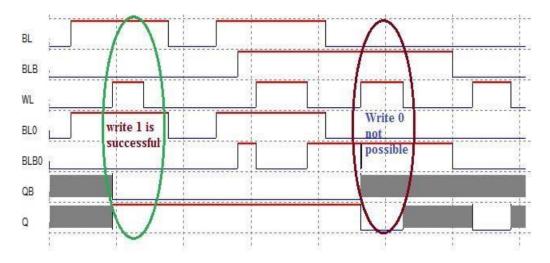

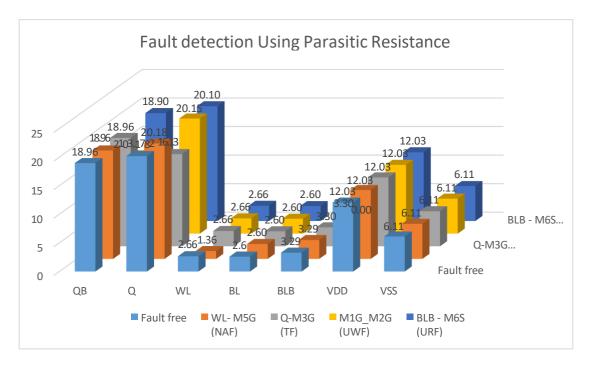

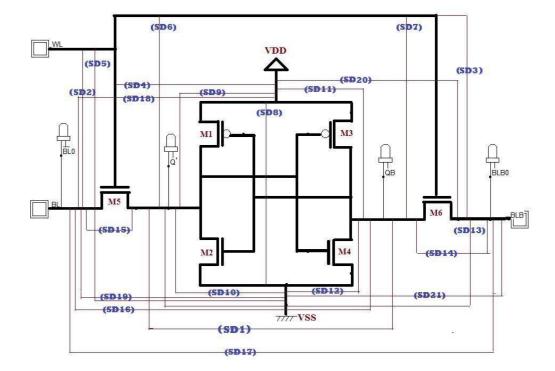

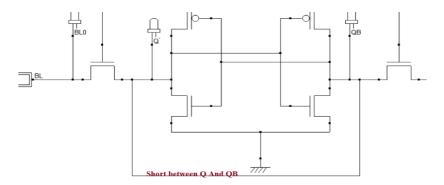

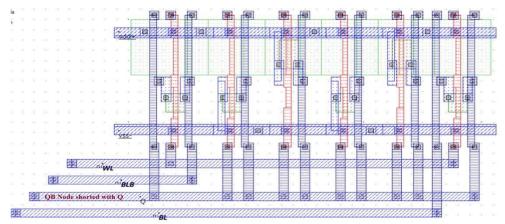

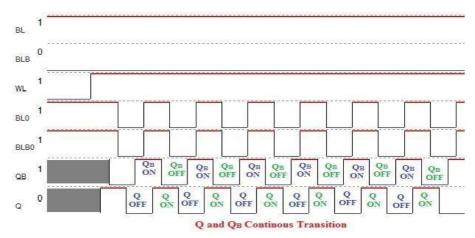

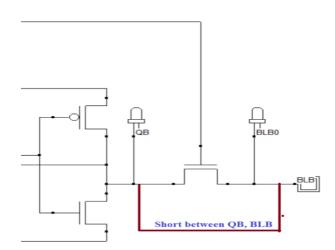

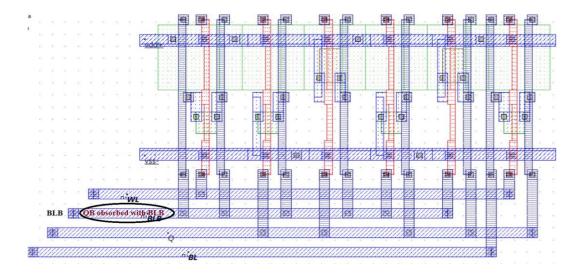

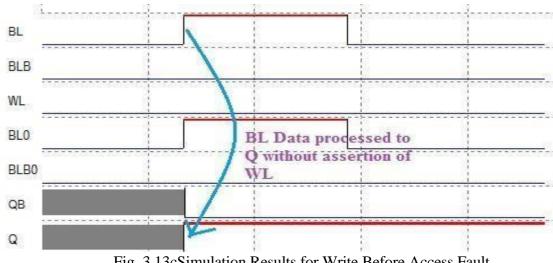

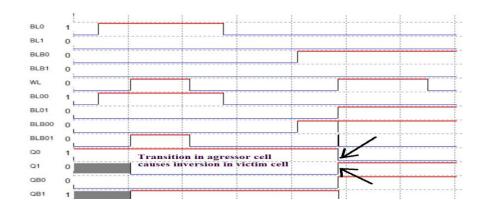

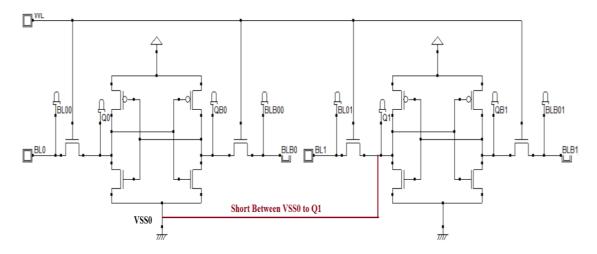

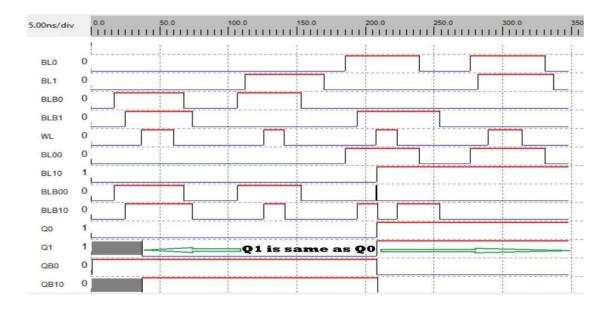

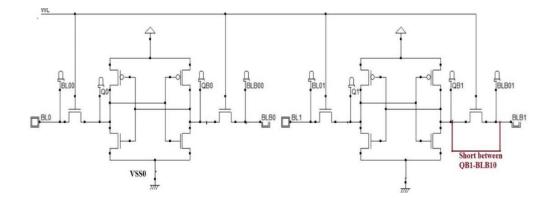

The significance of embedded SRAM testing when they are placed in SoCs and brief details on different faults and fault models of eSRAM with their implementation methods were discussed in Chapter 1. The criterion is to reduce the test time in addition to the complete fault coverage.