# DESIGN AND PERFORMANCE OPTIMIZATION OF MODIFIED TUNNEL FIELD EFFECT TRANSISTOR (TFET) FOR HIGHLY EFFICIENT, LOW POWER, DIGITAL VLSI CIRCUIT APPLICATIONS

Thesis Submitted for the Award of the Degree of

# **DOCTOR OF PHILOSOPHY**

in

**Electronics and Communication Engineering**

By

Sabitabrata Bhattacharya

**Registration Number: 41900709**

**Supervised By**

Dr. Suman Lata Tripathi (21067) School of Electronics and Electrical Engineering (Professor) Lovely Professional University

Transforming Education Transforming India

LOVELY PROFESSIONAL UNIVERSITY, PUNJAB 2024

## **DECLARATION**

I, hereby declared that the presented work in the thesis entitled "Design and Performance Optimization of Modified Tunnel Field Effect Transistor (TFET) for Highly Efficient, Low Power, Digital VLSI Circuit Applications" in fulfilment of degree of Doctor of Philosophy (Ph. D.) is outcome of research work carried out by me under the supervision of Dr. Suman Lata Tripathi, working as Professor, in the School of Electronics and Electrical Engineering of Lovely Professional University, Punjab, India. In keeping with general practice of reporting scientific observations, due acknowledgements have been made whenever work described here has been based on findings of other investigator. This work has not been submitted in part or full to any other University or Institute for the award of any degree.

Jasilebrah Blety

(Signature of Scholar)

Name of the scholar: SABITABRATA BHATTACHARYA

Registration No.: **41900709**

Department/school: Electronics & Communication Engineering

Lovely Professional University,

Punjab, India

## **CERTIFICATE**

This is to certify that the work reported in the Ph. D. thesis entitled "Design and Performance Optimization of Modified Tunnel Field Effect Transistor (TFET) for Highly Efficient, Low Power, Digital VLSI Circuit Applications" submitted in fulfillment of the requirement for the award of degree of Doctor of Philosophy (Ph.D.) in the <u>Electronics &</u> <u>Communication Engineering Department</u>, is a research work carried out by <u>Sabitabrata</u> <u>Bhattacharva</u>, (41900709), is bonafide record of his original work carried out under my supervision and that no part of thesis has been submitted for any other degree, diploma or equivalent course.

sminni

(Signature of Supervisor)

Name of supervisor: Dr. Suman Lata Tripathi

Designation: Professor

Department/school: School of Electronics and Electrical Engineering

University: Lovely Professional University, Punjab, India

#### ABSTRACT

In today's scenario VLSI Technology is growing by shrinking its unit modules or the transistors. MOSFETs which has ruled the VLSI market for almost three decades is now becoming unable to follow the Moore's law pattern due to its thermionic limitation of subthreshold slope and rapidly increasing short channel effects (SCEs) in the nanometre regime. A new device at least as much efficient as the MOSFET but prone to it's scaling limitation is the need of the hour. TFET is one such candidate. It is structuring very similar to MOS but it's operating principle is entirely different. But it has certain other limitations like poor ON current and ambipolarity. The present research focuses on fighting these limitations of TFET by performing structural, geometrical and material modifications in it. Firstly, the research introduces the VLSI domain, it's advent and evolution to it's present state. Then the motivation behind taking up the Tunnel FET device is illustrated. Next the conventional structure of the TFET and it's structural similarities and differences with MOSFET is explained. After that all the digital and analog/RF performance parameters for estimating the efficiency of a TFET structure are introduced in detail. Two Simulation tools, viz Cogenda Visual TCAD and Silvaco Atlas are extensively used throughout the research. A brief introduction to both the tools are given. A detailed literature survey is done on almost all the variations of TFET device proposed by researchers from time to time until the present day. Some researchers have proposed Double Gate structure for better control over the channel current. Much research is done on engineering the gate dielectric to high-k and low -k combination in place of a single oxide layer. Heterogenous metal combination for the gate contact is also used by some researchers to have a variation of metal work functions to bring about better performance. Junctionless or dopingless techniques are also employed, like charge plasma to form a n electrically induced junction in place of a permanent on to avoid leakages. To increase the tunnelling phenomenon lower bandbap materials are also utilised.Some researchers applied vertical channel to have transverse tunnelling along with the lateral counterpart so as to increase the overall drive current. Many application orientated research is also done to use the TFET device for Bio-molecule sensors etc. We firstly developed a novel device called n channel JL DG TFET with a SiGe p+ pocket towards the source and optimised it with respect to 4 metrics, viz channel length, gate metal -oxide combination, mole fraction of Ge in the pocket and temperature and designed the optimum structure and verified it for efficiency with rigorous simulations. Next, we developed p-JL DG TFET with similar procedure and with the combination of both designed an inverter circuit and verified its

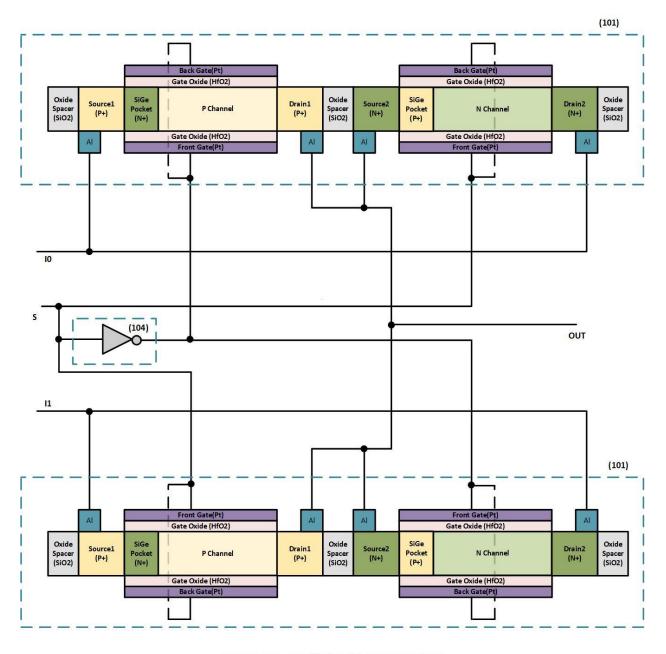

performance. Next, we designed two transmission gate (TG) circuits using our constructed and optimised complementary JL DG TFET and JL SG TFET with SiGe source pockets. The device performed well above expectations. Finally, we concluded our research with the development of yet another well-established circuit the 2x1 Multiplexer (MUX) using the complementary JL DG TFET and the TG made using it.

#### ACKOWLEGMENT

First and foremost, I am thankful to the almighty for making things possible at the right time. I owe my success to my supervisor and would like to sincerely thank Dr. Suman Lata Tripathi for her guidance. I greatly appreciate her support, positive attitude, and her vast knowledge in a wide range of topics. Her guidance not only in terms of giving ideas and solving research problems, but also in terms of giving freedom to do research in my own ways has proved to be useful and invaluable. I am deeply influenced by my supervisor's way of guidance and sincerely thankful for standing by my side in tough times. I would like to thank my wife Raka Chatterjee, for her unconditional love, support, and encouragement. Last but not least, I would like to thank my family (especially my mother and son) and my friends for their continuous love and support. Finally, a special thanks to all the people who helped me in direct and indirect ways to accomplish this work.

# TABLE OF CONTENTS

| DECLARATION.                                                     | II  |

|------------------------------------------------------------------|-----|

| CERTIFICATE                                                      | III |

| ABSTRACT                                                         | IV  |

| ACKNOWLEDGEMENT                                                  | VI  |

| TABLE OF CONTENTS                                                | VII |

| LIST OF TABLES                                                   | XI  |

| LIST OF FIGURES                                                  | XII |

| CHAPTER 1: INTRODUCTION                                          | 1   |

| 1.1 Brief History of VLSI Design                                 | 1   |

| 1.2 Moore's Law and its continued significance                   | 3   |

| 1.3 Motivation behind selection of TFET for the present research | 5   |

| 1.4 Basic structure of Tunnel FET                                | 6   |

| 1.5 Performance Parameters of Tunnel FET                         | 8   |

| 1.5.1 Threshold Voltage                                          | 8   |

| 1.5.2 Subthreshold Slope                                         | 8   |

| 1.5.3 ON State Current.                                          | 9   |

| 1.5.4 OFF State Current                                          | 9   |

| 1.5.5 Drain Induced Barrier Lowering (DIBL).                     | 9   |

| 1.6 Analog/RF performance parameters of TFET                     | 10  |

| 1.6.1 Transconductance.                                          | 10  |

| 1.6.2 Cut-off Frequency                                          | 10  |

| 1.6.3 Gain-Bandwidth Product(GBP)                                | 11  |

| 1.6.4 Transit Time                                               | 11  |

| 1.7 TCAD Simulation Tools used in this research                  | 11  |

| 1.7.1 Cogenda Visual TCAD tool                                   | 12  |

| 1.7.2 Silvaco ATLAS TCAD tool                                    | 12  |

| 1.8 Outline of the Thesis                                        | 13  |

| CHAPTER 2: LITERATURE REVIEW                                     | 14  |

| 2.1 GDO HD GAA TFET                                              | 14  |

|    | 2.2 LD-HTFET                                                        | 15 |

|----|---------------------------------------------------------------------|----|

|    | 2.3 SiGe S NW TFET                                                  | 16 |

|    | 2.4 HGD DW TFET                                                     | 16 |

|    | 2.5 TM GAA TFET                                                     | 17 |

|    | 2.6 U HJ VTFET                                                      | 18 |

|    | 2.7 VS-TFET                                                         | 19 |

|    | 2.8 DE-QG-TFET                                                      | 20 |

|    | 2.9 Core and Shell Gate Si nanotube TFET                            | 21 |

|    | 2.10 DMCG CP TFET                                                   | 22 |

|    | 2.11 HGD DE DMG DL TFET                                             | 23 |

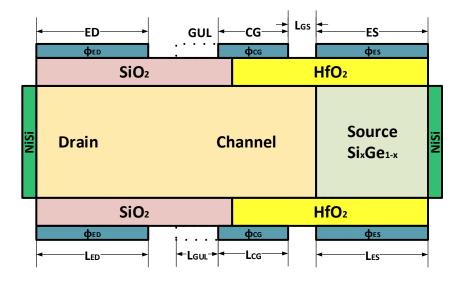

|    | 2.12 HM GUL ED TFET                                                 | 24 |

|    | 2.13 JL-TFET with SiGe n+ pocket                                    | 25 |

|    | 2.14 JL SG TFET                                                     | 25 |

|    | 2.15 Doping Less Si Nanowire Vertical TFET                          | 26 |

|    | 2.16 SD SG TFET                                                     | 27 |

|    | 2.17 GOSC TFET with BOX Layer                                       | 28 |

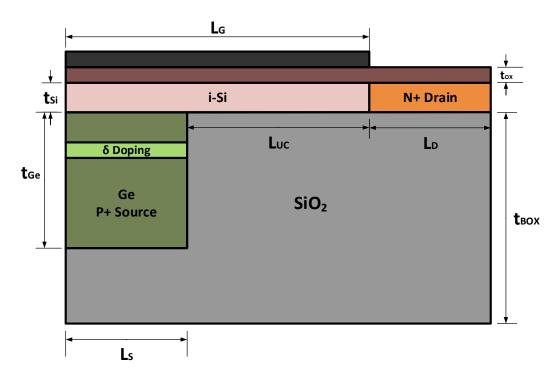

|    | 2.18 L BOX Ge Source Vertical TFET                                  | 29 |

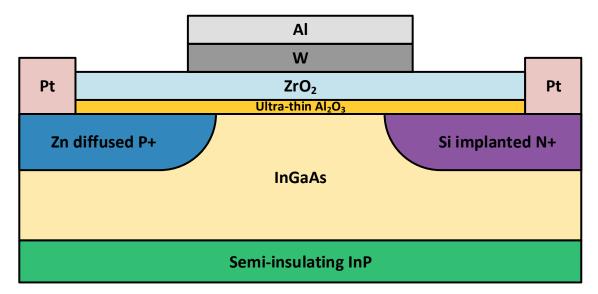

|    | 2.19 W/ZrO2/Al2O3 gate stack Zn Source InGaAs planer TFET           | 30 |

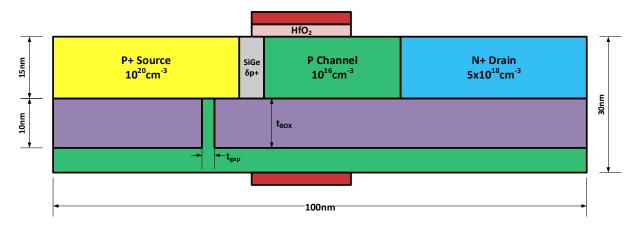

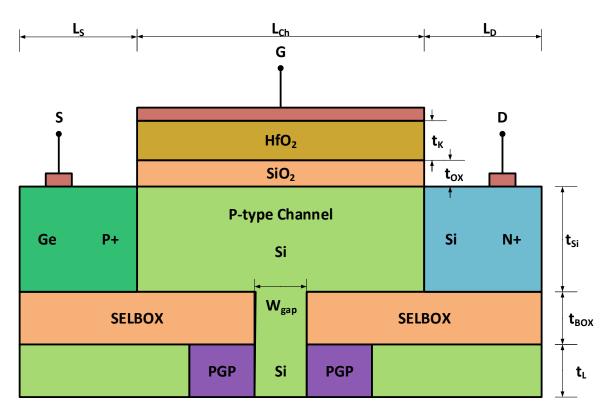

|    | 2.20 p+ SiGe Layer SELBOX TFET                                      | 31 |

|    | 2.21 GSHJ-PGP-STFET                                                 | 32 |

|    | 2.22 V DM TFET for biomolecule sensing                              | 33 |

|    | 2.23 A Comparative Study of Recent TFET Architectures               | 39 |

|    | 2.24 Problem Formulation                                            | 41 |

|    | 2.25 Research Objectives                                            | 43 |

| CH | IAPTER 3: Dual Gate Tunnel FET with SiGe Pocket with 18nm tech node | 45 |

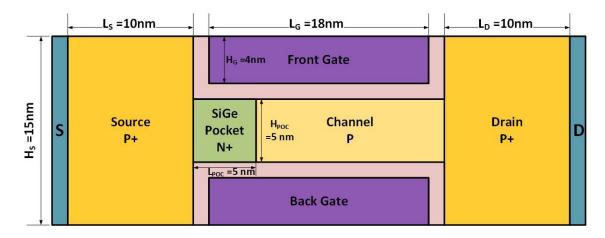

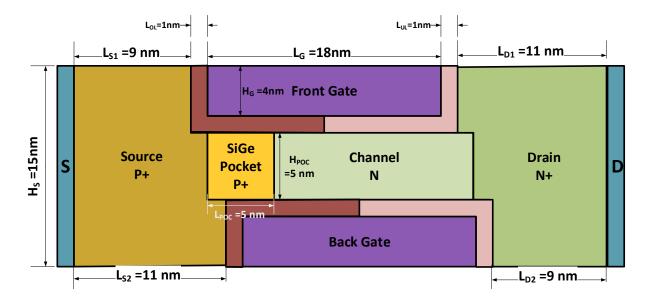

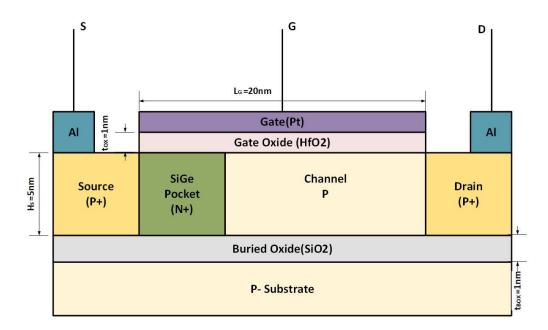

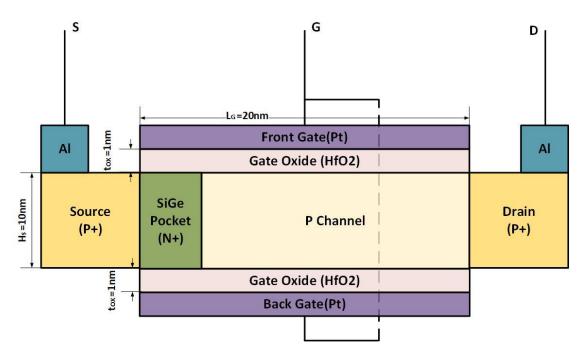

|    | 3.1 Structure and dimensions of the JL DG TFET                      | 46 |

|    | 3.2 Detailed Analysis of the JL DG TFET                             | 46 |

|    | 3.3 Summary                                                         | 51 |

| CH | IAPTER 4: Low Power Inverter with SiGe Pocket N & P JL DG TFETs     | 53 |

|    | 4.1 Geometry and Measurements for n channel JL DG TFET              | 53 |

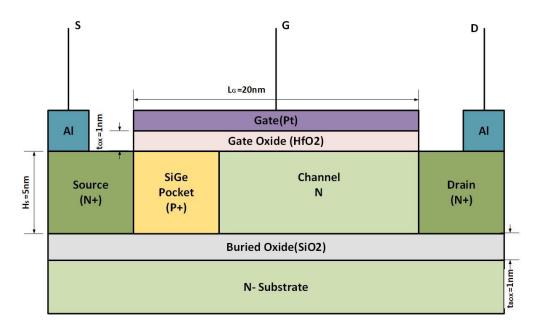

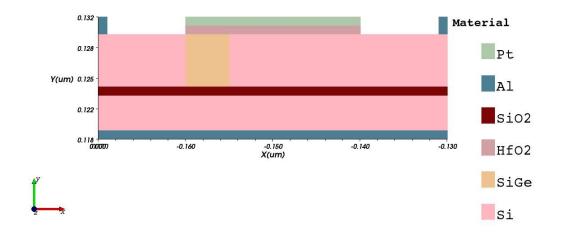

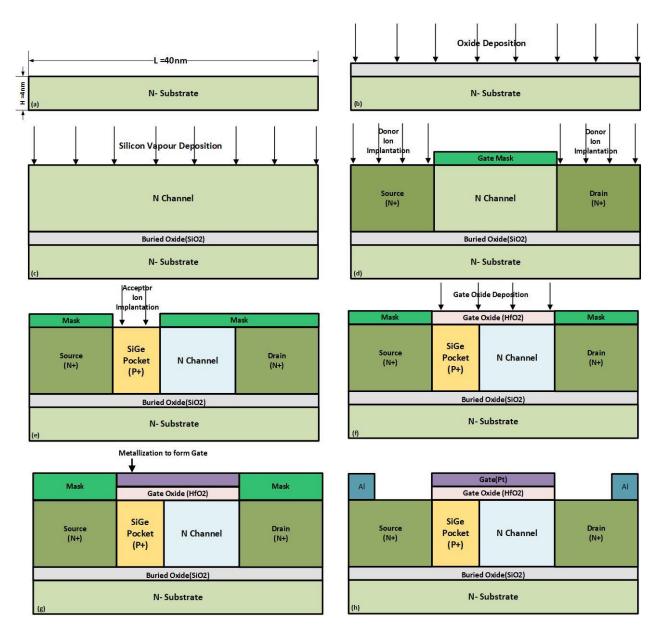

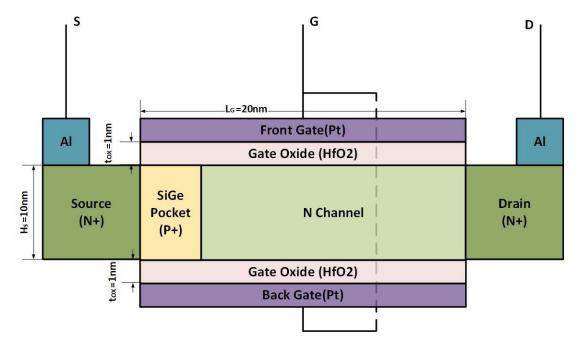

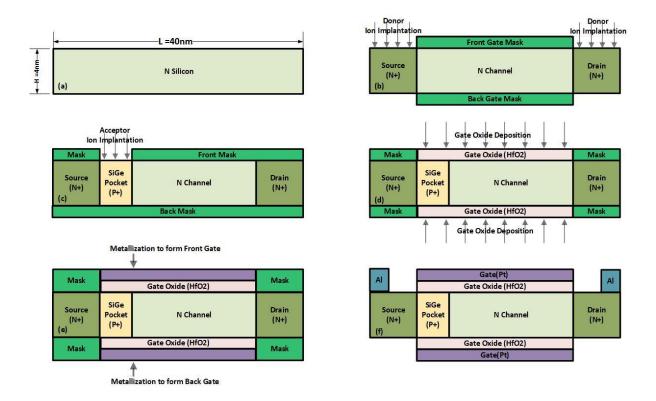

| 4.2 Process for Fabricating of the nJL DG TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

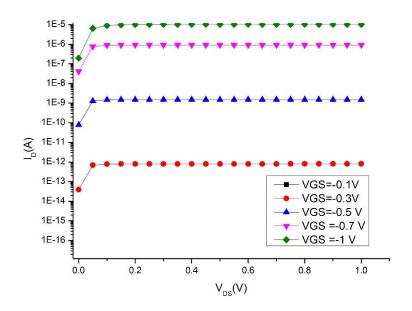

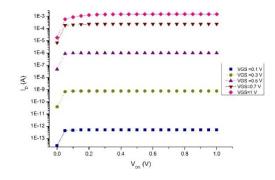

| 4.3 Characteristic curves of the nJL DG TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55                                                                               |

| 4.4 Optimization of the nJL DG TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57                                                                               |

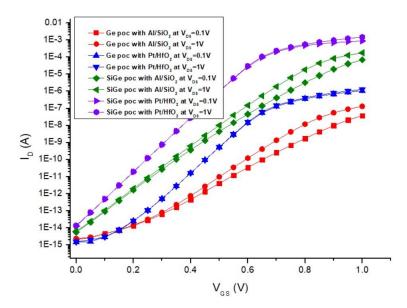

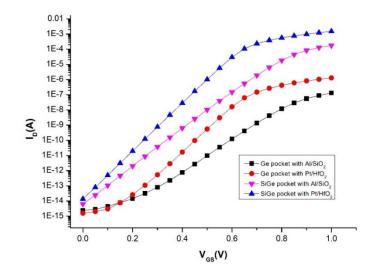

| 4.4.1 Optimization of the Metal Contact & Oxide layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57                                                                               |

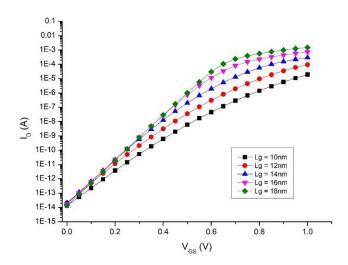

| 4.4.2 Optimization of the Length of the Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 58                                                                               |

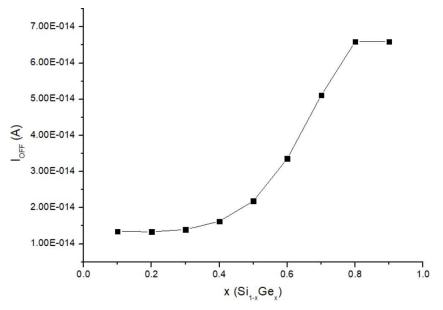

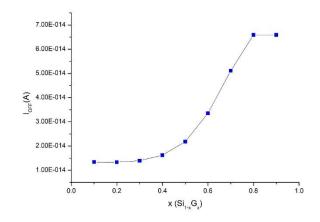

| 4.4.3 SiGe pocket mole fraction optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 59                                                                               |

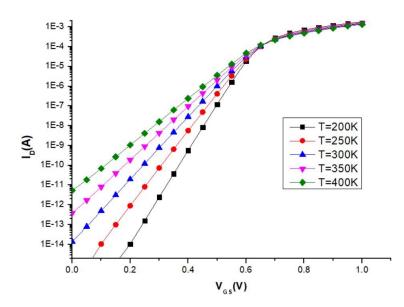

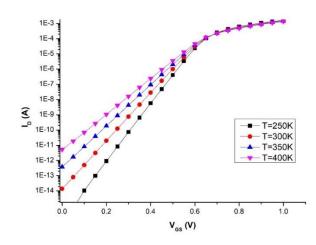

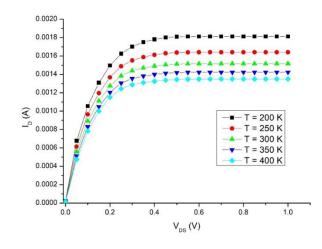

| 4.4.4 Optimization with Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 59                                                                               |

| 4.5 Construction of the p-JL DG TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 61                                                                               |

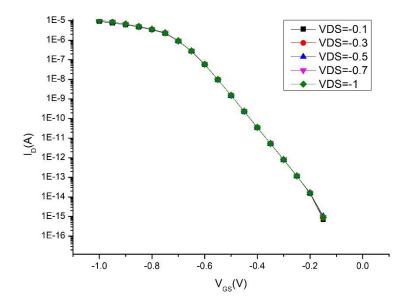

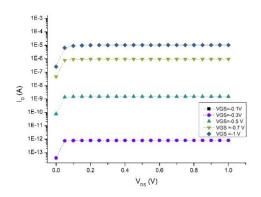

| 4.5.1 Characteristics of p-JL DG TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62                                                                               |

| 4.6 Construction of Inverter using n & p-JL DG TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64                                                                               |

| 4.7 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 64                                                                               |

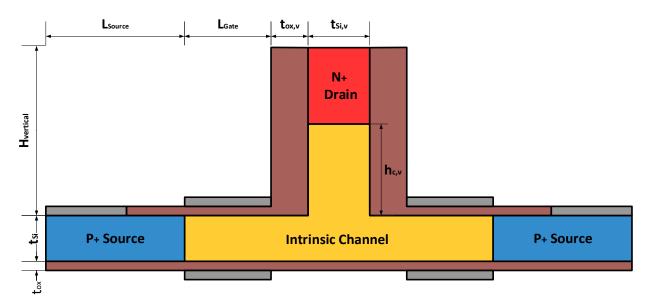

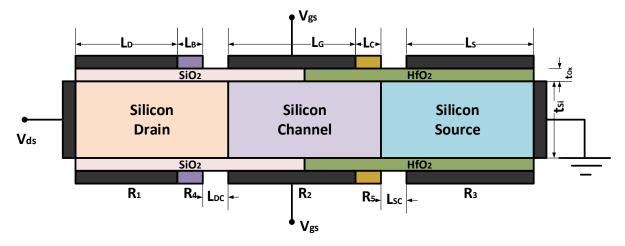

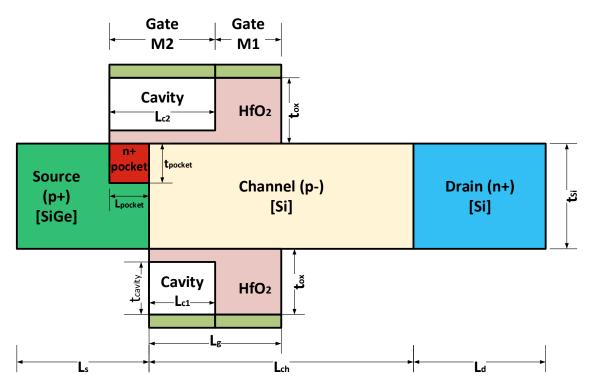

| CHAPTER 5: Asymmetric double gate P-I-N Tunnel FET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66                                                                               |

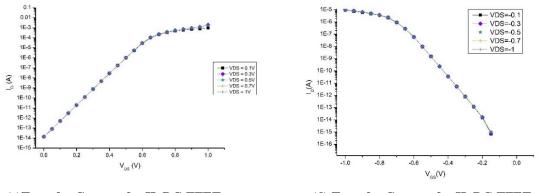

| 5.1 Dimensions and Structure of Asymmetric double gate P-I-N TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 67                                                                               |

| 5.2 Findings and Interpretations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68                                                                               |

| 5.3 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 69                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| CHAPTER 6: Application of the JL TFETs: Implementation of TG & 2:1 MUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 71                                                                               |

| CHAPTER 6: Application of the JL TFETs: Implementation of TG & 2:1 MUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>71</b><br>72                                                                  |

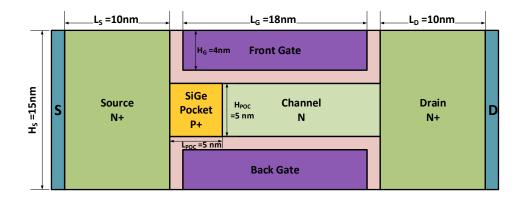

| CHAPTER 6: Application of the JL TFETs: Implementation of TG & 2:1 MUX<br>6.1 Structure & Geometry of n-JL SG TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>71</b><br>72<br>74                                                            |

| CHAPTER 6: Application of the JL TFETs: Implementation of TG & 2:1 MUX<br>6.1 Structure & Geometry of n-JL SG TFET<br>6.2 Process for Fabrication of the n-JL SG TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>71</b><br>72<br>74<br>75                                                      |

| CHAPTER 6: Application of the JL TFETs: Implementation of TG & 2:1 MUX<br>6.1 Structure & Geometry of n-JL SG TFET<br>6.2 Process for Fabrication of the n-JL SG TFET<br>6.3 Geometry & Structure of p-JL SG TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>71</b><br>72<br>74<br>75<br>76                                                |

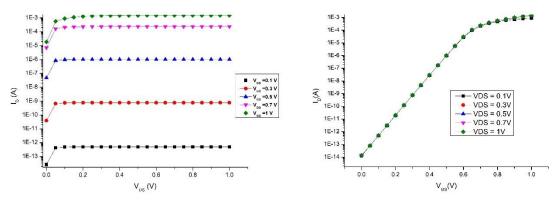

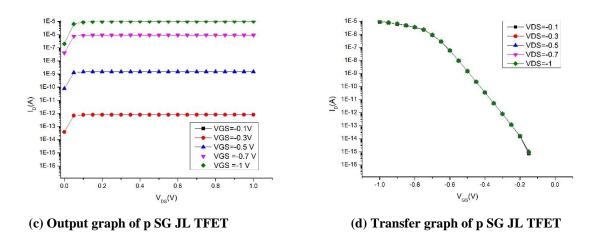

| CHAPTER 6: Application of the JL TFETs: Implementation of TG & 2:1 MUX<br>6.1 Structure & Geometry of n-JL SG TFET<br>6.2 Process for Fabrication of the n-JL SG TFET<br>6.3 Geometry & Structure of p-JL SG TFET<br>6.4 Characteristic graphs for n & p SG TFETs with BOX layer                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>71</b><br>72<br>74<br>75<br>76<br>77                                          |

| <ul> <li>CHAPTER 6: Application of the JL TFETs: Implementation of TG &amp; 2:1 MUX</li> <li>6.1 Structure &amp; Geometry of n-JL SG TFET</li> <li>6.2 Process for Fabrication of the n-JL SG TFET</li> <li>6.3 Geometry &amp; Structure of p-JL SG TFET</li> <li>6.4 Characteristic graphs for n &amp; p SG TFETs with BOX layer</li> <li>6.5 Comparing the performance of the SG JL TFET to the traditional MOSFET</li> </ul>                                                                                                                                                                                                                                                                                                          | <b>71</b><br>72<br>74<br>75<br>76<br>77<br>77                                    |

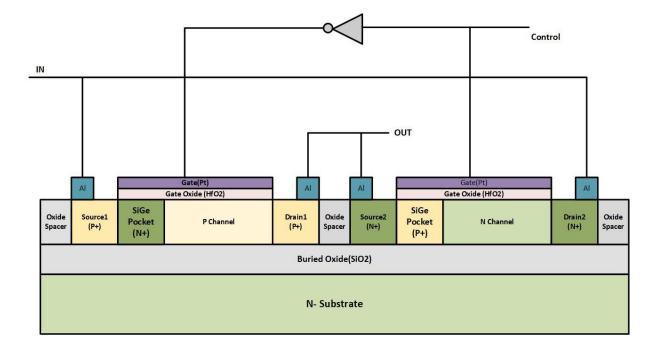

| <ul> <li>CHAPTER 6: Application of the JL TFETs: Implementation of TG &amp; 2:1 MUX</li> <li>6.1 Structure &amp; Geometry of n-JL SG TFET</li> <li>6.2 Process for Fabrication of the n-JL SG TFET</li> <li>6.3 Geometry &amp; Structure of p-JL SG TFET</li> <li>6.4 Characteristic graphs for n &amp; p SG TFETs with BOX layer</li> <li>6.5 Comparing the performance of the SG JL TFET to the traditional MOSFET</li> <li>6.6 Construction of TG with n &amp; p-JL SG TFETs</li> </ul>                                                                                                                                                                                                                                               | 71<br>72<br>74<br>75<br>76<br>77<br>77<br>78                                     |

| <ul> <li>CHAPTER 6: Application of the JL TFETs: Implementation of TG &amp; 2:1 MUX</li> <li>6.1 Structure &amp; Geometry of n-JL SG TFET</li> <li>6.2 Process for Fabrication of the n-JL SG TFET</li> <li>6.3 Geometry &amp; Structure of p-JL SG TFET</li> <li>6.4 Characteristic graphs for n &amp; p SG TFETs with BOX layer</li> <li>6.5 Comparing the performance of the SG JL TFET to the traditional MOSFET</li> <li>6.6 Construction of TG with n &amp; p-JL SG TFETs</li> <li>6.7 VTC of the TG constructed with n &amp; p-JL SG TFETs</li> </ul>                                                                                                                                                                             | 71<br>72<br>74<br>75<br>76<br>77<br>77<br>78<br>79                               |

| <ul> <li>CHAPTER 6: Application of the JL TFETs: Implementation of TG &amp; 2:1 MUX</li> <li>6.1 Structure &amp; Geometry of n-JL SG TFET</li> <li>6.2 Process for Fabrication of the n-JL SG TFET</li> <li>6.3 Geometry &amp; Structure of p-JL SG TFET</li> <li>6.4 Characteristic graphs for n &amp; p SG TFETs with BOX layer</li> <li>6.5 Comparing the performance of the SG JL TFET to the traditional MOSFET</li> <li>6.6 Construction of TG with n &amp; p-JL SG TFETs</li> <li>6.7 VTC of the TG constructed with n &amp; p-JL SG TFETs</li></ul>                                                                                                                                                                              | 71<br>72<br>74<br>75<br>76<br>77<br>77<br>78<br>79<br>81                         |

| <ul> <li>CHAPTER 6: Application of the JL TFETs: Implementation of TG &amp; 2:1 MUX</li> <li>6.1 Structure &amp; Geometry of n-JL SG TFET</li> <li>6.2 Process for Fabrication of the n-JL SG TFET</li> <li>6.3 Geometry &amp; Structure of p-JL SG TFET</li> <li>6.4 Characteristic graphs for n &amp; p SG TFETs with BOX layer</li> <li>6.5 Comparing the performance of the SG JL TFET to the traditional MOSFET</li> <li>6.6 Construction of TG with n &amp; p-JL SG TFETs</li> <li>6.7 VTC of the TG constructed with n &amp; p-JL SG TFETs</li> <li>6.8 Geometry &amp; Dimensions of n-JL DG TFETs</li> <li>6.9 Steps for Fabrication of the n-JL DG TFET</li> </ul>                                                              | 71<br>72<br>74<br>75<br>76<br>77<br>77<br>78<br>79<br>81<br>82                   |

| <ul> <li>CHAPTER 6: Application of the JL TFETs: Implementation of TG &amp; 2:1 MUX</li> <li>6.1 Structure &amp; Geometry of n-JL SG TFET.</li> <li>6.2 Process for Fabrication of the n-JL SG TFET</li> <li>6.3 Geometry &amp; Structure of p-JL SG TFET.</li> <li>6.4 Characteristic graphs for n &amp; p SG TFETs with BOX layer</li> <li>6.5 Comparing the performance of the SG JL TFET to the traditional MOSFET.</li> <li>6.6 Construction of TG with n &amp; p-JL SG TFETs</li> <li>6.7 VTC of the TG constructed with n &amp; p-JL SG TFETs</li> <li>6.8 Geometry &amp; Dimensions of n-JL DG TFETs</li> <li>6.9 Steps for Fabrication of the n-JL DG TFET</li> <li>6.10 Geometry &amp; Measurements of p-JL DG TFET</li> </ul> | 71<br>72<br>74<br>75<br>76<br>77<br>77<br>78<br>79<br>81<br>82<br>83             |

| <ul> <li>CHAPTER 6: Application of the JL TFETs: Implementation of TG &amp; 2:1 MUX</li> <li>6.1 Structure &amp; Geometry of n-JL SG TFET</li> <li>6.2 Process for Fabrication of the n-JL SG TFET</li> <li>6.3 Geometry &amp; Structure of p-JL SG TFET</li> <li>6.4 Characteristic graphs for n &amp; p SG TFETs with BOX layer</li> <li>6.5 Comparing the performance of the SG JL TFET to the traditional MOSFET</li></ul>                                                                                                                                                                                                                                                                                                           | 71<br>72<br>74<br>75<br>76<br>77<br>77<br>77<br>78<br>79<br>81<br>82<br>83<br>84 |

| 6.15 Comparative Study of TG with SG JL TFETs & DG JL TFETs |     |

|-------------------------------------------------------------|-----|

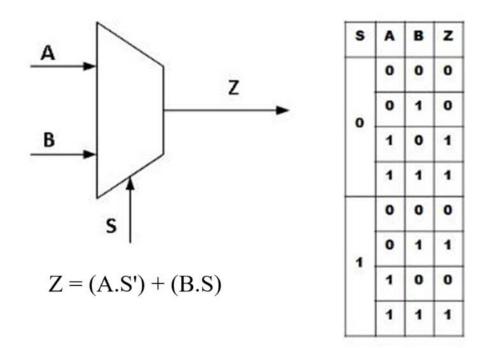

| 6.16 A Digital Multiplexer                                  |     |

| 6.17 Implementation of 2:1 MUX using n & p-JL DG TFETs      |     |

| 6.18 Conclusions                                            | 91  |

| CHAPTER 7: CONCLUSION & FUTURE SCOPE                        | 92  |

| 7.1 Conclusion                                              |     |

| 7.2 Future Scopes                                           |     |

| BIBLIOGRAPY                                                 | 94  |

| LIST OF PUBLICATIONS                                        | 106 |

# LIST OF TABLES

| 2.1 Literature review                                           |    |

|-----------------------------------------------------------------|----|

| 2.2 Comparison of TFET designs' performances for DC parameters  | 40 |

| 2.3 Analog/RF performance parameters comparison of TFET designs | 41 |

| 2.4 Device Abbreviations Chart                                  | 44 |

| 3.1 Measurements of the n-JL DG TFET                            |    |

| 3.2 Performance comparison, gate contacts, oxides               |    |

| 3.3 Performance matrix, gate lengths                            |    |

| 3.4 Comparison matrix of SS for gate length, temperature        |    |

| 3.5 Comparison matrix of JL DG TFET with contemporary TFETs     | 51 |

| 4.1 Detailed dimensions p+ SiGe pocket nJL DG TFET              |    |

| 4.2 Performance Matrix of n-JL DG TFET                          |    |

| 4.3 Performance Matrix of n-JL DG TFET with L <sub>G</sub>      |    |

| 4.4 Comparison of SS for $L_G \& T$                             | 61 |

| 5.1 Asymmetric double gate P-I-N TFET Dimensions                | 67 |

| 6.1 TG Truth Table                                              | 72 |

| 6.2 Dimension Matrix for n-JL SG TFET                           | 72 |

| 6.3 Table of Comparison for SG JL TFET and MOSFET               | 77 |

| 6.4 Dimension Matrix for n-JL DG TFET                           |    |

| 6.5 Table of Comparison for DG JL TFET and SG JL TFET           |    |

| 6.6 Comparison Matrix of TGs                                    |    |

# LIST OF FIGURES

| 1.1 Moore's Law                                                                |

|--------------------------------------------------------------------------------|

| 1.2 Fundamental Architecture of n & p TFET and n MOS7                          |

| 2.1 Cross Section of GDO HD GAA TFET15                                         |

| 2.2 Cross Section of LD HTFET                                                  |

| 2.3 Cross Section of SiGe S NW TFET16                                          |

| 2.4 Cross Section of HGD DW TFET17                                             |

| 2.5 Cross Section of TM GAA TFET                                               |

| 2.6 Cross Section of U HJ VTFET 19                                             |

| 2.7 Cross Section of DG VS TFET20                                              |

| 2.8 Cross Section of T-Channel DE QG TFET21                                    |

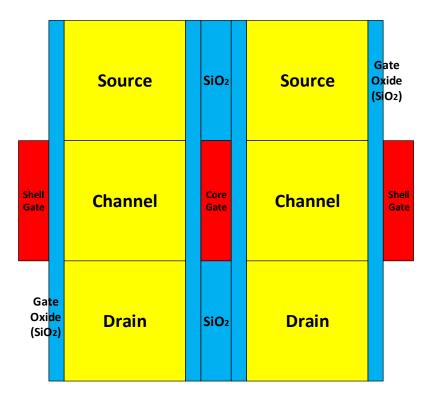

| 2.9 Cross Section of Core & Shell Gate Si nanotube TFET                        |

| 2.10 Cross Section of DMCG CP TFET                                             |

| 2.11 Cross Section of HGD DE DMG DL TFET                                       |

| 2.12 Cross Section of HM GUL ED TFET24                                         |

| 2.13 Cross Section of JL TFET with SiGe n+ pocket25                            |

| 2.14 Cross Section of SiGe source pocket JL SG TFET26                          |

| 2.15 Cross Section of Doping less Vertical TFET27                              |

| 2.16 Cross Section of SD SG TFET                                               |

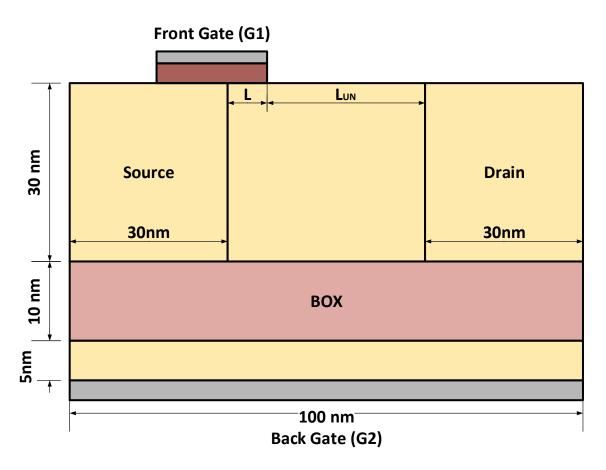

| 2.17 Cross Section of GOSC TFET with BOX layer                                 |

| 2.18 Cross Section of L BOX Ge Source Vertical TFET                            |

| 2.19 Cross Section of W/ZrO2/Al2O3 gate stack Zn Source InGaAs planer TFET .31 |

| 2.20 Cross Section of p+ SiGe Layer SELBOX TFET                                |

| 2.21 Cross Section of GSHJ-PGP-STFET                                           |

| 2.22 Cross Section of V DM TFET for bio-sensing                                |

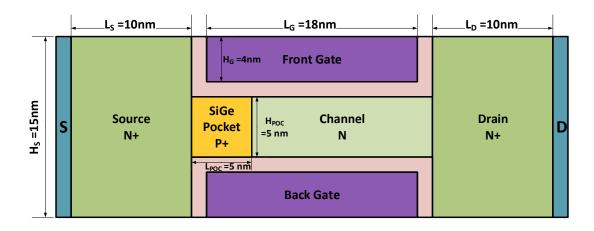

| 3.1 Cross Section of JL DG TFET with P+ SiGe pocket                            |

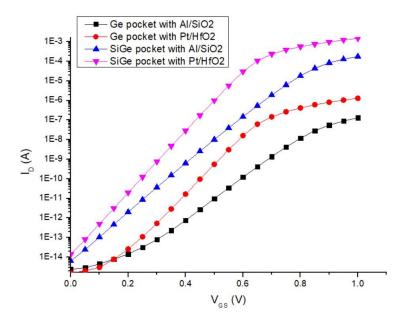

| 3.2 Transfer Curve of nJL DG TFET with varying gate contact, pocket & oxide47  |

| 3.3 Transfer Curve of nJL DG TFET in linear and saturation regions           | 47 |

|------------------------------------------------------------------------------|----|

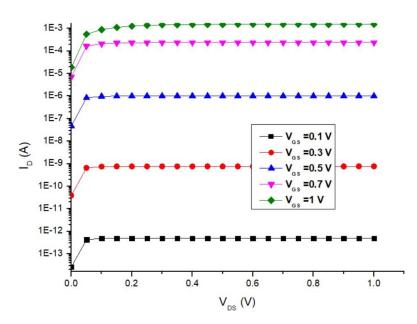

| 3.4 Output Curve of nJL DG TFET                                              | 48 |

| 3.5 Transfer Curve of nJL DG TFET with varying gate length                   | 48 |

| 3.6 Mole fraction(x) of Ge with I <sub>OFF</sub>                             | 49 |

| 3.7 Transfer Curve of nJL DG TFET with varying T                             | 49 |

| 4.1 p+ SiGe pocket nJL DG TFET                                               | 54 |

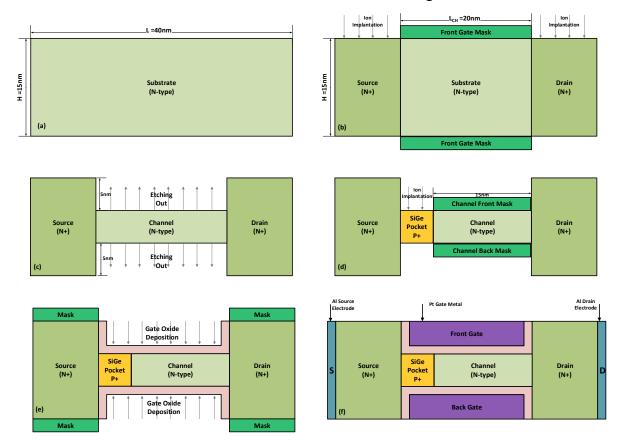

| 4.2 Fabrication steps for nJL DG TFET                                        | 55 |

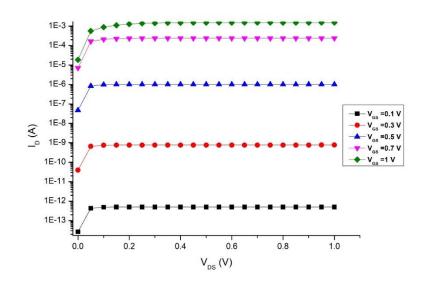

| 4.3 Drain Curve of nJL DG TFET                                               | 56 |

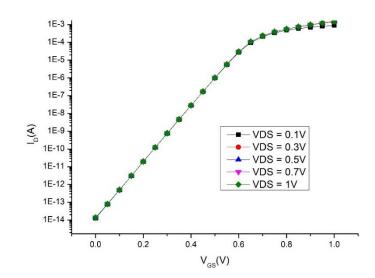

| 4.4 Transfer Curve of nJL DG TFET                                            | 56 |

| 4.5 Transfer Curve of nJL DG TFET with varying pocket, metal, oxide          | 57 |

| 4.6 Transfer Curve of nJL DG TFET with varying L <sub>G</sub>                | 58 |

| 4.7 Mole fraction(x) of Ge with I <sub>OFF</sub>                             | 59 |

| 4.8 Transfer Curve of nJL DG TFET with varying T                             | 60 |

| 4.9 Drain Curve of nJL DG TFET with varying T                                | 60 |

| 4.10 n+ SiGe pocket p-JL DG TFET                                             | 61 |

| 4.11 Output Curve of p-JL DG TFET                                            | 62 |

| 4.12 Transfer Curve of pJL DG TFET                                           | 63 |

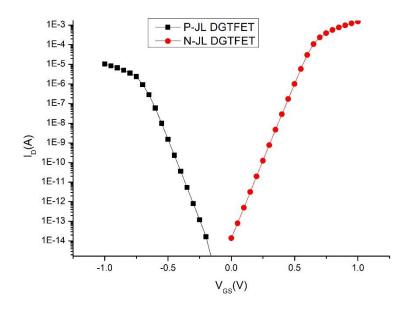

| 4.13 Transfer Curve of p-JL & n-JL DG TFET together on same plot             | 63 |

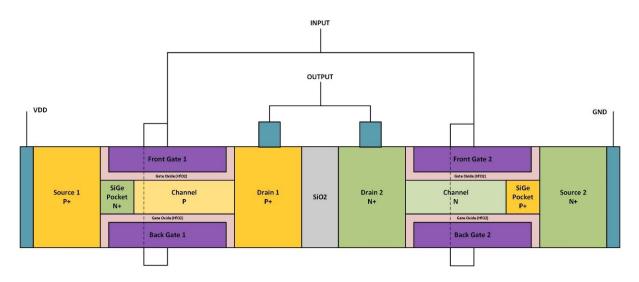

| 4.14 Inverter using n & p -JL DG TFET                                        | 64 |

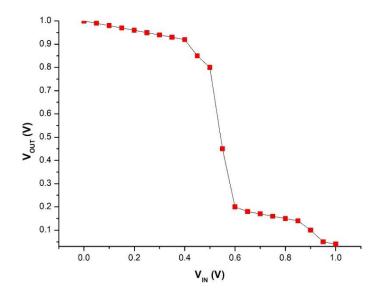

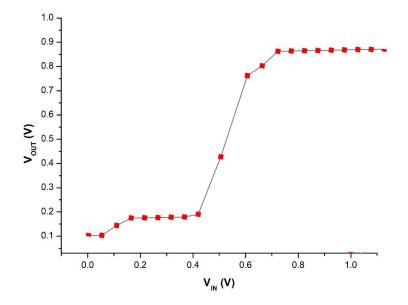

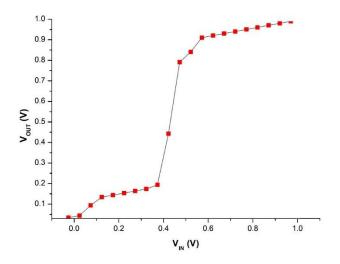

| 4.15 $V_{\text{OUT}}$ v/s $V_{\text{IN}}$ of the inverter using c-JL DG TFET | 65 |

| 5.1 proposed Asymmetric double gate P-I-N TFET structure                     | 66 |

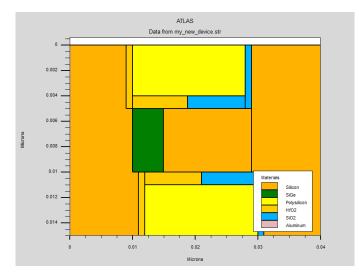

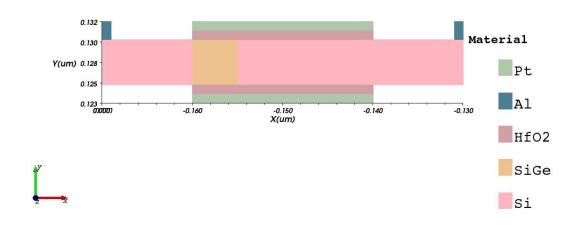

| 5.2 Asymmetric double gate P-I-N TFET on Tonyplot of Silvaco Atlas           | 67 |

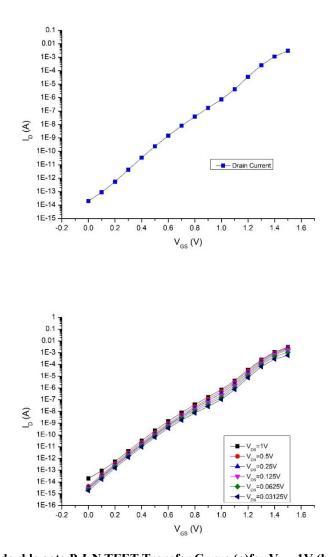

| 5.3 Asymmetric double gate P-I-N TFET Transfer Curve                         | 68 |

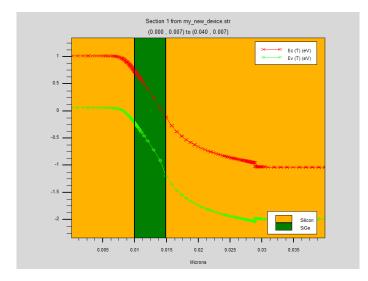

| 5.4 Valence Band (VB) and Conduction Band (CB) of the device at 300K         | 69 |

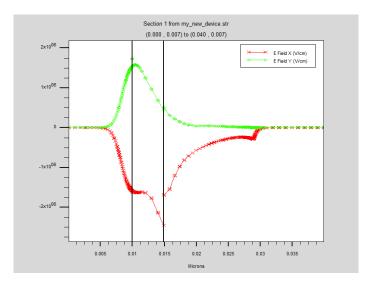

| 5.5 The device's electric field intensity along the x and y axes             | 69 |

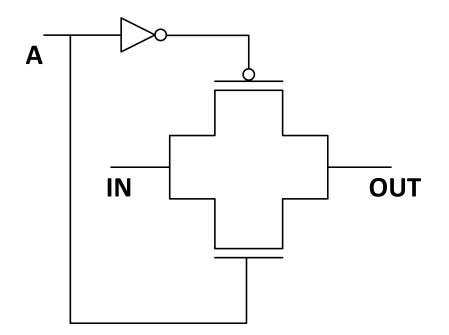

| 6.1 Conventional TG with p & n MOS                                           | 71 |

| 6.2 n-JL SG TFET with p+ pocket & BOX Layer                                  | 73 |

| 6.3 Tool view of n-JL SG TFET                                                | 74 |

| 6.4 Fabrication steps for nJL SG TFET with BOX layer                         | 75 |

| 6.5 p-JL SG TFET with n+ pocket & BOX Layer                                  | 76 |

| 6.6 Output and Transfer curves of the n & p SG JL TFETs with BOX | 77 |

|------------------------------------------------------------------|----|

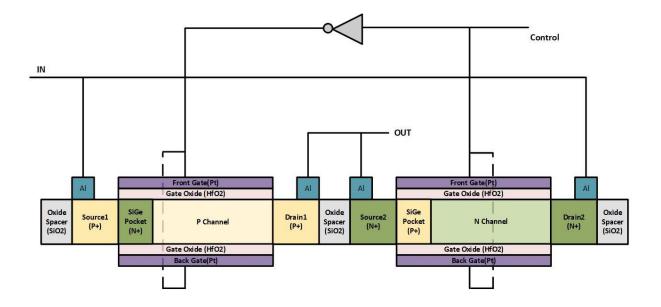

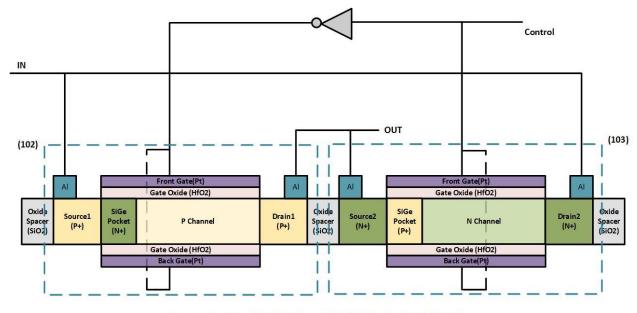

| 6.7 Structure of TG with n & p-JL SG TFETs                       | 78 |

| 6.8 VTC of the TG made with n & p-JL SG TFETs                    | 79 |

| 6.9 n-JL DG TFET with p+ pocket                                  | 80 |

| 6.10 Tool view of n-JL DG TFET with P+ SiGe                      | 81 |

| 6.11 Fabrication steps for nJL DG TFET with P+ SiGe              | 82 |

| 6.12 p-JL DG TFET with n+ pocket                                 | 83 |

| 6.13 Output & Transfer Curves of the n and p JL DG TFETs         | 84 |

| 6.14 Structure of TG with n & p-JL DG TFETs                      | 85 |

| 6.15 VTC of the TG made with n & p-JL DG TFETs                   | 86 |

| 6.16 Block Diagram of 2:1 MUX, Logic Expression & Truth Table    | 88 |

| 6.17 Transmission Gate made with n & p-JL DG TFETs               | 89 |

| 6.18 2:1 MUX made with n & p-JL DG TFETs                         | 90 |

# CHAPTER 1 INTRODUCTION

#### 1.1 Brief History of VLSI Design

First solid-state transistor was invented in 1947 at Bell Labs. First integrated circuit was developed by Jack Kilby at Texas Instruments. Intel launched its Itanium processor in 2008 which consists of 2 billion transistors. The above growth rate corresponds to about 53% in about 50 years. This unprecedented growth has not been shown by any other industry for such a long span of time and it is continuing till this day. This great advancement in the field of VLSI and electronics at large emerged from steady scaling down of transistors and huge improvisations in the fabrication steps. Generally, there is always a trade-off between cost, power consumption and efficiency in most of the engineering industries, but for the case of VLSI the converse became true as when transistors were scaled down their speed increased, power consumption became much lesser, and cost decreased manifolds. This converse nature of the VLSI industry helmed the great progress of electronics and society as well. A teenager's iPod now contains the memory required for an entire company's accounting system.

Integrated circuit advancements have changed the face of warfare, made space travel possible, improved the safety and fuel economy of cars, added a great deal of human knowledge to Web browsers, and flattened the planet. About 6 quintillion  $(6 \times 10^{18})$  transistors, or almost a billion for each person on the earth, were produced by the industry in 2007. Numerous engineers have achieved financial success in this domain. Those with creative ideas and the ability to make them a reality are going to reap new rewards. Electronic circuits in the early half of the 20th century used bulky, pricy, power-hungry, and unstable vacuum tubes. At Bell Laboratories, John Bardeen and Walter Brattain constructed the first operational point contact transistor in 1947. Although Bell Labs almost declared it a military secret, the gadget was unveiled to the public the next year. A decade later, Jack Kilby from Texas Instruments recognised the possibility of miniaturisation provided more than one transistor could be constructed on a single silicon piece. His initial integrated circuit prototype was made with gold wires and a slice of germanium. Bardeen, Brattain, and William Shockley, their mentor, were awarded the 1956 Nobel Prize in Physics for creating the transistor. Kilby's development of the integrated circuit earned him the 2000 Nobel Prize in Physics.

Consider transistors as electrically operated switches that have two extra terminals which are either detached or connected based upon the current or voltage applied at the controlling terminal. Transistors have a controlling terminal called control. Bell Laboratories created the BJT or bipolar junction transistor not long after the invention of point contact transistors. In terms of dependability, noise level, and power efficiency, bipolar transistors were superior. Primarily, bipolar transistors or BJTs were only employed in early integrated circuits (ICs). To switch much greater currents between the other 2 terminals (the collector & emitter terminals), BJTs or bipolar junction transistors need to supply a very tiny amount of current through the base or the control terminal. It is not possible to integrate more transistors onto a single die than this due to the quiescent amount of power dissipated by the base currents, which flows even when the circuit is not undergoing switching.

Metal Oxide Semiconductor Field Effect Transistors, or MOSFETs, started to be produced by the 1960s. The main advantage of MOSFETs is that, when they are idle, they consume negligible control current. MOS devices are available in 2 flavours: n channel MOS & p channel MOS, which utilizes silicon that is n type or p type, respectively. FETs or Field Effect Transistors were first conceptualised in the year 1925 by the German physicist Julius Lilienfield. In the year 1935, Oskar Heil proposed a device that was similar to the MOSFET. However, early attempts to make working devices were thwarted by issues with the materials. The early MOSFET based logic circuits were described in the year 1963 by Frank Wanlass of Fairchild[1]. Fairchild's gates gave rise to the term complementary metal oxide semiconductor, or CMOS, because they incorporated both nMOS and pMOS transistors. Despite using discrete transistors, the circuits' power consumption was just nanowatts, which is almost five orders of value lesser than that of their bipolar equivalents. MOSFET based ICs or integrated circuits gained popularity as a result of their very low cost and simpler fabrication method, which resulted from the development of the silicon planar process and smaller area required for each transistor[2]. Early commercial processes had low yield, reliability, and performance since they solely employed pMOS transistors.

In the 1970s, nMOS transistor processes became widespread[3]. With its 4004 4-bit CPU and 1101 256-bit static RAM, Intel was the first company to proceed further with the nMOS technology. Despite being less expensive to produce than CMOS, nMOS logic gates still required much more power to operate. With the integration millions of transistors into a unit chip in the 1980s, power consumption emerged as a significant concern. Almost, for all digital logic applications, CMOS techniques have largely taken the place of nMOS and bipolar processes due to their widespread adoption.

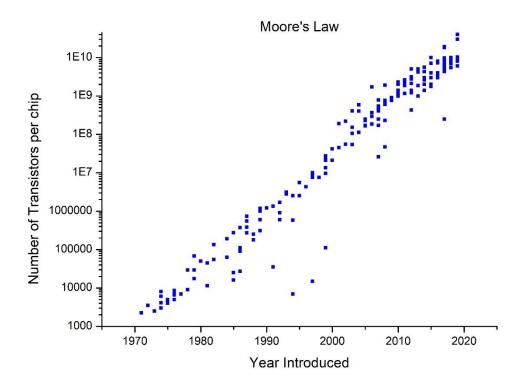

### 1.2 Moore's Law and its continued significance

Plotting the number of transistors that may be produced on a chip most profitably results in an uninterrupted line on a semilogarithmic scale, as Gordon Moore noted in 1965 [4]. He discovered that the transistor count doubled every 18 months at the time. Moore's Law is the name given to this insight, which has come to pass as a self-fulfilling prophecy. Since the 4004's inception, the total quantity of transistors in the processors manufactured by Intel has doubled every 26 months. Building bigger chips and, to a lesser degree, shrinking transistor size are the main forces behind Moore's Law. Fig.1.1 depicts the plot of Moore's Law in its present form.

#### Fig1.1 Moore's Law

Chip integration has been divided into four categories: small-, medium-, large-, and very largescale. Circuits that use small-scale integration (SSI), like the 7404 inverter, have less than ten gates and about six transistors per gate. Circuits classified as medium-scale integration (MSI) include the 74161 counter, which has up to 1000 gates. Up to 10,000 gates can be found in (LSI) large-scale integration circuits, which include basic microprocessors of 8-bits. Once it was realised that if this naming trend persisted, newer names would need to be coined every 5 years, most integrated circuits built after the 1980s is referred to as very large-scale integration, or VLSI.

Dennard's Scaling Law[5] is a corollary to Moore's law, which states that transistors get faster, use less power, and are less expensive to produce as they get smaller. The clock frequency of Intel microprocessors has doubled approximately every 34 months. Around 2004, this frequency scaling reached its limit, and clock frequencies levelled out at 3 GHz. Even more sophisticated than raw clock speed is computer performance, as measured by the amount of time it takes to run an application. These days, a chip's number of cores determines performance rather than its clock speed.

Despite the fact that a single CMOS FET consumes very less energy when it switches, a massive number of transistors flipping at extremely fast speeds has once again made power consumption a crucial design factor. Furthermore, because transistors are now so tiny, they can no longer turn off entirely. When multiplied by a billion or more of transistors on a single chip, little current leaks via each transistor suddenly result in a large power usage. The smallest diameter of a transistor that can be produced with reliability is referred to as the feature size in a CMOS FET manufacturing flow process. In 1971, the 4004's feature size was 10  $\mu$ m. In 2008, the Core 2 Duo's feature size was 45 nm. Every two to three years, manufacturers release a brand new process generation, which is also known as a technology node, that packs two times as many transistors in a similar area but has a 30% reduced feature size. Lower feature sizes are represented in nanometres ( $10^{-9}$  m), while feature sizes of the range of 0.25  $\mu$ m are frequently expressed in microns ( $10^{-6}$  m). Effects including wire resistance, transistor leakage, and differences in the properties of neighbouring transistors, which were comparatively insignificant in micron processes, have a significant impact in nanoscale processes.

Due to the need for every business to stay ahead of its rivals, Moore's Law has continued to be a reality till date. Transistors obviously cannot be any smaller than atoms, hence this scaling cannot continue indefinitely. Dennard scaling has started to decelerate already. Designers are forced to choose between increasing power and decreasing delay by the 45 nm generation[6]. Cutting-edge techniques are limited to IC chips which will trade in large numbers or that have requirements of performance that are at the forefront of the industry, even though the expense of printing individual transistors is decreasing due to the exponential rise in one-time design expenses. Still, several fundamental constraints to scaling forecasts have already shown out to be incorrect. Getting ahead of the competition can provide billions of dollars to creative engineers and material scientists. Experts predicted that scaling would go on for at least ten years in the early 1990s, but after that the future was uncertain. We continue to think that Moore's Law will hold true for at least ten more years in 2024.

#### **1.3 Motivation behind selection of TFET for the present research**

The trend of scaling electronic devices, which was initiated over 50 years ago by Gordon Moore's law, is still going strong. However, the thermionic limitation (60 mV/dec) on the subthreshold swing at ambient temperature has created a bottleneck for scaling using standard MOS devices[7]. Other drawbacks of scaling down MOS devices include higher junction and gate-oxide leakage [8], short channel effects such as Drain Induced Barrier Lowering (DIBL) and V<sub>T</sub> lowering[9], among others. Researchers have occasionally suggested several devices to address the scaling down issues caused by MOS devices. The tunnel field effect transistor, or TFET, is one of the main candidates to replace MOS transistors in contemporary low power CMOS comparable circuits. The TFET, which has a highly doped p+ type material for the source, a highly doped n+ type material for the drain, and an intrinsic or minimally doped region for the channel, is essentially a reverse biassed P-I-N structure[10]. To provide very high input impedance, the gate is constructed over the intrinsic channel with a thin dielectric layer electrically shielding it from the channel. With the exception of the reverse doping at the source and drain regions, the structure of TFET and MOSFET are identical. Because of their similar structures, TFETs can easily replace MOSFETs in circuits that are compatible with CMOS technology [11]. However, in terms of functionality, TFET and MOSFET are completely different from one another since, in contrast to MOS devices, which primarily rely on thermionic emissions, TFETs generate the ON state current using the Band-to-Band Tunnelling mechanism (BTBT). To regulate the conduction of the reverse biassed PIN diode, the TFET gate essentially modifies the tunnelling current across it. Using them, subthreshold slopes significantly lower than 60mV/dec can be achieved because the thermionic emission is not included in the conduction of TFET[11], [12]. In comparison to MOS devices, TFETs have significantly lower dynamic power dissipation, or the power needed or lost when a state changes from high to low or vice versa[11], [13]. Because the TFET devices do not rely on thermionic emissions in any way for conduction, they have the characteristic of having very low OFF state current. They are highly effective in the construction of low power consumption SRAM cells and associative memory (AM) based on cellular neural networks (CNNs) because of their very low off state current & steep SS or subthreshold slope[14], [15]. Since there is a significant fluctuation in channel conduction due to variations in the gate material's dielectric constant, dielectric engineering for the gate insulator is also used to boost the efficiency of the TFET. Applications for biomolecule sensors make use of the TFET current's exceptional sensitivity to changes in the gate oxide's dielectric constant[16], [17]. In addition, TFET-based devices are very helpful in low-power IoT, ML, and AI applications nowadays[15], [18], [19].

A few disadvantages of TFET devices are also present; the two main ones are very tiny ON state current value and ambipolar conduction, or conduction in the opposite direction when switched OFF. Researchers have suggested a number of altered topologies for the traditional TFET devices to lessen these shortcomings. Using numerous gates and gate-all-around structures is one practical strategy for improving ON current and improving channel conduction control [20], [21]. The second method used to improve performance is dielectric engineering of the gate oxide, which involves utilising numerous dielectrics at the gate with different diameters and k values[22], [23]. In order to boost the overall ON current, the TFET can also be built vertically, resulting in lateral BTBT and vertical tunnelling [24]–[26] Asymmetric gates and changes to the channel's gate overlap/underlap can also be used to increase the ON current[27], [28].

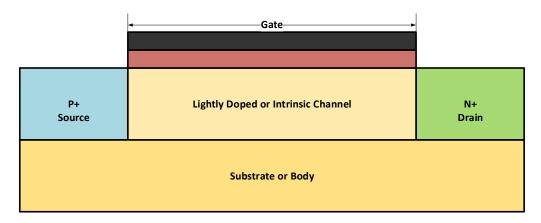

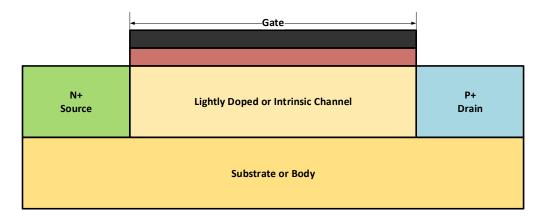

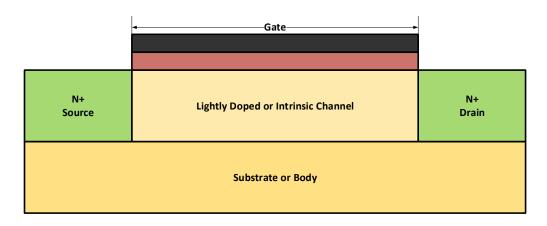

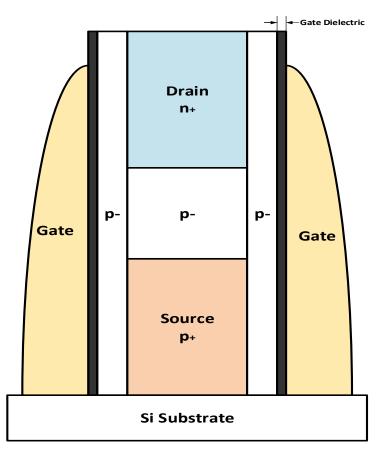

#### **1.4 Basic Structure of Tunnel FET**

Now let's look at the fundamental design of a tunnel FET. The functioning concept of TFET is predicated on this fundamental configuration of regions, terminals and doping [29]; we shall go into numerous modifications of this structure in the literature review chapter. An n-channel TFET's fundamental construction is depicted in Figure 1.2(a). The source, channel, and drain are the three regions of the apparatus. When the architecture of an n-channel MOSFET and n-channel TFET is compared (Figure 1.2(c)), it can be observed that the MOSFET's source doping is n-type, while the TFET's is p-type. The sole significant distinction between a MOSFET and a TFET is this. Typically, the TFET's channel area is either intrinsic or very mildly doped. Figure 1.2(b) illustrates a p-channel TFET.

Fig1.2(a) Fundamental Architecture of n-TFET

Fig1.2(b) Fundamental Architecture of p-TFET

Fig1.2(c) Fundamental Architecture of n-MOSFET

#### **1.5 Performance Parameters of Tunnel FET**

In this section we will go through the major performance parameters of TFET viz. threshold voltage ( $V_T$ ), subthreshold slope (SS),  $I_{ON}$ ,  $I_{OFF}$ , drain induced barrier lowering (DIBL). These are some of the major parameters on the basis of which we are going to compare the different structurally and geometrically modified versions of the basic TFET structure in the upcoming chapters.

#### **1.5.1 Threshold Voltage**

The lowest gate to source voltage necessary to start current conduction via a FET's channel is known as  $V_T$  or the threshold voltage. In the context of traditional MOS, it refers to the potential necessary at gate terminal for creation of inversion region in the channel, thus creating a conduit for the movement of charge carriers among the drain and source. However, in the context of TFETs, it can be seen as the lowest gate source voltage necessary to bring the channel's conduction band and source's valence band into alignment so that band to band (BTB) tunnelling among them can begin. The threshold voltage for a TFET is temperature independent.

#### 1.5.2 Subthreshold Slope

The quantity of gate potential needed to cause a one decade variation in the drain current in the area below the threshold is known as the subthreshold slope[30]. It can be expressed mathematically as ratio of the variation in the gate's voltage to the variation in the logarithm of current at the drain, given as

$$S = \frac{dV_g}{d(\log I_d)} \text{ mV/dec}$$

(1.1)

The sub-threshold slope for standard MOS devices is determined to be entirely free of the gate to source potential & is provided as[31]

$$S_{MOSFET} = \frac{kT}{q} \ln 10 \left( 1 + \frac{C_D}{C_{ox}} \right)$$

(1.2)

where kT/q is the thermal limitation of MOSFET devices, preventing them from having a minimum SS of 60mV/dec at T=300K (ambient temperature). C<sub>D</sub> and C<sub>ox</sub> are the device's

depletion and oxide capacitances. TFET devices, however, rely on the barrier of tunnelling near the junction of source & channel rather than temperature barrier. For a TFET, the subthreshold slope is provided below [32]

$$S_{TFET} = \frac{V_{GS}^2}{2V_{GS} + B_{kane} W_g^{3/2} / D}$$

(1.3)

Consequently, in contrast to MOSFETs, TFETs have a subthreshold slope that is mostly influenced by the gate voltage and very somewhat by the bandgap at the source-channel junction (tunnelling junction). So, it is evident that utilising low  $V_{GS}$  can result in a TFET with a sub 60mV/dec S value.

#### 1.5.3 ON State Current

The ON state current ( $I_{ON}$ ) of a TFET is a critical performance evaluation parameter that needs to be as large as feasible for optimal performance. This is nothing but the drain - source current ( $I_{DS}$ ) that passes via the apparatus when the voltage between the gate and the source is higher than  $V_{T}$ . More concisely, it's the drain-source current, while the device is turned ON. At the source-channel junction, BTBT or Band-to-Band-Tunnelling of the electrons is the main reason for  $I_{ON}$ .

## 1.5.4 OFF State Current

I<sub>OFF</sub> is used to represent it. It can be described as the amount of current that flows between the source and drain when the device is deemed off or when the gate to source voltage is less than the threshold voltage. I<sub>OFF</sub> should ideally be moving towards zero, but in reality, because of a small subthreshold slope, it has a non-zero value. Because of several leakage processes and the ambipolar behaviour of TFETs, I<sub>OFF</sub> has a small value, however it needs to be kept as little as possible for optimal performance.

Another crucial performance metric is the ratio of ON current to the OFF current.  $I_{ON}/I_{OFF}$  ought to be as large as feasible for the TFET to operate as efficiently as possible.

## 1.5.5 Drain Induced Barrier Lowering (DIBL)

The reduction in the V<sub>Th</sub> or threshold voltage with elevated drain biases is caused by a sort of short channel effect called DIBL or Drain Induced Barrier Lowering. For the TFET to function as well as feasible, it must be as tiny as possible. The ON current depends heavily on the drain

voltage instead of gate voltage due to the high value of DIBL. It renders the device unusable and destroys its gate controllability. Its mathematical definition is the ratio of the difference between the highest and lowest drain voltages and the difference between the threshold voltages recorded at those values[33], and is represented as shown below,

$$DIBL = -\frac{v_{Th}^{high} - v_{Th}^{low}}{v_D^{high} - v_D^{low}}$$

(1.4)

The negative sign before the formula ensures that the value of the DIBL is always positive since the threshold voltage,  $V_T$  recorded at higher drain voltage is invariably lesser than that recorded at lower drain voltage. Drain Induced Barrier Lowering or DIBL is measured in mV/V, & it must be, as minimal as feasible.

#### 1.6 Analog or RF performance metrics of TFET

For very low power transistors to work with today's high-speed CPUs, they need to have fast switching rates. TFET efficiency is determined by several key high-frequency performance factors, including transconductance ( $g_m$ ), cut-off frequency ( $f_T$ ), gain bandwidth product (GBP), and transit time( $\tau$ )[34].

#### **1.6.1 Transconductance**

Assuming the drain to source voltage remains constant, the transconductance (gm) of a TFET is determined by the rate at which the drain current changes to change the gate to source voltage. It is provided mathematically as,

$$g_m = \frac{\partial I_{DS}}{\partial V_{GS}}\Big|_{V_{DS}=constant}$$

(1.5)

It is graphically represented as the TFET's slope of transfer characteristic.

#### **1.6.2 Cut-off Frequency**

For analog/RF operations, one of the most significant performance characteristics is the cutoff frequency ( $f_T$ ). It is described to be the frequency for which the short circuit current gain for small signals decreases to unity value.[34]. It is expressed as

$$f_T = \frac{g_m}{2\pi (c_{gs} + c_{gd})}$$

(1.6)

where the gate to drain capacitance is denoted by  $C_{gd}$  and the gate to source capacitance by  $C_{gs}$ . For optimal performance, the value cut-off frequency must be high.

#### 1.6.3 GBP or the Gain Bandwidth Product

The next crucial RF performance characteristic is GBP, which is the trade-off between the device's gain & bandwidth. It oversees figuring out a circuit's selectivity. Typically, GBP or Gain Bandwidth Product is used to assess the device's efficiency at a DC gain value of 10[35] and is expressed mathematically as,

$$GBP = \frac{g_m}{20\pi C_{gd}} \tag{1.7}$$

#### 1.6.4 Transit Time

The transit time, represented by  $\tau$ , is another crucial factor that impacts the RF/ analog performance of TFET device. The transit time indicates how long it takes for the charge carriers to go from the device's source to the drain [34]. It serves as a gauge for the device's speed. It can be expressed mathematically as proportional to the reciprocal of the cut-off frequency,

$$\tau = \frac{1}{2\pi f_T} \tag{1.8}$$

#### 1.7 TCAD Simulation Tools used in this research

TCAD or Technology Computer Aided Design, is a useful technique for cutting plan costs, improving the effectiveness of device design, and creating innovative and improved device designs. In this research two very efficient and widely used TCAD tools are utilized, viz Cogenda Visual TCAD tool and Silvaco ATLAS TCAD tool.

#### 1.7.1 Cogenda Visual TCAD tool

Cogenda Visual TCAD tool is a comprehensive software solution designed to streamline the process of Technology Computer-Aided Design (TCAD) in semiconductor industries. Offering a user-friendly interface and powerful simulation capabilities, Cogenda Visual TCAD facilitates precise modelling and analysis of semiconductor devices and processes. Its intuitive visualizations enable engineers to efficiently explore device behaviour, predict performance, and optimize designs, ultimately accelerating product development cycles and enhancing overall efficiency in semiconductor research and development. The upcoming chapters will elaborate more on how the tool has been fully utilised for the present research.

#### 1.7.2 Silvaco ATLAS TCAD tool

Silvaco's ATLAS TCAD tool is a cutting-edge software solution revolutionizing semiconductor device simulation. Renowned for its versatility and accuracy, ATLAS empowers semiconductor engineers to delve into the intricate physics governing device behavior with unparalleled depth. Its comprehensive suite of features enables precise modeling and analysis of various semiconductor devices, from transistors to solar cells, facilitating exploration across a broad spectrum of applications. ATLAS's robust simulation engine, coupled with its user-friendly interface, empowers researchers and engineers to predict device performance, optimize designs, and accelerate innovation cycles in semiconductor technology. By providing a powerful platform for in-depth analysis and exploration, Silvaco's ATLAS TCAD tool continues to drive advancements at the forefront of semiconductor research and development. This tool is also used extensively in our research as will be clarified in the upcoming chapters.

#### 1.8 Outline of the Thesis

This section describes the outline of the thesis in detail. The present Thesis work is an illustration of the research carried out for designing and optimizing a modified Tunnel Field Effect Transistor for use in low power VLSI circuits. The thesis is divided into seven chapters. The chapter-1 is the Introduction, which firstly introduces VLSI technology as an engineering stream and its advent and evolution since the discovery of transistor in 1947. It also explains the motivation behind opting for TFET as our device for research. Then it demonstrates the different performance parameters of TFET on the basis of which the optimization of our proposed research is done. Finally, It introduces the two most important EDA tools Cogenda Visual TCAD and Silvaco ATLAS used extensively in the research. Next chapter-2 is Literature Survey, which illustrates most of the contemporary TFET architectures introduced by researchers till date, their detailed structures, dimensions etc. It also compares the structures for the merits and shortcomings through a tabular representation. The chapter-3 is illustration of our first major breakthrough, the design and optimization of a device called n channel JL DG TFET with p+ type SiGe pocket near the source region of channel. It demonstrates how the device is having much superior performance compared to the existing devices of similar dimensions. Next chapter-4 is on the design of an inverter circuit using both n-JL DG TFET and p-JL DG TFET. It explains the implementation of p JL DG TFET along with the fabrication steps. Finally, it compares and plots the performance of the implemented inverter which proves to be a worthy replacement for CMOS inverters for very low power circuits. Next chapter-5 illustrates our new novel design, Asymmetric double gate P-I-N Tunnel FET. It describes the dimensions and structure of Asymmetric double gate P-I-N TFET. Then it summarises the device characteristics and interprets the findings. Chapter-6 focuses on the application perspectives of the proposed JL DG TFET and illustrates the implementation of two major digital circuits using the JL DG TFET, viz. the transmission gate and the 2:1 Multiplexer (MUX). Finally, Chapter-7 concludes our research with the summary of major findings and future scopes of further research.

# CHAPTER 2 LITERATURE REVIEW

Although TFET devices have a lot of merits to be utilised as worthy replacement of MOSFETs from low power VLSI circuits, they have a few disadvantages as well, the two main ones are very modest ON state current value and ambipolar conduction, or conduction in the reverse direction when switched OFF. To lessen these shortcomings, researchers have suggested a number of altered topologies for the traditional TFET devices. In this section we will illustrate a few of the major strategies found in the literature for generation of highly efficient TFET circuits and devices.

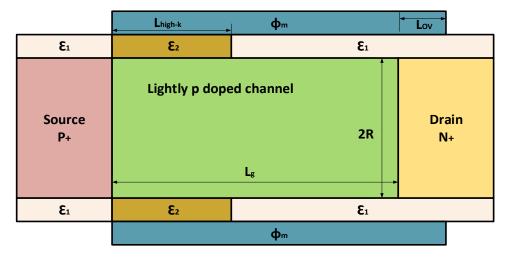

# 2.1 Gate-Drain Overlap Hetero-Dielectric Gate-All-Around TFET (GDO HD GAA TFET)

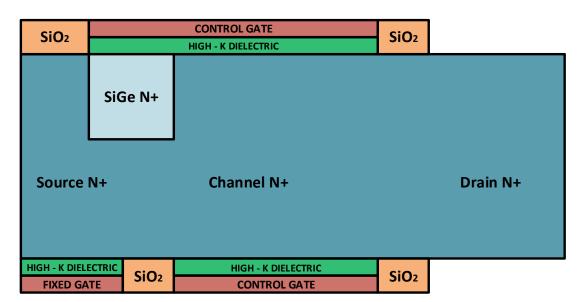

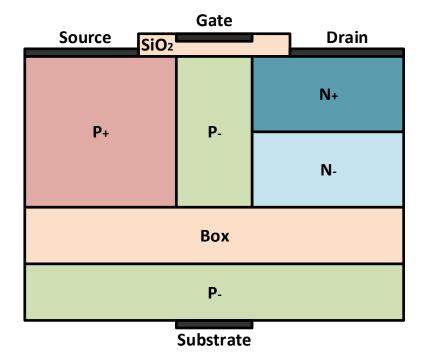

When building and modifying the fundamental Tunnel FET structure, researchers concentrated on different structural and geometrical adjustments as well as the application of more recent and cutting-edge materials. Here, several of these structures are categorised and their dimensional characteristics are briefly explained. A small number of them concentrated on using low band gap material as the source and a heterogenous dielectric structures for the gate dielectrics that combined low and high k materials. Madan & Chaujar [27] proposed GDO HD GAA TFET, a TFET having gate to drain overlapping, gate dielectric of heterogenous materials, and gate wrapped all-round the channel structure (Fig. 2.1). While the hetero material used for the gate dielectric improves the I<sub>ON</sub>, the gate-drain overlap inhibits the ambipolar nature of current. Additionally, the gate's surrounding structure enhances its ability to control the tunnel current. Dimensions of the device being given as channel length, L<sub>g</sub>=50nm, R=10nm, T<sub>ox</sub>=2nm, Gate metal  $\Phi$ =4.3eV,  $\varepsilon_2$ =21(HfO<sub>2</sub>, High k),  $\varepsilon_1$ =3.9(SiO<sub>2</sub>, Lower-k), highk dielectric length L<sub>high-k</sub>=10nm & Source of type p+, Channel of type p-, Drain of type n+ doping of 1x 10<sup>20</sup> cm<sup>-3</sup>, 1x 10<sup>16</sup> cm<sup>-3</sup> respectively.

Fig.2.1 Cross-section of GDO HD GAA TFET

#### 2.2 Low Doping Heterogenous Gate Dielectric TFET (LD-HTFET)

Wang et al. [22] paper proposed the LD-HTFET (Fig. 2.2), a Carbon Nano Tube-based TFET with heterogeneous gate dielectric and low doping. The authors also compared the LD-HTFET's performance to that of the HK-TFET, a CNT or Carbon Nano Tube based TFET having high k material for the dielectric at gate, & the HTFET, which is the only TFET with heterogeneous gate dielectric. When light doping and gate dielectric modulation are present, the device-level study of switching behaviours and HF figure of performance is conducted using the quantum kinetic model. It is discovered that the LD-HTFET has superior HF and switching figures. HSPICE circuit simulations revealed significant gains in the power delay product, delay energy, and static noise margin. The LD-HTFET has the following device dimensions: a 20 nm gate length, a 2 nm gate oxide thickness, a 20 nm source/drain expansion length, and a gate oxide with  $\varepsilon$  values of 16 and 3.9 for high and low k, respectively.

Fig.2.2 Cross-section of LD HTFET

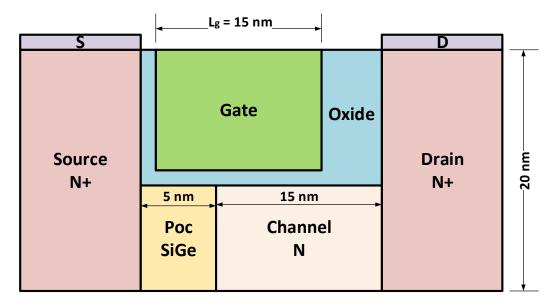

#### 2.3 Hetero Gate Dielectric, Nano Wire TFET with SiGe Source (SiGe S NW TFET)

In order to build analog circuits such as operational amplifiers, Patel et al.[34] presented the SiGe S NW TFET (Fig.2.3) with a hetero gate dielectric & source built of lower bandgap SiGe material. They also assessed the SiGe S NW TFET's performance in comparison to the conventional Si nanowire TFET. The constructed source's narrow bandgap SiGe and the usage of HfO<sub>2</sub> (with a higher value for k) as the gate-oxide near source to channel junction resulted in a SS of 6.54 mV/dec, which is much low compared to that of the traditional device's 36.24 mV/dec. An increase in transconductance brought about by an improvement in ON current(640 times than conventional TFET) led to improved RF/analog performance. While the device's diameter changes, the channel length varies very little and has little effect on SS. The device measures 20 nm in length, 20 nm in diameter for the nanowire, 2 nm for  $t_{ox}$ , 1 x 10<sup>17</sup> cm<sup>-3</sup> for substrate doping, 1 x 10<sup>18</sup> cm<sup>-3</sup> for drain doping, and 1 x 10<sup>20</sup> cm<sup>-3</sup> for source doping.

Fig2.3 Cross-section of SiGe S NW TFET

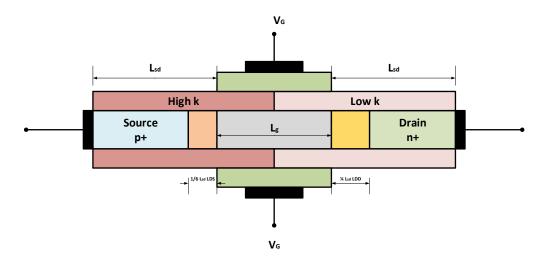

# 2.4 Heterogenous Gate Dielectric Double-Gate-Metal Work-Function TFET (HGDDW TFET)

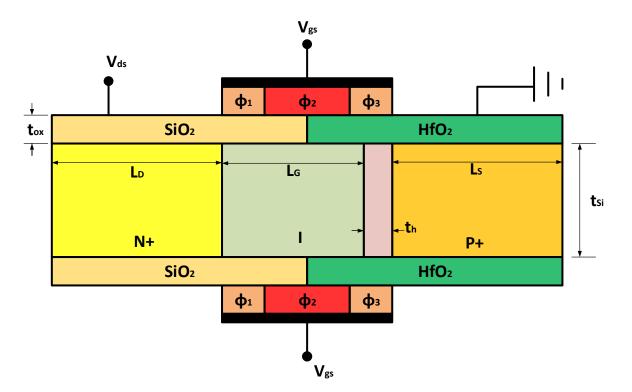

Few engineers combined several gate metal combinations with different work functions. For instance, a heterogenous gate-dielectric based double-gate-metal work function transistor (HGDDW TFET) that reduces ambipolar-behaviour & improves RF performance figure was proposed by Raad et al.[36]. Three gate metals with distinct work functions,  $\Phi_1=\Phi_3=4.0$ eV and  $\Phi_2=4.6$ eV are present in its structure (Fig. 2.4). On the drain side, low  $\Phi$  increases ON current and decreases ambipolarity. High k(HfO<sub>2</sub>) towards the source end aids in improving drive/ON current by decreasing the width of tunnelling at source-channel interface, lower k SiO<sub>2</sub> is

employed at the drain end to decrease the ambipolar leakage & improve RF figure of performance.  $L_D=L_S=100$ nm,  $L_G=50$ nm are the device dimensions that is used. It comprises a high-density layer with t<sub>h</sub>=2nm, t<sub>ox</sub>=2nm, t<sub>Si</sub>=10nm, lengths of  $\Phi_1$  and  $\Phi_3=10$ nm, and drain/source doping of  $1 \times 10^{20}$  cm<sup>-3</sup>.

Fig.2.4 Cross section of HGD DW TFET

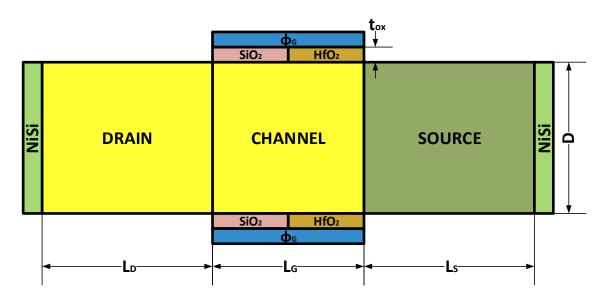

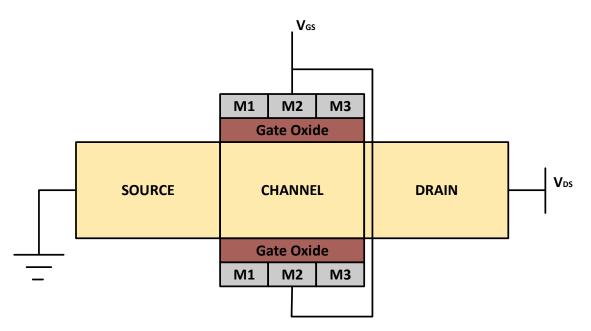

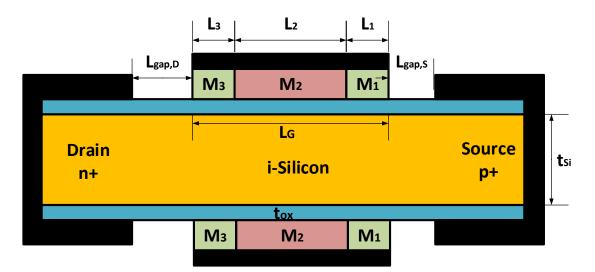

#### 2.5 Triple-Metal Gate-All-Around TFET (TMGAA TFET)

A Si nano wire-based Triple-Metal-Gate-All-Around TFET (TM GAA TFET) was proposed by Bagga & Dasgupta [37] (Fig. 2.5). The gate, which is wrapped around the structure and made of three different metals, bends the energy band close to the source to boost driving current and helps to form a barrier to prevent backward tunnelling current from draining. Kane's model and Poisson's equation dependent analytical approach are used to verify the device. Poisson's Equation in cylindrical coordinates can be expressed as follows:

$$\frac{1}{r}\frac{\partial}{\partial r}\left(r\frac{\partial\varphi(r,z)}{\partial r}\right) + \frac{\partial^2\varphi(r,z)}{\partial z^2} = \frac{-qN_C}{\varepsilon_{Si}} \quad \text{for } (0 \le z \le L, \ 0 \le r \le R)$$

(2.1)

The device's dimensions are as follows: the channel's length, L=L1+L2+L3=60 nm; the metal M1 and M2 lengths, L1=10nm and L2=30 nm, M3 length L3 is 20; the work-functions,  $\Phi_{M1}$ =4.4 eV,  $\Phi_{M2}$ =4.8 eV,  $\Phi_{M3}$ =4.6 eV; the gate-oxide thickness, t<sub>ox</sub> is 2, & the Silicon nanowire radius, R is 10 nm.

Fig.2.5 Cross-section of Si nanowire TM GAA TFET

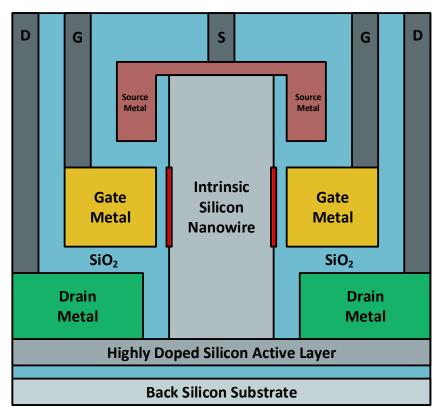

## 2.6 U-Gate Hetero-Junction Vertical Tunnelling FET (U HJ VTFET)