# DESIGN AND OPTIMIZATION OF APPROXIMATE LOW POWER MULTIPLIER FOR DSP APPLICATION

Thesis Submitted for the Award of the Degree of

# **DOCTOR OF PHILOSOPHY**

in

**Electrical and Electronics Department**

By

SHEETAL NAGAR

**Registration Number: 41900673**

| Supervised By                  | Co-Supervised by              | Co-Supervised by       |

|--------------------------------|-------------------------------|------------------------|

| Dr. Shanky Saxena              | <b>Dr. Govind Singh Patel</b> | Dr. Seema Nayak        |

| <b>EE(Assistant Professor)</b> | EC(HOD)                       | ECE(HOD)               |

| LPU, Punjab                    | SIOTCOE, YADRAV,MH            | IIMTCOE, Greater Noida |

# LOVELY PROFESSIONAL UNIVERSITY, PUNJAB 2025

# **DECLARATION**

I, hereby declared that the presented work in the thesis entitled "Design and optimization of Approximate low Power multiplier for DSP Applications" in fulfillment of degree of Doctor of Philosophy (PhD.) is outcome of research work carried out by me under the supervision, Dr. Shanky Saxena working as Assistant Professor, in the Department of Electrical and Electronics of Lovely Professional University, Punjab, India. In keeping with general practice of reporting scientific observations, due acknowledgement have been made whenever work described here has been based on findings of other investigator. This work has not been submitted in part or full to any other University or Institute for the award of any degree.

(Signature of Scholar)

Name of the scholar: Sheetal Nagar

Registration No.: 41900673

Department/school: Electronics and Electrical

Lovely Professional University,

Punjab, India

# Certificate

This is to certify that **Ms. Sheetal Nagar** has completed the PhD. Electronics and Communication Engineering titled, "**Design and optimization of Approximate low Power multiplier for DSP Applications**" under my guidance and supervision. To the best of my knowledge, the present work is the result of his original investigation and study. No part of this thesis work has ever been submitted for any degree.

This thesis is fit for the submission for the partial fulfillment of the condition for the awardof degree of Ph.D. in Electronics and Communication Engineering.

Signature of Supervisor

Dr. Shanky Saxena

Associate Professor

School of Electrical Engineering

Lovely Professional University Punjab

Signature of Co-Supervisor

Dr. Govind Singh Patel

Professor

Department Of ECE SITCOE,

YADRAV,ICHALKARANJI, MH

Dr. Seema Nayak

Professor

Department of ECE,

IIMT College of Engineering Greater Noida

# **Abstract**

In the modern era, the increasing demand for lightweight, low-power, and high-performance electronic devices has led to the development of advanced tools and techniques for designing energy-efficient multipliers. One such technique is compressor-based multiplication, which utilizes compression methods to reduce the number of partial products (PP) generated during the multiplication process, thereby decreasing the circuit's power consumption. This work focuses on the design of a compressor-based low-power multiplier, including its fundamental principles, implementation strategies, and potential applications. Furthermore, it explores the use of approximate computing techniques to further minimize power consumption in the compressor-based multiplier design. As a result, compressor-based low-power multiplication emerges as a promising approach for developing high-performance and energy-efficient multipliers, particularly suitable for battery-powered devices such as smartphones and light weight gadgets.

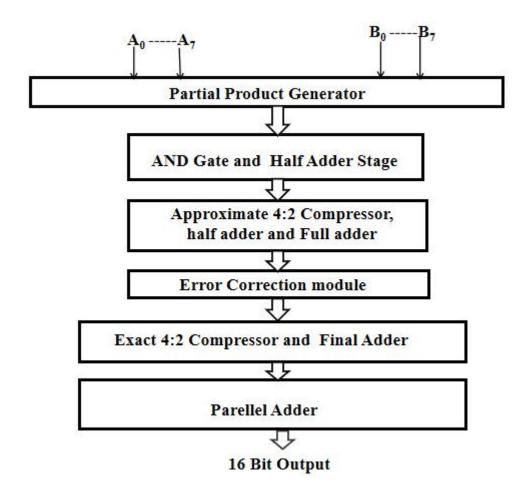

The proposed design incorporates a compressor-based Dadda multiplier to enhance key performance parameters. Both exact and inexact compressors are utilized to compress the partial product stages. The multiplier architecture integrates Half Adders (HA), Full Adders (FA), and both accurate and 4:2 inexact compressors. This architecture is implemented in an 8×8 Dadda multiplier to optimize power-related parameters. The work achieves notable reductions in delay and area, making these compressor-based designs especially suitable for error-tolerant or error-resilient applications. In today's fast-paced environment, which demands high-speed and compact solutions—particularly in wearable technologies—such multipliers are increasingly relevant. In this work, the design is also implemented for image processing applications. The multiplier is designed using Verilog, and the implementation tools include Cadence with 45 nm CMOS technology and Xilinx ISE. The proposed multiplier design demonstrates improved performance and efficiency, as visually summarized in the graphical abstract

A new era of the light weight, wearable which consume low power are on the top most demand of the society. Multiplication is the basic unit of the digital world. Consumption of low power in Multipliers is the highly popular in the research field. Inexact Computing is highly used methodology for the low power consumption in low power multipliers. This

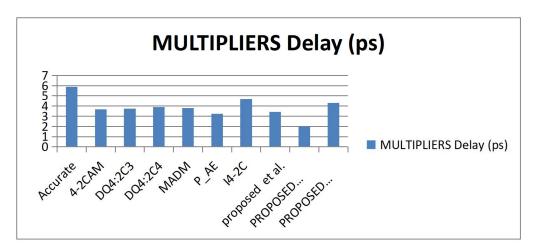

Incredible fast technique most probable used the error tolerant applications like Video, Image Processing, FIR filters, Speech signal analysis and DSP (Digital signal processing) applications. The objective of this research is to explore the impact of inaccurate compressor designs on power utilization area in cell count and delay. The Proposed designs accoutered using 45 nm CMOS technology in Cadence. Through extensive experimentation and analysis, it was found that the proposed designs led to significant improvements in power consumption, with a reduction of 46%. Moreover, the delay was reduced by 65%, and there was a substantial decrease in area by 80.35% compared to accurate multiplier implementations. These findings underscore the potential of inaccurate compressor designs in enhancing the efficiency and performance of low-power multiplier Area and Power of proposed architecture had been obtained using the synthesis tool Xilinx Vivado using Verilog programming. Results of the work show the improvement in terms of Area and Power using cadence.

In the last overall conclusions from the present study has been presented along with the futurescope available with this study.

# Acknowledgement

I extend my heartfelt gratitude to the individuals who have contributed, directly or indirectly, to the completion of this thesis.

First and foremost, I am deeply thankful to my esteemed supervisors, Dr. Shanky Saxena, Dr. Govind Singh Patel, and Dr. Seema Nayak, for their invaluable advice, guidance, and unwavering support throughout my research journey. Their mentor-ship equipped me with the necessary skills for independent inquiry, fostering an environment where I could explore my ideas while receiving constructive feedback, ensuring the professional execution and timely completion of my work.

I am indebted to Dr. Shobit Saxena, Dr. Abhishek, Dr. Aruna Pathak, and Dr. P. Ramesh for their continuous technical assistance, which significantly enriched the quality of my research. Additionally, I express my gratitude to Dr. P. Ramesh for indirectly supporting my work through insightful research articles that served as constant sources of inspiration and guidance.

Attending various conferences and workshops during my PhD journey has been invaluable, and I am immensely grateful to all those with whom I collaborated and who provided invaluable feedback and constructive criticism.

Special thanks are due to Dr. Mayank Aggrwal, Dinesh Yadav, and Dr. Taslima Ahmad for their unwavering motivation and endless emotional support, which played a pivotal role in sustaining my enthusiasm and determination.

Finally, I extend my deepest appreciation to my friends and family for their unwavering love and support. My parents, Mr. Mahavir Singh Nagar and Mrs. Sheelam Nagar, have been pillars of strength, always encouraging me to strive for excellence. My husband, Mr. Jitendra Verma, and my daughter, Aashvi Verma, have been unwavering in their support, providing encouragement and understanding throughout this journey. Their unwavering support has been instrumental in my accomplishments thus far. The significance of emotional support in completing a PhD cannot be overstated, and I am truly grateful.

| <b>Table of Contents</b>                        |      |  |

|-------------------------------------------------|------|--|

| Title Page                                      | i    |  |

| Declaration                                     | ii   |  |

| Certificate                                     | iii  |  |

| Abstract                                        | iv   |  |

| Acknowledgment                                  | vi   |  |

| Table of Contents                               | vii  |  |

| List of Figure                                  | xi   |  |

| List of Table                                   | xiii |  |

| List of Abbreviations                           | xiv  |  |

| CHAPTER 1: INTRODUCTION                         | 1    |  |

| 1.1 Motivation                                  | 1    |  |

| 1.2 Power Optimization                          | 5    |  |

| 1.3 Architecture of Low Power Multiplier Design | 7    |  |

| 1.3.1 Architecture of multipliers               | 10   |  |

| 1.3.2 Wallace Tree Multiplier                   | 11   |  |

| 1.3.3 Conventional Wallace tree Multiplier:     | 12   |  |

| 1.3.4 Modified Wallace tree Multiplier          | 12   |  |

| 1.3.5 Wallace Booth Multiplier                  | 13   |  |

| 1.3.6 Dadda Multiplier                          | 14   |  |

| 1.4 Integrated Circuit Multiplication           | 15   |  |

| 1.5 Design Consideration of Digital Circuit     | 16   |  |

| 1.6 Power Vs Energy                                             | 16 |

|-----------------------------------------------------------------|----|

| 1.7 Delay and Power in multipliers                              | 17 |

| 1.8 Overview of Monograph                                       | 19 |

| 1.9 Organization of the thesis                                  | 22 |

| CHAPTER 2. Literature Review: Multipliers and Power Dissipation |    |

| 2.1 Introduction to Multipliers                                 | 24 |

| 2.1.1 Structure of Multiplier                                   | 24 |

| 2.1.2 Generation of Partial Product                             | 25 |

| 2.1.3 Reduction of Partial Product                              | 26 |

| 2.1.4 Array type Reduction                                      | 27 |

| 2.1.5 Wallace tree Reduction of PP                              | 28 |

| 2.1.6 Partial Product Reduction/Generation                      | 30 |

| 2.1.7 Final Addition of Multiplier                              | 31 |

| 2.1.8 Summary                                                   | 35 |

| 2.2 Introduction to CMOS Power                                  | 35 |

| 2.2.1 Basics of Static and Dynamic Power                        | 35 |

| 2.2.2 Power Optimization Fundamentals                           | 36 |

| 2.3 Literature Review to identify Gap                           | 37 |

| 2.4 Literature Gap                                              | 44 |

| 2.5 Summary                                                     | 45 |

| CHAPTER 3.Optimization Techniques and Proposed Methodology      | 48 |

| 3.1 Introduction                                                | 48 |

| 3.2 Operating Parameters for categorization                     | 49 |

| 3.3 Algorithm and Methodology                                   | 51 |

| 3.3.1Accurate 4:2 Compressor                                     | 51 |

|------------------------------------------------------------------|----|

| 3.3.2 Approximate Compressor:                                    | 54 |

| 3.3.3 Structure of the 4-2 Compressor                            | 54 |

| 3.3.4 Truth Table for the 4-2 Compressor                         | 54 |

| 3.3.5 Compressor Adder                                           | 55 |

| 3.3.6 Implementation in Dadda Multiplier                         | 56 |

| 3.4 Power Optimization Techniques                                | 57 |

| 3.5 Error Correcting Module (ECM)                                | 59 |

| 3.6 Circuit Design Considerations                                | 60 |

| 3.7 Performance Analysis                                         | 60 |

| 3.8 Summary                                                      | 60 |

| CHAPTER 4. Proposed Design and Model                             | 62 |

| 4.1 Introduction                                                 | 62 |

| 4.2 Design and Architecture                                      | 62 |

| 4.3 Tools and Technologies Utilized                              | 64 |

| 4.4 The Proposed System                                          | 65 |

| 4.5 Approximate Compressor Based Multiplier                      | 66 |

| 4.6 Error-correcting module (ECM)                                | 68 |

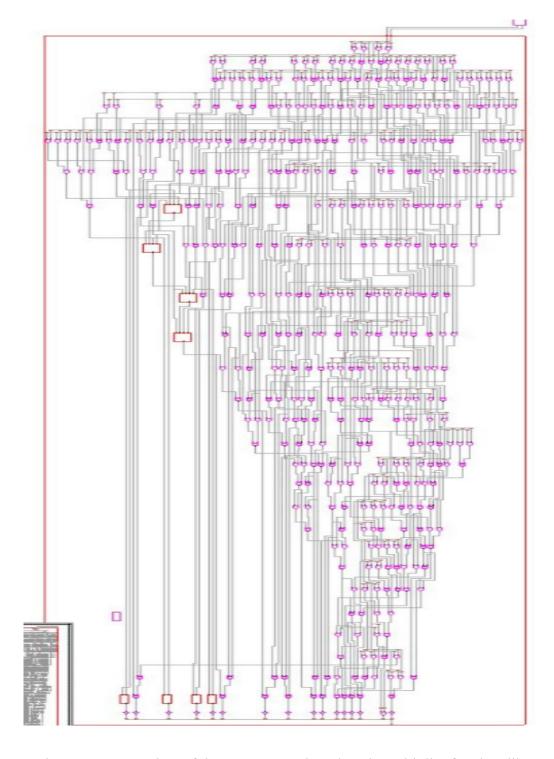

| 4.7 Design of the Proposed Architecture of Dadda Multiplier      | 69 |

| 4.8 Simulation Results and Discussion for parameter optimization | 72 |

| 4.9 Summary                                                      | 74 |

| CHAPTER 5. Experimental Results                                  | 75 |

| 5.1 Introduction                                                 | 75 |

| 5.2 Performance Analysis and Evaluation                          | 76 |

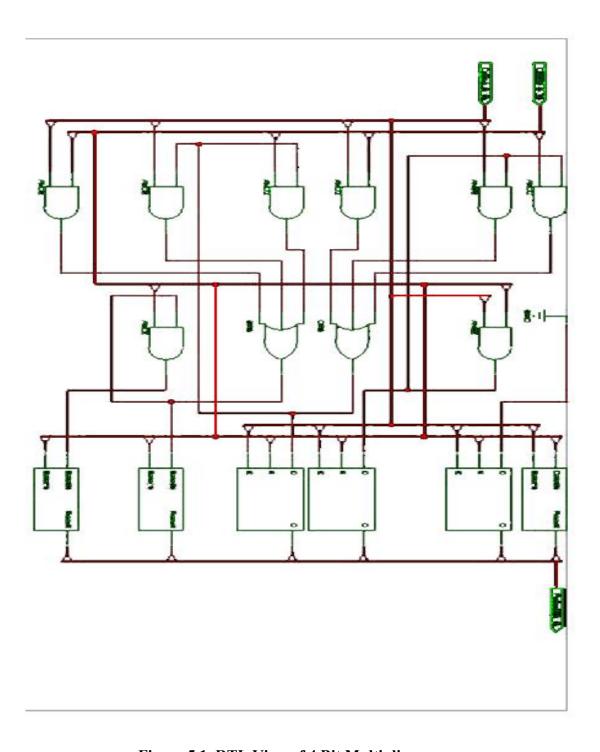

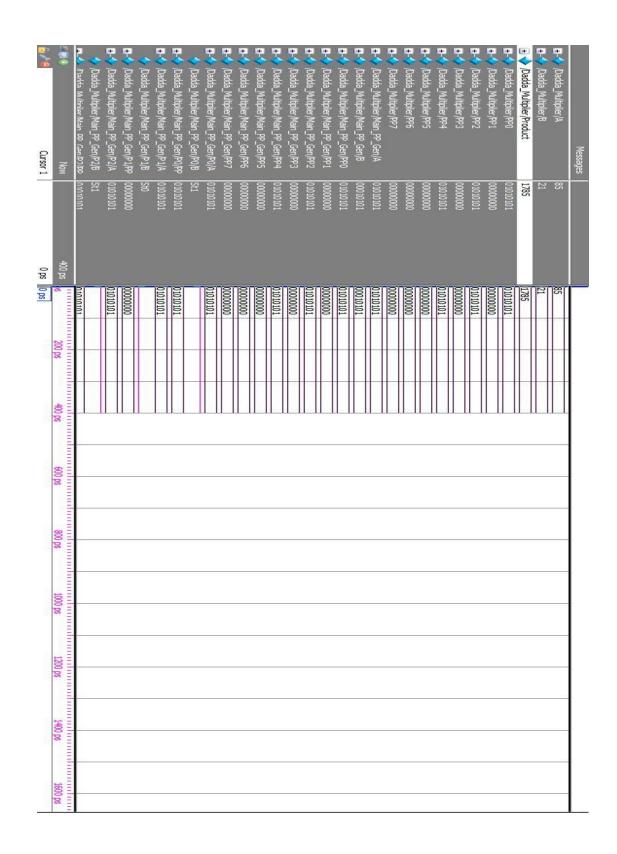

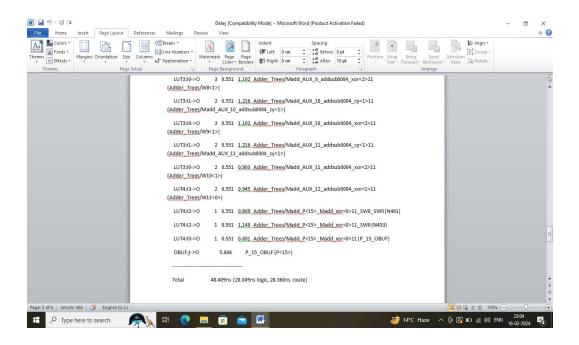

| 5.2.1 Performance Analysis Using Xilinx                          | 77 |

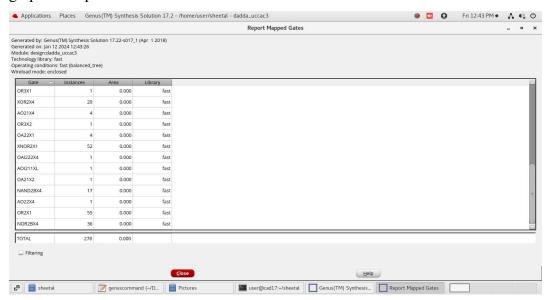

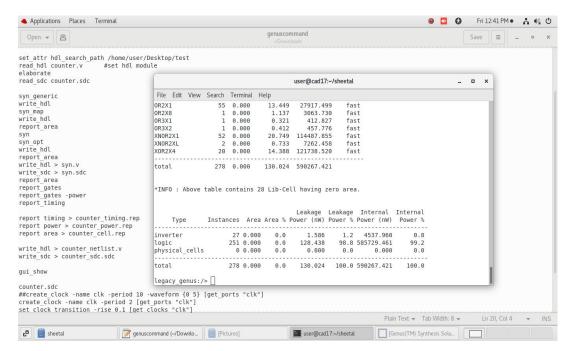

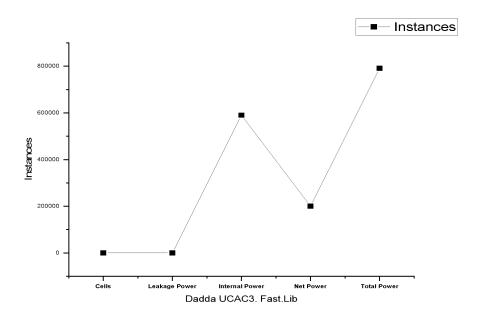

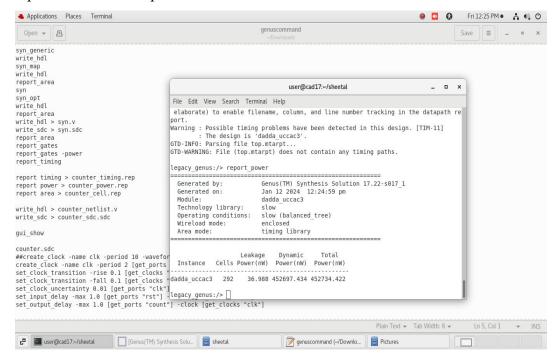

| 5.2.2 Performance Analysis Using Cadence 45nm for fast.lib       | 81 |

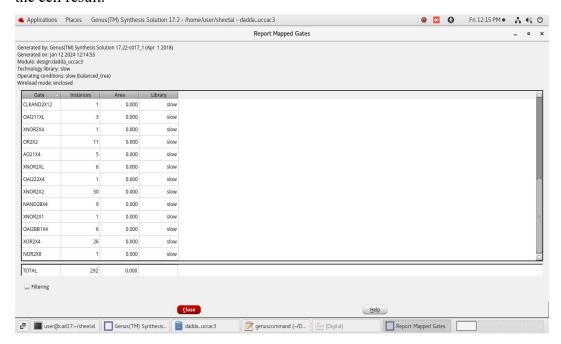

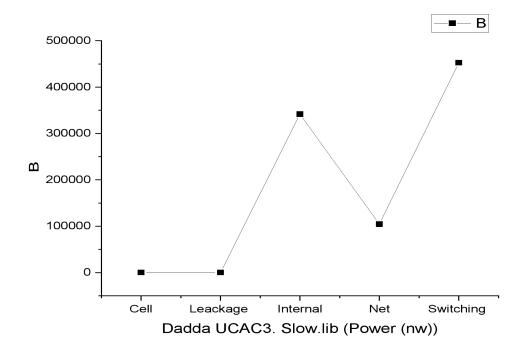

| 5.2.3 Performance Analysis Using Cadence 45nm for slow.lib       | 83 |

| 5.3 Parameter Result using cadence                               | 87 |

| 5.3.1 Parameter result Using Cadence 45nm for fast.lib           | 87 |

| 5.3.2 Parameter result Using Cadence 45nm for slow.lib           | 89 |

| 5. 4 Performance optimization                                    | 91 |

| 5.4.1 Analysis of the impact of optimization techniques on performance | 92  |

|------------------------------------------------------------------------|-----|

| 5.4.2 Effectiveness Of optimization on overall performance             | 93  |

| 5.5 Application in Image Processing                                    | 94  |

| 5.6 Achievements of Objectives and Report                              | 95  |

| 5.6.1 Parameter Report observation for booth LPM                       | 95  |

| 5.6.2 Parameter Report observation for booth LPM                       | 96  |

| 5.7 Conclusion                                                         | 97  |

| 6. Conclusion and Future Work                                          | 99  |

| 6.1 Introduction                                                       | 99  |

| 6.2 Research Contribution                                              | 100 |

| 6.3 Future Work                                                        | 102 |

| REFERENCES                                                             |     |

| LIST OF PUBLICATION                                                    |     |

# LIST OF FIGURE

| Figure No. | Title of Figure                                            | Page No. |

|------------|------------------------------------------------------------|----------|

| Figure 1.1 | Wallace Tree Multiplier                                    | 12       |

| Figure 1.2 | Conventional Wallace Tree Multiplier                       | 12       |

| Figure 1.3 | Modified Wallace Tree Multiplier using in MAC Unit         | 13       |

| Figure 1.4 | Novel Wallace Booth Multiplier                             | 13       |

| Figure 1.5 | 4x4 Dadda Multiplier using RCA                             | 14       |

| Figure 2.1 | Digital multiplier flow                                    | 25       |

| Figure 2.2 | PP( Partial product) generation for 6*6 bit multiplication | 25       |

| Figure 2.3 | Illustrates the addition of partial products (PP)          | 27       |

| Figure 2.4 | Array to reduce PP (partial product)                       | 28       |

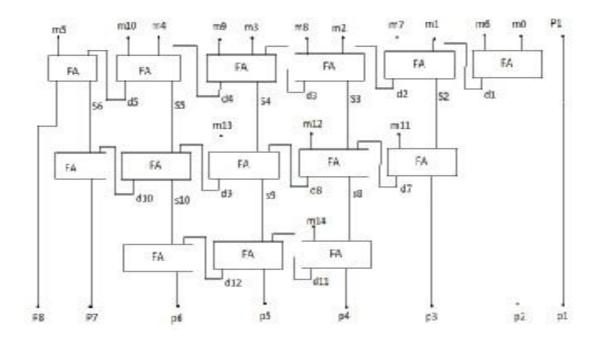

| Figure 2.5 | Illustrates the Wallace tree partial product reduction     | 29       |

| Figure 2.6 | Result, the size of the PPA cluster is reduced             | 31       |

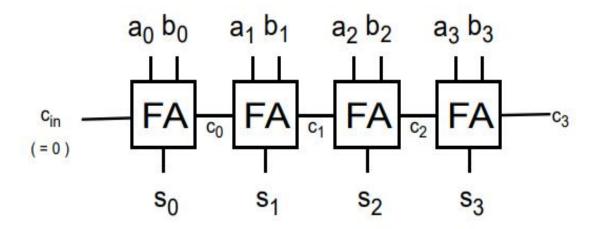

| Figure 2.7 | Block diagram of Ripple adder                              | 32       |

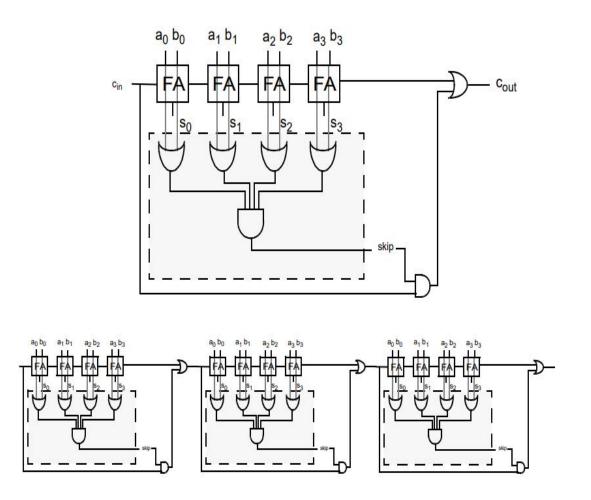

| Figure 2.8 | Illustrates Carry Skip Adders                              | 33       |

| Figure 2.9 | Illustrates the diagram of Carry Select Adders             | 35       |

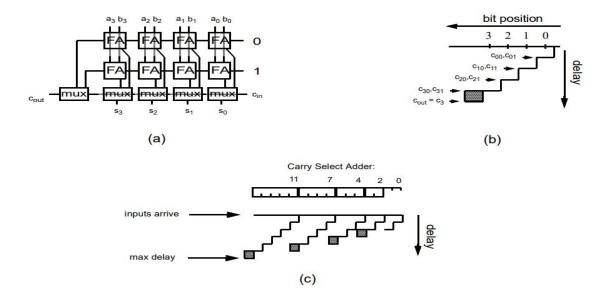

| Figure 3.1 | Process Flow Chart                                         | 51       |

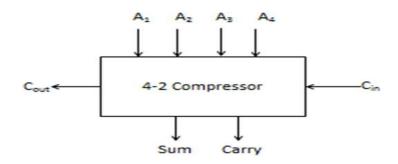

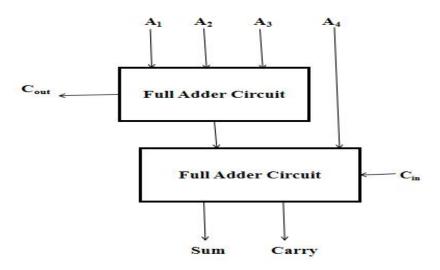

| Figure 3.2 | Basic Block diagram of 4:2 Compressor                      | 52       |

| Figure 3.3 | Basic Block diagram of 4:2 Compressor using FA             | 52       |

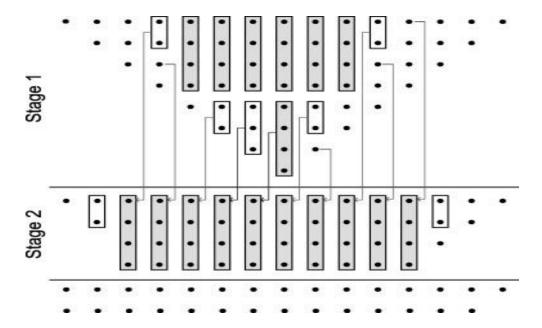

| Figure 3.4 | Design of Low power multiplier using Compressors           | 57       |

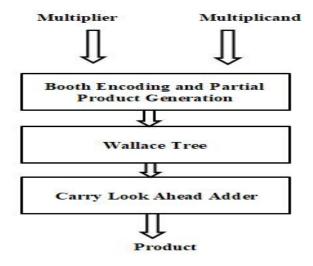

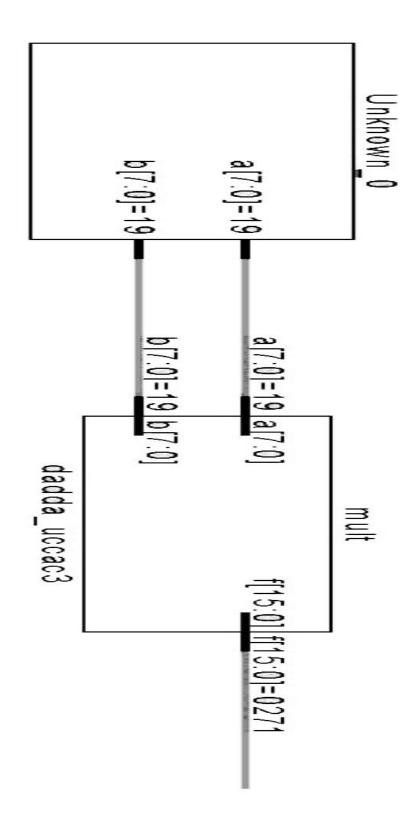

| Figure 4.1 | Dadda Multiplier flow diagram with Multiplier              | 63       |

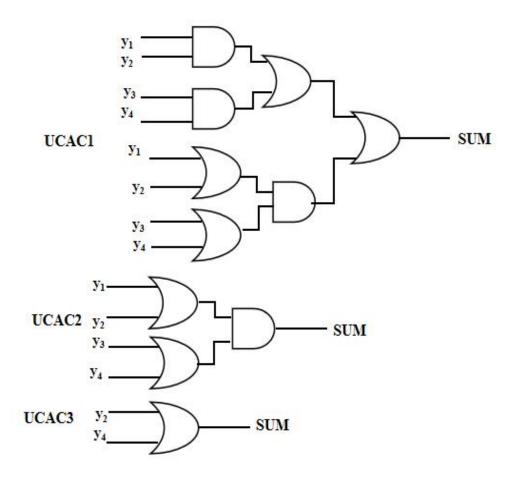

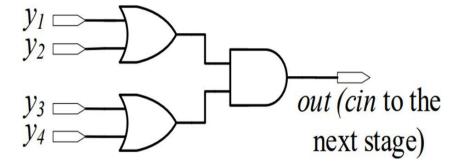

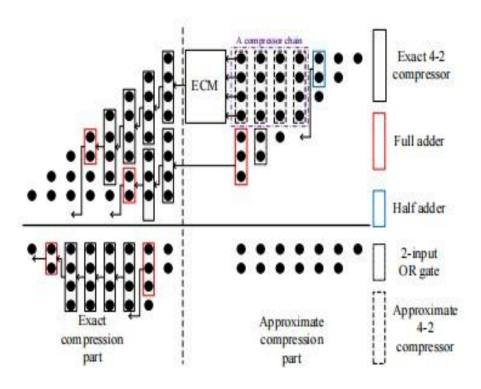

| Figure 4.2 | Basic diagrams of Implemented 4-2 compressors              | 67       |

| Figure 4.3 | Circuit of the Error Correcting Module                     | 68       |

| Figure 4.4 | Dadda Multiplier with the proposed design                  | 69       |

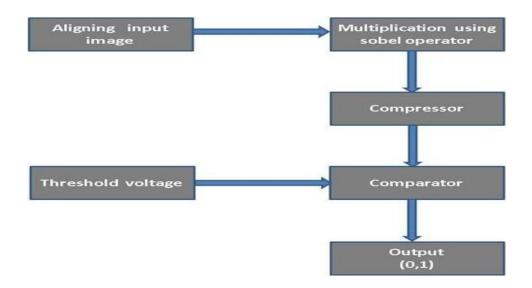

| Figure 4.5 | Sobel edge detection block diagram                         | 71       |

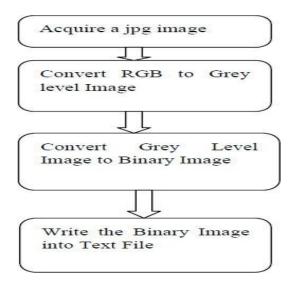

| Figure 4.6 | Process flow of RGB to binary image conversion             | 71       |

| Figure 5.1 | RTL View of 4 Bit Multiplier                               | 77       |

| Figure 5.2 | RTL View of 8 bit Multiplier                               | 78       |

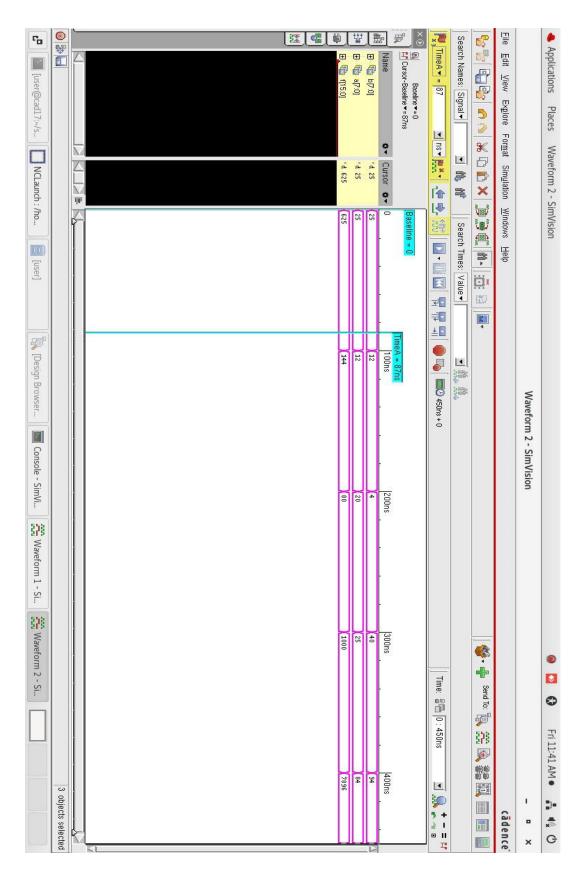

| Figure 5.3 | Waveform for 8 bit Dadda Multiplier                        | 79       |

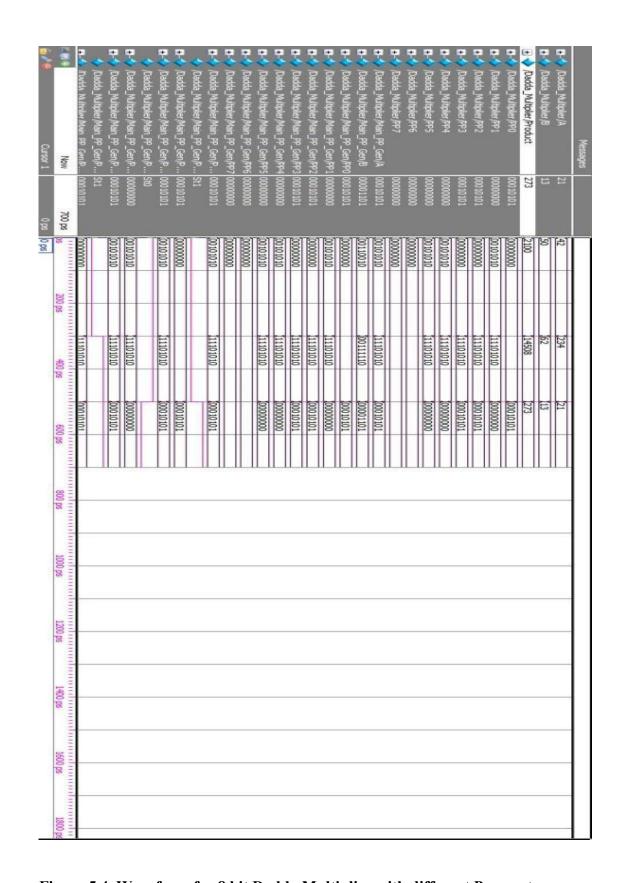

| Figure 5.4  | Waveform for 8 bit Dadda Multiplier with different Parameter   | 80 |

|-------------|----------------------------------------------------------------|----|

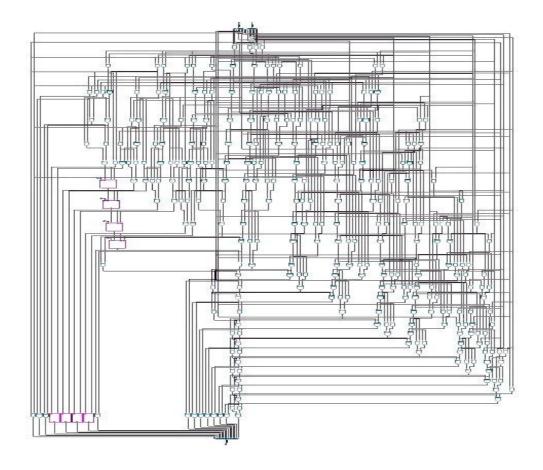

| Figure 5.5  | RTL View of the Compressor based 8 Bit Multiplier for fast.lib | 81 |

| Figure 5.6  | Simulation setup for 8*8 multiplier for fast.lib               | 82 |

| Figure 5.7  | RTL View of the Compressor based 8 Bit Multiplier for          | 83 |

|             | slow.lib                                                       |    |

| Figure 5.8  | Out Put Waveform of 8 bit low power Multiplier for             | 84 |

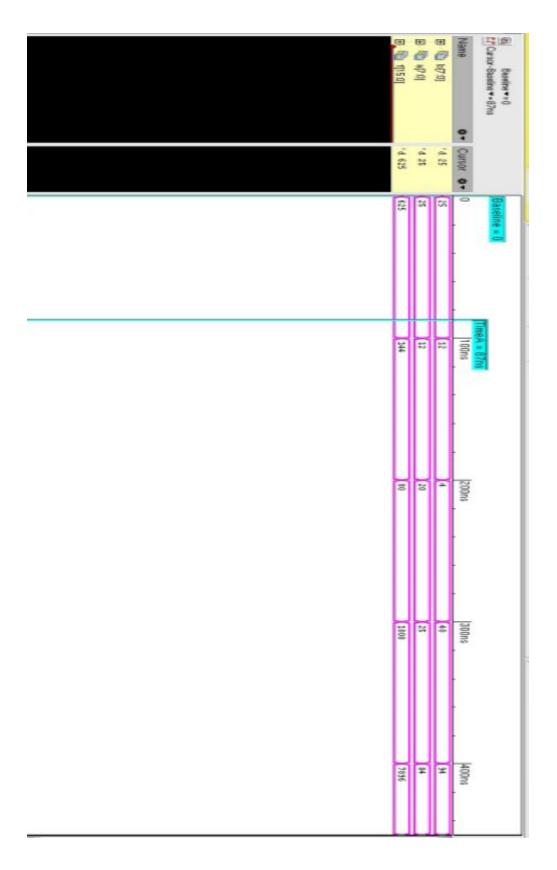

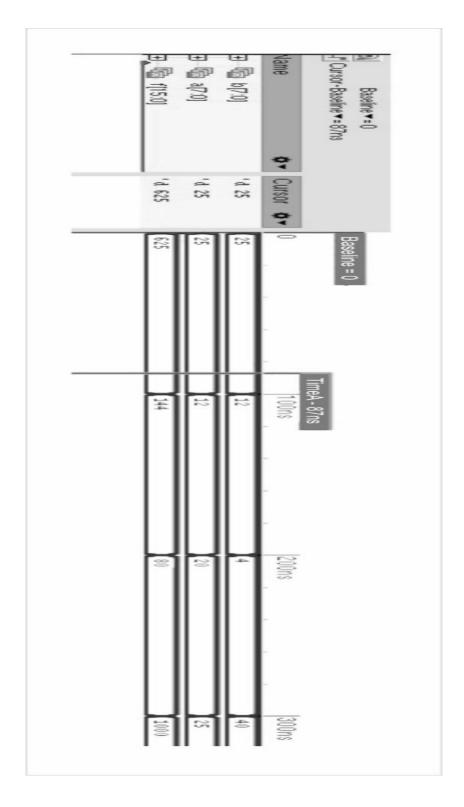

|             | slow.lib                                                       |    |

| Figure 5.9  | Out Put of 8 bit low power Multiplier with input and           | 85 |

|             | output                                                         |    |

| Figure 5.10 | Close view of 8 bit low power Multiplier with Input and        | 86 |

|             | Output                                                         |    |

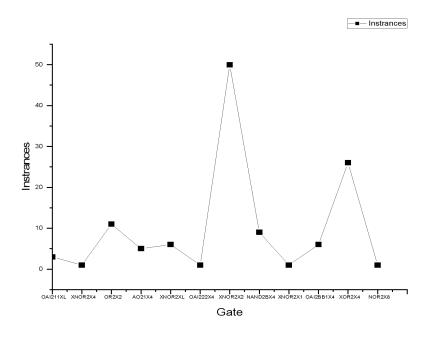

| Figure 5.11 | Cell Report for fast.lib                                       | 87 |

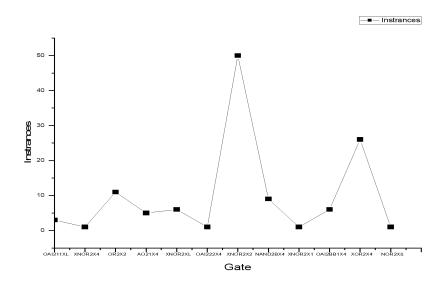

| Figure 5.12 | Graph for Cell Report for fast.lib                             | 87 |

| Figure 5.13 | Power Synthesis Report for fast.lib                            | 88 |

| Figure 5.14 | Graph for Power Synthesis Report for fast.lib                  | 88 |

| Figure 5.15 | Cell Report for slow.lib                                       | 89 |

| Figure 5.16 | Graph for Cell Report for slow.lib                             | 89 |

| Figure 5.17 | Power Synthesis Report for slow.lib                            | 90 |

| Figure 5.18 | Graph for Power Synthesis Report for slow.lib                  | 90 |

| Figure 5.19 | Graphical Representation of different multiplier Result        | 94 |

| Figure 5.20 | Output Image of Application of Proposed Multiplier             | 94 |

|             | Edges                                                          |    |

| Figure 5.21 | Output Image of Application of proposed Multiplier             | 95 |

|             | 1                                                              |    |

# LIST OF TABLE

| Table No. | Title of Table                                      | Page No. |

|-----------|-----------------------------------------------------|----------|

|           |                                                     |          |

| Table 2.1 | Booth Encoding                                      | 30       |

| Table 2.2 | Analysis of various Low Power multiplier Techniques | 39       |

| Table 3.1 | Comparison of 4:2 Compressors                       | 53       |

| Table 3.2 | Truth Table for the 4-2 Compressor                  | 55       |

| Table 4.1 | Truth Table for proposed compressor                 | 66       |

| Table 4.2 | Performance matric of dadda Multiplier              | 72       |

| Table 4.3 | Error detection with various parameter              | 74       |

| Table 5.1 | Comparison of different multiplier using Xilinx     | 91       |

| Table 5.2 | Performance Comparison of multiplier using Candace  | 92       |

| Table 5.3 | Comparison Table of Proposed Multiplier with the    | 93       |

|           | Literature                                          |          |

# **ABBREVIATIONS**

| CMOS | Complimentary metal oxide Semiconductor     |

|------|---------------------------------------------|

| CPTL | Complimentary Pass Transistor Logic         |

| CDAC | Capacitor-Based Digital-To-Analog Converter |

| СР   | Charge Pump                                 |

| DCO  | Digitally Controlled Oscillator             |

| DRC  | Design Rule Check                           |

| DMRO | Dual-Mode Ring Oscillator                   |

| DPI  | Digital Phase Interpolation                 |

| DPLL | Digital Phase Locked Loop                   |

| ECM  | Error Correcting module                     |

| FA   | Full Adder                                  |

| GDI  | Gate Diffusion Input                        |

| IC   | Integrated Circuit                          |

| LE   | Logic Element                               |

| LPM  | Low Power Multiplier                        |

| NMOS | N-type metal oxide Semiconductor            |

| PMOS | P-type metal oxide Semiconductor            |

| PP   | Partial Product                             |

| RC   | Resistance Capacitance                      |

| VLSI | Very Large Scale Integration                |

#### **CHAPTER 1**

#### Introduction

#### 1.1 MOTIVATION

Reducing power dissipation has become a top design priority due to the growing complexity of microelectronic circuits and the level of device integration [1]. Although power efficiency in electronic circuits has long been desired, it has only recently evolved into a crucial consideration during the initial stages of the design process [2]. Two types of power dissipation constraints exist. The first is related to cooling issues in high-performance systems [3]. High-speed circuits release large quantities of energy in a short period of time, generating significant heat as a byproduct. The integrated circuit package used must be capable of dissipating this heat. If the package (PCB, system enclosure, or heat sink) cannot sufficiently disperse the heat, or if the necessary thermal components are prohibitively expensive, heat removal may become a limiting constraint [4].

The second scenario of high-power circuit failure is linked to the rising acceptance of portable electronics. All battery-powered devices, including laptops, pagers, portable video players, and mobile phones, have a finite operating period before requiring recharging [5]. Low-power operation is preferred in integrated circuits to extend battery life. Additionally, newer generations of applications often demand more computational power, which places additional stress on the system's energy storage components [6]. Recent technological advancements have successfully reduced power usage. Power dissipation has decreased due to trends such as the shift from bipolar devices to CMOS and the shrinking of lithographic feature sizes, even though high integration speed was the primary driver of these advancements [7]. Power optimization has only recently been recognized as a separate design objective. In this study, we will focus on the digital multiplier, a component widely used in contemporary microelectronic circuit design, for power optimization [8]. In this chapter, we will provide a broad overview of power optimization and discuss how it relates to existing design processes. We will also give a quick overview of the

multiplier, its various uses, and some design objectives for creating efficient designs. With the rising integration of devices and the increasing complexity of electronic circuits, reducing power dissipation has become a primary design objective [9]. While power efficiency has always been advantageous in electronic circuits, it has recently turned into a limiting factor for a wide range of applications, requiring consideration from the outset of the design process [10]. Arithmetic circuits, such as multipliers and adders, are fundamental components in the design of communication circuits. Recently, there has been a growing interest in designing digital systems for communication applications and advanced signal processing with low power consumption and no performance penalty [11]. Designing low-power, high-speed arithmetic circuits requires a combination of techniques at four levels: algorithm, architecture, circuit, and system levels [12]. This study presents the design and simulation of a multiplier architecture suitable for high-performance and low-power applications.

Digital multipliers are the most commonly used components in various modern circuit designs. They are fast, reliable, and efficient components used to perform arithmetic operations [13]. Depending on the design of the components, there are different types of multipliers available. The choice of multiplier architecture is based on the specific application [14]. Power dissipation in a multiplier is a critical issue, as it reflects the total power consumed by the circuit and, thus, affects the performance of the device.

Current digital systems may require a high volume of calculations while facing certain energy and speed limitations [15]. In portable systems, where the energy stored in the battery is the primary source of power for operation, reducing energy consumption is a vital design objective. Similarly, this importance extends to systems designed to harness energy from the environment [16]. In numerous applications, such as communications, biomedical devices, multimedia, and the Internet of Things (IoT), the computations involve digital signal processing (DSP) of signals. For a large set of applications where minimal output quality is acceptable, DSP blocks may perform the necessary processing efficiently [17]. These blocks consist of arithmetic units that can operate using the approximate computational paradigm.

In these applications, the base output quality may depend on a trade-off between quality and energy efficiency/speed. Inexact computing inherently involves sacrificing precision for energy savings or speed (performance) [18]. This paradigm can be applied in both software and hardware domains of processing systems. In the hardware domain, several inexact components, such as adders and multipliers, have been introduced [19]. Notable examples of inexact adders include Estimated Arrival I, AMAs, TGAs, LOA, Estimated Arrival II, LREA, Stuff, iRAP-CLA, and QuAd. These inexact components have been evaluated using them in DSP blocks such as Finite Impulse Response (FIR) filters and Discrete Cosine Transform (DCT) applications, including image processing [20]. Inexact computing can also be applied at the algorithmic level in DSP applications, while precise components are used to execute data path tasks after algorithmic approximations have been applied [21]. The use of inexact units in computation frameworks, including DSP blocks, may degrade the output quality, which should be carefully assessed for optimal utilization of these units [22]. More specifically, one must evaluate the impact of estimation errors on output quality as a critical step in employing inexact units.

An efficient assessment can be accomplished using a mathematical model for the units, such as inexact adders. In traditional approaches, statistical representations of inexact component errors have been obtained through comprehensive simulations. To address the complexity, some researchers have relied on Monte Carlo (MC) simulations to determine quality [23]. However, the limitations of exhaustive and MC simulations include the need to simulate every type of multiplier along with its configuration, requiring substantial runtimes for evaluating the output quality of DSP applications [24]. Additionally, these methods do not provide insights into the sources and causes of the errors, nor do they offer a clear understanding of how estimation errors affect signal characteristics [25].

To overcome these issues, a fully analytical modeling approach for various error metrics, such as error probability and mean error distance, has recently been introduced [26]. Although the main problems were addressed in these studies, the use of convolution algorithms resulted in significant computational overhead in

evaluating output quality [27]. By employing MC simulations to find statistical error characteristics of the adders/multipliers, semi-analytical approaches have been introduced to address the extensive runtimes for output quality assessment. Ultimately, optimizing speed and energy characteristics for a given maximum acceptable output quality loss is a key objective in designing digital systems based on inexact computing [28]. Since the improvement structure heavily relies on the quality assessment technique, an efficient modeling procedure is highly desired to prevent excessive runtime [29]. Most digital signal processing (DSP) systems incorporate a multiplication unit to perform calculations such as correlation, convolution, filtering, and frequency analysis. In many DSP algorithms, the multiplier is in the critical delay path and ultimately determines the performance of the computation [30]. The speed of multiplication is crucial not only in DSP but also in general processors today, especially with the rise of media processing.

In the past, multiplication was primarily executed using a series of additions, subtraction, and shift operations. Recently, numerous multiplication algorithms have been developed, each with its own advantages and disadvantages in various fields [31]. The multiplier is a relatively large block within a computing system. The amount of hardware involved is proportional to the square of its size; for example, a multiplier of size n bits has O(n²) gates. For multiplication algorithms used in DSP applications, latency and throughput are the two significant constraints from a delay perspective [32]. Latency refers to the actual delay in processing a function, measuring how long it takes after the inputs to a device are stable for the results to be available on the outputs. Throughput is the number of multiplications that can be performed in a given period [33].

Multipliers are not only high-latency blocks but also significant sources of power dissipation. Therefore, if one aims to minimize power consumption, it is crucial to identify strategies to reduce delay through various optimization techniques [34]. Minimizing power consumption in digital systems involves optimizing all levels of design. This includes the technology used to implement the digital circuits, the style

of circuits and geometry, the architecture for executing the necessary circuits, and, at the highest level, the algorithms used [35].

The key technological concept revolves around supply voltage and voltage scaling, enabling the reduction of input voltage with minimal impact on logic speed [36]. Energy is consumed as capacitance is switched power can be reduced by minimizing capacitance through activity reduction, choice of number representation, careful management of signal transitions, re-synchronization to minimize glitches, logic design, circuit design, and physical layout [37].

High-level optimization strategies for low-power multipliers are covered in this dissertation. High-level approaches are algorithmic and architectural techniques that take into account the mathematical properties of multiplication and the characteristics of the input data [38]. This study's primary research hypothesis is that high-level multiplier design optimization results in more power-efficient solutions than low-level multiplier design optimization alone. We specifically explore how to regulate the active multiplier resources to align with the features of external data, as well as how to improve the internal algorithm and design of multipliers. Power reduction with minimal area and delay overhead is the main goal [39]. Another advantage of high-level optimization lies in its capacity to decrease both power consumption and area or delay through the use of novel algorithms or designs.

## 1.2 Power Optimization

Energy is a measure of all the Joules dissipated by a circuit, whereas power is the total number of Joules dissipated over a certain period of time. Although they are similar, low-power and low-energy designs have different objectives. Power becomes an issue primarily when cooling is a concern. Peak power is often used for reliability analysis, signal noise margin, and power and ground cable design [39]. In the context of improving battery lifespan, energy per operation or task is a better indicator of a system's energy efficiency. To evaluate the benefits of designs in digital CMOS, the well-known power-delay product is frequently utilized. However, this can be misleading since power × delay = (energy/delay) × delay = energy, implies that delay

is irrelevant. The term "energy-delay product" should be used instead, as it refers to two separate measurements of circuit behavior. To ensure that a comparison of power-delay products is equivalent to a comparison of energy-delay products, various schemes should be evaluated at the same frequency.

Dynamic power and static power are the two main sources of power dissipation in digital CMOS circuitry. Dynamic power is associated with capacitance charging and discharging, short-circuit current dissipation, and other events that change logic states. The sole source of static current in CMOS logic is unintentional leakage current, which may manifest as reverse-biased PN junction current or sub-threshold channel conduction current [34]. Even so, sporadic exceptions to the conventional CMOS logic, including pseudo-N MOS logic, can result in significant static current.

Power optimization of digital systems has been researched at various abstraction levels, from the most fundamental technological level to the most complex system level [35]. Power consumption is reduced at the technological level through advancements in the manufacturing process, including smaller feature sizes, extremely low voltages, copper interconnects, and insulators with low dielectric constants [36]. Lower voltages can be applied to non-critical system blocks thanks to the support for different supply voltages during manufacturing [37]. To lessen imbalances in wire capacitance and signal latency, placement and routing are modified at the layout level. Transistor sizing, network restructuring, and other circuit logic designs are employed to reduce power at the circuit level. Various strategies have been proposed at the gate level. Gate-level techniques used in commercial tools like Power Compiler include cell size, cell composition, equivalent pin switching, and buffer insertion. These approaches yield an average power saving of 11% while increasing area by 9%. Additional gate-level techniques, such as signal gating, delay balancing, input synchronization, and signal polarity optimization, have also been suggested. Clock gating has been widely used at the register-transfer level (RTL) to deactivate combi-national or sequential blocks that are not in use at a given time. In Power Compiler, operand isolation is employed to deactivate a data path unit if its outputs are not being used, while clock gating disables an entire register bank.

Computational gating is an RTL signal gating method that identifies output-invariant logical conditions at some combi-national block inputs and inhibits inputs under these conditions. Re timing rearranges registers in sequential circuits to prevent the propagation of erroneous transitions [38].

There is considerable flexibility in power optimization at the architectural and system levels. The two primary methods for achieving better performance than required and then trading operation frequency for supply voltage reduction are parallelism and pipe-lining. Transforming the control-data-flow graph (CDFG) is another effective strategy for creating low-power architecture [39]. Asynchronous systems are also studied to avoid a global clock signal and minimize unnecessary computations. The practice of deactivating or disabling components in event-driven systems when they are not in use is referred to as a power management approach. Despite the fact that power reduction has been achieved through optimization approaches at all levels, strategies at the lowest technology level and the highest architecture/system level are often more effective than those at intermediate levels. Three significant power consumption parameters—C<sub>L</sub> and V<sub>DD</sub>—are impacted by technology-level optimization. All four factors (C<sub>L</sub>, V<sub>DD</sub>, switching activity, and frequency) are influenced by algorithm/architecture-level identification optimization, particularly through the of candidates V<sub>DD</sub> reduction. In contrast, middle-level optimization often has a limited impact on one or two aspects.

## 1.3 Architecture of Low Power Multiplier Design

Multiplication consists of three phases: producing partial products (PPs), reducing partial products (PPR), and performing carry-propagate addition (CPA) [38]. In general implementations, there are sequential and combi-national multipliers. Due to the high level of integration now possible, this study focuses solely on combi-national multipliers used in digital VLSI systems. Several multiplication algorithms exist within the PPG, PPR, and CPA methodologies.

Radix-2 digit-vector multiplication is the simplest form for PPG, utilizing AND gates to reduce the number of PPs and thus the overall complexity. One operand is often encoded into high-radix digit sets based on area and delay considerations of PP reduction. The radix-4 digit set, with values  $\{-2, -1, 0, 1, 2\}$ , is the most commonly used. For PPR, there are two approaches: column reduction, carried out by an array of counters, and row reduction, performed by an array of adders. There are two main categories within row reduction: linear arrays and tree arrays. While both tree array and column reduction have delays of  $O(\log n)$ , where n is the number of PPs, linear arrays have a latency of O(n). A fast adder technique is necessary for the final CPA since it is on the critical path. If it is desirable to retain duplicate results from PPG for additional arithmetic operations, the final CPA may occasionally be delayed.

Low-level strategies, particularly many of the power optimization techniques discussed in Section 1.2, are relevant to the design of low-power multipliers [35]. These low-level methods have been examined for multipliers and include signal polarity optimization, delay balancing, input synchronization, transistor reordering and sizing, pass-transistor logic, swing-restricted logic, transistor sizing, and voltage scaling [36]. However, these methods have only moderately improved power consumption in multipliers, often requiring significant design effort or resulting in high area or delay overhead.

Three factors make low-power multiplier design challenging. First, there is a quadratic relationship between operand accuracy and multiplier area. Second, the multiple logic levels in parallel multipliers can cause erroneous transitions or errors [37]. Third, to achieve high speed, parallel multipliers may have highly complex structures, which reduces the effectiveness of layout and circuit-level optimization.

Multiplication is a fundamental arithmetic operation that differs from random logic in several ways at both the algorithmic and bit levels of computing. However, low-level power optimization techniques have not adequately addressed these differences [38]. Additionally, the low-level properties of the incoming data are challenging to account for. Therefore, it would be beneficial to develop algorithmic and architectural-level

power optimization strategies that consider the mathematical properties and operand characteristics of multiplication [39].

Multipliers perform the core function of multiplication in most arithmetic computing systems [40]. They are an indispensable part of various applications such as FIR filters, arithmetic circuits, the Internet of Things (IoT), DSP applications, artificial intelligence, and other domains that involve intensive computation. However, multipliers consume a significant amount of power, which in turn reduces processing speed. Reducing power consumption in multipliers can help shorten processing time and improve overall system efficiency [42]. As a result, low-power design solutions for multipliers have generated significant interest in recent years. Based on the techniques used to perform multiplication, multipliers can be categorized as follows:

- 1. ARREY Multipliers

- 2. BOOTH Multipliers

- 3. WALLACE Multipliers

These multipliers are suitable for Very Large Scale Integration (VLSI) technology with CMOS implementation. Array multipliers are fast, but they suffer from high hardware complexity. The area required for array multipliers is large, which leads to increased delay and, consequently, higher power consumption. Booth multipliers are used for high-speed applications; however, their main drawback is excessive power consumption. Wallace multipliers are also designed for fast operations and are commonly employed in speed-critical systems. Some ancient Vedic methods of multiplication include:

- 1. Urdhva Tiryakbhyam sutra

- 2. Nikhilam sutra

These Vedic multipliers are particularly effective when handling a large number of bits. The Urdhva Tiryakbhyam Sutra is based on traditional multiplication techniques [43]. Both Vedic methods are known for their high processing speed. Vedic multipliers are fast and widely applicable in DSP applications. As the number of bits

(N) increases, delay is significantly reduced in Vedic multipliers, making them well-suited for modern digital designs. The main aim of this paper is to present a comprehensive literature review of different multiplier designs and their applications.

## 1.3.1 Architecture of multipliers

The dynamic growth of DSP applications is increasing day by day due to the high demand for low power consumption, less area, and lightweight designs, which are top priorities for designers working on communication systems and multimedia devices [44]. To design low-power multipliers, various tools are employed for simulation, synthesis, and parameter analysis. Multipliers can be implemented using tools like Xilinx 14.5, Xilinx ISE 14.7, Cadence, and Verilog HDL, depending on the target application area.

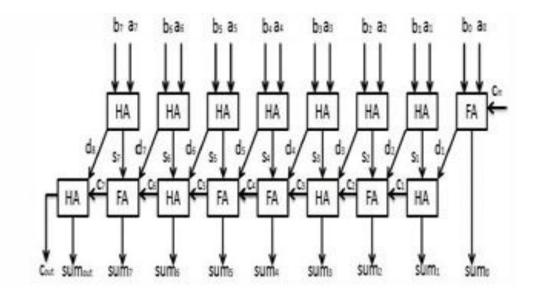

The Wallace Multiplier uses a column compression architecture to improve multiplication speed. Its performance is significantly better than that of the Array Multiplier, particularly because the delay variation depends on the length of the operand word. XOR- X NOR based compressors like 5:2, 4:2, and 3:2 are used to reduce the number of partial products in the Wallace Tree structure [45].

In the case of the Dadda Multiplier, as the operand word size increases, so do the key performance parameters—speed, area, and power consumption [46]. Traditional 8×8 Dadda Multipliers require extensive wiring overhead due to a large number of addition operations. The authors compared several multiplier architectures, including Regular Dadda, Decomposed Dadda, Partitioned Dadda, Wallace Tree (based on 3:2, 4:2, and 5:2 compressors), and Hybrid Multiplier designs. The simulation results of these architectures yielded a total power consumption ranging from 0.737 to 2.440 mW, delay from 4.4 to 7.5 ns, and a power-delay product between 5.527 and 10.73 [47]. The performance of digital multipliers such as Carry Save, Array, Baugh-Wooley, and Wallace Tree Multipliers was also analyzed. A 0.8V power supply and 22nm Predictive Technology Models were used for simulation. According to the analysis, the Baugh-Wooley Multiplier had the lowest delay and emerged as the fastest multiplier. In this method, the authors implemented a 2's complement

approach for multiplication and presented results for a 4×4 Baugh Wooley Multiplier. Using a 46-transistor full adder cell, the Array Multiplier had a delay of 165 ps and power consumption of 135  $\mu$ W, while the Baugh Wooley Multiplier had a delay of 123.26 ps and power of 85.11  $\mu$ W. When implemented with a 28-transistor full adder, the Array Multiplier showed 154.68 ps delay and 88.42  $\mu$ W power, while the Baugh-Wooley Multiplier showed 106 ps delay and 79.63  $\mu$ W power [48]. The analysis also considered the Wallace Tree and Carry Save Multipliers.

A high-speed and area-efficient Booth Re-code Wallace Tree Multiplier was proposed for fast arithmetic circuits. In this design, the author reduced the area of the Wallace Tree Multiplier by applying the Booth Re-coding Algorithm and a compressor adder. The design was implemented using Verilog HDL, and synthesis was performed on a Xilinx Virtex-6 FPGA. Results showed that the proposed Wallace Tree Multiplier is 67% more efficient in terms of speed compared to the existing Wallace Tree architecture. Additionally, it was 53% faster than the Vedic Multiplier, 22% faster than the Radix-8 Booth Multiplier, and 18% faster than the Radix-16 Booth Multiplier. The area of the proposed Wallace Tree Multiplier was also significantly reduced [49].

Multiplication is a fundamental operation in all microprocessor and micro controller-based systems used in DSP applications and is typically performed using combinational circuits [20]. Based on the literature review presented in this paper, the focus remains on the low-power, high-speed, and area-efficient design of multipliers. Among the various architectures proposed, the Wallace Tree and Dadda Multipliers are the most frequently considered due to their strong performance across critical parameters. Consequently, this study focuses on the architectures and analysis of these multipliers.

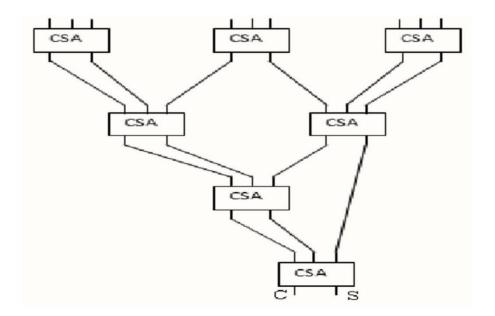

**1.3.2** Wallace Tree Multiplier: Wallace Tree Multipliers were developed by Wallace to enable the fast processing of two-number multiplication [49]. In the Wallace Tree Multiplier method, a three-step multiplication process is applied. A three-input Wallace Tree circuit uses Carry-Save Adders (CSA), as shown in Figure 1.1.The output from each stage is supplied as input to the next stage, allowing for efficient reduction of partial products and accelerating the overall multiplication process.

Figure 1.1 Wallace Tree Multiplier [49]

The circuit layout in the Wallace Tree Multiplier method is somewhat complex, but it offers very high speed performance [12]. Its fast switching speed and low power consumption make the Wallace Tree Multiplier a high-speed multiplier with a superior architecture [49]. There are different types of Wallace Tree Multipliers, each designed to further optimize specific performance parameters such as area, delay, or power efficiency.

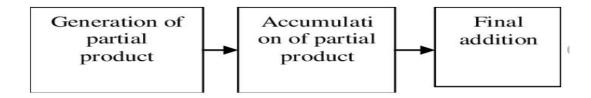

**1.3.3. Conventional Wallace tree Multiplier**: This is the simplest multiplier in terms of architecture, consisting of three main blocks. The first block handles the generation of partial products, the second block is responsible for the accumulation of partial products, and the final stage performs the addition, as illustrated in Figure 1.2.

Figure 1.2. Conventional Wallace Tree Multiplier [49].

**1.3.4. Modified Wallace tree Multiplier:** In this Wallace tree multiplier Reverse pyramid style is applied by the designers for partial products. A reduction tree to reduce the complexity of Wallace tree multiplier [50]. Figure 1.3 shows the modified Wallace tree multiplier is using in a MAC unit.

Figure 1.3. Modified Wallace Tree Multiplier using in MAC Unit [50].

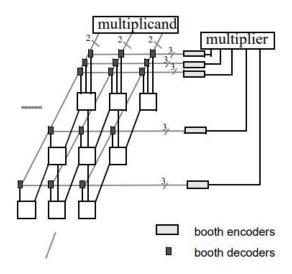

**1.3.5** Wallace Booth Multiplier: In this multiplier, the Booth Recoding algorithm and compressors are used. The Booth Recoding algorithm is employed to reduce the number of partial products [29]. The main advantage of this architecture is its reduced area and high speed [35].A Wallace Tree architecture is implemented using compressors instead of traditional full adders. The architecture of the Wallace Tree multiplier is modified using 3:2 compressors in the first stage, 4:2 compressors in the second stage, and 5:2 compressors in the third stage, essentially forming a combination of three full adders. Figure 1.4 illustrates the Novel Wallace Booth Multiplier.

Figure 1.4. Novel Wallace Booth Multiplier [51].

**1.3.6 Dadda Multiplier:**The Dadda Multiplier was invented by computer scientist Luigi Dadda in 1965 [51]. It is derived from the family of parallel multipliers. In Dadda multipliers, the adder stages are minimized, making it an advanced and refined version of the Wallace multiplier. The Dadda multiplier is implemented based on the Dadda scheme, which reduces the number of adder stages required for the addition of partial products. Full adders and half adders are used in this architecture. The structure of the Dadda multiplier reduces the tree to only two rows, allowing for stage-wise reduction as necessary. Overall, the Dadda multiplier is a refinement of the Wallace multiplier, optimized for area and delay. A 4×4 Dadda multiplier using half adders and full adders along with a Ripple Carry Adder (RCA) at different stages is shown in Figure 1.5.

Figure 1.5. 4x4 Dadda Multiplier using RCA [51]

Requirement of wider and fast CPA is the main drawback of Dadda Multiplier. Structure of Wallace tree multiplier is better than the Dadda multiplier [51]. The Hybrid multiplier is an advanced research topic in multiplier design, combining both Wallace multiplier and Dadda multiplier architectures. A 4×4 Dadda multiplier and a 4×4 Wallace multiplier were constructed for analysis and simulation. The simulation tool used was MICROWIND with a technology node of 0.25 micrometers. Various parameters of these multipliers were simulated, and notably, compressors were not used in this structure. The design consumes less area and low power, showing a 40% improvement in the power-delay product compared to the existing 8×8 Wallace and Dadda multipliers, which use compressors.

This dissertation systematically examines low-power multiplier design at both the algorithmic and architectural levels from two perspectives: internal efforts focused on multiplier design and external efforts considering input data characteristics. For internal efforts, we consider techniques such as PPG re-coding, operand representation, and PPR structure optimization. For external efforts, we investigate signal gating to disable portions of a full-precision multiplier. The types of multipliers researched include linear array multipliers, leapfrog multipliers, left-to-right multipliers, split multipliers, and tree multipliers. Column reduction multipliers are not considered, as they achieve similar latency and area as tree arrays but significantly worsen regularity. Since adding signed integers is convenient using the two's complement form, it is widely employed in digital arithmetic systems.

## 1.4 Integrated Circuit Multiplication

Digital multiplication is one of the most fundamental operations in a wide variety of algorithms. The widespread use of the multiplication operation in computing has led to numerous implementations with various requirements and objectives. Some applications require a wide dynamic range and high accuracy, while in other cases, these requirements are not as strictly defined [52]. When high accuracy is a concern, digital multiplication is preferred over analog methods, as it is relatively straightforward to create digital multipliers that meet the specific accuracy required by the application.

The level of accuracy necessary for multiplication varies by function. For example, image compression methods typically require 8 bits, whereas more accurate digital signal processing (DSP) tasks require 16 bits. Generally, digital signal processing utilizes 16-bit multipliers, while microprocessors employ 53/64-bit multipliers. In these designs, integer multiplication is the fundamental operation; in floating-point multipliers, the integer multiplication units are smaller versions of the larger floating-point units [53]. The architecture is influenced by whether the procedures are signed or unsigned, and several innovative methods have been proposed to modify the bit representation of numbers to achieve power savings. However, delay has historically been, and remains, the primary concern in multiplication.

## 1.5 Design Consideration of Digital Circuits

In ensuring correct digital functionality, the primary concern for system designers has always been speed. A circuit is designed to operate at a specific delay; if this delay is not met, the entire system may fail to function properly. While further reductions in delay are beneficial, they are not always strictly necessary.

Other factors may hold equal or greater importance than power dissipation; considerations regarding area, performance, and reliability are also crucial for designers. It's worth noting that power reduction methods are not necessarily negatively correlated with delay reduction. For instance, one strategy to reduce delay in a circuit is to increase the driving strength of gates, which can lead to increased power consumption [53]. However, reducing interconnect capacitance is another method that lowers both power and delay. Generally, significant power savings can be achieved if delay is not a critical issue, but it is irrelevant to prioritize power reduction without considering other factors.

## 1.6 Power vs Energy

For the purposes of this discussion, the distinction between the terms "power" and "energy" is crucial. It should be noted that power refers to the rate at which energy is dissipated by a circuit over time, whereas energy measures the total amount of energy

dissipated by a circuit regardless of the time factor. Power reduction is technically a distinct objective from energy reduction. When heat removal is an issue, power can become problematic.

A package's heat sink might not be able to transfer heat quickly enough if too much energy is converted into heat in a short period; this can result in an increase in temperature and subsequent thermal failure. The cooling structure is better equipped to handle the circuit's thermal demands if the same amount of energy is generated over a longer period of time [53]. Here, power reduction refers to minimizing the situation in which a significant amount of energy is lost in a short time frame. However, the overall amount of energy lost may not change.

The goal of energy reduction is to lower the total amount of energy that must be dissipated. Since time is not a factor in this calculation, we often refer to energy per operation as the metric to be optimized. Thus, while energy reduction pertains to optimizing battery longevity, power reduction falls within the realm of thermal reliability.

## 1.7 Delay and Power in Multipliers

The multiplication operations used by digital signal processing (DSP) algorithms are the main topic of this thesis. In this domain, accuracy is often required to be 8 or 16 bits. Algorithms impose two limitations on multiplication in terms of delays: throughput and latency. A device's latency measures how long it takes for the final result to appear on the outputs once the inputs are stable. Throughput, on the other hand, measures how many multiplications can be completed in a specific length of time. For a straightforward combi-national multiplier, throughput depends on delay. However, there are several methods for computing multiple multiplications simultaneously, where latency is only tangentially connected to throughput.

Throughput is a critical issue in DSP. Digital signal processing algorithms frequently deal with the transmission and detection of audio and visual inputs, such as images or sounds [54]. In such applications, using narrow bit-width multipliers is feasible

because the precision requirements are less stringent compared to other tasks, such as numerical algorithms for scientific computing. Additionally, small multipliers do not lead to lengthy delay paths. The key limiting specification for many DSP applications is throughput. These tasks often require processing images of relatively low quality, but they work with vast amounts of data representing various image or sound samples. For instance, generating an image involves executing calculations on numerous polygons, but the required accuracy (in bits needed to identify a specific color or spatial coordinates) is minimal. Numerous 8-bit computations are necessary for voice compression [55].

One technique to execute a large number of calculations quickly is to reduce the latency of multiplication, allowing the multiplier to start executing the next operation sooner. However, increasing throughput is a more effective approach to boost the number of calculations. Using multiple devices on a single chip increases throughput by the number of additional units, whereas pipeline or interleaving data allows a single functional unit to perform multiple tasks concurrently. These methods are typically more effective than merely reducing latency since attempts to decrease a circuit's delay often lead to diminishing returns (after a certain point, increasing the number of transistors does not significantly reduce delay). Conversely, optimizing throughput allows the number of operations that can be calculated in a given period to rise with each new functional block introduced.

In strongly coupled hardware/software systems, implementing pipeline can be challenging, even though it improves throughput. While the logic implementation of pipeline is relatively simple, it can be difficult to persuade compilers to create programs that effectively utilize it. The challenge lies in establishing a sequence of tasks to start execution while other tasks are still finishing. These "concurrent" or "overlapping" methods of system behavior introduce timing conditions that complicate the task of writing a compiler that can exploit such hardware techniques. Furthermore, while some DSP calculations lend themselves to parallel execution, others require processing to be more sequential, rendering additional pipeline hardware unnecessary [56]. Ultimately, very high-speed code is often written by hand

in low-level programming. Understanding all the techniques for optimizing a pipe lined function can be quite tedious when done manually.

These considerations support the use of multiple multiplication functional units on a single chip rather than implementing a heavily pipe lined multiplier. The multiplier is a relatively large block within a computing system. The amount of hardware involved is proportional to the square of its size (i.e., a multiplier of size nm bits has O(n2)O(n^2)O(n2) gates). Not only is the multiplier a high-delay block, but it can also be a significant source of power dissipation. Given the arguments outlined above, having several multipliers on-chip becomes essential as more DSP processing power is required [57]. The power dissipation associated with multiplication will become more pronounced, regardless of whether the pipe lined approach is used; a first-order pipe lined multiplier will dissipate as much power as several multiplier blocks. Although a pipe lined version has fewer gates, it will still experience a similar amount of switching. Consequently, digital multipliers have become one of the primary circuits targeted for power reduction.

## 1.8 Overview of Monograph

Following this, a concise overview of the research methodology employed in this dissertation is provided. The design and experimental procedures used in our research are fully described in the thesis. We start by identifying crucial elements that impact algorithmic and architectural power usage. These elements include the internal designs of multipliers and the characteristics of external data. Second, we propose advanced power optimization approaches that integrate both internal and external efforts. Internal work includes improvements to the reduction structure, operand representation, and multiplier re-coding, while external actions involve various forms of signal gating. To assess the feasibility of each method, we conduct high-level first-order estimates and theoretical analyses.

Third, we implement the proposed schemes and associated earlier schemes in structural verilog language that are independent of technology. For design optimization and maintenance flexibility this language is used widely. These designs can be translated into the Artisan TSMC 0.18-mm, 1.8-volt standard-cell library and assessed using wire-load models in the Synopsys design environment or Cadence. The next step involves running automatic layouts with Cadence Silicon Ensemble, using guided floor-planning to examine the impact of layout on high-performance multipliers.

In this work, we aim to identify the relevant factors that affect both power and delay in multipliers. As referenced above, power should be considered simultaneously with delay; a reduction in power with a corresponding increase in delay yields net advantage. In the first phase of our research, we focused on existing delay reduction strategies for multipliers and examined their power dissipation properties. Delay reduction techniques for digital multipliers are well established, with a history spanning over thirty years. Various delay targets can be met using different enhancement strategies, and at times, multiple methods may be applied simultaneously. It is of great interest to identify which strategies should be employed to reduce delay while also aiming to minimize power consumption. Those approaches that show the most promise, as well as those that have not been previously explored, are typically the focus of our most intense investigation.

In the second phase of this work, we sought to expand the range of potential strategies by exploring ideas for power reduction that emerged from the initial analysis. Not all the ideas we implemented were successful; however, we identified several methods that show promise for reducing power in multipliers. Our experimental methodology relied on the standard cell design approach. These were thoroughly characterized for energy dissipation and delay under various input conditions and output loads. The multiplier logic was derived from standard descriptions found in the literature, and the actual logic synthesis was performed automatically using synthesis algorithms obtained from the literature, along with several enhancements we added to the process.

Once the multiplier was synthesized, the impact of physical effects was evaluated using a placement and routing stage, which aimed to determine rough wiring characteristics based on routing length. In later stages, results were validated by performing a full design using the Cadence tool suite. Given the logic and physical

description of the functionality, timing analysis was conducted using static delay data from the specified standard cells. Delay was estimated using a logic simulator that counted switching events and evaluated glitches.

Our design methodology evolved over time as our tools were refined and accuracy improved. First, we needed to perform specific tasks that were impractical using vendor tools—some of these, like multiplier synthesis, were essential to this dissertation's contributions. Second, while vendor tools could perform some tasks necessary for this work (e.g., Cadence could be used for static timing analysis), we required slight modifications to vendor tool functionalities (e.g., timing analysis computing the static longest path) that were difficult to achieve. Although coding such methodologies increased the time required to complete this task, we also gained the advantage of accessing these techniques at a very fine level of detail (for instance, we could integrate timing code within the inner loop of our multiplier synthesis algorithm).

The primary objective of this research is to explore and develop an efficient design framework for Approximate Low Power Multipliers, particularly suited for Digital Signal Processing (DSP) applications. To begin with, the study aims to establish a comprehensive set of operating parameters that will serve as a foundation for the classification and evaluation of various approximate multiplier designs. This classification facilitates a systematic approach to analyze trade-offs between accuracy, power, delay, and area. Following this, the research focuses on the development of a novel algorithm for low power multiplication that incorporates approximation techniques to achieve substantial energy savings while maintaining acceptable levels of computational accuracy. A key goal of the proposed work is to optimize power consumption in the designed multiplier architecture to enhance overall system performance, particularly in power-constrained environments. This architectural design will consider the critical balance between performance, power, and precision, ensuring practical applicability in real-world signal processing scenarios.

For more accurate delay and power computation, interconnect parameters are retrieved and back-annotated into Cadence. Full-timing gate-level simulation yields a

power estimation. Finally, experimental findings comparing various compressor based low power digital multiplier are presented and discussed.

## 1.9 Organization of the Thesis

The organization of thesis is as follows

Chapter 1 presents the introduction to the work, beginning with the motivation behind the research followed by the need for power optimization in digital circuits. The architecture of low power multipliers is explored in detail, including various multiplier structures such as the Wallace tree, Dadda, and Booth multipliers. Integrated circuit multiplication is discussed, along with important digital design considerations. A comparative overview of power versus energy, and delay and power trade-offs in multipliers is also presented. The chapter concludes with an overview of the entire monograph.

Chapter 2 provides a detailed literature review covering fundamental concepts of multipliers and their role in digital design. The structure and operation of multipliers are explained including partial product generation and reduction techniques such as array and Wallace tree reduction. The chapter further explores CMOS power dissipation, differentiating between static and dynamic power. The fundamentals of power optimization are addressed, followed by a review of existing literature to identify research gaps relevant to the thesis.

Chapter 3 outlines the optimization techniques and proposed methodology used in this research. It starts by describing the operating parameters used for categorization. A detailed explanation of the proposed algorithm, particularly the design and function of the accurate and approximate 4:2 compressor, is given. The compressor's integration into the Dadda multiplier is discussed. Power optimization strategies and an error-correcting module (ECM) are introduced. Circuit design considerations and performance analysis methods are also covered.

Chapter 4 presents the proposed design and model of the system. The design architecture and the tools used for implementation are explained. The proposed

system integrates an approximate compressor-based multiplier along with an ECM. The detailed design of the proposed Dadda multiplier is elaborated. Simulation results are presented and discussed to evaluate design efficiency and parameter optimization.

Chapter 5 covers the experimental results and performance evaluation of the proposed architecture. Performance analysis is carried out using Xilinx and Cadence tools under different library conditions (fast.lib and slow.lib). Parameter results are reported and analyzed. The chapter also examines the impact of optimization techniques on overall performance, including their effectiveness. A practical application in image processing is briefly introduced to demonstrate the proposed design's utility. Finally, the extent to which the research objectives have been achieved is discussed.

Chapter 6 concludes the thesis by summarizing the contributions of the research. It also outlines the future scope and potential extensions of the work in related areas.

The thesis concludes with references and a list of publications that support and relate to the work presented.

#### **CHAPTER 2**

# Literature Review: Multipliers and Power Minimization Using Compressors

This Chapter presents about a portion of the essential ideas which are normal to the areas which we examined. To start with, a short depiction of computerized multipliers, their design and applications. Postpone decrease methods are likewise talked about. Then, we go over power scattering in CMOS circuits, alongside a few essential strategies which can be used to decrease power parameters.

# 2.1 Introduction to Multipliers

To comprehend postponement and parameters as power compromises in multipliers circuits, it will portray the essential circuit design of computerized multiplier executions. Inspect a portion of strategies it is created to diminish multiplier timings, especially acquire a comprehension of trademark power dispersal. Few understanding acquired using perception of rationale phenomenon, power dissemination reviewed by few sources; methods which decrease the parameter power because any of these sources can demolish the parameter power scattering by other one. Short conversation of wellsprings of power scattering in computerized CMOS delineate the significant impacts. Integration of total applicable power disseminating impacts this investigation, It is decided to assess multiplier plans by fostering a strategy which uses different methodology for circuits at low level test systems to compute power utilization. Make up to gradualness definite methodology, a reenactment based assessment program permitted fast examination of force and postponement to plans, exactness confirmed utilizing the point by point circuit test systems.

## 2.1.1 Basic structure of Multiplier

Essentially, automated replication should be evident to facilitate the advancement of spot movements that involve additions [58]. Here, two numbers, the multiplicand and the multiplier, are combined prior to the final addition.

Figure 2.1. Digital multiplier flow [58]

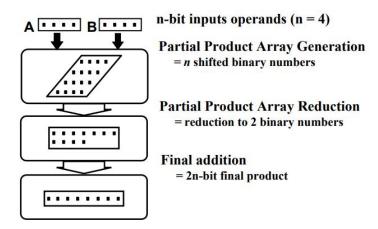

Think about duplication of same numbers: the multiplicand C and multiplier P, now P is a n-cycle number using bit portrayal {pn-1, pn-2,...,p0}, main piece pn-1, most in-huge piece p0; multiplicand has a comparative piece portrayal {cn-1,cn2,...,c0}. Unsigned augmentation, for the n moved multiplicand are added with structure outcome. Whole strategy separated using stages: fractional item (PP) age, incomplete item decrease, and last expansion. This is delineated thoughtfully as shown in Figure 2.1.

# 2.1.2 Generation of PP(Partial Product)

Underlying move toward computerized duplication is to produce n moved duplicates of the C, it included the following steps [58]. A available moved duplicate of the C will added relies upon worth of P bit that is multiplier bit relating to C duplicate. In event that the multiplier and multiplicand are included.

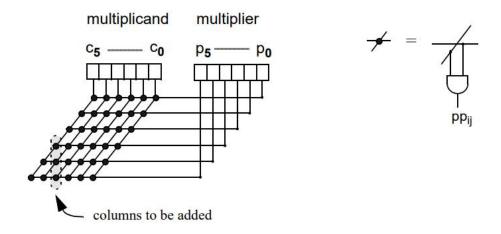

Figure 2.2.PP( Partial product) generation for 6\*6 bit multiplication [58].

In the event that the piece is '0', C isn't add. Piece portrayal by capability will carried out utilizing coherent AND entryway, it performs AND(Pi,Ci), j = 0 to n-1, I = 0 to n-1. Subsequent qualities are called incomplete item bits or just, incomplete items; assuming we cover these halfway items by bit positions, we show up at a construction displayed in Figure 2.2. In this plan, the halfway item pieces are organized in segments. Subsequent trapezoidal construction is known as a fractional item cluster or basically PPA. Different types of incomplete item exhibits exist, contingent upon the number portrayal. For model, in the accompanying segment we depict a typical variation called Corner re coding, which permits a marked multi-bit incomplete item portrayal of the plan. Normal variations for proficiently carrying out two's supplement are depicted in [57]. There are a few significant focuses to see about the halfway item exhibit. To start with, in the most fundamental detailing (PPA bits produced through consistent AND), every one of the pieces are made in equal; Static postponement of every one pieces is equivalent. Next is components of the exhibit is elements of size of P and C: the level of the cluster is relative to the size of the P, and width are corresponding to size of C. At long last, every one of the pieces in a specific section are added, & a few segments have less pieces than other ones.

#### 2.1.3 Reduction of Partial Product

Basics of a productive advanced multiplier execution is how PPA pieces added. Traditional convey adders carry out addition tasks, deferral of multitude of adders consumes more time. All things being equal, the incomplete item is decreased utilizing a procedure called convey save expansion [58]. This methodology permits progressive increments to be integrated into one worldwide expansion step. Think about a mathematical piece vector portrayal of the accompanying structure.

Think about the case where good for nothing vectors added. The most reduced piece state, 2 pieces are add then convey is proliferated to following piece state. That point convey in & following 2 pieces at maximum piece position consolidated, & do produced. Utilizing undulating strategy, addition of two n-digit number taken O(n) successive piece options, coming about in postponement O(n). We need addition of three piece a,b and c, every one size is n, then utilize it to addition of initial.

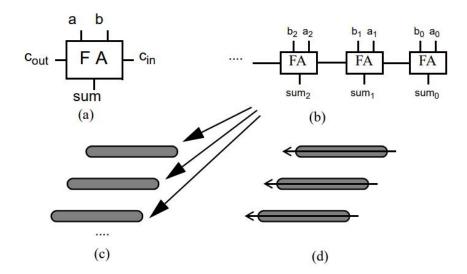

Figure 2.3. illustrates the addition of partial products (PP). (a) showcases the block diagram of a full adder. (b) presents the basic block RA (ripple adder). (c) demonstrates ripple addition employed to add copies of the multiplicand. (d) describes the basic method of ripple adders with a complexity of O(n^2) [58].

A and operation with B, afterward add C then aftereffect of A+B. Quantity of piece increments are O(2n). That's what somehow happened which involve the strategy in dim-witted design for add n moved duplicates of n-bit C. This occurs because we assume that addition operations depend on previous addition operations, where the outputs of earlier operations serve as inputs to subsequent operations. See Figure 2.3. Albeit the eventual outcome happens from joining tasks, measure of freedom exists with every activity. Think about add activity at segment using section premise; every one of the pieces in a section should be added together, alongside the convey in pieces of the past section. The postpone in working out the result in section is an element to convey in bit stream ( taken from past segment) is accessible, the quantity of pieces which are using for addition as shown in figure 3 Convey store expansion use the way which add activities in discrete sections autonomously performed.

#### 2.1.4 Array Style Reduction

Array Style Reduction (ASR) plays a pivotal role in crafting efficient digital multipliers, especially within low-power and high-performance scenarios. This review explores the importance of ASR and its ramifications on the design and enhancement of multipliers.

In this segment, we depict the most essential strategy, called cluster fractional item decrease. Putting it together, "cluster fractional item decrease" could potentially refer to a process or technique aimed at reducing the number of fractional items within a cluster. This could involve methods for consolidating or combining similar fractional values within the cluster to simplify the data set or improve computational efficiency.

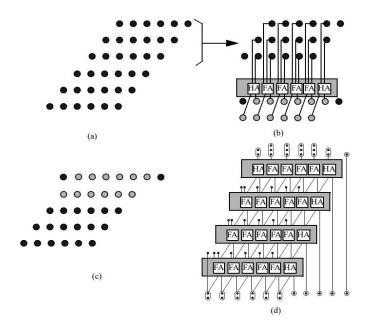

Figure 2.4. Array to reduce PP (partial product) - (a)The PP (partial product) (b)

Carry save full adder to reduce 3 bit (c) resulting PPA (d) Whole [59].

array. For instance, in the Figure 2.4a, shown the PPA produced for the 6-cycle by 6-digit duplication. Consolidating consequences to expansion using leftover pieces for PPA, it obtain an outcome to shows up in Figure 2.4c. Three vectors diminished to 2 vectors. This design rehashes until the full cluster is launched as in Figure 2.4 the outstanding trademark about the cluster design is its ordinary construction [59]. It is beneficial to spread out, solitary viper block & related connections ions recreated width, profundity of cluster.

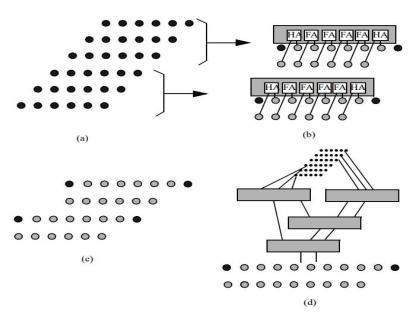

## 2.1.5 Wallace Tree Partial Product Reduction

Wallace Tree Partial Product Reduction stands as a technique employed in digital circuit design, specifically in crafting high-speed multipliers, aimed at efficiently diminishing the quantity of partial products generated throughout the multiplication