# DESIGN AND ANALYSIS OF RING STRUCTURED BASED VCO FOR HIGH FREQUENCY APPLICATIONS

Thesis Submitted for the Award of the Degree of

# **DOCTOR OF PHILOSOPHY**

in

**Electronics and Communication Engineering**

By

Priyanka Kumari B.S

41800147

**Supervised**

$\mathbf{B}\mathbf{y}$

Dr. Sobhit Saxena

**Professor**

**School of Electronics and Electrical Engineering**

LOVELY PROFESSIONAL UNIVERSITY, PUNJAB 2025

## **DECLARATION**

I, hereby declared that the presented work in the thesis entitled "Design And Analysis Of Ring Structure Voltage Controlled Oscillator For High Frequency Applications" in fulfilment of degree of **Doctor of Philosophy** (**Ph.D.**) is outcome of research work carried out by me under the supervision of Dr Sobhit Saxena, working as Professor, in the School of Electronics and Electrical Engineering of Lovely Professional University, Punjab, India. In keeping with general practice of reporting scientific observations, due acknowledgements have been made whenever work described here has been based on findings of other investigator. This work has not been submitted part or full to any other University or Institute for the award of any degree.

Name of the scholar: Priyanka Kumari B S

Registration No.:41800147

Department/school: Electronics & Communication Engineering

Lovely Professional University,

Punjab, India

## **CERTIFICATE**

This is to certify that the work reported in the Ph.D. thesis entitled **Design And Analysis Of Ring Structure Voltage Controlled Oscillator For High Frequency Applications**" submitted in fulfillment of the requirement for the award of degree of **Doctor of Philosophy** (**Ph.D.**) in the **Electronics & Communication Engineering**, is a research work carried out by **Priyanka Kumari B S, 41800147**, is bonafide record of his/her original work carried out under my supervision and that no part of thesis has been submitted for any other degree, diploma or equivalent course.

13/

(Signature of Supervisor)

Name of supervisor: Dr Sobhit Saxena

Designation: Professor

Department/school: School of Electronics and Electrical Engineering

University: Lovely Professional University

## **ABSTRACT**

VCO is the basic building block in many communications and signal processing equipment and plays a crucial role in generating essential high-frequency clock signals that drive data transmission and reception, and that can be adjusted by a control voltage. Generally, LC oscillators provide superior phase noise and greater oscillation frequencies, but this comes at the expense of a limited frequency tuning range and a complicated manufacturing procedure for inductors and capacitors on the silicon surface.

Device scaling uncovered many short channel effects (SCEs), and the bulk CMOS technology behavior upsets with these SCEs. To overcome these exposed effects, single gate devices should be substituted with multiple gate devices to enrich the gate control over the conducting channel. Fin gate FET technology is a promising device to provide efficient gate control over the conducting channel. There are few multi gate Fin-FET devices are Double gate Fin-FET (DG-Fin-FET), Triple gate Fin-FET (TG-Fin-FET) and gate around Fin devices. Ring-based voltage-controlled oscillator (VCO)'s frequency of oscillations should be less sensitive to the supply voltagevariations. A sudden drop in supply voltage significantly affects the performance of the VCO. Supply voltage insensitive circuit or low voltage operated designs are the backbone of the constantVCO performance. CMOS based supply compensation techniques reduce the oscillation frequency with the supply voltage decrease. Hence fully customized Fin-FET based circuits designs are unveiled as the solutions to reduce the significant amount of power wastage and delay of the stages as the switching characteristics of the Fin-FET is better than the bulk CMOS transistor, which eliminates the losses and negates supply noise.

In this thesis, we proposed a new low power technique to lower the power of VCO and enhance battery life. The CMOS ring oscillator designs are made on different nano scale technologies and verified the major design parameters such as frequency of oscillations, power, and area of the designs as one part of the thesis. The other part of thesis is related to the designs of ring oscillators to improve the oscillation frequency and power. An 18 nm technology Fin-FET has been modeledin order to achieve desired characteristics. This FinFET greatly reduced the SCEs compared to thebulk MOSFET hence used in the designs of three stage, five stage and twenty-one stage ring oscillators. Supply voltage considered as 1V. The oscillator has exceptional performance across several domains, such as the microwave frequency range inside the L-band,

sensitivity to supply variations, occupied area, power consumption, and phase noise. The frequency of oscillations increased along with reduced stage number; we got 17.7GHz frequency from the three-stage ring circuit. Verilog A and Cadence Virtuoso helped with our designs.

# Acknowledgement

I am sincerely thankful to my supervisor, Dr. Sobhit Saxena, a Professor in the School of Electronics and Electrical Engineering at Lovely Professional University, Phagwara, Punjab, India, for his unwavering support and guidance throughout my research journey. Dr. Sobhit Saxena consistently offered the direction, inspiration, and knowledge required to complete my Ph.D. program. His readiness to assist me in overcoming any challenges and his steadfast support during tough times were invaluable. Our joint success would not have been possible without his unconditional support, for which I am deeply grateful.

Additionally, I would like to express my profound appreciation to Lovely Professional University for beautiful environment that was supportive and conducive to my research, from the initial idea to the completion of this dissertation. The significant support and scholarships provided by the University's management were instrumental in the successful completion of my Ph.D. program. I'm also very thankful to my friends and family for their tremendous support. Although I cannot name each person individually, their contributions were crucial in helping me achieve my goals.

I am incredibly thankful to my family for their steady support throughout my academic journey. Their constant positivity, patience, and unconditional love have been a rock-solid foundation for my efforts. Their presence and encouragement have played a crucial role in my achievements over the years and have provided a solid foundation for my efforts. I am pro foundly thankful for their belief in me and their encouragement to pursue my goals.

# **TABLE OF CONTENTS**

|      |         |                                        | Page No |

|------|---------|----------------------------------------|---------|

|      |         | TABLE OF CONTENTES                     | vi      |

|      |         | LIST OF FIGUTERS                       | ix      |

|      |         | LIST OF TABLES                         | xi      |

|      |         | ABBREVATIONS                           | xii     |

|      |         | ABSTRACT                               | Iv      |

|      | PTER I: | INTRODUCTION                           | 11 – 28 |

| 1.1  |         | Introduction                           | 11      |

| 1.2  |         | VCO Applications                       | 12      |

| 1.3  |         | VCO Characteristics                    | 13      |

| 1.4  |         | Oscillator                             | 14      |

| 1.5  |         | Ring Oscillator                        | 16      |

| 1.6  |         | Importance of Miniaturization          | 19      |

| 1.7  |         | Low-power techniques                   | 20      |

| 1.8  |         | Importance of energy efficient designs | 21      |

| 1.9  |         | Fin-FET Technology                     | 22      |

| 1.10 |         | Motivation of the thesis               | 26      |

| 1.11 |         | Research gaps                          | 26      |

| 1.12 |         | Objectives of the thesis               | 26      |

| 1.13 |         | Methodology                            | 27      |

| 1.14 |         | Thesis Organization                    | 27      |

| CHA  | PTER II | : LITERATURE REVIEW                    | 29-35   |

|      |         | Literature Review                      |         |

| CHA  | PTER II | I: CMOS RING OSCILLATOR                | 36-58   |

| 3.1  |         | Scaling theory                         | 36      |

| 3.2  |         | Ring Oscillator                        | 38      |

| 3.3  |         | Ring Oscillator design                 | 40      |

| 3.4  |         | Basic Inverter                         | 41      |

|      | 3.4.1   | Stacking inverter                      | 43      |

|      | 3.4.2   | Sleep transistor method                | 44      |

|      | 3.4.3   | Sleepy stack technique                 | 45      |

|      | 3.4.4   | Zigzag technique                       | 46      |

|      | 3.4.5   | Sleepy keeper technique                | 47      |

| 3.5  |         | Ring Oscillator Analysis               | 48      |

|      | 3.5.1   | Design                                 | 48      |

| 3.6  |         | Results                                | 51      |

| CHA  | PTER IV | V: FINFET DESIGN                       | 59-87   |

| 4.1  |         | Introduction                           | 59      |

| 4.2  |         | Basic Fin-FET structure                | 61      |

|      | 4.2.1   | Classification of Fin-FET structures   | 62      |

| 4.3 |          | Fin-FET Challenges                          | 65      |

|-----|----------|---------------------------------------------|---------|

| 4.4 |          | Fin-FET operation                           | 67      |

| 4.5 |          | Fin-FET characteristics                     | 68      |

| 4.6 |          | Fin-FET Design                              | 71      |

|     | 4.6.1    | Fin-FET implementation and characterization | 71      |

| 4.7 |          | FinFET Inverter                             | 82      |

|     | 4.7.1    | SG-Fin-FET Inverter Design                  | 82      |

| CHA | APTER V  | : FINFET BASED RING OSCILLATOR              | 87-116  |

| 5.1 |          | Introduction                                | 87      |

| 5.2 |          | Basic Fin-FET Ring Oscillator               | 88      |

| 5.3 |          | Three stage ring Oscillator                 | 90      |

| 5.4 |          | Three stage Fin-FET based ring Oscillator   | 91      |

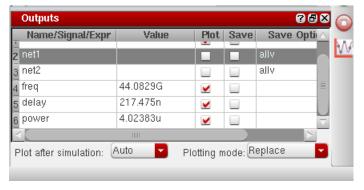

|     | 5.4.1    | Transient Analysis                          | 94      |

| 5.5 |          | Five stage ring oscillator                  | 96      |

| 5.6 |          | Twenty-one stage ring oscillator            | 100     |

| 5.7 |          | Stability Analysis                          | 105     |

| 5.8 |          | Phase Noise                                 | 105     |

|     | 5.8.1    | Jitter Analysis                             | 111     |

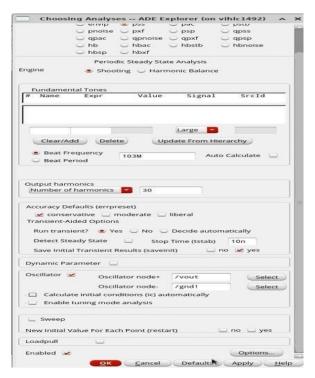

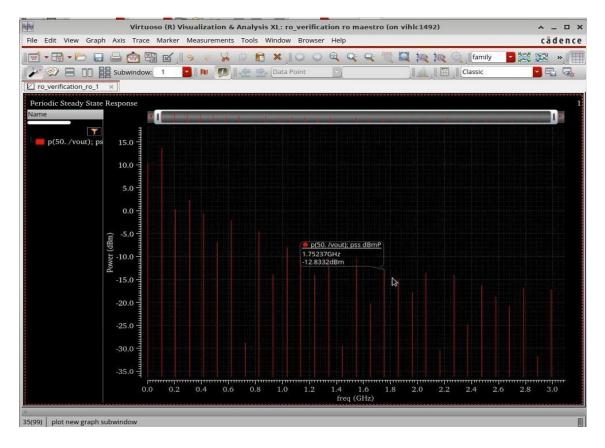

|     | 5.3.4    | Phase Steady State Analysis                 | 113     |

| 5.4 |          | Conclusion                                  | 115     |

| CHA | APTER- V | VI: CONCLUSIONS AND FUTURE SCOPE            | 117-119 |

| 6.1 |          | CONCLUSIONS                                 | 117     |

| 6.2 |          | FUTURE SCOPE                                | 119     |

|     |          | APPENDIX                                    | 119-127 |

|     |          | REFERENCES                                  | 127-138 |

# LIST OF FIGURES

| Figure No.     | Title of the Figure                                               | Pg. No. |

|----------------|-------------------------------------------------------------------|---------|

| Figure 1.1     | Block Diagram of PLL                                              | 12      |

| Figure 1.2     | Simple Oscillator circuit                                         | 14      |

| Figure 1.3     | Simple three inverter ring oscillator                             | 16      |

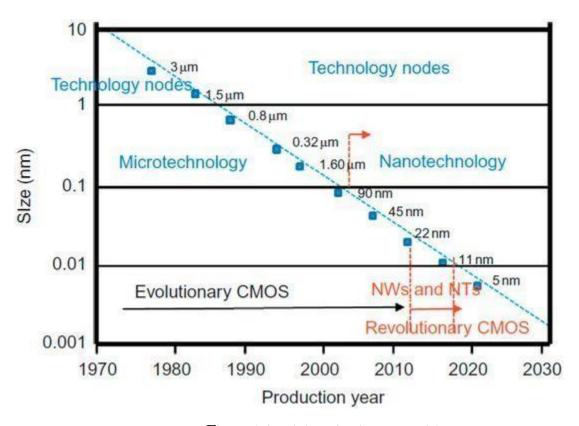

| Figure 1.4     | Miniaturization trend                                             | 19      |

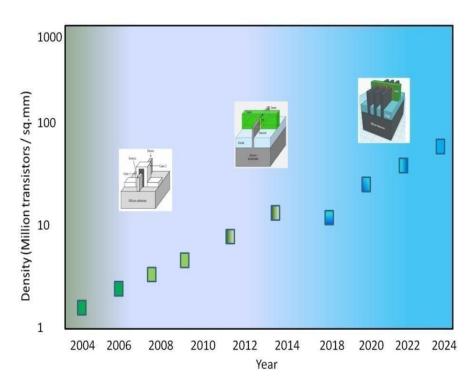

| Figure 1.5     | Chip density across technological node                            | 23      |

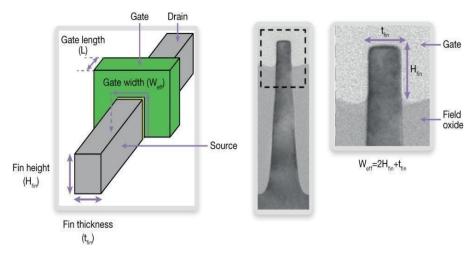

| Figure 1.6     | Basic FinFET structure                                            | 24      |

| Figure 3.1     | Trends in future size over time.                                  | 37      |

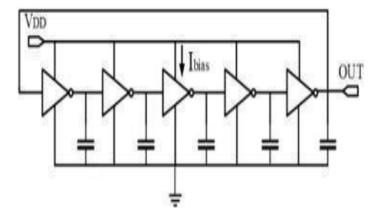

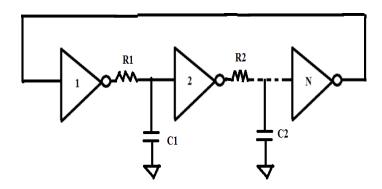

| Figure 3.2     | A Five stage Ring Oscillator                                      | 40      |

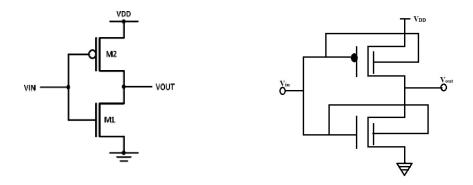

| Figure 3.3     | Basic Inverter circuit                                            | 42      |

| Figure 3.4     | Stack inverter circuit.                                           | 44      |

| Figure 3.5     | Sleep transistor inverter circuit                                 | 44      |

| Figure 3.6     | Sleepy stack inverter                                             | 45      |

| Figure 3.7     | Zigzag inverter circuit                                           | 46      |

| Figure 3.8     | Sleepy keeper inverter                                            | 46      |

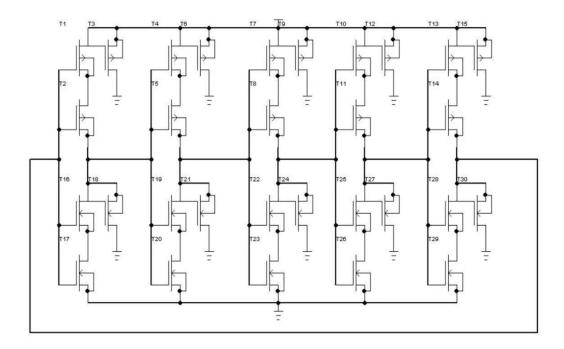

| Figure 3.9     | Five Stage Sleepy Keeper Ring Oscillator                          | 50      |

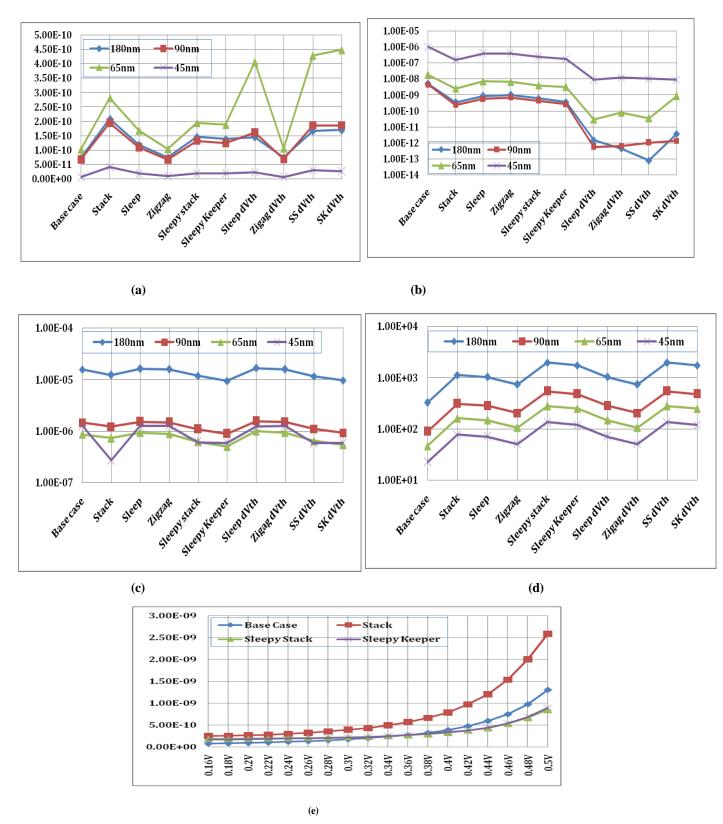

| Figure 3.10(a) | Five stage ROs delay values                                       | 55      |

| Figure 3.10(b) | Five stage ROs Static power                                       | 55      |

| Figure 3.10(c) | Five stage ROs Dynamic power                                      | 55      |

| Figure 3.10(d) | Five Stage ROs Area                                               | 55      |

| Figure 3.10(e) | Five stage ROs Area overheads                                     | 55      |

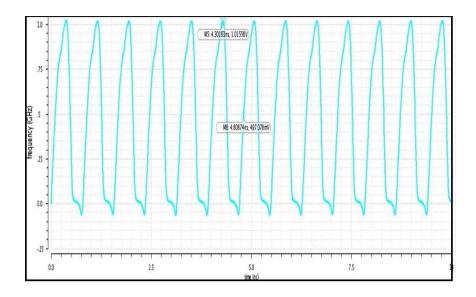

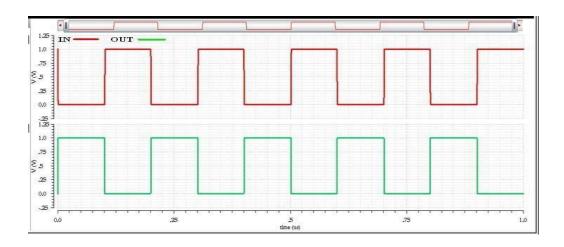

| Figure 3.11    | Five stage ring oscillator output                                 | 56      |

| Figure 3.12    | Five stage ring oscillator frequency response                     | 57      |

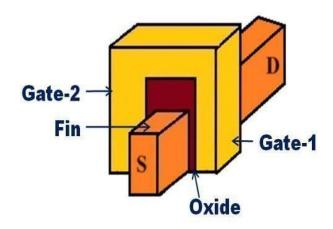

| Figure 4.1     | Basic Fin-FET structure                                           | 63      |

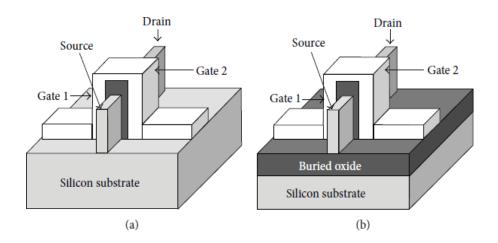

| Figure 4.2     | Comparisons of structures (a) Bulk Fin FET (b) SOI Fin FET design | 64      |

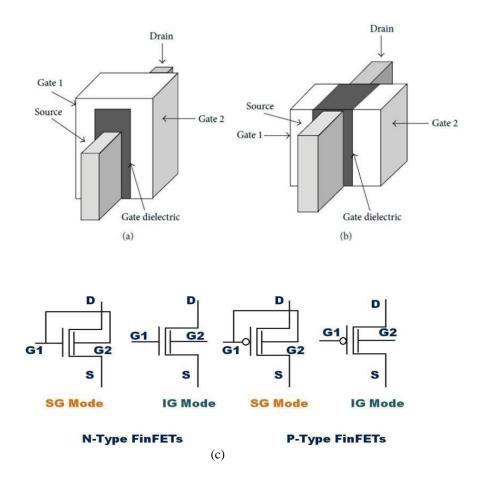

| Figure 4.3     | Structure schematic: (a) SG Fin-FET, (b) IG Fin-FET               | 65      |

|                | (c) Symbols of device sN-Type and P-Type SGF and IGF devices      |         |

| Figure 4.4     | Fin-FET Geometry                                                  | 68      |

| Figure 4.5     | Log-linear characteristics of MOSFET                              | 69      |

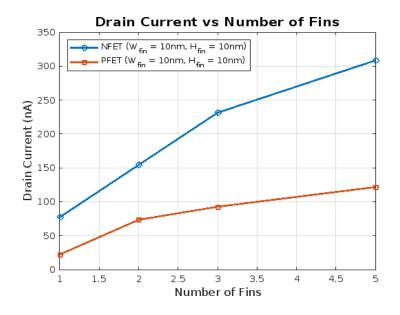

| Figure 4.6     | Drain current Vs number of fins at $Wfin = Hfin$                  | 74      |

|                | @10nm(a)nFin FET(b)pFin -FET                                      |         |

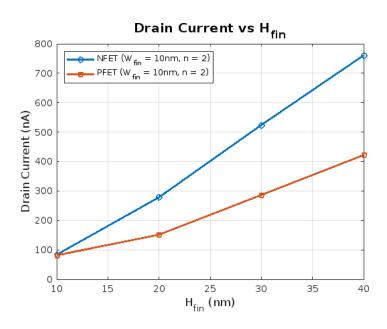

| Figure 4.7  | Drain current of both the Fin-FETs at <i>W fin</i> @ 10nm, with changing <i>H fin</i> from 10nm to 40nm | 76  |

|-------------|---------------------------------------------------------------------------------------------------------|-----|

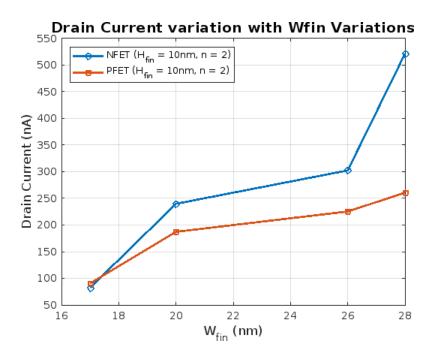

| Figure 4.8  | Drain current of n-type and p-type Fin-FET varying TFIN                                                 | 77  |

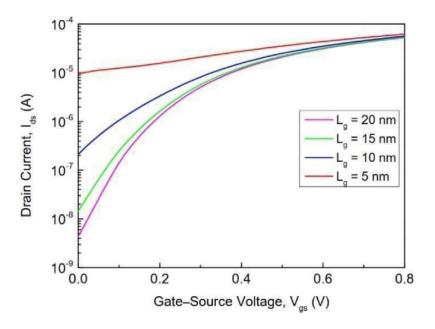

| Figure 4.9  | Fin-FET transfer characteristics                                                                        | 78  |

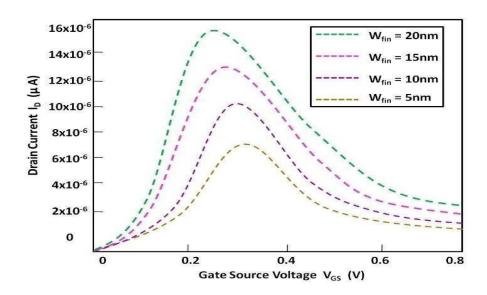

| Figure 4.10 | Impact of Wfin on IDS and gm.                                                                           | 79  |

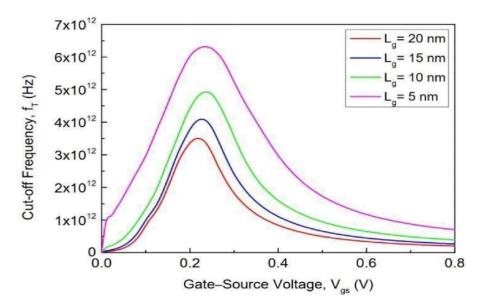

| Figure 4.11 | FinFET cutoff frequency as a function of VGS                                                            | 81  |

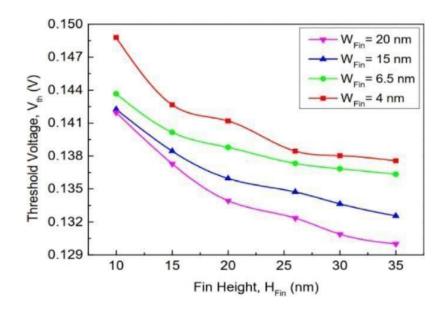

| Figure 4.12 | Impact of Fin height on Threshold Voltage                                                               | 82  |

| Figure 4.13 | Inverter circuits (a) Basic circuit (b) Fin-FET based                                                   | 83  |

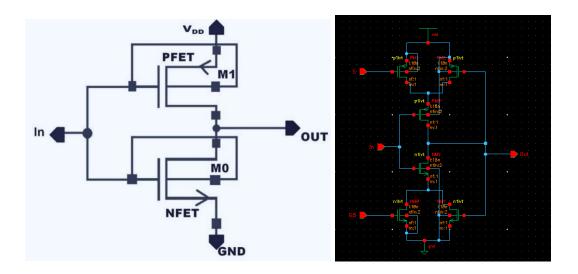

| Figure 4.14 | Fin-FET based Inverter circuit (a) basic and (b) sleepy keeper type                                     | 85  |

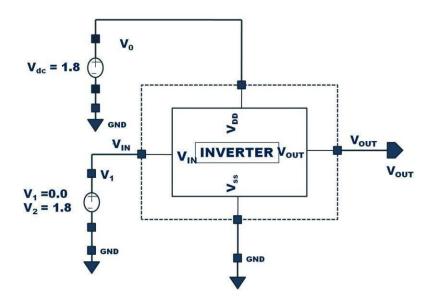

| Figure 4.15 | Inverter test circuit.                                                                                  | 86  |

| Figure 4.16 | 18 nm Fin-FET Inverter output                                                                           | 87  |

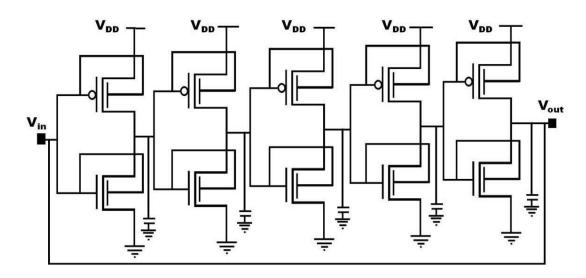

| Figure. 5.1 | Basic three stage Fin-FET ring oscillator circuit                                                       | 93  |

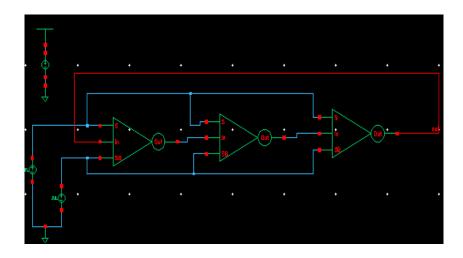

| Figure 5.2  | Three stage Fin-FET ring oscillator schematic circuit                                                   | 96  |

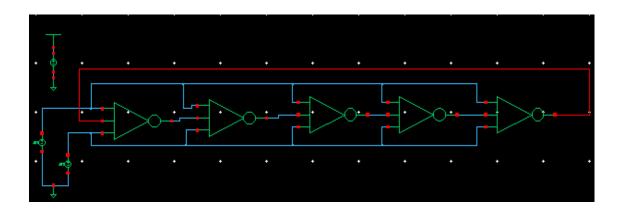

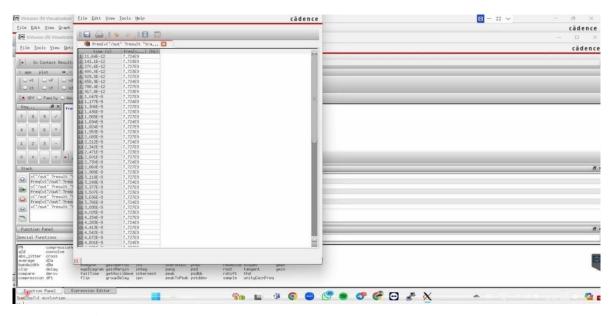

| Figure 5.3  | Analysis choosing popup window                                                                          | 97  |

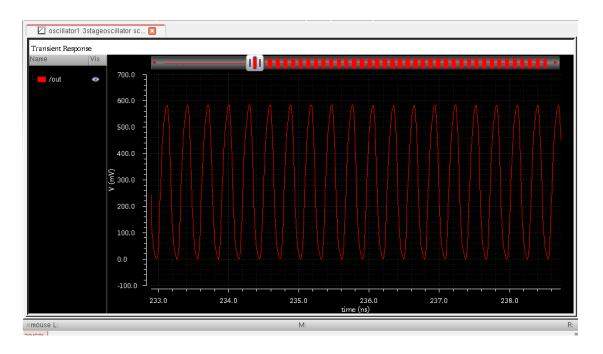

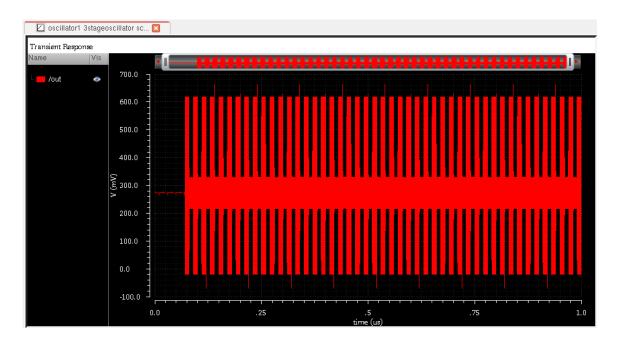

| Figure 5.4  | Transient response of 3 stage Fin-FET ring oscillator                                                   | 98  |

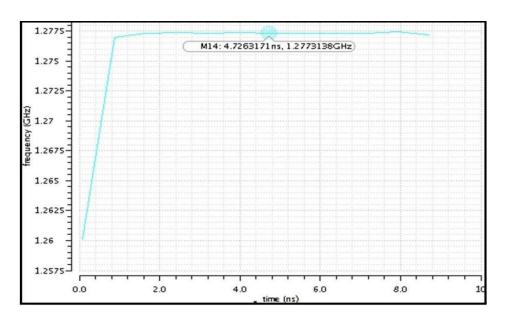

| Figure 5.5  | Three stage Fin-FET based ring oscillator frequency response                                            | 98  |

| Figure 5.6  | Five stage Fin-FET ring oscillator circuit                                                              | 100 |

| Figure 5.7  | Five stage Fin-FET ring oscillator schematic circuit                                                    | 101 |

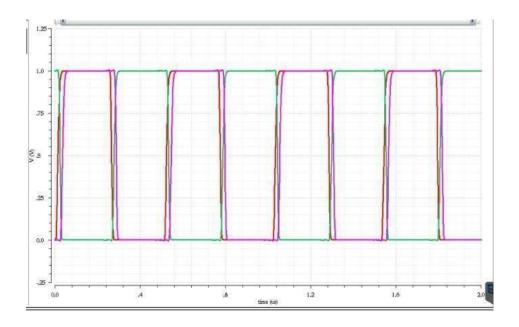

| Figure 5.8  | Five stage Fin-FET ring oscillator Transient response                                                   | 101 |

| Figure 5.9  | Five stage Fin-FET ring oscillator frequency response                                                   | 102 |

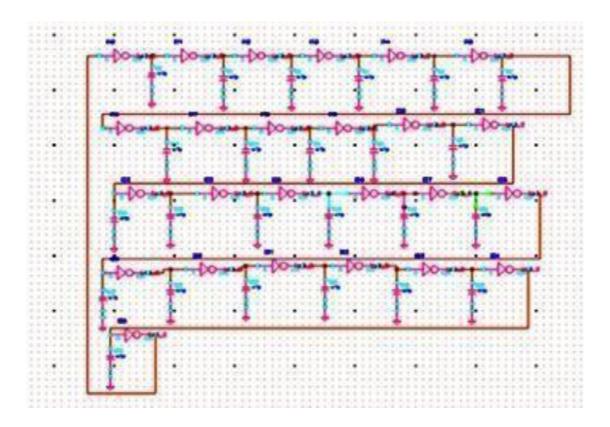

| Figure.5.10 | 21 stage ring oscillator schematic circuit                                                              | 105 |

| Figure 5.11 | Transient Analysis of first four stages in 21 stage RO                                                  | 107 |

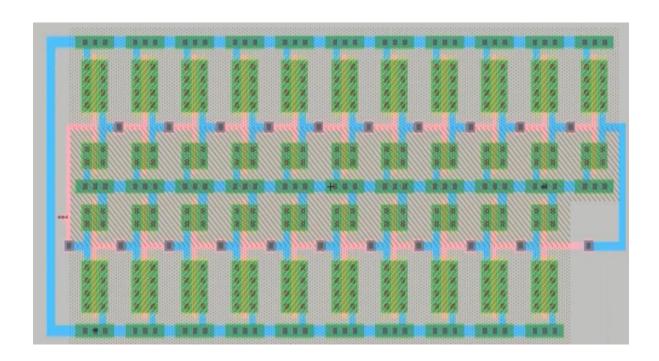

| Figure 5.12 | 21 Stages ring oscillator Layout                                                                        | 108 |

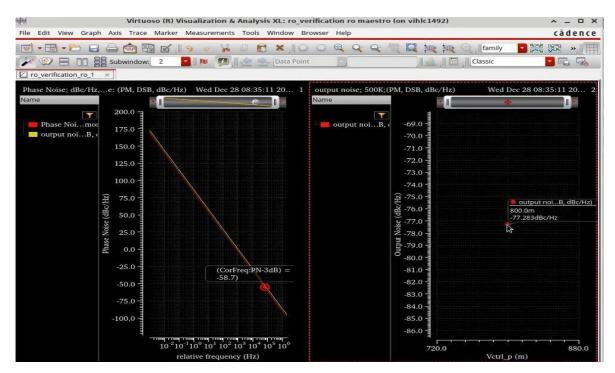

| Figure 5.13 | Phase Noise curve                                                                                       | 110 |

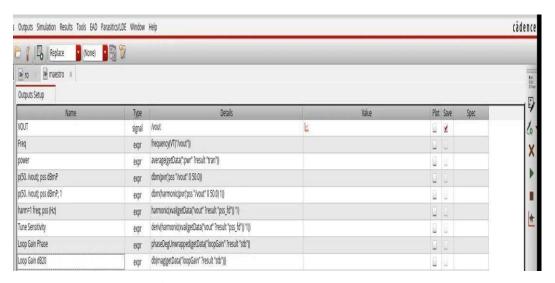

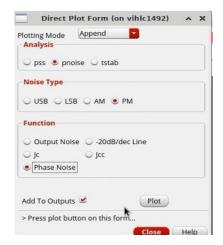

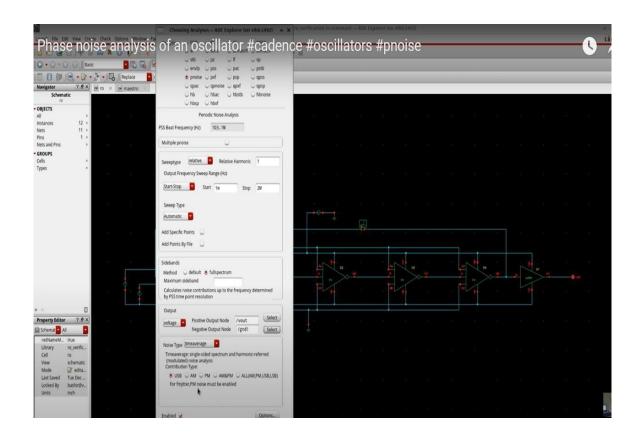

| Figure 5.14 | Phase Noise setup window                                                                                | 111 |

| Figure 5.15 | Phase Noise analysis setting window                                                                     | 112 |

| Figure 5.16 | Phase Noise popup window                                                                                | 112 |

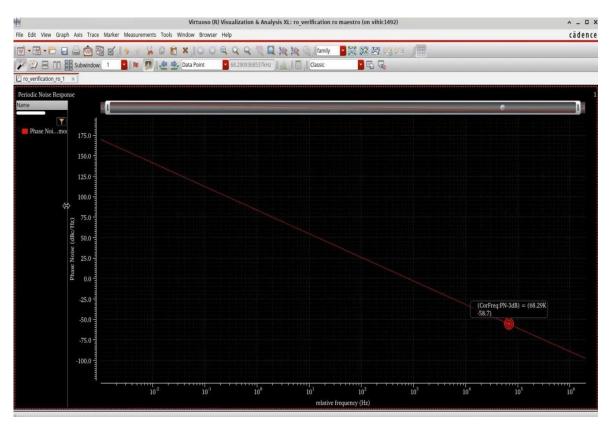

| Figure 5.17 | Phase Noise response                                                                                    | 113 |

| Figure 5.18 | Settings for output noise measurement                                                                   | 113 |

| Figure 5.19 | Output noise and phase noise plots                                                                      | 114 |

| Figure 5.20 | Jitter settings popup window                                                                            | 115 |

| Figure 5.21  | Ring oscillator Jitter waveform | 116 |

|--------------|---------------------------------|-----|

| Figure 5.22  | PSS setting window              | 117 |

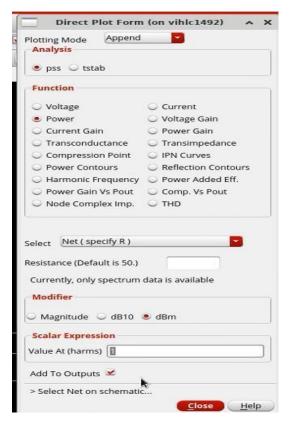

| Figure 5.23  | Direct plot form window         | 118 |

| Figure. 5.24 | PSS response plot               | 118 |

# LIST OF TABLES

| Table No.  | Title of the Table                                                                                      | Pg. No. |

|------------|---------------------------------------------------------------------------------------------------------|---------|

| Table 3.1  | Results for the chain of Inverters using 180nm technology                                               | 43      |

| Table 3.2  | Results for the chain of Inverters using 90nm technology                                                | 43      |

| Table 3.3  | Results for chain of Inverters using 65nm technology                                                    | 44      |

| Table 3.4: | Results for the chain of Inverters using 45nm technology                                                | 44      |

| Table 3.5  | Comparison parameters of proposed work and existing work                                                | 49      |

| Table 3.6  | Comparison with only 45nm technology work                                                               | 59      |

| Table 4.1  | PFin-FET and nFin-FET drain current for number of fins increasing from 1 to8, <i>W fin=H fin</i> @ 10nm | 60      |

| Table 4.2  | Drain current of both the Fin-FETs at <i>W fin</i> @ 10nm, with changing <i>H fin</i> from 10nm to 40nm | 60      |

| Table 4.3  | Drain currents of both the Fin-FETs at $n=1$ , $Hfin = 10nm$ , $Wfin$ changing from 10nm to 40nm        | 61      |

| Table 4.4  | Analysis of different logic circuits for 16nm technology node                                           | 70      |

| Table 5.1  | The performance comparison of ring oscillator circuits                                                  | 99      |

# CHAPTER 1

# INTRODUCTION

The introduction of Voltage-controlled oscillator (VCO), types of VCOs, the characteristics of VCOs required to be used in different kinds of applications, the benefits and setbacks are discussed here. On the other side the motivation of the thesis, research gaps and the well-defined objectives explained in this chapter. Finally, the thesis organization of therest of the chapters explained here.

#### 1.1 INTRODUCTION

VCO is the fundamental building block in many electronic circuits, especially for communication and signal processing applications. It plays a crucial role in modern communication systems such as both in wired and wireless. They act as the heart of the system, generating the essential high-frequency clock signals that drive data transmission and reception, and that can be adjusted by a control voltage. Depending on the components and the intended usage, the terms "ring oscillator," "relaxation oscillator," and "LC oscillator" refer to the various electrical and electronic components that can create VCO circuits. LC oscillators often exhibit superior phase noise and higher oscillation frequencies, but this comes at the expense of a limited frequency tuning range and a more complex manufacturing procedure for the inductors and capacitors on the silicon substrate. Ring oscillators provide advantages over LC oscillators in terms of simplicity of manufacture onsilicon and an extensive frequency tuning range [1]. VCO contributes the following to the communication systems.

i) **Highly stable clock generation**: VCO can generate precise and stable clock signals within specific frequency ranges. This stability is crucial for ensuring accurate data timingand synchronization throughout the communication process.

- ii) Frequency agility: VCO can adjust its output frequency based on a control voltage. This enables communication systems to switch between different channels, bands, or protocols seamlessly.

- iii) **Phase modulation and frequency modulation**: By modulating the control voltage of a VCO, information can be encoded onto the carrier signal using either phase modulation(PM) or frequency modulation (FM). This is how Analog and digital data are carried over the communication channel.

#### 1.2 VCO APPLICATIONS:

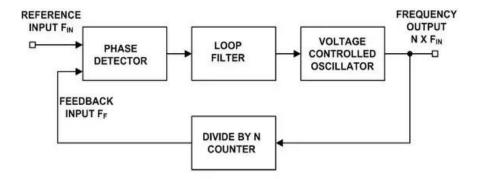

VCO is an essential component in communication systems due to their ability to generate stable, tunable, and modulatable high-frequency signals. Their accuracy makes them vital for efficient and reliable data transmission and reception. VCO is the important block in various applications such as frequency synthesizer circuits, phase- locked loop (PLLs) circuits, and wireless communication systems. Radio and television transmitters for generating the carrier frequencies for broadcasting. Radar systems for generating high-frequency pulses are used for target detection. Global position systems (GPS) receivers for generating the reference signal for time synchronization [4-6]. The application of VCO in PLL is shown in figure 1.1. Input signals of the PLL circuit are two frequencies, one is direct signal, and the other is fed from the output itself (feedback).

Figure 1.1: Block Diagram of PLL [6].

The Phase frequency detection network is a comparator circuit that compares and detects a phase difference between the two signals. The low pass filter bypasses only the lowest frequency component (difference of frequency) and is fed to a bias generator (not mentioned in figure) which generates a DC value corresponding to the difference signal. The DC value is fed as the input of VCO. It generates a frequency signal in accordance with the DC bias. The generated frequency is compared (divide by N is optional) again. Process stops when both the frequencies are equal [31].

#### 1.3 VCO CHARACTERISTICS:

VCO performance is defined by several key metrics [31-32]. Such as:

- i) **Frequency Range**: This specifies the range of frequencies the VCO can generate by adjusting the control voltage. A wider range provides more flexibility for various applications. Ring oscillators typically offer a wide tuning range compared to other VCO topologies.

- ii) **Power Supply**: This denotes the voltage required to operate the VCO. Lower power consumption is usually preferred, especially for portable devices. Ring oscillator circuits arewell known for their low power consumption compared to some other VCO designs.

- iii) **Area Occupied**: Compact designs are desirable for minimizing overall system size and cost. Ring oscillators have a relatively small footprint due to their simple cascade.

- iv) **Power Consumption**: This measures the amount of power consumed by the VCO during operation. Lower power consumption improves battery life and reduces heat generation. As mentioned earlier, ring oscillators are generally energy-efficient compared to the other VCOs.

- v) **Delay**: This is defined as the time required for the VCO circuit to stabilize at another frequency after the control voltage is changed. Shorter delays are preferred for fast tuning and responsiveness. Ring oscillators tend to have fast tuning times due to their simple structure.

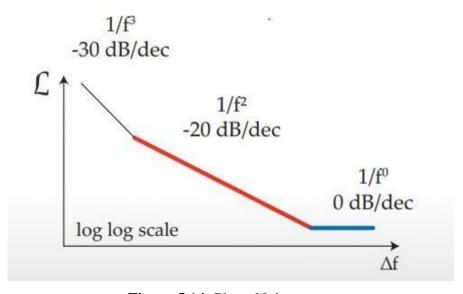

- vi) **Phase Noise**: This is a critical metric that describes the unwanted fluctuations in the VCO's output phase. Lower phase noise ensures a cleaner signal and better data transmission quality. Ring oscillators exhibit relatively higher phase noise compared to some other VCO designs, which can be a limitation for demanding applications [39].

After studying the above characteristics of the VCO, there are many VCO topologies but out of all the topologies, ring oscillator topology is very popular as it covers all the characteristics that a VCO requires.

While ring oscillators offer many advantages like simplicity, small size, and low power consumption, their limitations in phase noise and tuning accuracy need to be considered for demanding communication systems.

#### 1.4 OSCILLATOR:

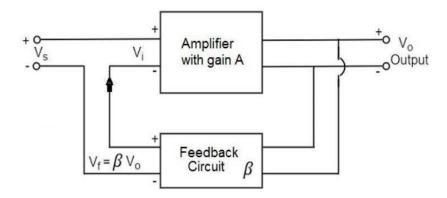

Oscillator is an electronic circuit that generates a periodic signal without an external input. Unlike amplifiers that utilize negative feedback, oscillators employ positive feedback to sustain oscillations. The oscillator block diagram is shown in figure 1.2. Where, in the forward path there is an amplifier with amplification factor A, and the feedback path frequency dependent on attenuation factor is  $\beta(j\omega)$ .

Figure 1.2: Simple Oscillator circuit.

Assume the positive feedback, then to produce sustained oscillations, the oscillator circuit must fulfill the Barkhausen criteria [72-73].

To maintain stable oscillations, an oscillator must fulfill the following conditions:

• **Loop Gain:** The product of the amplifier's gain and the feedback factor must be equal to or greater than 1.

i.e the total loop gain,  $T(j\omega) = |A\beta(j\omega)| \approx 1 - \cdots (1.1)$

• Phase Shift: The total phase shift around the feedback loop must be an integer

multiple of  $360^{\circ}$ .

i.e the phase angle,

$$\angle T(j\omega 0) = 0^0$$

or  $2\pi$ ---- (1.2)

By adhering to these criteria, the circuit can avoid damp or divergent oscillations, ensuringa stable output signal. Once power is switched on, oscillations may begin to decline or even rise if the amplitude criterion is satisfied ( $|T(j\omega o)|=1$  or even >1), but the phase condition is not fulfilled. When the phase criterion is met, the circuit becomes susceptible to oscillations. Even with minimal initial disturbances, the system will tend to produce sustained output oscillations. This is the only way to enable a system's self-excitation via positive feedback. Furthermore, the frequency often deviates from the precise frequency where the design meets the amplitude criterion. Therefore, the system will attempt to oscillate at a different frequency, denoted as ' $\omega_c$ '. Until a limiting mechanism activates, oscillation amplitudes will increase at the new frequency ' $\omega_c$ ', provided the amplitude criterion remains met. However, if the amplitude of the loop gain is < 1, at the frequency w1, will witness damped oscillations or no oscillations at all [76-77].

Oscillator performance is evaluated based on multiple parameters including operating frequency, tuning range, power consumption, output power, and phase noise. To provide a standardized comparison, a figure of merit (FOM) is introduced, as defined by equation (1.3).

$$FOM = 10 \log \left(\frac{f_0}{\Delta f}\right)^2 \left[\frac{1}{V_{DD*I*PN}}\right]$$

-----(1.3)

Where,

'V<sub>DD</sub>' is the supply voltage

'I' is the current

'PN' is the phase noise

' $f_0$ ' is the oscillating frequency

' $\Delta f$ ' is the frequency drift or offset

Clock generation typically employs two types of oscillators: LC oscillators and ring oscillators. LC oscillators leverage the resonance of inductor-capacitor (LC) tanks to produce clock signals, offering excellent noise performance. In contrast, ring oscillators

comprising a series of delay stages, such as CMOS inverters, connected in a loop are more compact in area. They are also capable of generating multi-phase outputs, making them particularly suitable for system-on-chip (SoC) applications where space is limited, and multi-phased clocks are essential for I/O interfaces. Ring oscillators typically exhibit lower FOM values compared to LC oscillators due to higher power consumption and degraded phase noise at equivalent frequencies. To address these limitations, current-starved ring oscillators have emerged, offering improvedtuning range, reduced area, and lower phase noise [2].

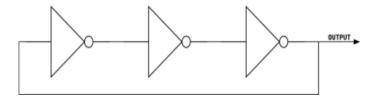

#### 1.5 RING OSCILLATOR

Ring oscillator is the common configuration for VCOs using cascaded odd-number inverter stages are presented in figure 1.3. Each stage in the ring oscillator is known as the delay stage which produces the delay of ' $\tau_d$ ' and the inverter is designed with either NMOS or PMOS or CMOS or BiCMOS or e.t.c. First delay stage output is connected to the second stage as the input, second delay stage output is connect to the third delay stage as the input and the third delay stage output is connected back to the first stage as the input [7].

**Figure 1.3**: Simple three inverter ring oscillator

The frequency (f) of this ring oscillator canbe measured with equation 1.4.

$$f = \frac{1}{2N\tau_d} - - - -(1.4)$$

Where ' $\tau_d$ ' is the delay of each inverter stage, N is the number of delay stages.

The transfer function of the single stage is given by

$$H = \frac{A_0...}{1 + \frac{S}{\omega_0}} (1.5)$$

For 'N' stages, the overall transfer function is

$$H_T = \begin{bmatrix} \frac{A_0}{2} \\ 1 + \omega_0 \end{bmatrix}^N - - - - - (1.6)$$

The angle is

$$\theta_{tot} = N \, Tan^{-1} \left( \frac{\omega}{\omega_0} \right) - \cdots - (1.7)$$

From the angle criteria,

$$\omega_{osc} = \omega_0 Tan(\frac{180^0}{N}) - (1.8)$$

Here, ' $\omega_0$ ' indicates the angular frequency of the oscillator when the loop is completely closed and the equations (1.1) and (1.2) are satisfied. While the odd number of stage configurations always satisfies the oscillation condition, for an even number of stages, the loop establishes positive feedback rather than a negative one, which may result in latch-up.

Ring oscillators hold a special place due to several reasons [12-13]:

- i) Simplicity and Cost-Effectiveness: Unlike other VCO designs that rely on complex tuning mechanisms like LC tanks or crystal resonators, ring oscillators leverage a chain of interconnected inverters. This simple architecture translates to easier design, fabrication, and lower cost compared to other VCOs.

- **ii) Wide Tuning Range**: By adjusting the supply voltage or biasing currents in the inverters, ring oscillators can achieve a substantial range of output frequencies.

- **iii**) **Low Power Consumption**: Due to their minimal circuitry, ring oscillators inherently consume less power compared to other VCOs.

- iv) Easy Integration and Scalability: Ring oscillators rely on standard CMOS technology, making them readily compatible with other integrated circuits and easily scalable for miniaturization in modern electronics.

- v) Robustness and Stability: Their simple design makes ring oscillators inherently robust against environmental fluctuations and temperature changes.

- vi) Phase Noise: While inherently higher than some VCOs, phase noise of ring oscillators can be improved through various techniques.

### **Limitations of ROs compared to VCOs:**

This arrangement leverages the delay in each inverter stage to create a self-oscillating loop. The frequency depends on the number of inverters, their individual delays, and the supply voltage. While simple and efficient, ring oscillators have their limitations, especially in terms of phase noise and tuning linearity. It is assumed that each stage delay time is constant for every inverter stage which makes the circuit restricted to only to the lower frequency tuning range and linearity. And, if the number of stages is increased then circuit will have an increased chip area and power consumption [10].

However, designing high-performance ring oscillators poses several challenges. Their oscillation frequency is influenced by a complex set of variables, including process variations, the number of stages, transistor sizing, and supply/control voltage—often in non-linear ways. This complexity makes it difficult to derive a clear analytical or empirical model linking these parameters. Furthermore, ring oscillator design requires extensive transient simulations to obtain critical time-domain performance metrics, such as operating frequency and RMS jitter, unlike small-signal analog circuits like amplifiers, which are easier to analyze. However, their limitations in phase noise, tuning accuracy, and output power need to be considered for specific application requirements. Ring oscillators come with some limitations compared to other VCOs [16-18]:

- i) **Higher Phase Noise**: They generally exhibit higher phase noise, which can introduce unwanted jitters and affect signal integrity.

- **ii) Limited Tuning Accuracy**: While offering a wide range, the tuning accuracy of ring oscillators is lower than other configurations, especially at higher frequencies.

- **iii)** Lower Output Power: Their simple design limits their output power compared to other VCOs, potentially requiring additional amplification stages in certain applications.

#### 1.6. IMPORTANCE OF MINIATURIZATION

Miniaturization is a rapidly advancing technological approach aimed at creating extremely small electronic, mechanical, and optical devices. This includes components such as computers, semiconductor chips, sensors, biosensors, integrated circuits (ICs), and microprocessors used in vehicles and other modern systems. Today, the prevalence of compact, portable gadgets easily carried in a pocket is a direct result of miniaturization, which enables the downsizing of components while delivering numerous advantages and broad applications. Beyond electronic devices, miniaturization plays a crucial role in the advancement of nanotechnology, allowing for the fabrication of a wide array of structures with unique features and enhanced properties. The benefits of miniaturization are evident in hybrid microcircuits, offering reduced size and weight. With continuous progress in integrating and shrinking portable devices, the concept of wearable computing is becoming a practical reality [11]. The trend of miniaturization is shown in figure 1.4

Figure 1.4: Miniaturization trend [36]

Miniaturization offers numerous advantages, including reduced device size, lower manufacturing costs, increased speed, lower power consumption, improved efficiency, and enhanced portability.

There are a few disadvantages also in Miniaturization, like thermal increase or overheating issue. Decreasing feature size and increasing package densities are making thermal issues extremely important in integrated circuit designing. Extra cooling system is needed for thermal management

#### 1.7. LOW-POWER TECHNIQUES

As mentioned, ring oscillators are popular choices because of their ease of implementation and small power consumption. Still, additional optimizations can be applied. To achieve optimal efficiency in portable systems, employing dedicated low-power techniques alongside device scaling is crucial.

These can include **Circuit-level techniques**: Optimize transistor sizing, reduce switching activity, use low-power logic styles, and utilize power gating to shut down unused circuit blocks. **Architecture-level techniques**: Employ pipelining, low-power clocking schemes, and sleep/idle modes to minimize active power consumption. **System-level techniques**: Optimizesoftware algorithms, utilize dynamic voltage scaling, and implement energy harvesting from ambient sources [14-15].

Few low power technologies in ring oscillator design are

- i) Current-starved technique: Reduce supply voltage and utilize current steering techniques to minimize power consumption [13].

- **Multi-phase technique**: Generate multiple clock signals from a single oscillator, reducing overall circuit complexity and power [77].

- **Dynamically adjustable frequency**: Adapt the operating frequency based on workload demands, reducing unnecessary power consumption when not at peak performance [27].

Overall, the combination of device scaling and low-power techniques proves a potent strategy for maximizing battery life and minimizing system size in portable circuits. By understanding the limitations of scaling alone and actively implementing innovative low-power design principles, we can create efficient and long-lasting electronic devices for the future.

#### 1.8 IMPORTANCE OF ENERGY EFFICIENT DESIGNS

Ultra-low power is one of the main inherent aims of energy efficient designs. Ultra-low power ring oscillator addresses this demand by minimizing power consumption while maintaining reliable performance. Designing ultra-low power circuits in nanoscale technologies poses several challenges. These challenges include overcoming process variations, minimizing power consumption, ensuring stable and accurate frequency generation, and addressing the impact of technology scaling on device characteristics. Nanoscale technologies have revolutionized the field of integrated circuits, enabling the development of highly efficient and compact electronic devices.

Moore's law states that when devices get smaller, planar transistors have negative consequences such as gate oxide tunnelling, increased leakage currents, and the amplification of SCEs. As semiconductor technologies advance, the transistor sizes decrease, leading to increased integration density and reduced power supply voltages. This necessitates the development of novel circuit topologies and design techniques to achieve ultra-low power operation [34].

Research in VLSI unveiled many new device structures such as Double gate FET(DG-FET), Fin-FET and Tunnel FETs (TFET) [4]. A buried oxide layer acts as an insulator on the silicon substrate, making the SOI- MOSFET different from the MOSFET. This configuration leads to a decrease in junction virtual capacitance, the prevention of undesirable latch-up generation, and a reduction in leakage power [5]. The two different categories of the Silicon on Insulator MOSFETs are namely fully depleted SOI-MOSFET and the partially depleted SOI-MOSFET.

The SOI-MOSFET has several drawbacks, including self-heating and challenges associated with producing thin silicon bodies. DGMOSFET is an extreme subject for VLSI research because it can be scaled to the shortest channel length for a given gate oxide thickness. FinFET device is a type of transistor design used in the construction of electronic circuits, particularly in the integrated circuits (ICs). It is an evolution of traditional MOSFET technology and is employed to overcome certain limitations associated with scaling down transistor size. The outstanding electrostatic integrity, minimal leakage current, improved short-channel effect, outstanding efficiency from the un-doped channel structure, elevated carrier mobility, and reduced random dopant fluctuation of FinFET make it an excellent option for future transistor technologies [19-23].

#### 1.9 Fin-FET TECHNOLOGY:

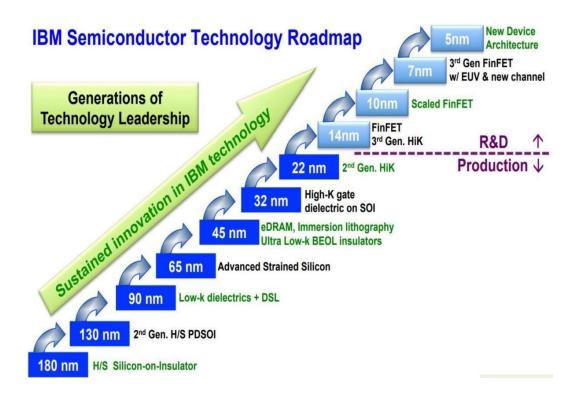

The key feature of Fin-FETs is the fin-like structure that protrudes from the surface of the silicon substrate, serving as the channel through which current flows. This design provides better control over the flow of current compared to traditional planarMOSFETs, allowing for improved performance and energy efficiency. The fin structure effectively increases the surface area for controlling the flow of current. The transition to Fin-FET technology became essential as semiconductor manufacturers faced challenges in shrinking transistor sizes using traditional planar designs. As transistors become smaller, quantum mechanical effects and leakage currents can adversely impact performance and power efficiency. Fin-FETs help address these issues, enabling the continued miniaturization of semiconductor devices. Fin-FET technology has been widely adopted in the semiconductor industry, and it has played a crucial role in the development of advanced processors, memory devices, and other integrated circuits. Technology has contributed to the enhancement of performance, energy efficiency, and overall functionality of electronic devices. The evolution of Fin-FET technology has followed a path of continuous refinement and optimization, with each subsequent generation introducing improvements in terms of performance, power efficiency, and manufacturability as in figure 1.5. Intel introduced the first generation of Fin-FET technology with its 22 nm process technology. Later, the 14 nm process node was introduced, incorporating further refinement [40-43].

**Figure 1.5:** Chip density across technological nodes [2].

Semiconductor manufacturers, including Intel and other leading foundries like TSMC and Samsung, moved to the second generation of FinFET technology at 10nm and 7nm process nodes. These nodes featured improvements in transistor density, performance, and energy efficiency compared to the first generation. The industry transitioned to even smaller process nodes, reaching 5nm and 7nm using EUV (Extreme Ultraviolet Lithography) technology.

Advances in materials, transistor design, and manufacturing techniques are being employed to overcome the technical challenges associated with scaling down to these dimensions.

#### 1.9.1 Fin-FET:

Fin-FET is a type of three-dimensional transistor structure, which has emerged as a leading design for integrated circuits (ICs). They offer significant performance and power efficiency advantages over traditional planar devices. The Key Features and Benefits of Fin device are i) 3D structure, ii) improved electrostatic control, iii) low power consumption, iv) scalability and v) versatility.

In 3D Structure, a vertical fin, surrounded by gate electrodes on three sides, provides superior control over the electric current flow compared to planar transistors. The gate electrodes can be made from polysilicon or metal alloys, offering flexibility in design. Fin-FETs provide better electrostatic control over the channel, reducing short-channel effects (SCEs) and enhancing carrier mobility. This leads to faster switching speeds and higher operating frequencies, making them ideal for applications like processors and GPUs. The lower operating voltage of Fin-FETs results in reduced leakage currents, contributing to lower power consumption compared to planar devices. This is particularly beneficial for battery-powered devices. Fin-FETs are highly scalable, allowing for continued miniaturization and increased chip density. This enables the development of smaller and more powerful electronic devices. Fin-FET technology encompasses various configurations, including multi-gate MOSFETs (Mu-GFETs) and Gate-All-Around FETs, to address different design requirements [50].

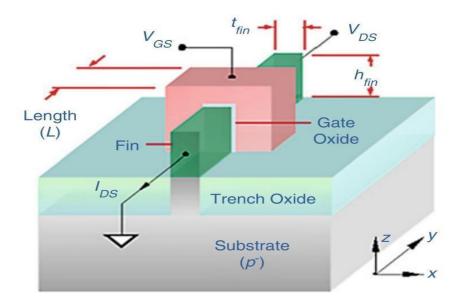

Fin-FET is a type of transistor that offers significant advantages over traditional MOSFET. Fin-FET is a non-planner 3D structure device with the gate surrounding the channel on three sides, providing enhanced performance and power efficiency. The basic Fin-FET structure is shown in figure 1.6 [55-57]. Here, Fin dimensions play a key role in the device performance. The important geometrical parameters are drawn gate length (Lgate) between the source and drain nodes, and the fin dimensions such as fin height (Hfin) and fin thickness (tfin) or width (Wfin).

Figure 1.6: Basic Fin-FET structure.

The key advantages of Fin-FET include **Higher On-State Current**: Fin-FET exhibit higher on-state current compared to bulk MOSFETs and DG-MOSFETs. **Lower Off-State Current**: Fin-FET have a lower off-state current, which is crucial for reducing leakage power. **Faster Switching Speed**: The improved channel control in Fin-FET enables faster switching times, making them suitable for high-performance applications.

The effective channel length (Leff) and width (Weffe) is calculated as in equations (1.9) and (1.10).

$$Leff = (Lgate + 2*Lext) (1.9)$$

Weffe =

$$(tfin + 2*Hfin)$$

(1.10)

The number of fins in Fin FET can be increased to more to achieve more control over the channel. For 'n' number of parallel fins in FinFET, the total width of the channel equation is modified as in equation (1.11).

$$W_{tot}=n(t_{fin}+(2*H_{fin}))$$

----- (1.11)

Then the drain current equation of FinFET is given by equation (1.12)

(I) =

$${}_{1}\mu \epsilon [t +2*H]$$

D  $= {}_{1}m \epsilon \frac{ins fin}{EOT [L_{gate}+2*L_{ext}]} (V_{GS} - V_{th})^{2} ---(1.12)$

#### 1.10 MOTIVATION OF THESIS

Most modern electronic systems, especially in the field of telecommunications, both wired and wireless require high-precision Voltage-Controlled Oscillators to function across a wide range of frequencies. These VCOs are essential components for tasks such as frequency synthesis, signal modulation, and clock generation. Among various VCO architectures, ring oscillators are considered a strong candidate due to their compact size, ease of integration, wide tuning range, and simple design, which make them ideal for System-on-Chip (SoC) applications. They can be easily implemented using standard CMOS or Fin-FET technologies, making them highly compatible with current fabrication processes. There are some design challenges with the ring oscillator such as miniaturization, short channel effects, gain and phase noise issues. In this thesis it is required to address these critical challenges and make them thrive the thirst of battery-operated communication technologies.

#### 1.11 RESEARCH GAPS

After the deep review of the deep literature on ring oscillators, I strongly conclude that there are a few issues in the existing designs. Balancing ultra-low power consumption with high frequency and low phase noise is still an ongoing challenge. Ring Oscillators are highly sensitive to temperature and process variations, affecting frequency stability and reliability. Techniques to reduce phase noise without increasing power or die area are limited.

#### 1.12 OBJECTIVES OF THE THESIS

Based on the research gaps mentioned above after literature study, the following objectives are defined to meet the problem statement.

**Objective-1**: To study literature and investigation of various low power schemes and propose and design a Five stage ring structured based voltage-controlled oscillator using 45 nm technology.

**Objective-2**: Achieve high frequency oscillations in the band ranging above higher frequency according to TRAI millimeter band using dual loop topology.

Objective-3: Optimization of power dissipation while maintaining high frequency

oscillations implement 3, 5 and 21 stage ring oscillator circuits with Fin-FET technology.

**Objective-4**: Simulate the designs and observe the power, delay, frequency and phase noise with tuning linearity

#### 1.13 METHODOLOGY

The Proposed methodology for achievement of the objectives is here.

- a) Study of various low power schemes to apply inverter circuit design.

- b) Implementation of CMOS Inverter on different nanoscale technologies along withlow power schemes. Performing simulations to measure power, delay, and frequencies.

- c) Consider the design whose parameters are very optimized parameters to design ring oscillator circuit.

- d) Design the Fin-FET, design Fin-FET base5 and 21stage ring oscillators.

- e) Simulate the circuit using Cadence Virtuoso tool and compare the results with open literature.

#### 1.14 THESIS ORGANIZATION

**Chapter 1**: Fundamental concepts of ring oscillators, their significances and potential advantages for portable, high-frequency applications are discussed. Subsequently, the importance of miniaturization, the trend of device scaling, ring oscillator characteristics, discussed along with Fin-FET technology.

Chapter 2: The deep literature study on VCO topologies, ring oscillator circuit designs, simulations and the results matching with the technological requirements. The aim is to identify established design principles, innovative optimization techniques, and emerging trends that inform the development of efficient and miniaturized communication circuits.

**Chapter 3**: In this chapter, various low-power schemes discussed by implementing those techniques to implementation of basic inverter circuit, evaluating the effectiveness of various parameters on different nanoscale technologies.

**Chapter 4**: Fin-FET device geometry, characteristics, advantages and challenges are discussed. The impact of parameters like power consumption, frequency range, and area efficiency are discussed.

**Chapter 5**: In this chapter, three, five and twenty-one stage Fin-FET based ring oscillator designs, simulations and results achieved are presented.

**Chapter 6**: Conclusion remarks along with the future scope direction of this research work topic ring oscillator design with the optimized parameters discussed.

# **CHAPTER 2**

# LITERATURE SURVEY

This chapter delves into the various types of oscillator circuits and the design approaches, merits and setbacks of the designs process. It focuses on the slope of improvement of figures of merits of various ring oscillator designs.

(Neha thakur, 2014) [3] explained a low power design, which observed that it depends on the device supply voltage and the threshold voltages. This is commonly beneficial because threshold voltage and supply voltages can be controlled easily. The circuit is further designed effectively to make it operate at higher speed with lower power requirement in the circuit. Thus, by doing so effective care must be taken for designing the circuit elsetrade off will affect the design.

(G. Jovanovic, 2009) [4] explained an N- stage VCO circuit implementation to achieve lownoise. In communication, it is applied for better frequency and high phase noise. It is not required for LC tank oscillator but is useful for the purpose of multistranded wireless transceiver. Power consumption has been reduced with better controlling of output frequency along with the advantage of full swing output signal acquired by controlling reverse body bias. Sushil Kumar et al, suggests differential LC and Voltage Controlled Oscillator generation of the ISM (Industrial, Scientific, and Medical) band, power consumption and layout design.

(Madhusudan Maiti, 2020,) [5] proposed a current-starved technique in the ring oscillator- based VCO circuit. This was designed on the 90 nm CMOS process and is operated with a 1.2Vsupply. This design results 44.59 µW of power consumption while generating a frequency of 1.78 GHz using a 7-stage configuration. This approach effectively balances power consumption and operating frequency.

(**Bodhisatwa Sadhu, 2013**) [6] presented a VCO design to achieve low-phase-noise. This was implemented in 32 nm SOI CMOS process and operated with 1.5V supply voltage in generating 22 GHz frequency. This design power consumption was 36 mW and

exhibiting a phase noise of -127.3 dBc/Hz. The design incorporated a transconductance linearization technique to improve phase noise performance.

(**Viashali, 2014**) [7] designed a single-ended seven stage ring oscillator circuit. This design was implemented in 130 nm CMOS process and operates at 1V supply. This seven-stage oscillator achieved the frequency of 917 MHz while consuming 16.55  $\mu$ W of power. This design demonstrated a significant reduction in power consumption compared to previous approaches.

(T. Sato, 2011) [8] introduced a novel figure of merit (FOML) to evaluate the frequency tuning range of LC oscillators. This metric addresses the limitations of conventional methods that often degrade phase noise when attempting to widen the adjusting range. FOML is derived from the ruin of the inductor's quality factor caused by tuning mechanisms.

$$FOM_L = FOM(f_{cent}) - 20 \log (1 + \frac{FTR}{2}) - \cdots (2.1)$$

where

$$FTR = \frac{f_{max} \pm f_{min}}{f_{cent}}$$

and

$$f_{cent} = \frac{f_{max} \pm f_{min}}{2}$$

(Razavi, 2019) [9] discussed the ring oscillator circuit importance in different applications, different types of ring oscillators and their design approaches along with the performancecomparisons. Finally explained how the ring oscillator is used in the VCO.

(**Bhavana Goyal, 2016**) [10] Proposed a differential configuration type ring oscillator to design VCO for the implementation of PLL circuit. Charge pump based PLL is designed. A five stage differential pair of ring oscillators is designed in 180 nm CMOS process. The circuit was operating with 3V power supply, then 6.5 GHz frequency achieved this circuitand consumed 36 mW of power.

(Sreenivasa Rao Ijjada, 2011) [11] discussed various low power techniques in VLSI circuits implementation. Proposed stacking of transistors techniques in the implementation of inverter, SRAM and few of other circuits and observed that a significant amount of power reduces with the stack techniques comparing with the conventional design approaches.

(Ebrahimi, 2023) [12] designed the ring oscillator which was operated in the subthreshold region to attain low power consumption. Unlike traditional ring oscillators whose frequency is strongly linked to temperature variations, this design incorporates two current sources such as a temperature-independent current source and a CTAT (Complementary to Absolute Temperature) current source. The CTAT current compensates for frequency drifts caused by temperature changes. This was designed in 180 nm RF-CMOS process, the prototype demonstrated a significant reduction in thermalcoefficient (TC) from 240 ppm/°C to 80.4 ppm/°C while maintaining a power consumption of 44.5 μW at the frequency of 1 MHz and a supply voltage of 1.8V.

(**Mahato, 2014**) [13] implemented a low-frequency ring oscillator circuit with CMOS thyristor concept. This design was Implemented in a 250 nm CMOS process and operated with a voltage of 2.5V. the design generated a sinusoidal output waveform operating at 8.94 Hz while consuming 5.7 µW of static power.

(J. C. Park and V. J. Mooney III, 2006) [14] introduced a "sleepy stack" approach in the design of ring oscillator circuit in reaching the low power. This logic circuit maintains its logic state in sleep mode, resulting in low power consumption due to minimal leakage. However, it is the most effective method for reducing leakage power consumption compared to other known strategies. This provides circuit designers with different options for addressing theissue of power leakage.

(Sharma, 2021) [15] highlighted the trade-off between device miniaturization for faster response times and the adverse impact on battery life. Scaling down MOSFET dimensions and operating voltages (V<sub>DD</sub> and Vth) is crucial for achieving low power consumption. However, aggressive threshold voltage scaling introduces leakage currents. The study explored various leakage control techniques and applied them to NAND gate designs implemented in a 16 nm technology node for comparative analysis.

(Ramesh, 2018) [16] derived a formula for the computation of frequency of oscillations of the ring oscillator very quickly. This has three terms such as number of stages, device channel length and empirical constant. A three stage and 23 stage ring oscillators were designed in 180 nm CMOS technology and measured 3.1 GHz and 0.7 GHz frequencies for the 5 and 23 stages respectively.

(P. S. Shanbhag, 2021) [17] designed a stacked inverter-based ring oscillator in 90nm CMOS technology with a mechanism to minimize the PVT variations at the temperature of 25°C. Here, a voltage biased circuit is added to minimize the temperature variations and trim bits are added to decrease the frequency variations. The circuit operated at a voltage of 1.8V and generated 1MHz oscillations and 22.36 μW power.

(Y. Ho, 2013) [18] designed a single stage ring oscillator with bootstrapping technique in 90 nm IP9M SPRVT CMOS technology and operated near threshold voltageof 0.3V to make it temperature insensitive over the period of frequency. This circuit oscillates at a frequency of 235 MHz with a power consumption of 7  $\mu$ W.

(Sreenivasa Rao Ijjada D. C., 2016) [19] discussed scaling limits and issues when it is beyond 45nm technology. And sighted many alternative devices to bulk CMOS especially at ultra nanoscale technologies. FinFET, TFET, SET, etc. are few of those kinds of devices. ExplainedFinFET merits and demerits in the present VLSI circuits.

(Sreenivasa Rao Ijjada C. M., 2016) [20] discussed the FinFET device full custom design using TCAD tool. To subdue the scaling issues a 20 nm FinFET designed using TCAD tools is characterized to check its superior control over the channel, performance and power budget.

(Ajaykumar Dharmireddy, 2019) [21] Designed tri gate SOI 32 nm technology Fin-FET. The fin dimensions such as fin width fixed as 5 nm, Wk=4.43,  $V_{GS}$ =0.7V,  $V_{DD}$ =0.7V,  $V_{DS}$ =0.05Vand the channel length is at 10nm. The fin height varied from 5 nm to 35 nm to see the impact of fin height on the device performance and observed its IV characteristics. From this it's observed that as the fin height increases effective channel with increase and the device performance increases.

(**Saurabh Sinha, 2012**) [22] discussed the predictive technology models (PTM) for FinFET technology forecasted and presented in the ITRS 2011. Explained the use of these models from the technology node 20nm to 7nm in the circuit implementation.

(**Sreenivasa Rao Ijjada A. d., 2020**) [23] designed a SOI-TG-FinFET using Verilog-A. The specifications of this device were considered as length=20nm, fin height=40 nm, fin

width=20 nm and the supply potential=0.7V. And designed CMOS inverter along with power gating low power scheme. Then a three-stage ring oscillator was designed and measured its frequency of oscillations as 2GHz, and power dissipation is 15% less than conventional ring oscillator.

(A. A. Zayed, 2019) [24] proposed and nine stage ring oscillator using Fin FET technology. The geometrical definitions of Fin-FET are defined as Lg=24 nm, Hfin=28 nm, Wfin=15 nm and operated at the voltage of 0.9V. The power consumption of this circuit is 264 μm and generates 4 GHz of oscillations.

(Acharya, 2011) [25] proposed a novel ring oscillator design optimized for performance. A nine-stage ring oscillator was implemented using a 130 nm CMOS process with transistor dimensions of Wn=200 nm, Wp=334 nm, and L=174 nm. The optimal device sizes were determined through a multi-objective optimization process using the CMODE algorithm. Phase noise, a critical performance metric, was calculated based on a specific formula.

$$\mathcal{L}\{\Delta f\} = \frac{8}{3\eta} \frac{\kappa T}{P_{avg}} \frac{V_{DD}}{V_{char}} \frac{fos^2}{\Delta f^2} --(2.2)$$

Where

$$V_{char} = \frac{\Delta V}{\gamma}$$

$\Delta V$  gate overdrive potential,

$\gamma$  coefficient=2/3 for LCDs,

$\Delta f$  offset frequency from carrierat which the phase noise measured,

$\eta$  characteristic constant =0.7 to 0.9.

$$Pavg = \eta V_{DD}I_{avg}$$

$$P_{avg} = \eta V_{DD} Nq_{max} fosc$$

$$P_{avg} = \eta V_{DD} NC_{tot} V_{DD} f_{osc} ----- (2.3)$$

(Lourts Deepak, 2012) [26] designed Fin-FET based three stage and five stage ring oscillator circuits in 32 nm technology for the frequencies of 40 GHz and 60 GHz. In this paper the resistor value is fixed at 10k ohms. The capacitor values are 4.3 pF and 2.65 pF for 40 and 60 GHz frequencies respectively. The delays of each stage in five stages ring circuits are 0.46 ps,0.48 ps,0.52 ps,0.54 ps and 0.56 ps.

(N. Collaert, 2004) [27] Discussed the modification of 180nm planner ring oscillator layoutfor the Fin-FET devices. Fabricated p-FET with gate length Lg=35nm and n-FET gate length Lg=25 nm, and 10 nm fin width. Implemented 41-stage ring oscillator circuit with fin dimensions as Hfin=80 nm and Wfin=10 nm. The. P and N channel FETs effective channel widths are derived from Wp=92 (Wfin+2Hfin) and Wn=60 (Wfin+2Hfin) and set as Wp=17  $\mu$ m and Wn=10  $\mu$ m respectively. The potentials are set as Vth=0.2V and V<sub>DD</sub>=1.5V. Then the fabricated 41 stage Fin-FET based ring oscillator circuit obtained 60 ps delay, Ioff = 60 nA and Idsat=380  $\mu$ A.

(A. A. Zayed, FinFET Based Low Power Ring Oscillator Physical Unclonable Functions, 2019) [40] implemented a Fin-FET based ring oscillator for implementation of physical unclonable functions (PUFs) in order to use in low power IoT applications. Frequency divider and D-FFs were used in the place of counters. NCSU PDK 20 nm Fin-FET technology used in the design process, operated with a potential of 0.8V and achieved  $264~\mu W$  of power.

(**K. Das, 2020**) [29] designed 180 nm CMOS and NMOS ring oscillators based on current staved technique to achieve a center frequency of 2.5 GHz suitable for Wi-Fi and Bluetooth applications. Made a comparison between two types of ring oscillators and made the conclusions as NMOS-based ring oscillator is optimal for phase noise performance and CMOS Ring oscillator is optimized for power of 4.61 μW.

(**K. S. Zaman, 2020**) [30] presented a three-stage ring oscillator design with current-starved technique to achieve low power for wireless applications which are operating within the ISM band of 5 GHz. This was designed in 130 nm CMOS process and simulated using ELDO Spice. This design was operated with a voltage of 1.2V and provided power consumption of 8 mW and a phase noise of -78 dBc/Hz at 1 MHz offset. The proposed delay cell occupied an area of 81.27 μm<sup>2</sup>.

(M. S. K. Hemel, 2023) [31] described the role and importance of healthcare workers in monitoring the patients. IoT-based wireless health monitoring systems have the potential to significantly reduce human intervention. This research incorporates a single-ended ring oscillator VCO, fabricated using 50 nm CMOS technology, as a core component. The VCO demonstrated a tunable frequency range from 1.67 GHz to 3.13 GHz by adjusting the control voltage between 0.9 V and 1.5 V. To achieve an oscillation frequency of 2.4 GHz, an input voltage of 1V is applied.

(Akanksha Gupta, 2020) [32] proposed a hybrid CMOS VCO designed to achieve low power consumption and a wide linear operating range. The core of the design involved a CMOS voltage-controlled oscillator constructed using three-transistor CMOS NAND gates. Ring oscillator configurations with three, five, and seven stages were explored. A novel delay cell comprising three CMOS NAND gates operating at a supply voltage of 0.7V was introduced. The study focused on regulating output frequency, power dissipation, and the overall performance of the hybrid CMOS VCO across different stage configurations. The hybrid approach demonstrated superior linearity compared to traditional CMOS circuits, eliminating the need for additional components like resistors for tuning.

# CHAPTER 3 CMOS RING OSCILLATOR DESIGN

In this chapter, discussed the implementation of basic inverter design and the importance of low power schemes in VLSI circuits design. Applied these low power schemes in the design of different inverter circuits for the implementation of five stage ring oscillator.

# 3.1 SCALING THEORY

The high-density chips in VLSI technology require transistors of sizes as small as possible. The concept of device size reduction is commonly known as scaling. Device scaling refers to deliberately reducing a device's total size using current technology while maintaining the exact geometric proportions of larger devices. Device scaling is a principle that involves reducing the size of a transistor by a constant factor in both horizontal and vertical dimensions. We anticipate that the scaling process will alter the gadget's operating parameters. The scaling trend according to ITRS (International technology road map for semiconductors) is presented in figure 3.1. Increased switching speed, reduced size and power dissipation are the benefits of scaling. With the scaled SiO2 thickness loses gate dielectric properties. In scaled devices, in addition to gate potential  $V_{GS}$ , drain potential  $V_{DS}$  will also show greater impact on the carrier flow in the channel [38].

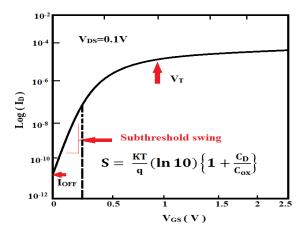

With increase in drain potential  $V_{DS}$  the channel current can be increased by reducing the potential barrier even when  $V_{GS} < V_{Th}$  is called subthreshold current The scaling process unavoidably causes noise, reducing high-density chips' dependability. In Long channel devices (LCD), the leakage components are tolerable, whereas in short channel devices (SCD), there is a significant number of leakages, which makes the device inefficient [1].

**Figure 3.1:** Trends in future size over time [36].

In LCDs, the dynamic power is more than the static power, whereas in SCDs, the static power is more than the dynamic power and increases rapidly along with the device scaling with respect to the dynamic power in a VLSI chip. The progress of the Bulk MOSFET scaling leads to serious Short Channel Effects (SCEs), which include the gate oxide, Sub-threshold, reverse bias, gate induced drain leakages, and device-to-device variations and punch-through effects [34]. Sub-threshold and gate oxide leakages contribute more shares in static power in the SCDs. In MOSFET, sub-threshold leakage current has dominated the gate leakage current up to the 65 nm technology. But, beyond this technology the scenario has reversed. According to the ITRS scaling trend, for a new technology, the amount of gate oxide thickness (tox) in the MOSFET was reduced by 18%. In MOSFET, for reliable operation, the minimum 'tox' should not be less than 2 nm thickness. But practical calculation of tox at 65 nm technology, oxide thickness becomes 1.4 nm. Hence, there is a gate leakage which is 1000 times more than the sub- threshold leakage [14].

## 3.2 RING OSCILLATOR

The introduction about ring oscillators is well defined in section 1.5. Ring oscillators are thefundamental building blocks in PLLs and frequency synthesizers. Employing an odd number of inverter stages in a delay buffer chain ensures signal inversion, leading to sustained oscillations. This configuration effectively minimizes power consumption compared to even-numbered chains. Lower power consumption, stable frequencies, and rapid response times all contribute to more efficient and reliable communication systems.

A perfect ring oscillator should have the following features [16-18]:

- Low power consumption: Minimizes energy footprint and operating costs.

- Low phase noise: Ensures reliable signal transmission and minimizes data errors.

- Minimal stage delay: Reduces overall VCO delay and improves response time.

- Low jitter: Provides stable frequencies and accurate synchronization.

- Wide frequency range: Allows for versatile usage in various communication applications.

Traditional ring oscillator designs often suffer from high power consumption and temperature- dependent frequency variations. Increasing the number of stages for wider frequency range unfortunately amplifies stage delay, leading to slower oscillation and higher power draw. Addressing these challenges requires innovative approaches:

- ❖ Bias current control: Adjusting the bias currents of transistors in each delay unit allows precise control of propagation delay, enabling faster oscillations without increasing stage count.

- Sleepy stack approach: This technique combines bias current control with a dedicated network to regulate power consumption.

- ❖ Single-stage inversion loop: Which involves only one inversion between the output and input stages, is employed to minimize power consumption. This approach effectively reduces power dissipation compared to designs with multiple inversions.

By strategically implementing these techniques, modern ring oscillator designs can achieve significantly improved performance compared to traditional approaches. VCO is responsible for generating precise and stable clock signals, and is achieved through the ring oscillator, and a crucial aspect of their performance is low jitter. Jitter is defined as the short-term variations in the timing of a clock signal. These variations can be initiated by noise, power supply fluctuations, and the temperature changes.

High jitter can disrupt digital circuits and degrade signal integrity, leading to errors and performance issues. Several inherent features of ring oscillators contribute to their ability to achieve low jitters:

- Differential operation: Many ring oscillators utilize differential designs, where

two identical loops run in opposite directions. This cancels out common

noise sources, reducing jitters.

- **Symmetrical delays**: By carefully matching the delays of each inverter stage, we willachieve more stable and predictable oscillations, minimizing jitters.

- **Controlled biasing**: Adjusting the bias current of the transistors in the inverters allows fine-tuning of the oscillation frequency and jitter performance.

Ring oscillators used to use more power and have more excellent phase noise for the same frequency, but they had a lower FOM than LC oscillators. The target performance for the VCOis the center frequency of 200 MHz and a phase noise requirement of -100 dBc @ 100 kHz. The implemented VCO was compared to an existing LC oscillator with similar specifications. The key trade-off between the ring oscillator and LC oscillator lies in area and power consumption. Ring oscillators generally occupy a smaller area but consume more power compared to LC oscillators [8]. This trade-off is a critical consideration when selecting the appropriate oscillator type for a specific application.

## 3.3 RING OSCILLATOR DESIGN

A ring oscillator involves an odd number of inverter stages which are connected in a closed loop configuration. In this configuration, the output of each inverter stage is the input to the subsequent stage and the final stage of inverter output is feeding back to the first stage. This arrangement offers advantages such as straightforward implementation and a wide operating frequency range at low control voltages. Each inverter stage within the ring oscillator contributes a delay to the overall oscillation period. For example, consider the five-stage CMOS ring oscillator as in figure 3.2, It consists of five basic CMOS inverters connected in a circular pattern [25]. The oscillator only relies on electricity for its operation. Within the realm of semiconductor physics, there exists a point at which the oscillations become uninterrupted. Circuits may employ this approach. Amplify the vibrations at a frequency of 33 oscillations per unit of time. Due to their comparable power consumption, people often use voltage-controlled oscillators (VCO) and ring oscillators. The oscillator's speed limitations stem from the maximum voltage it can supply to its circuits. The delay occurs at different stages of the chain.

**Figure 3.2:** A Five stage Ring Oscillator [28].

In ring oscillator,

- **Each** inverter introduces a slight delay due to its switching time.

- The cumulative delay of the loop will determine the oscillation frequency.

- ❖ The output signal transitions between high and low voltage levels, creating a clock signal.

For an 'N' stage ring oscillator, the frequency of oscillations ( $f_{osc}$ ) can be calculated with equation earlier presented in (1.1) and once again shown in equation (3.1). Where, the delay ( $\tau_d$ ) is the single inverter delay which is approximated by the time constant of an equivalent RC low-pass filter.

$$f_{osc} = \frac{1}{2N\tau d} - - - -(3.1)$$

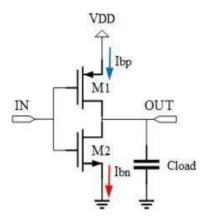

# 3.4 BASIC INVERTER

As we know, inverter is the basic component in the ring oscillator. The fundamental CMOS inverter employed with a PMOS and an NMOS transistor connected as shown in figure 3.3. When the input voltage (Vin) is low (logic 0), the PMOS will conduct, and pulls the output high to  $V_{DD}$ . Conversely, when Vin is high (logic 1), the NMOS transistor will conduct, pull the output low to ground (GND). This complementary structure enables low static power consumption [29-30]. For optimal inverter operation, both the NMOS and PMOS transistors must operate in the saturation region, defined by the conditions in equation (3.2). Where  $V_{GS}$  and  $V_{Th}$  are the gate to source and threshold potentials.

$$V_{GS} > V_{Th} \text{ and } V_{DS} > (V_{GS}-V_{Th})$$

----- (3.2)

This operating region introduces inherent resistance and parasitic capacitances within the transistors, contributing to propagation delay ( $\tau_d$ ). Propagation delay is the sum of rise and fall times. Therefore, the rise time or rise time delay ( $\tau_{rise} = \tau_{dHL}$ ) and fall time or fall time delay ( $\tau_{fall} = \tau_{dLH}$ ) are measured with equation (3.3) and equation (3.4) respectively.

$$\tau rise = \tau dHL = ln (2) Rnon Cload ---- (3.3)$$

$$\tau fall = \tau dLH = \ln(2) Rpon Cload - (3.4)$$

Where, 'Rnon' is the saturation on resistance of NMOS device and 'Rpon' is saturation on resistance of PMOS transistor. 'Cload' is the load capacitance of the inverter stage.

Figure 3.3: Basic Inverter circuit [28].

Total delay of an inverter is given by equation (3.5) and the frequency of the inverter circuit is given by the equation (3.6).

$$\tau d = (\tau dHL + \tau dLH)/2 - (3.5)$$

$$f_{osc} = \frac{1}{2\tau_d} - - - (3.6)$$

In integrated circuits, with technology above 180 nm, dynamic power makes up most of the power share, whereas static power predominates in chips with technology below 180 nm. Subthreshold leakage or current primarily causes static power dissipation. Subthreshold leakage occurs when the potential in between gate and source is lower than the device threshold voltage, a current flows in the device to the source from the drain [32-33]. Subthreshold current exhibits an exponential dependence on device threshold voltage. As device dimensions shrink into the nanoscale regime, aggressive threshold voltage reduction starts to a pronounced rise in subthreshold leakage. Consequently, minimizing this leakage current becomes crucial for optimizing device performance and energy efficiency at advanced technology nodes.

Numerous strategies have been proposed to mitigate static power consumption, including the stack approach, sleep transistor approach, sleepy stack approach (**SS**), zigzag approach, sleepy keeper (**SK**) technique, dual Vth technique, dual Vth with sleep transistor, dual Vth with zigzag (**dVth Zigzag**), sleepy dual Vth, Sleepy stack with dual Vth (**SS dVth**) and dual Vth with sleepy keeper (**SK dVth**) [37].

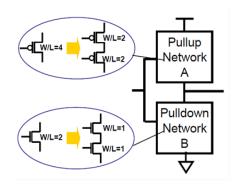

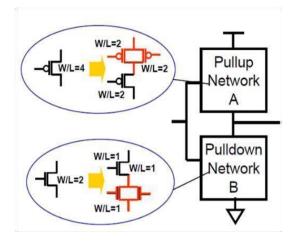

While each method offers specific advantages, they all come with certain trade-offs, as outlined in reference [49]. Optimizing the inverter design itself (e.g., using current-starved inverters) can help achieve higher oscillation frequencies without significantly increasing the number of inverters. Techniques like variable biasing or using additional control circuits can be employed to adjust the oscillation frequency within a certain range, even with a fixed number of inverters in the ring. NMOS based, CMOS inverter based, CS amplifier based, Source follower type and Differential amplifier based are the few techniques. The fundamental inverter depicted in Figure 3.3 comprises PMOS and NMOS transistors with respective widths of Wp=2 and Wn=1 units.

# 3.4.1 Stack Technique

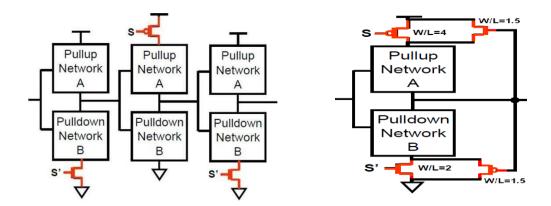

The stack technique involves replacing each individual transistor with a pair of identical transistors connected in series. This modification results in a 50% reduction in the width of each transistor, as depicted in Figure 3.4. This is a power-saving strategy in CMOS circuits that involves replacing individual transistors with pairs of series-connected transistors. This modification has several benefits: